Digital Electronics

Data Converters

Practice questions from Data Converters.

3

Total0

Attempted0

Correct0

IncorrectA 10-bit analog-to-digital converter (ADC) has a sampling frequency of 1 MHz and a full scale voltage of 3.3 V.

For an input sinusoidal signal with frequency 500 kHz, the maximum SNR (in dB, rounded off to two decimal places) and the data rate (in Mbps) at the output of the ADC are _________, respectively.

Given: Resolution bits

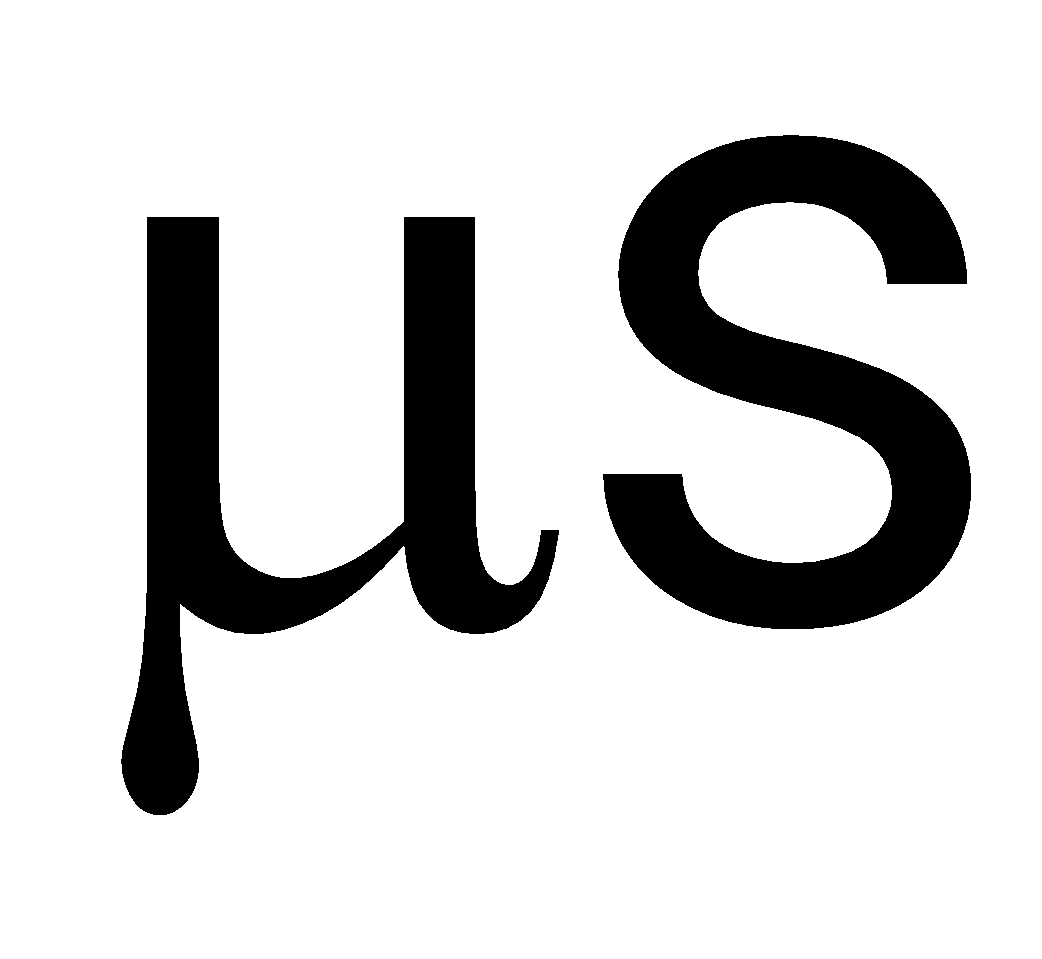

sampling frequency

full scale voltage (FSV)

Input sinusoidal signal frequency

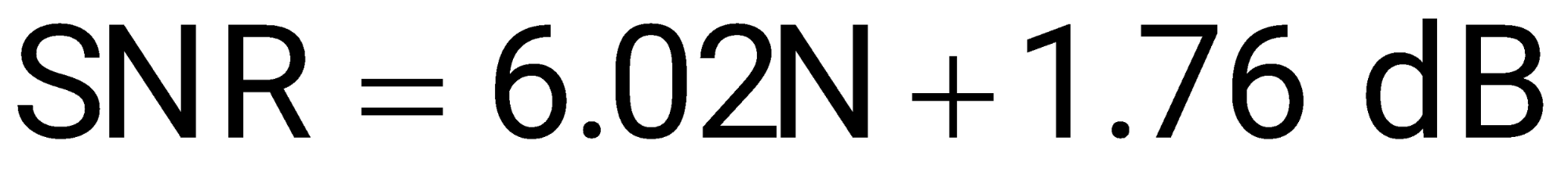

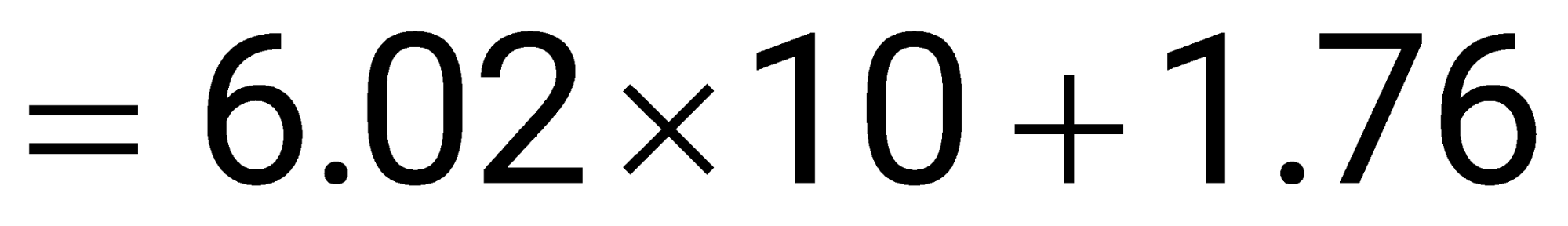

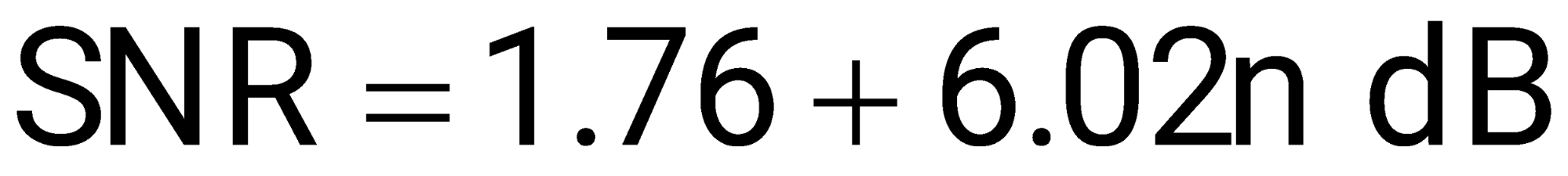

Maximum SNR (in dB) for -bit resolution,

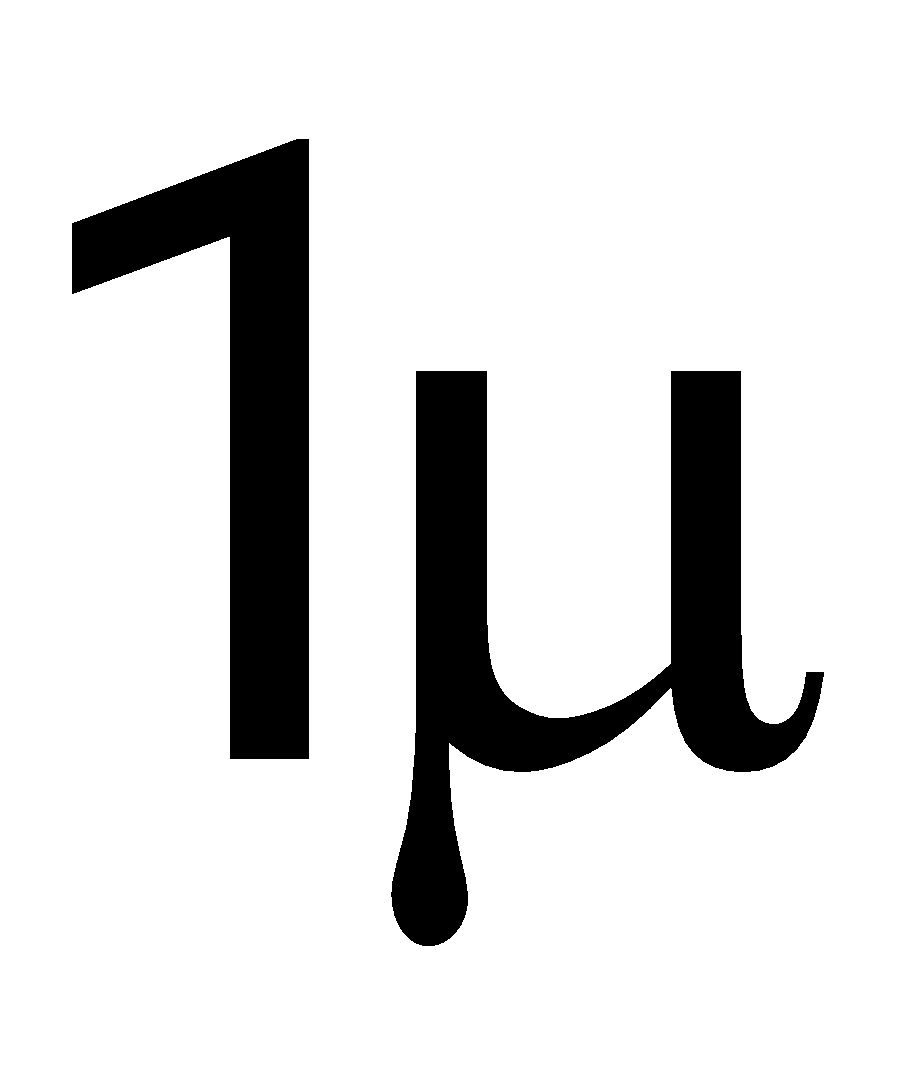

Data Rate sampling frequency No. of bits per sample

Hence, option (A) is correct.

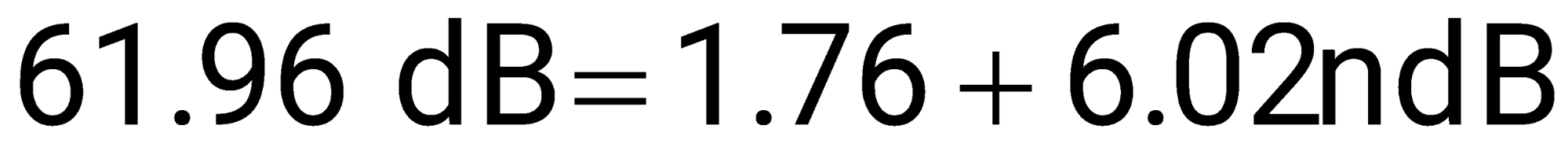

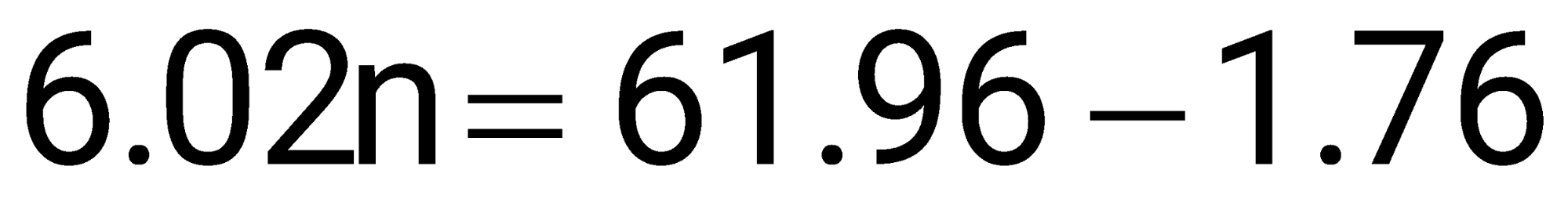

The signal-to-noise ratio (SNR) of an ADC with a full-scale sinusoidal input is given to be 61.96 . The resolution of the ADC is __________ (rounded off to the nearest integer). bits.

We know that for sinusoidal input, the signal to noise ratio (SNR) is given as,

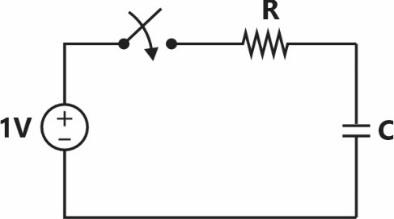

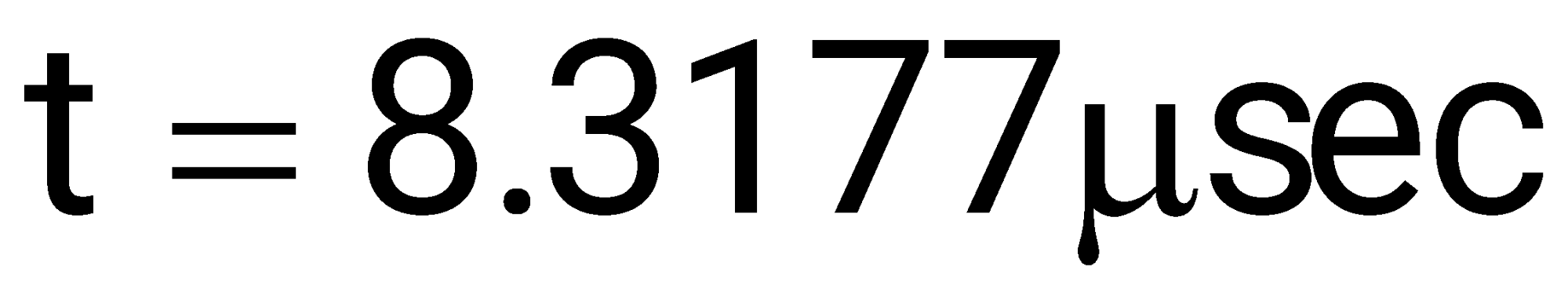

A sample and hold circuit is implemented using a resistive switch and a capacitor with a time constant of . The time for sampling switch to stay closed to charge a capacitor adequately to full scale voltage of with 12-bit accuracy is ________ .

(rounded off to two decimal places)

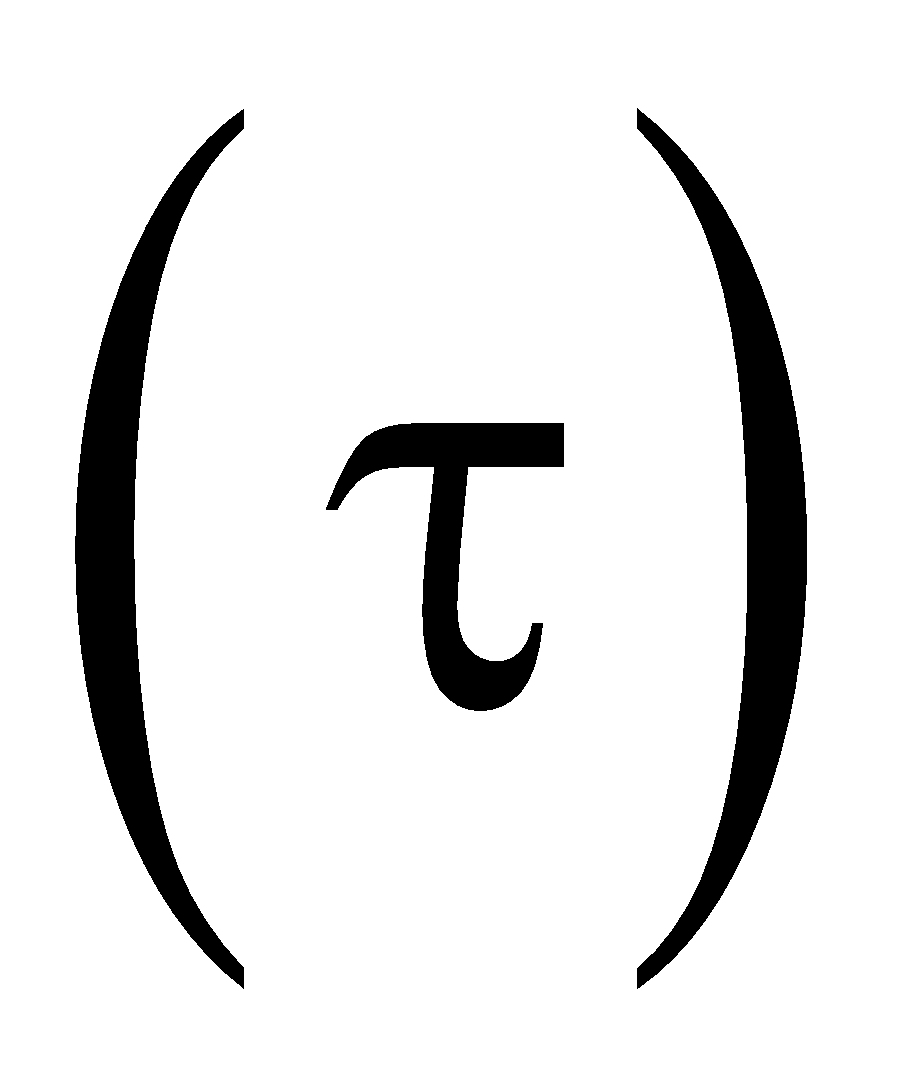

Given: Time constant of sec.

Full scale voltage

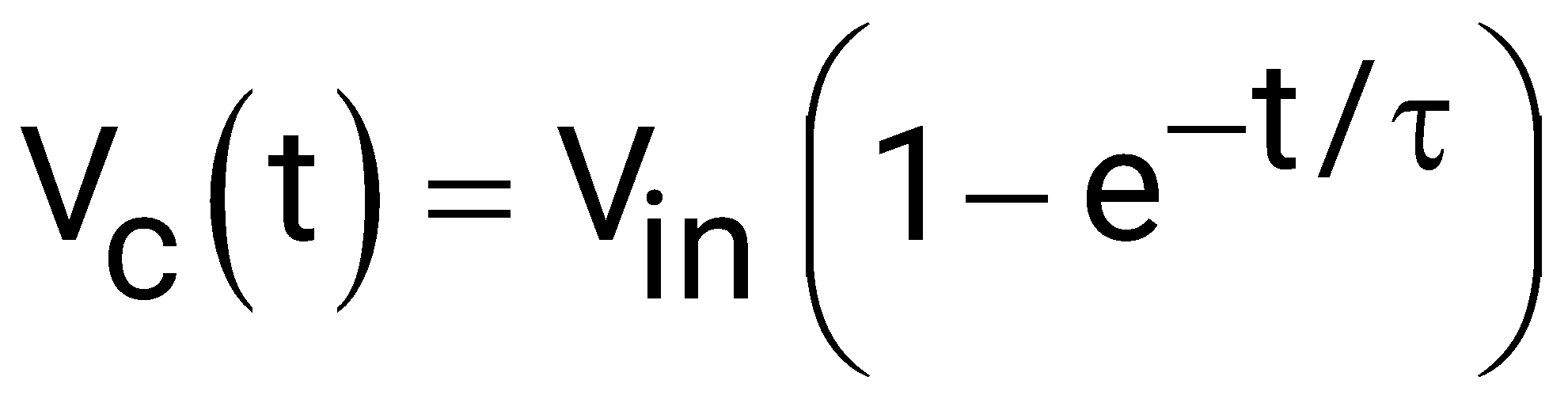

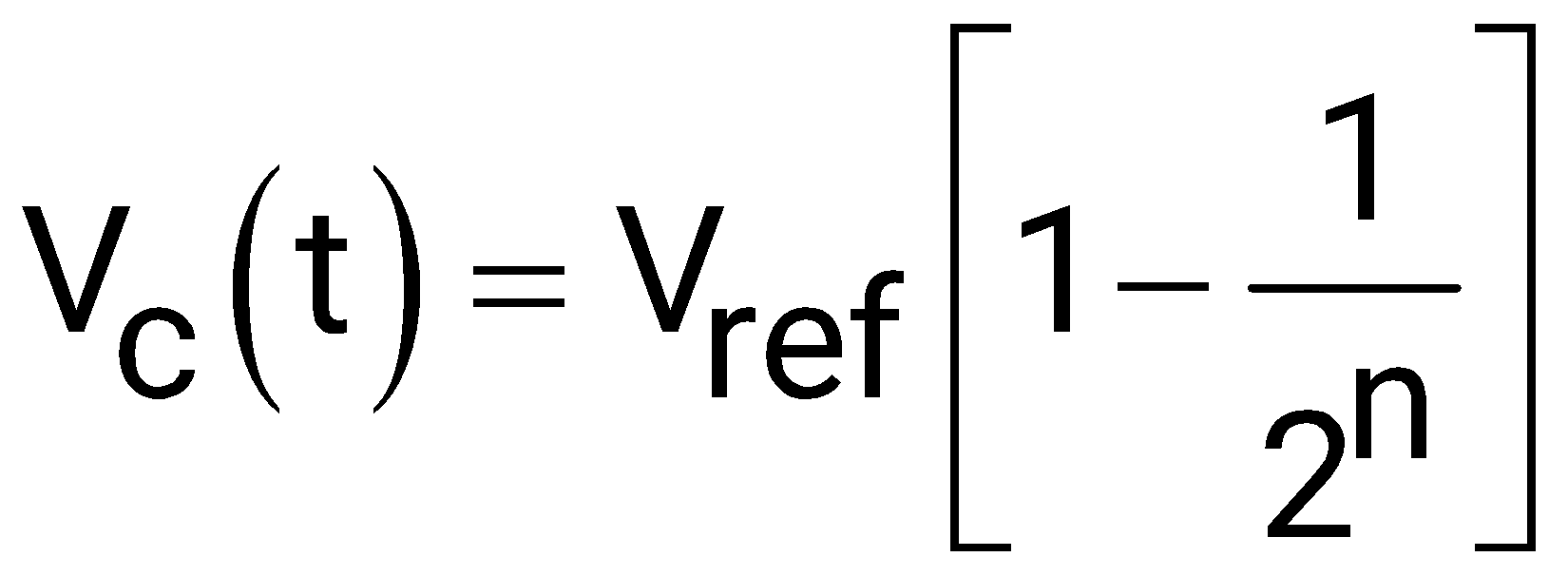

Steady state voltage of circuit is given by

…(i)

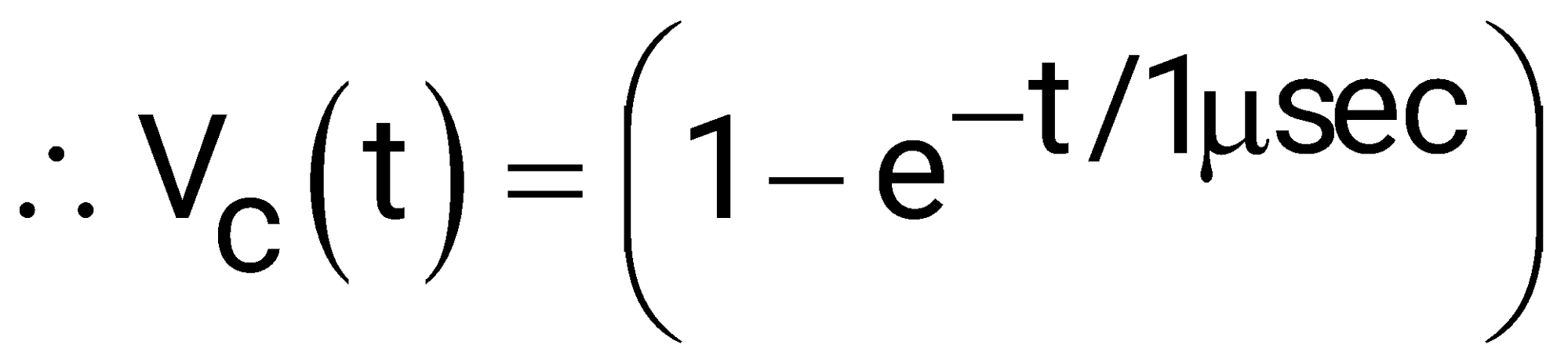

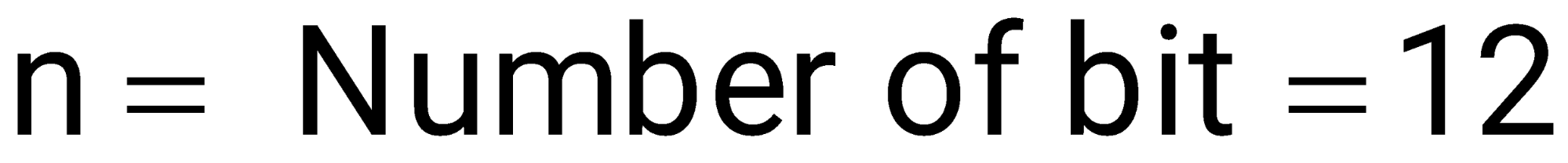

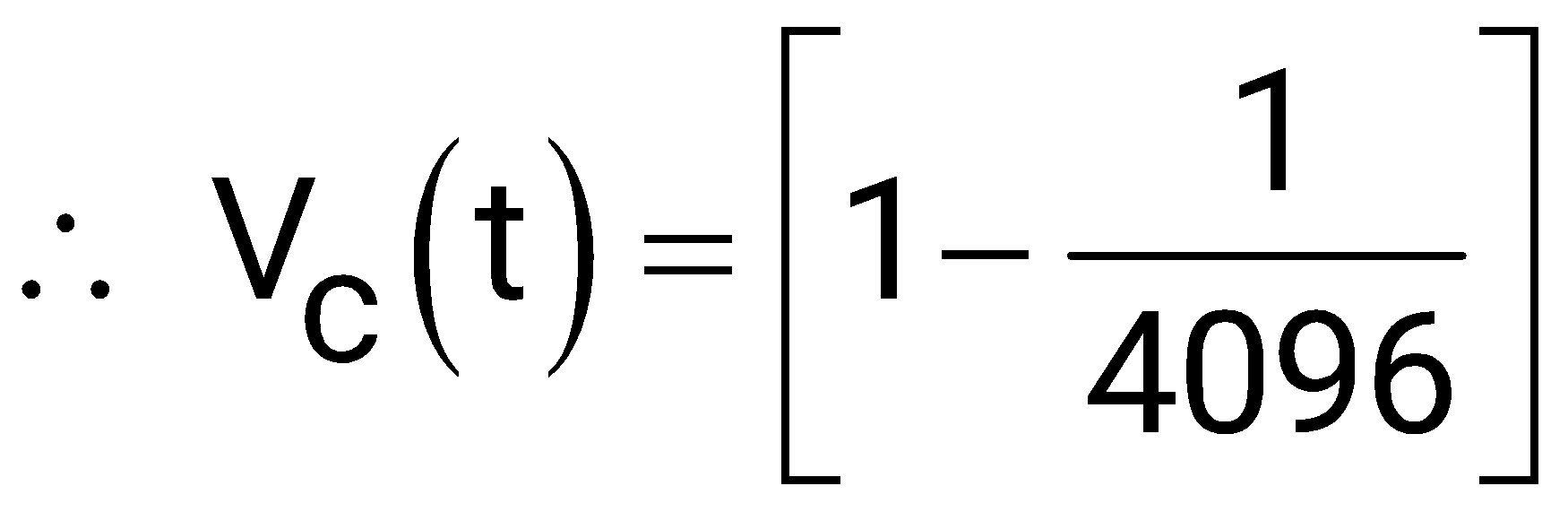

To calculate the voltage to stay closed to charge capacitor adequately to a full scale voltage with 12 -bit accuracy is given by

…(ii)

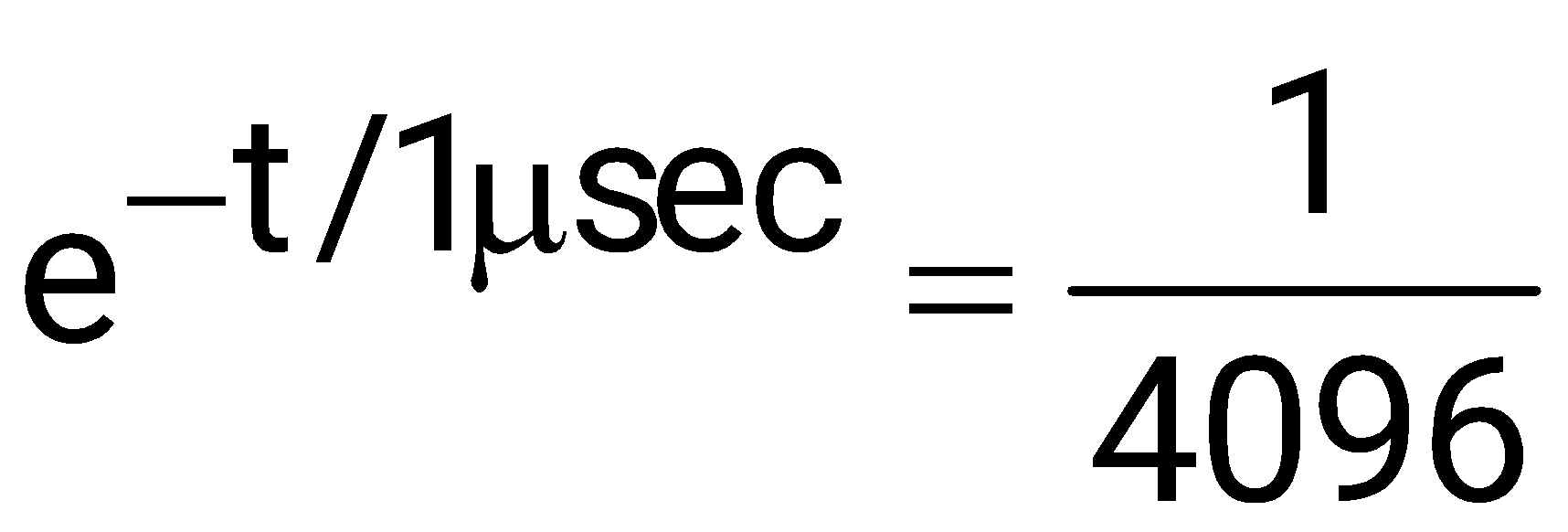

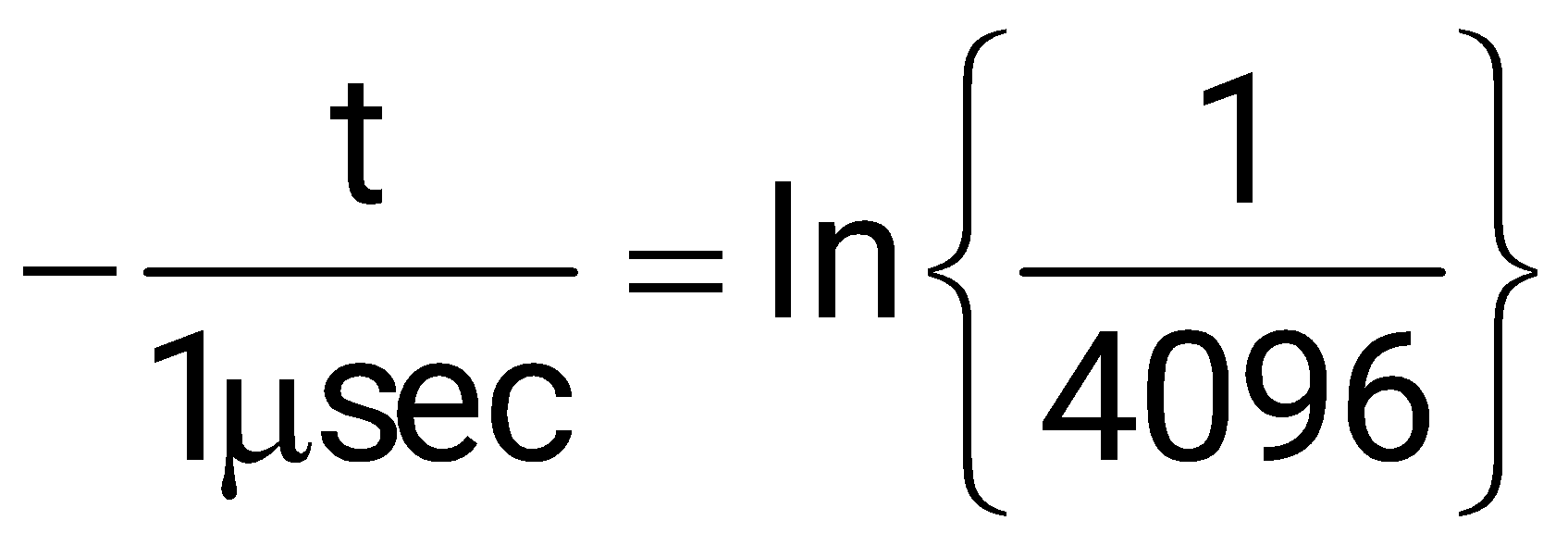

Comparing equations (i) and (ii), we get,