Digital Electronics

Combinational Circuits

Practice questions from Combinational Circuits.

5

Total0

Attempted0

Correct0

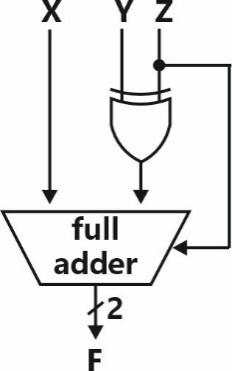

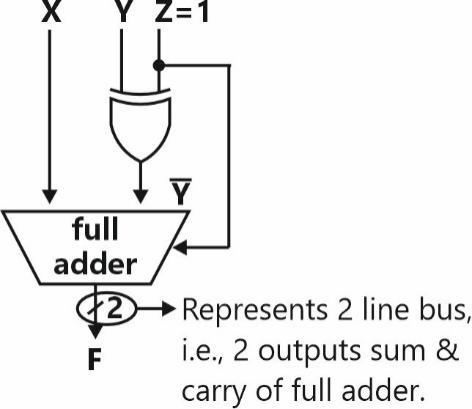

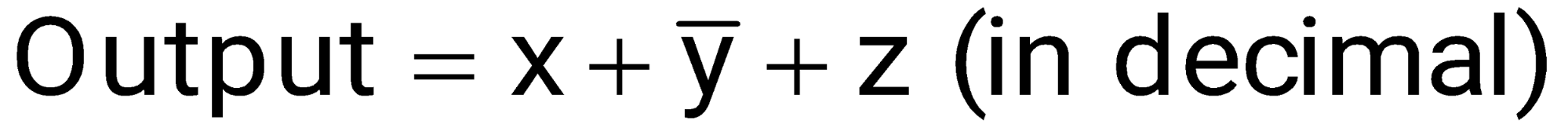

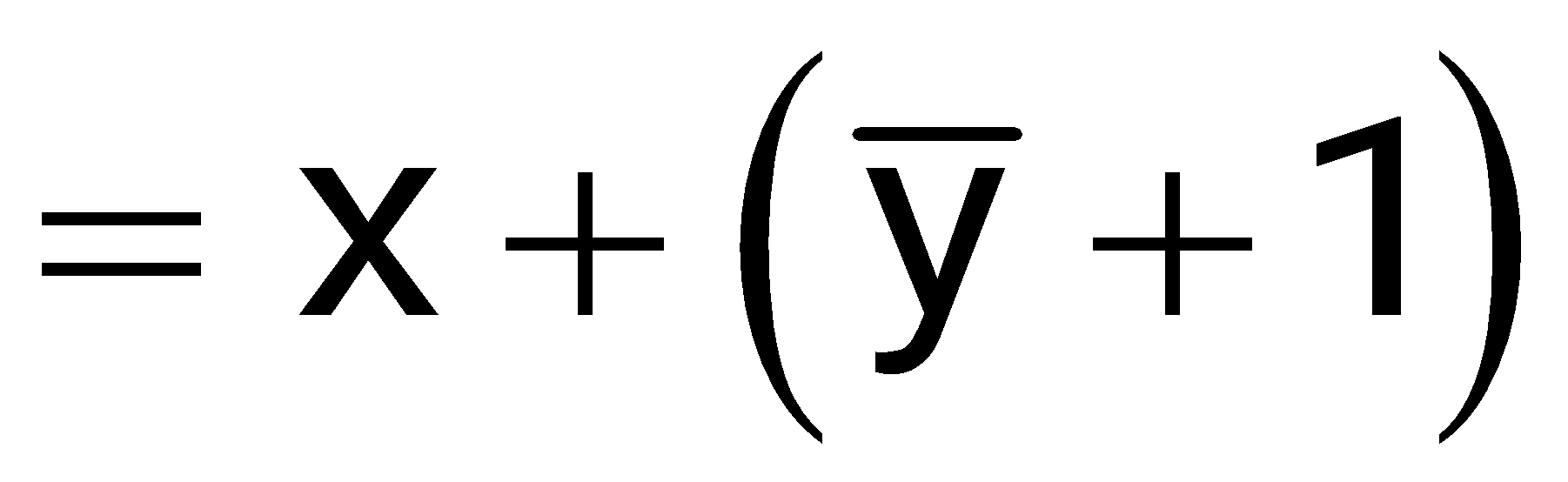

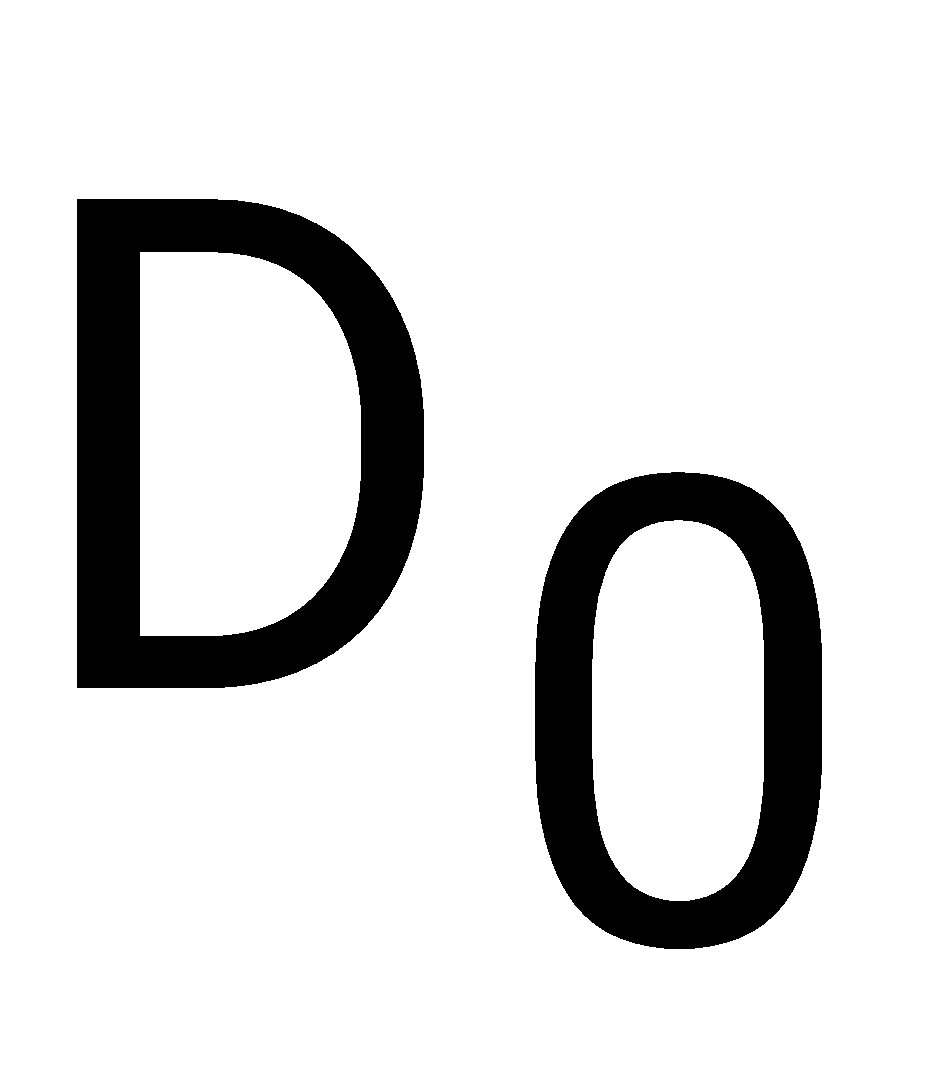

IncorrectA full adder and an XOR gate are used to design a digital circuit with inputs , and , and output , as shown below. The input is connected to the carry-in input of the full adder.

If the input is set to logic ' ', then the circuit functions as _________ with and as inputs.

When one input of XOR Gate is 1 then output is complement of other input.

→ 2’s Complement

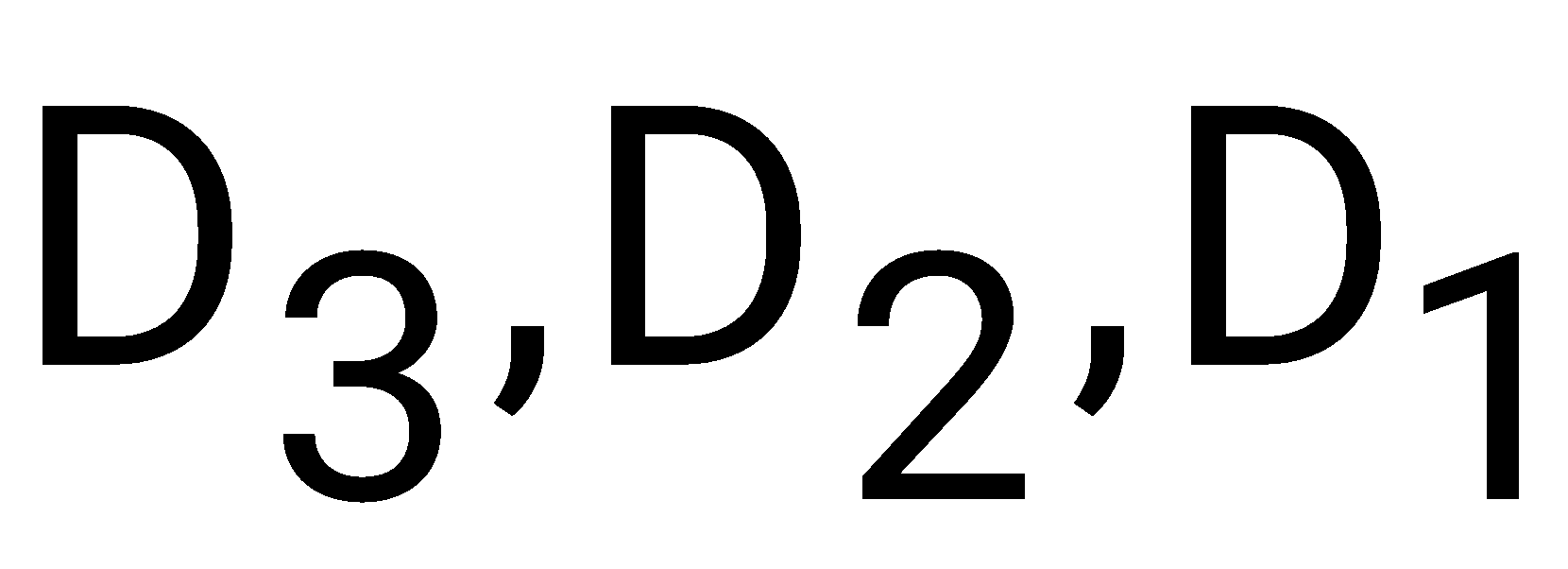

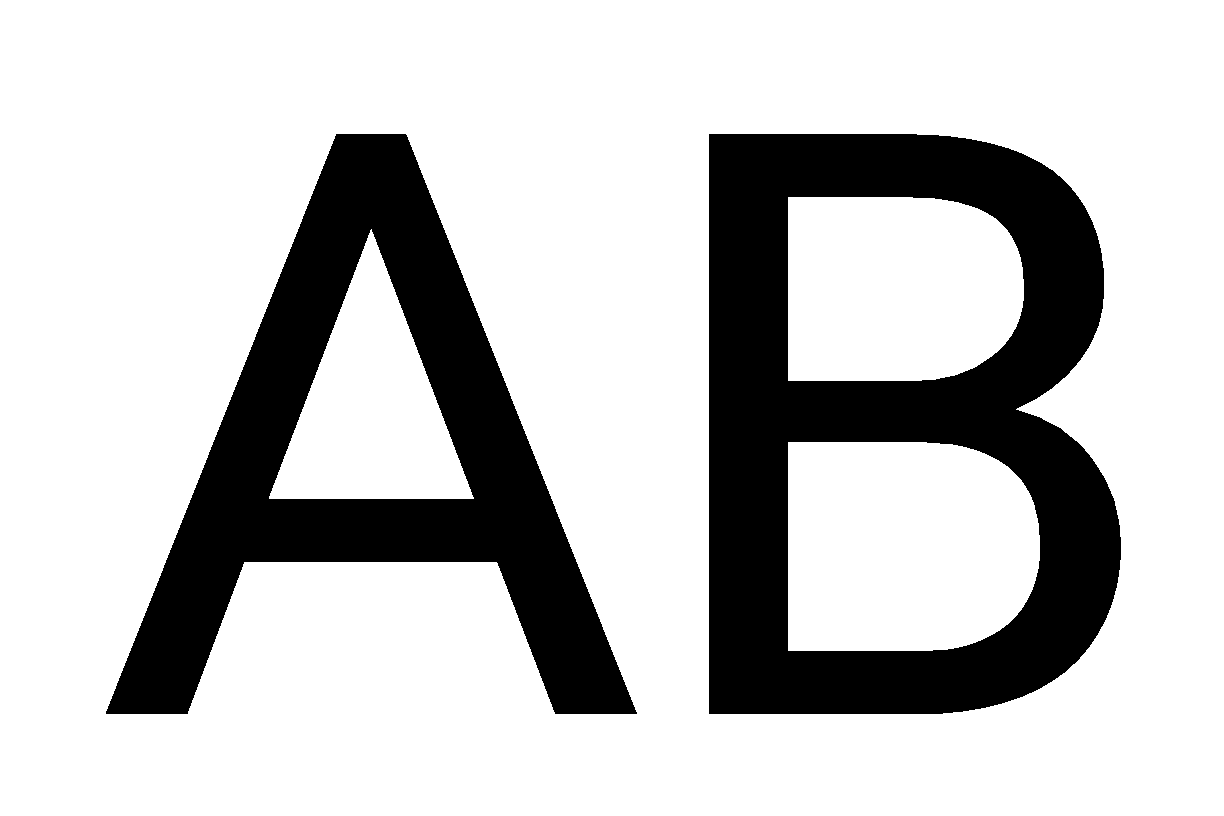

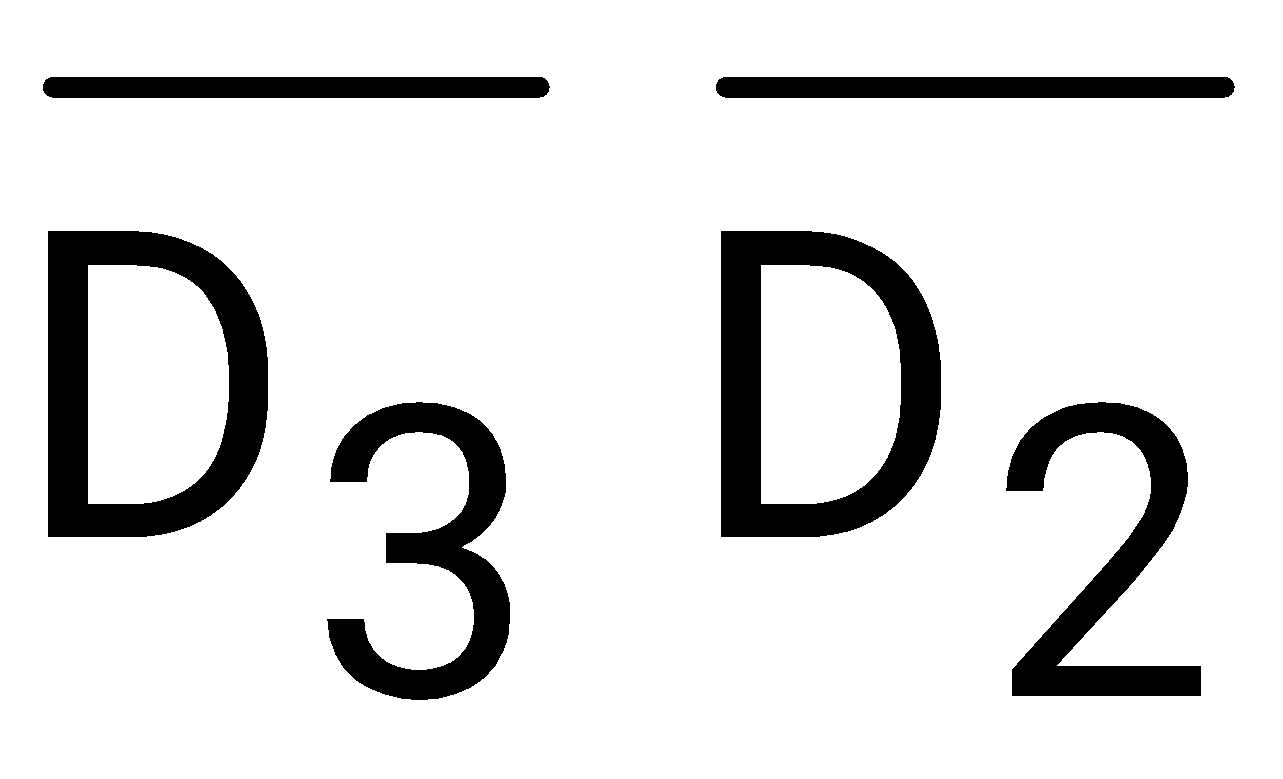

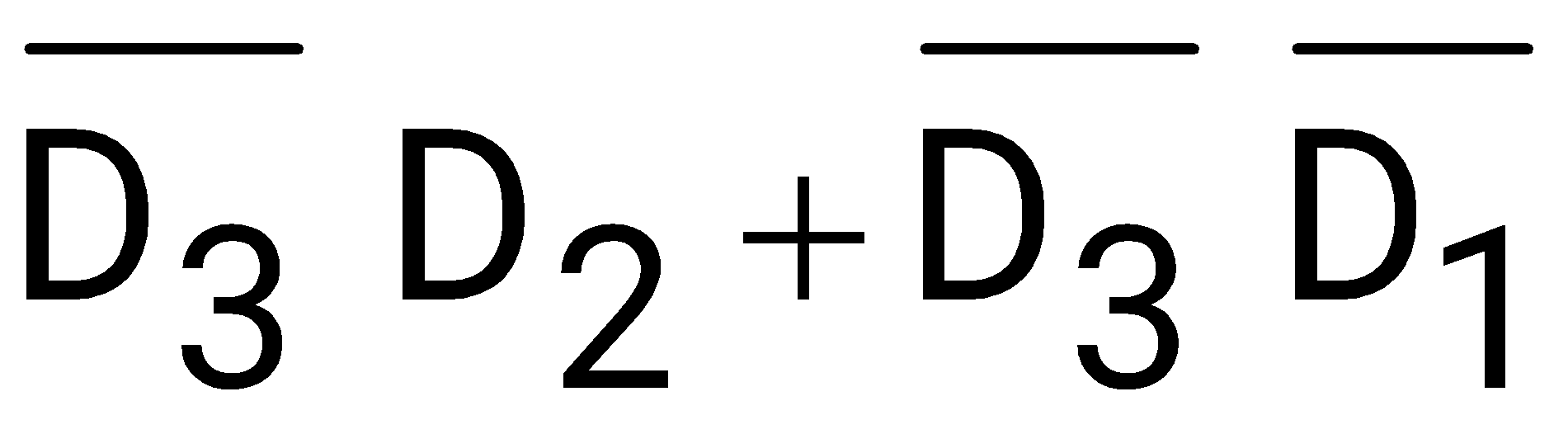

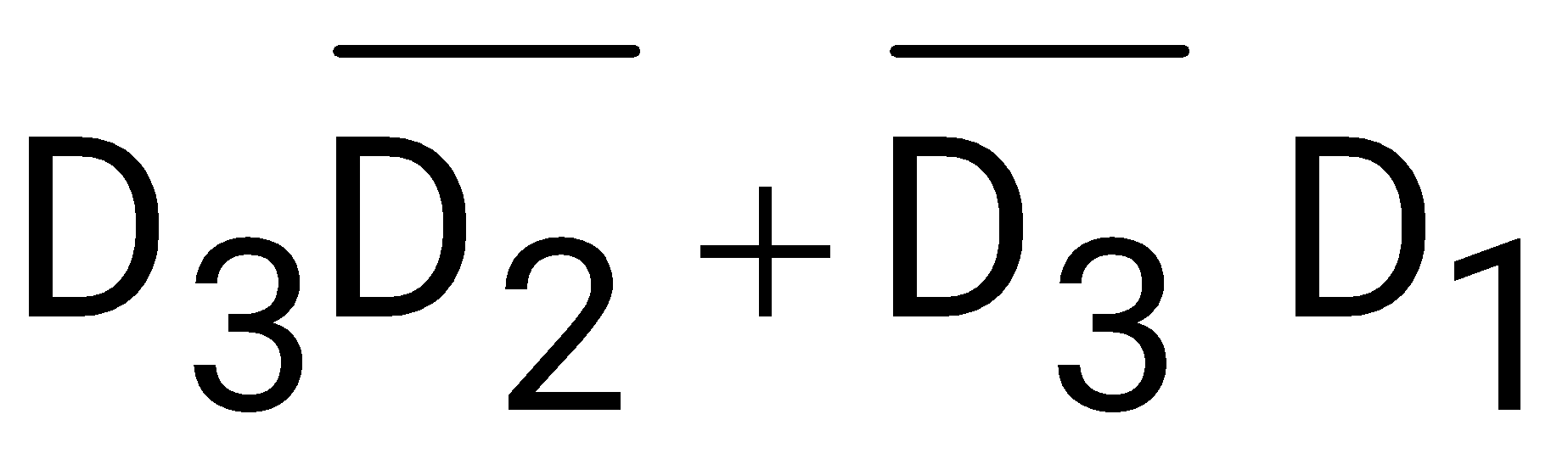

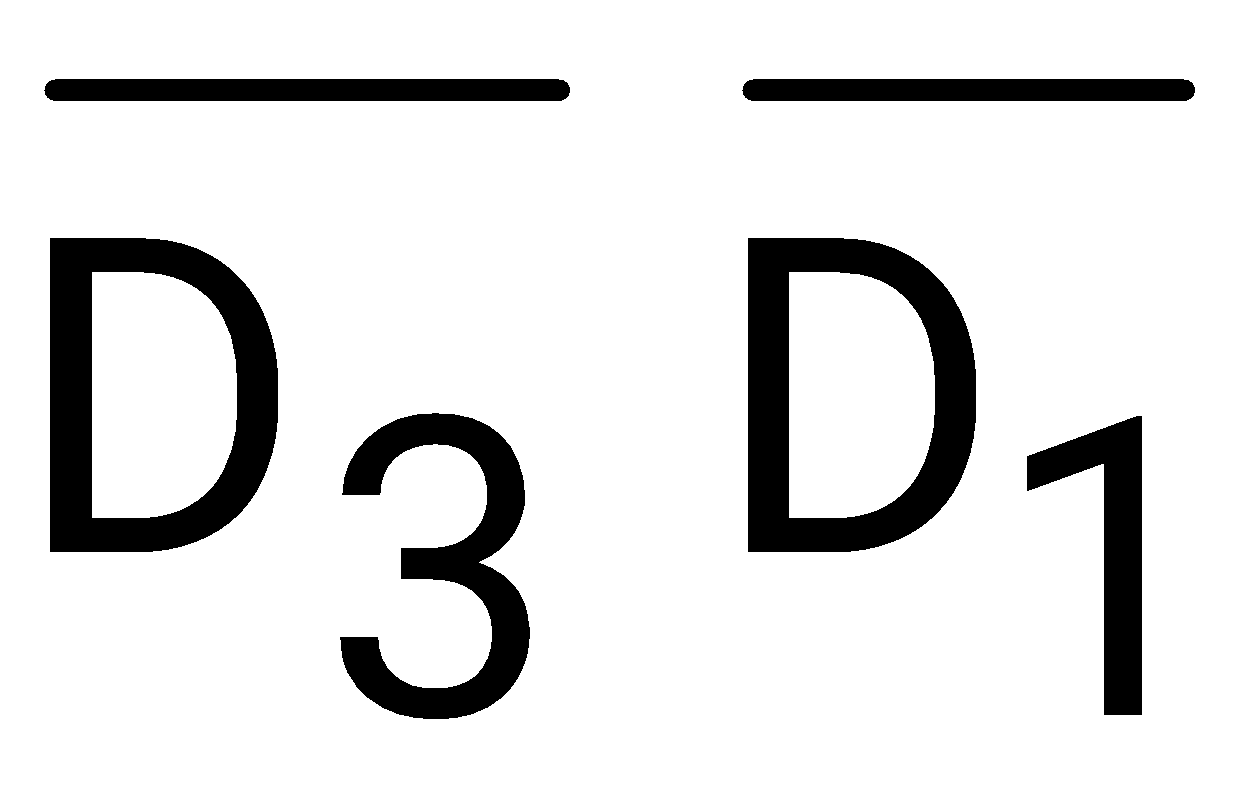

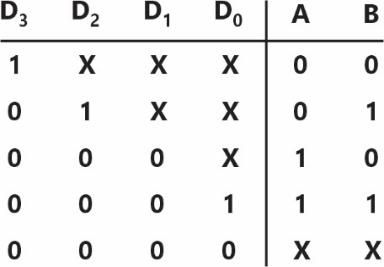

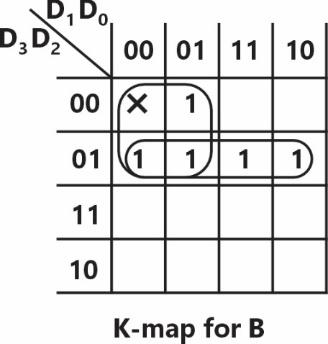

A 4-bit priority encoder has inputs , and in descending order of priority. The two-bit output is generated as , and 11 corresponding to inputs , and , respectively. The Boolean expression of the output bit is_____.

B = 1 for second row 01xx which means 4 minterms (0100, 0101, 0110, 0111 i.e. 4,5,6,7)

B = 1 for third row 000x which means two minterms (0000, 0001)

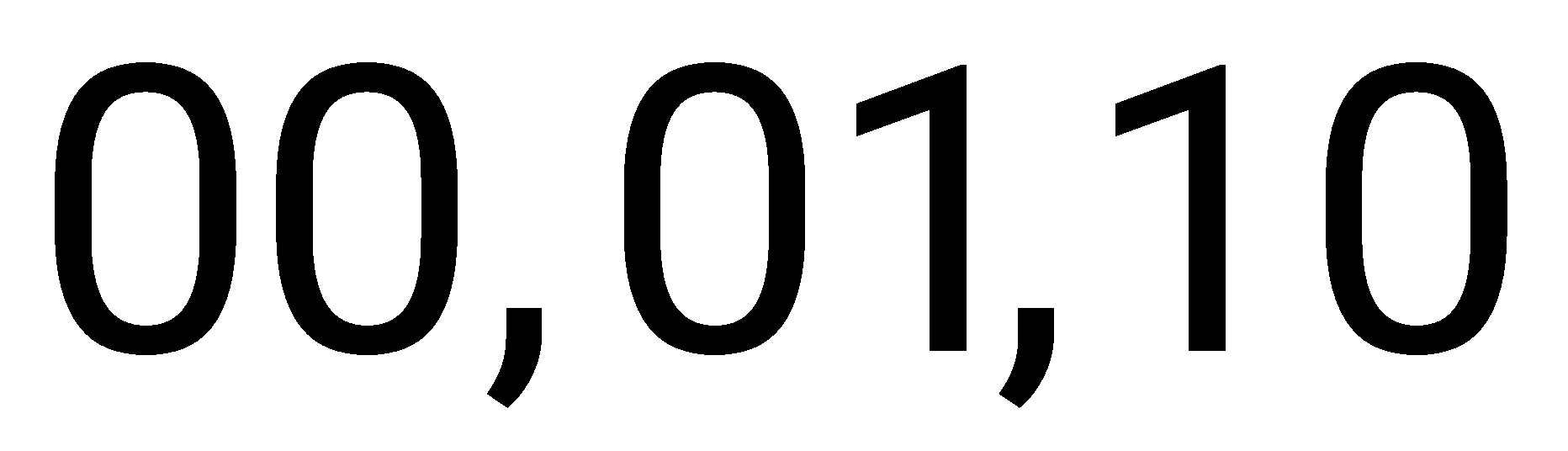

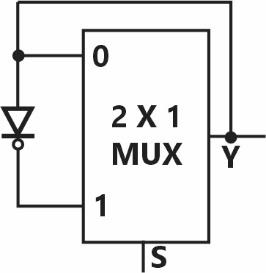

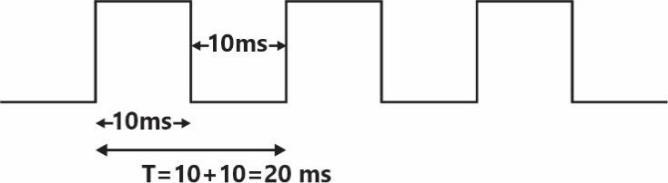

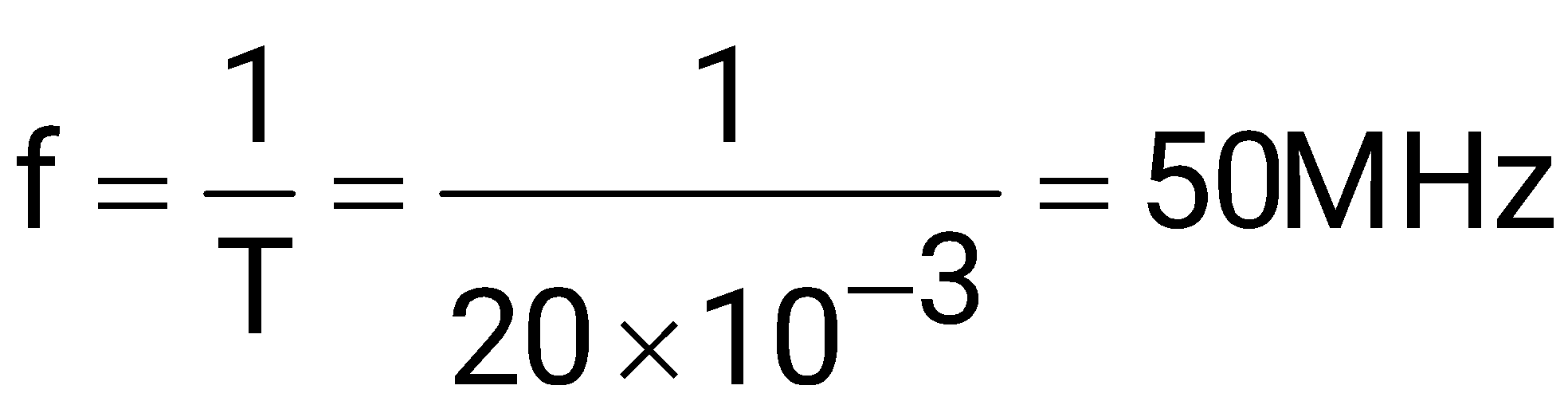

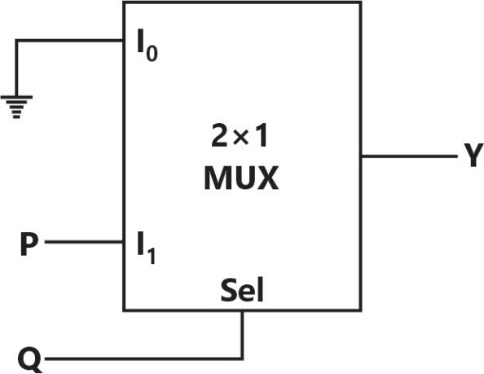

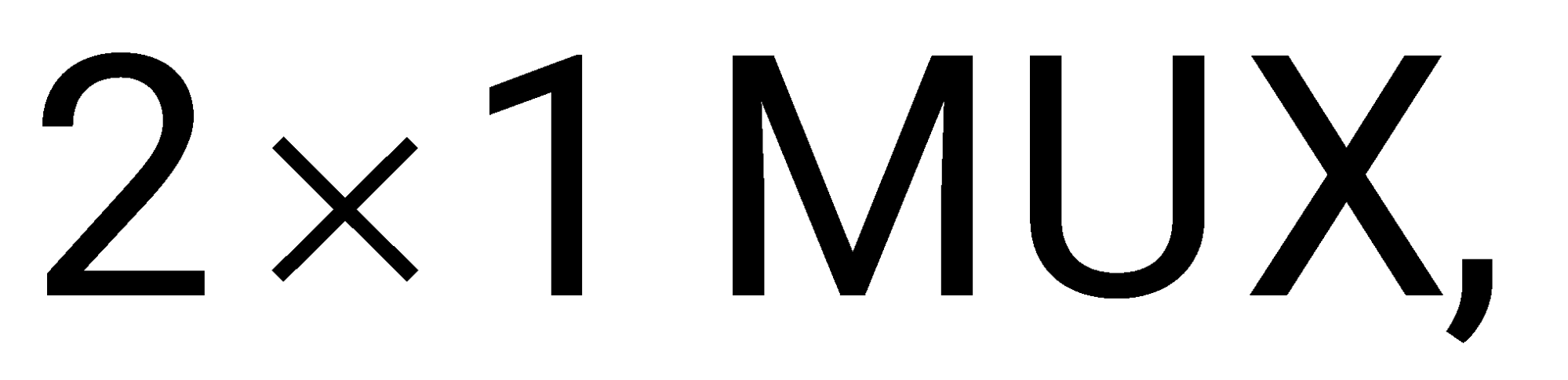

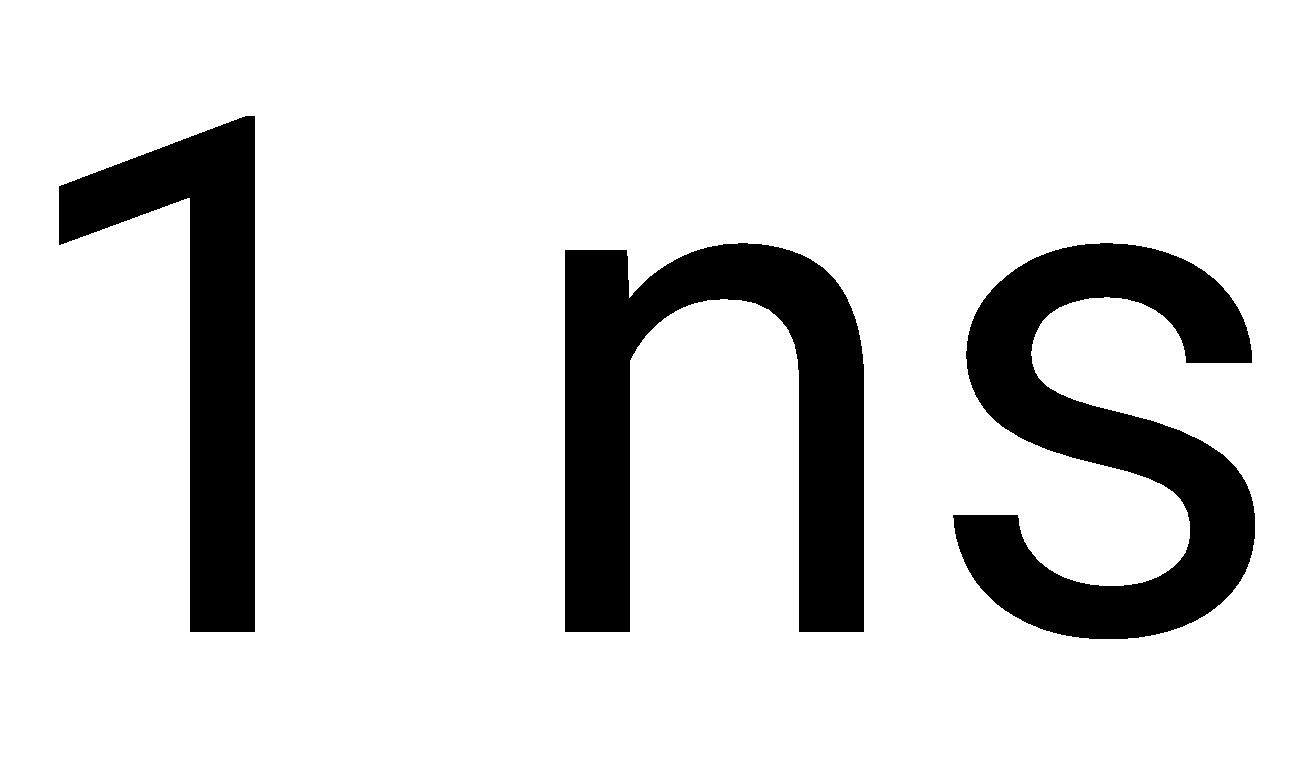

The propagation delay of the MUX shown in the circuit is 10 ns. Consider the propagation delay of the inverter as .

If is set to 1 then the output is________.

As

This means that circuit is operating in toggle mode and hence the output inverts itself every time after propagation delay.

If initially, wave form

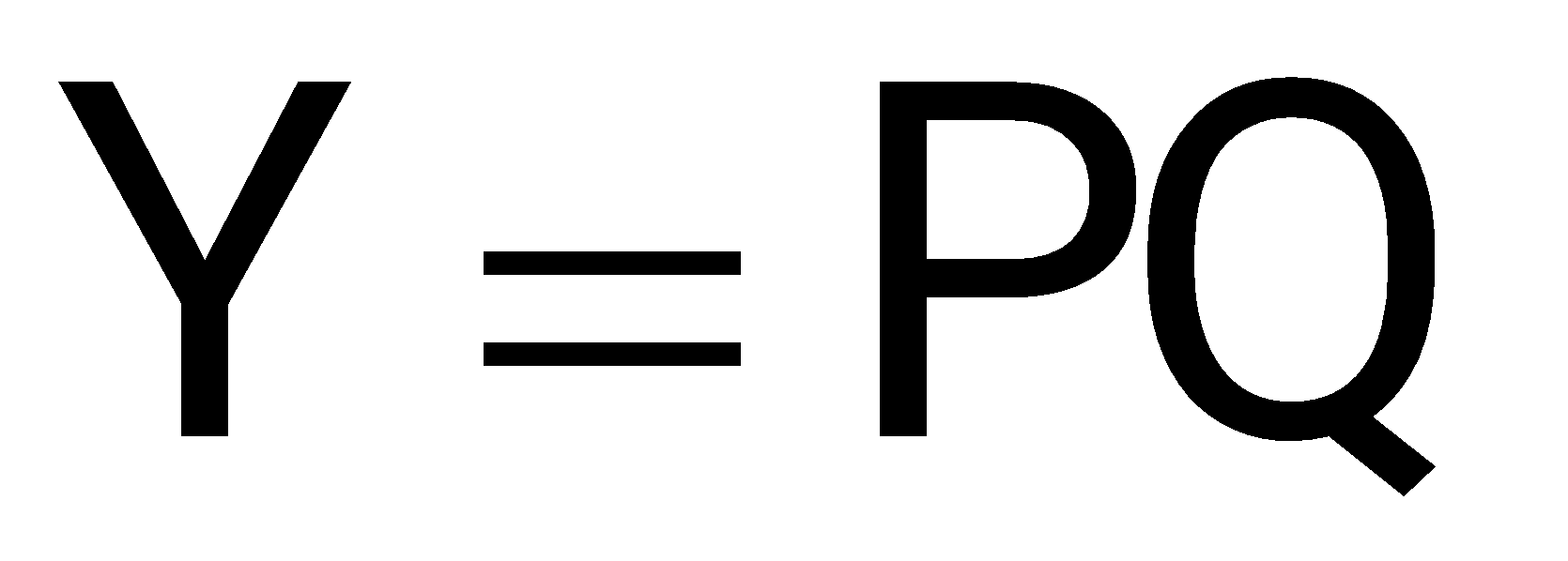

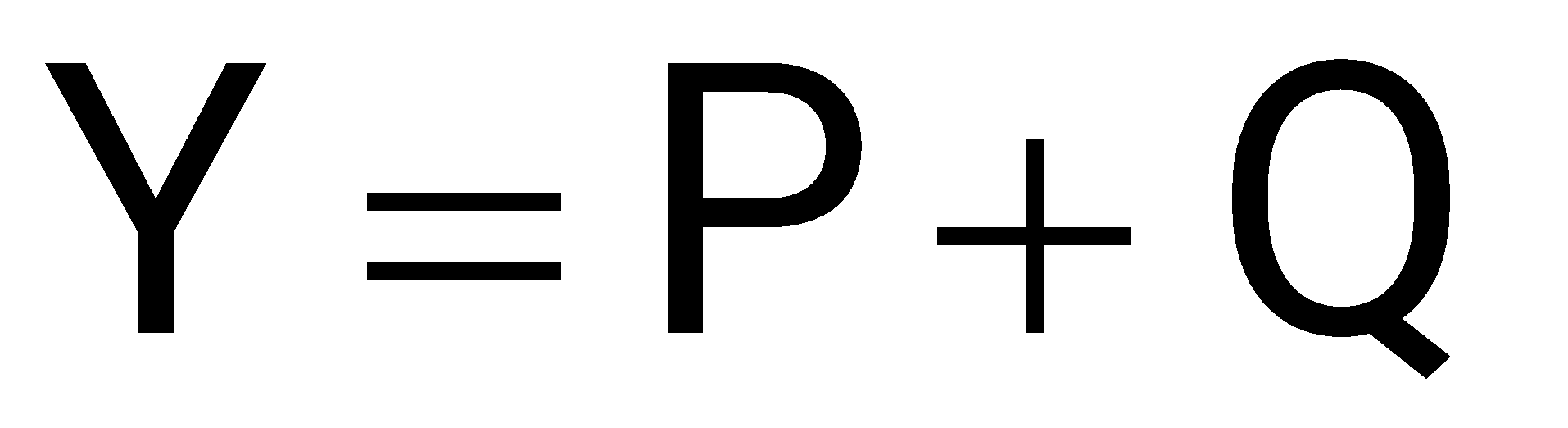

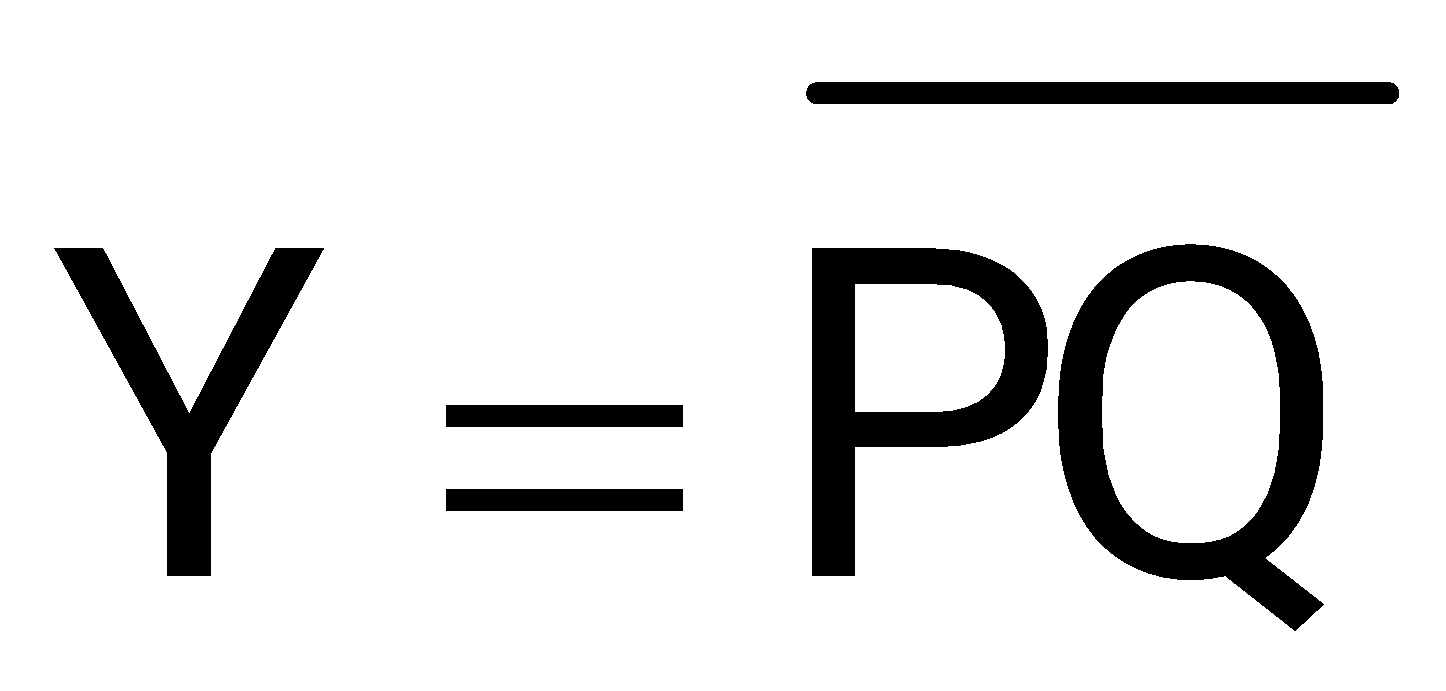

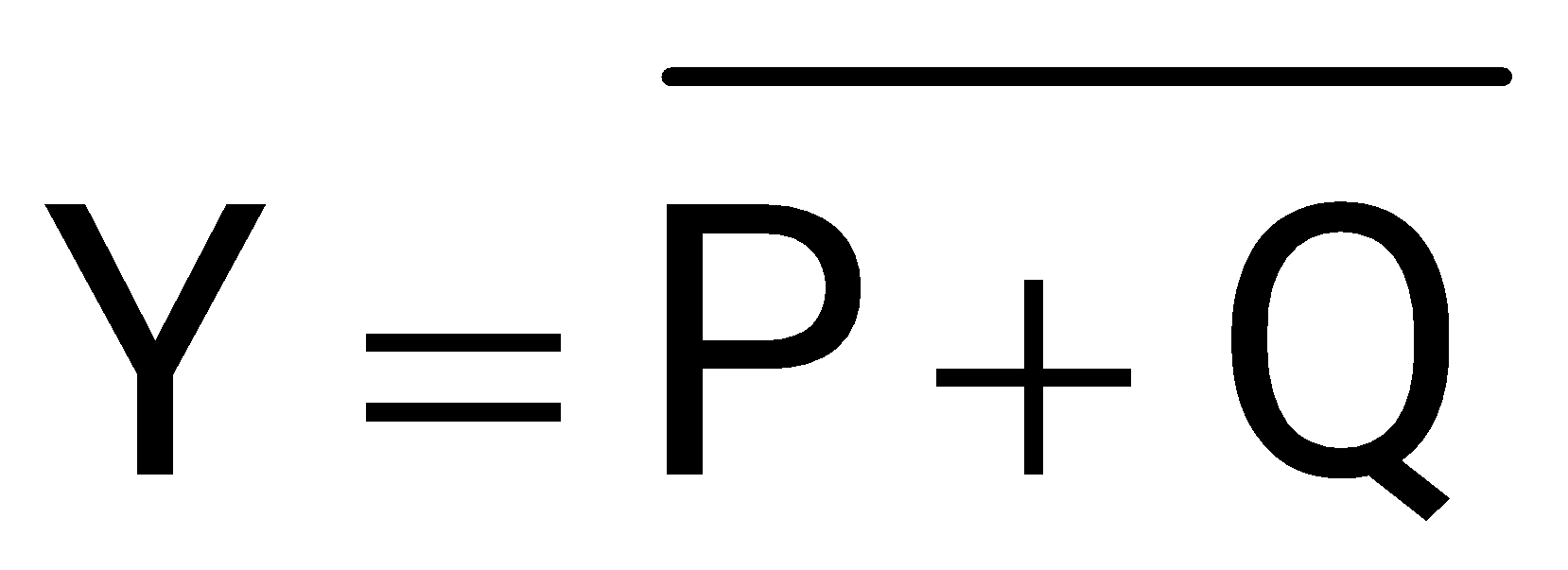

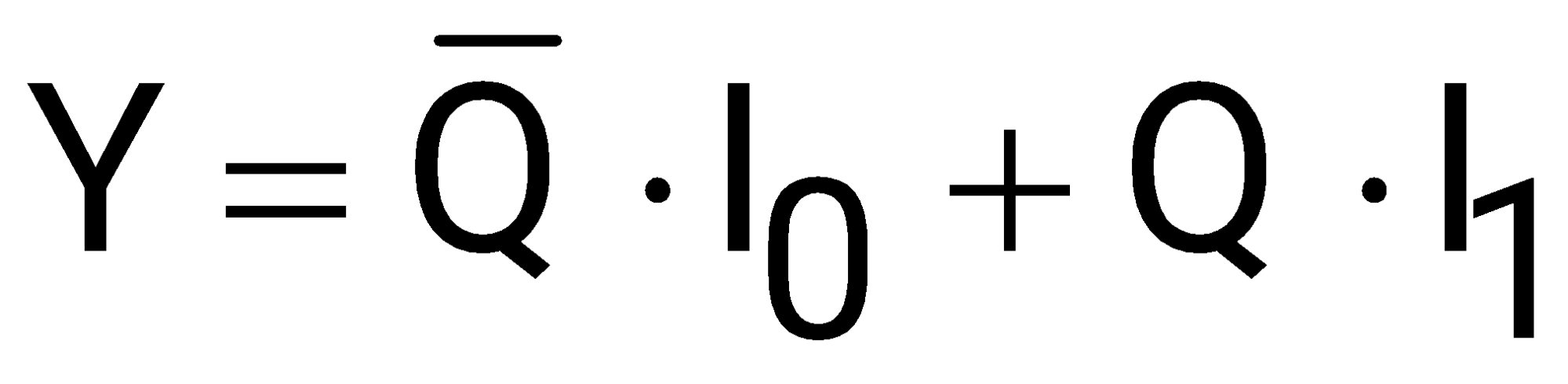

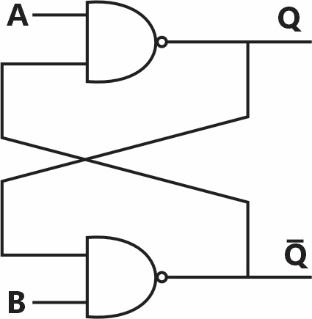

In the circuit shown below, and are the inputs. The logical function realized by the circuit shown below is

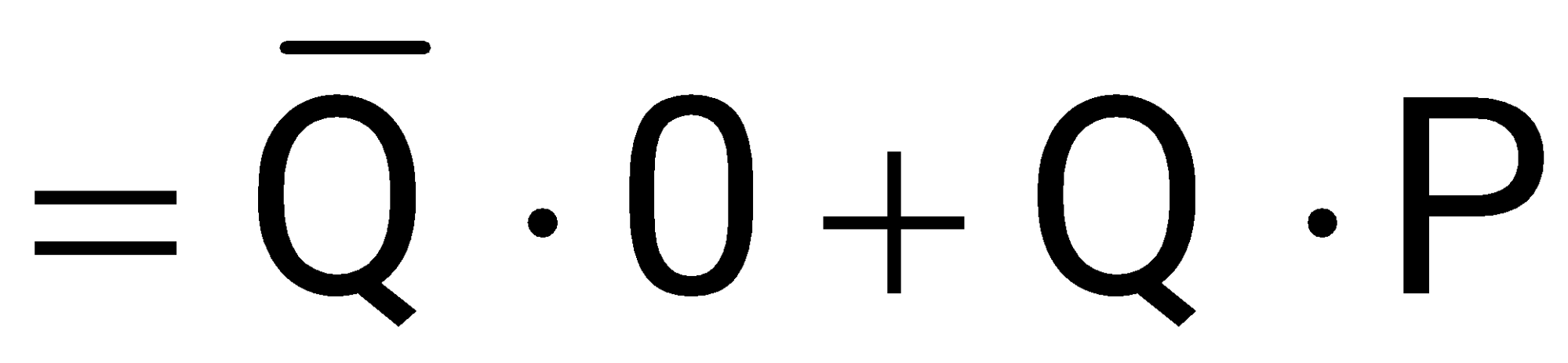

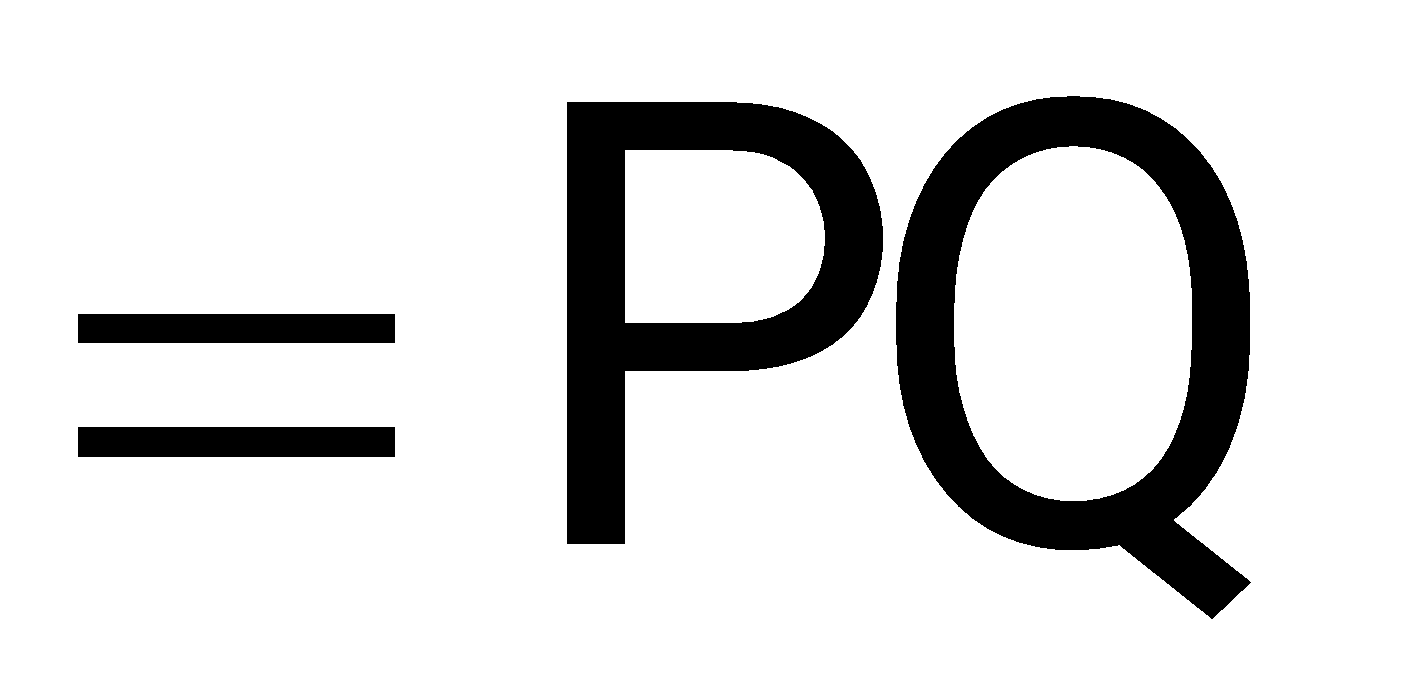

From the Y given

Output,

is 0, is 1 Put it in the equation of output

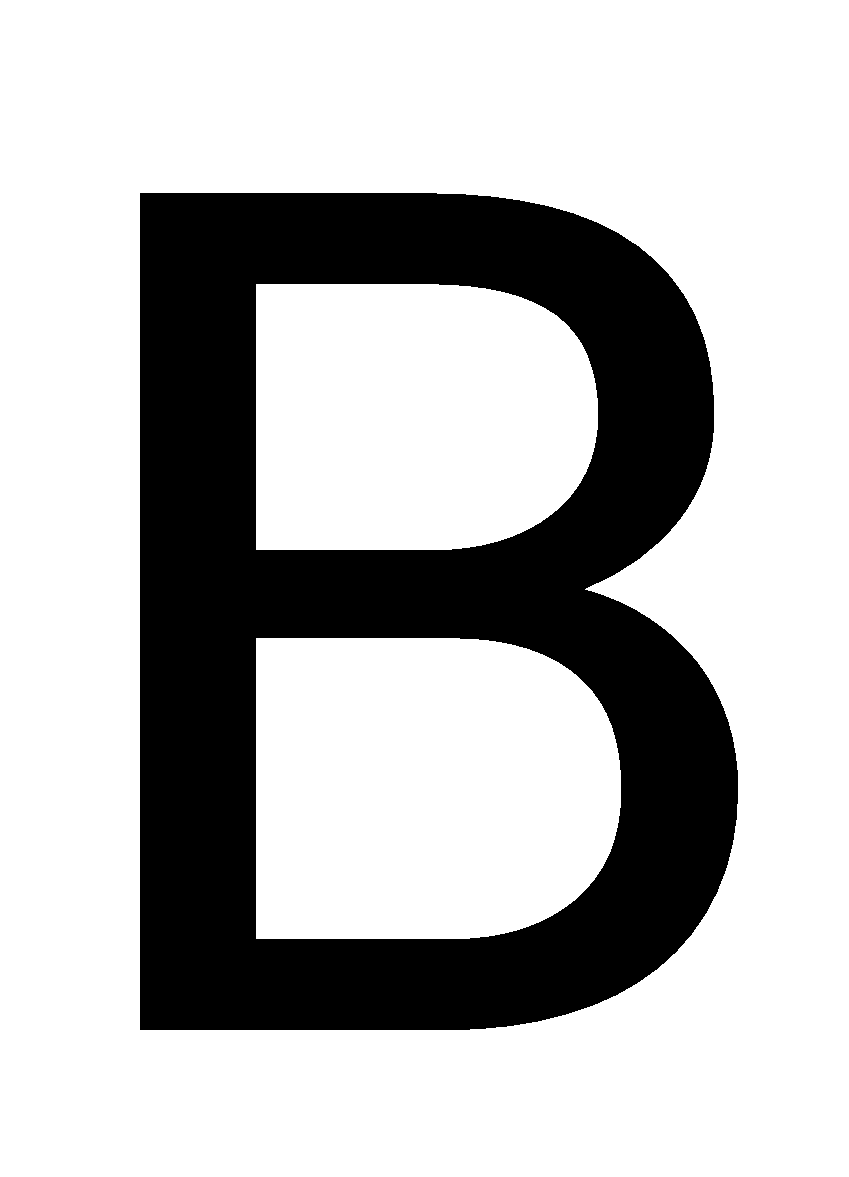

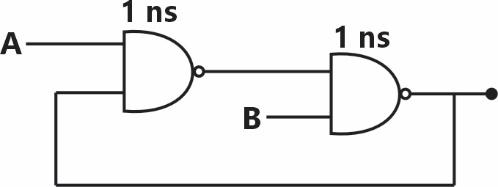

For the circuit shown below, the propagation delay of each NAND gate is . The critical path delay, in ns, is ________ (rounded off to the nearest integer).

Redrawing the circuit to simplify is as shown.

The critical path delay