Digital Electronics

Sequential Circuits

Practice questions from Sequential Circuits.

5

Total0

Attempted0

Correct0

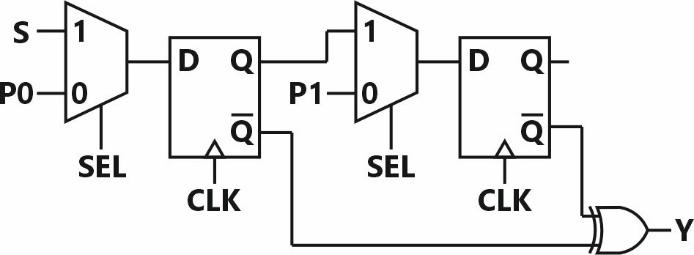

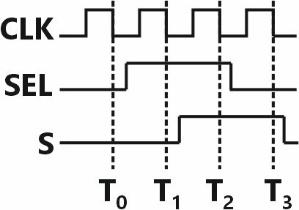

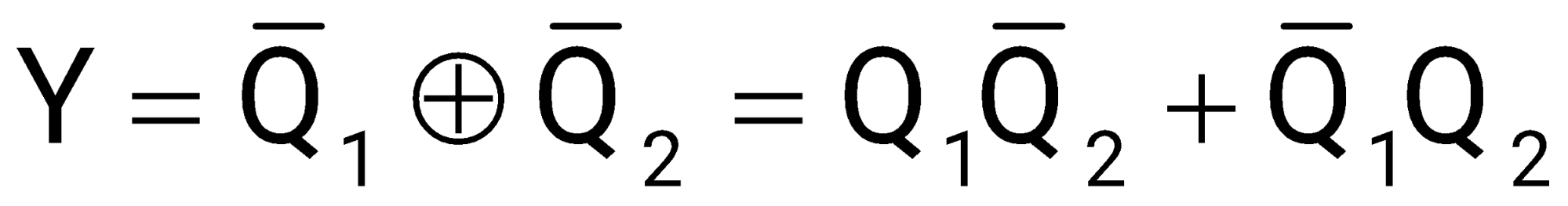

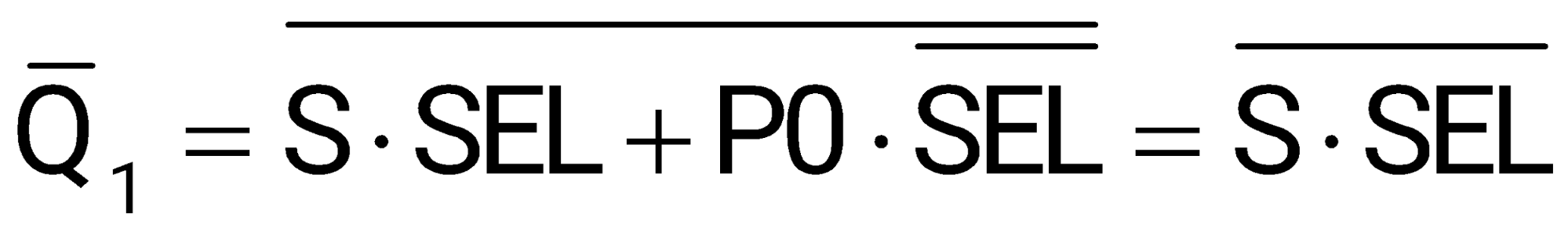

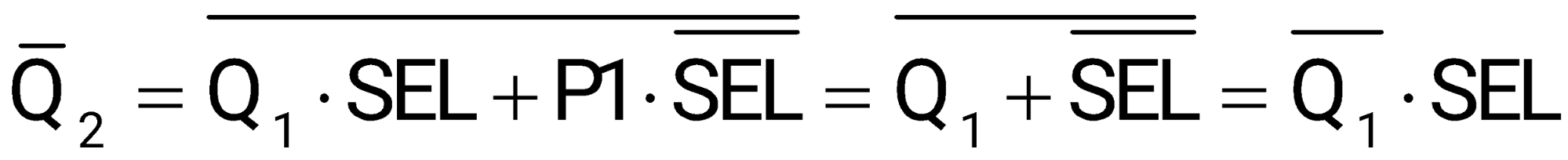

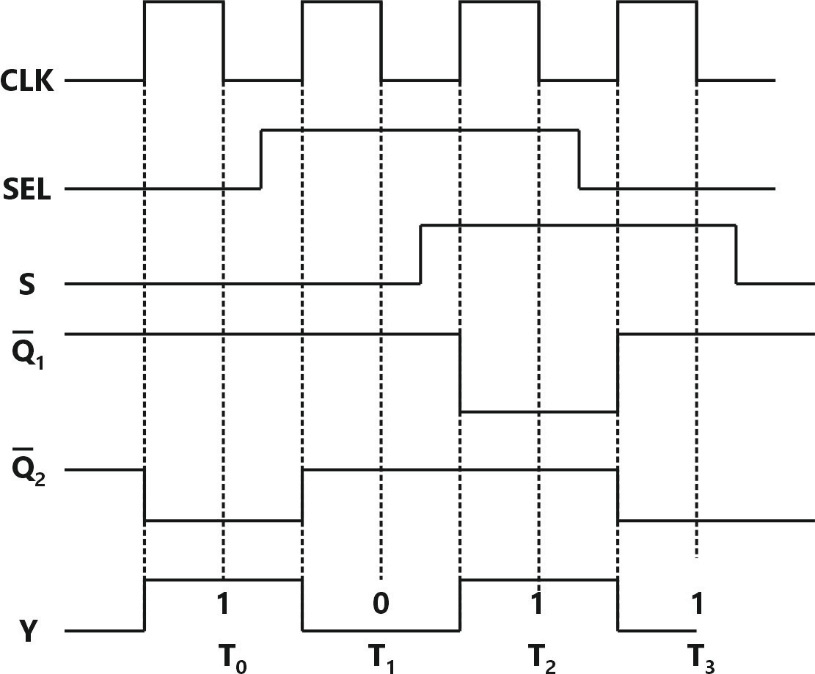

IncorrectA positive-edge-triggered sequential circuit is shown below. There are no timing violations in the circuit. Input is set to logic ' 0 ' and is set to logic ' 1 ' at all times. The timing diagram of the inputs and are also shown below.

The sequence of output from time to is ________.

Label left as and right

Y=1011

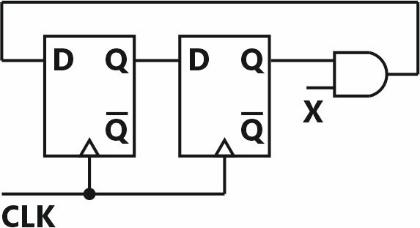

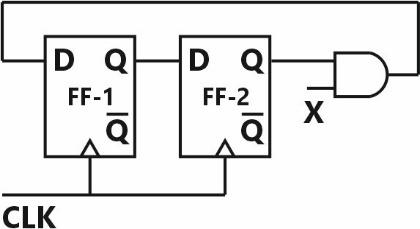

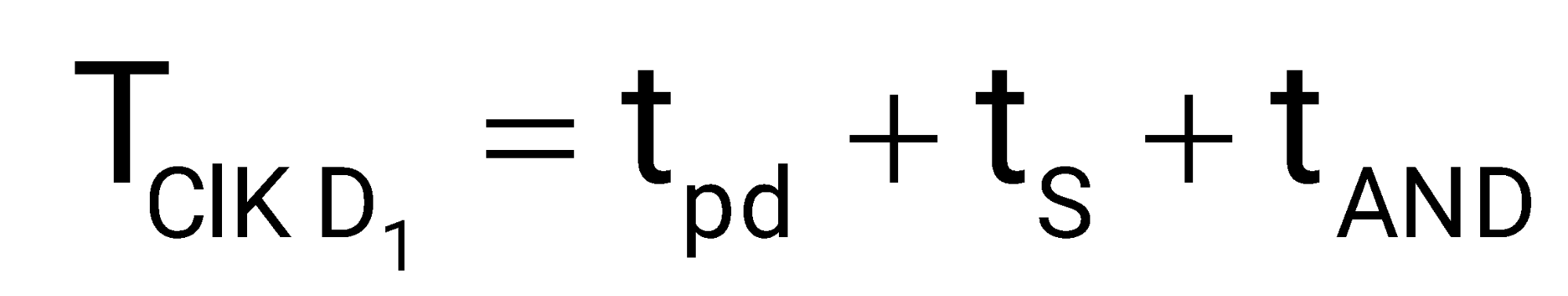

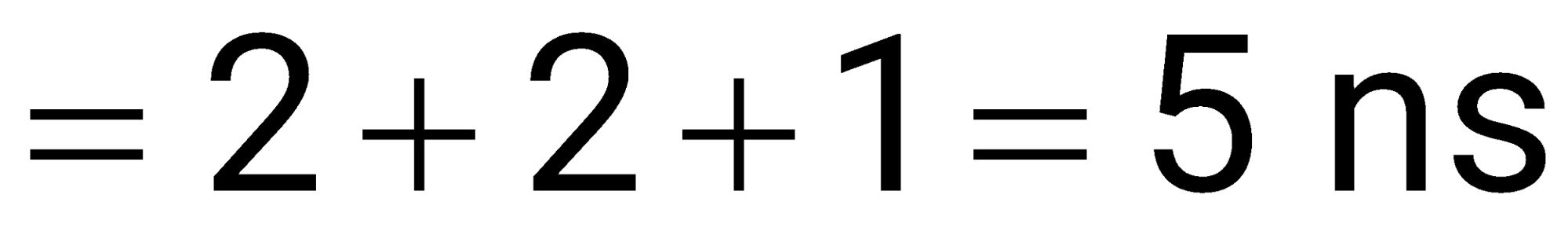

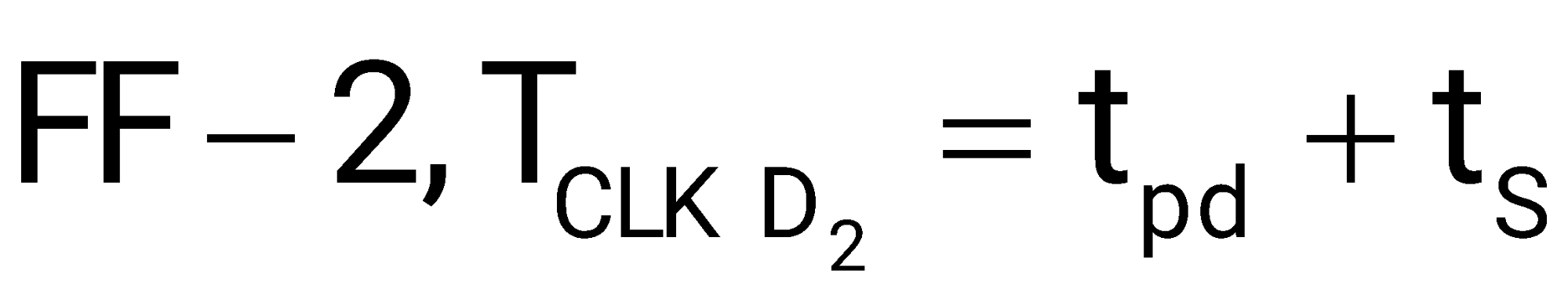

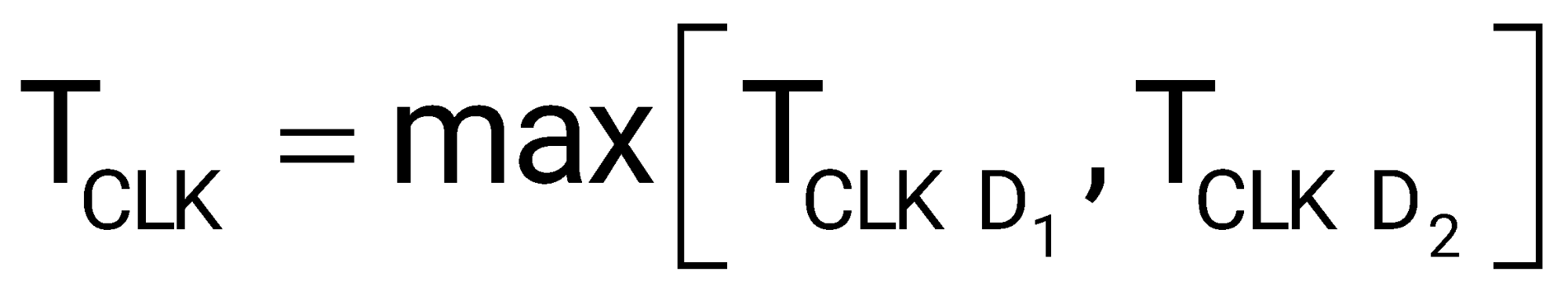

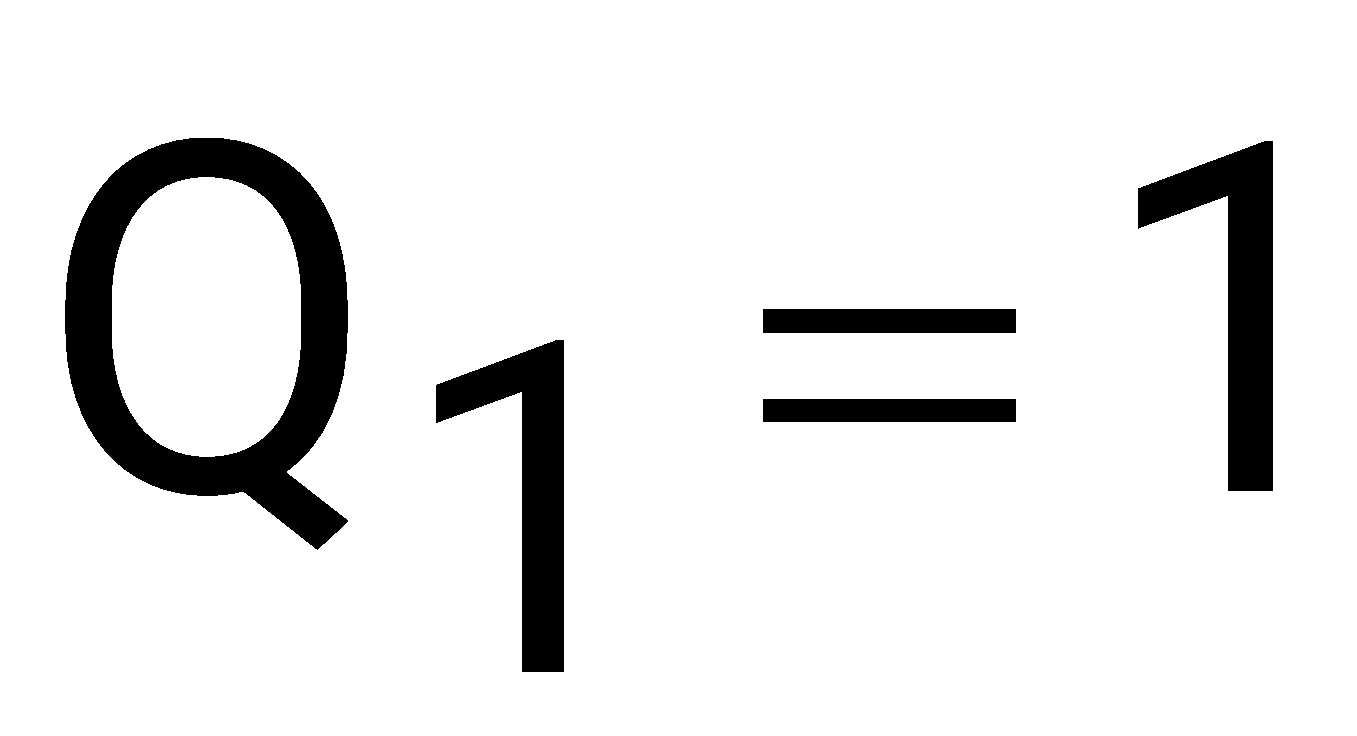

In the circuit shown below, the AND gate has a propagation delay of 1 ns. The edge-triggered flip-flops have a set-up time of 2 ns, a hold-time of 0 ns, and a clock-to-Q delay of 2 ns.

The maximum clock frequency (in MHz, rounded off to the nearest integer) such that there are no setup violations is ________

Given:

For FF, set-up time

For FF-1,

For

Time required for clock,

Maximum clock frequency,

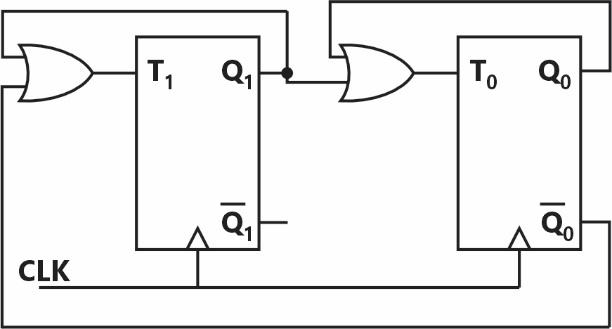

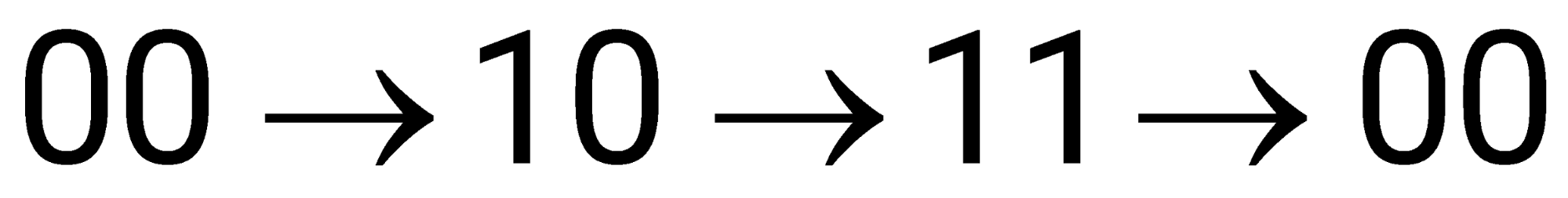

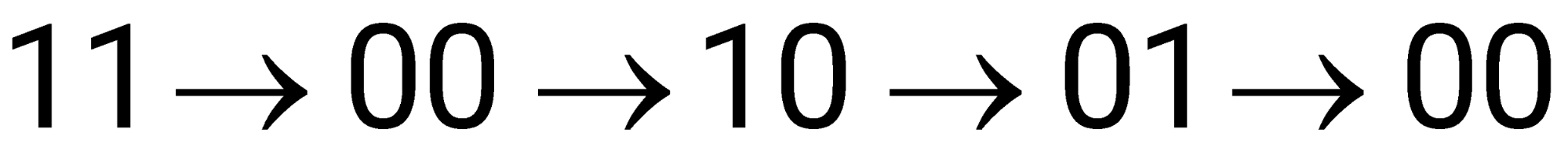

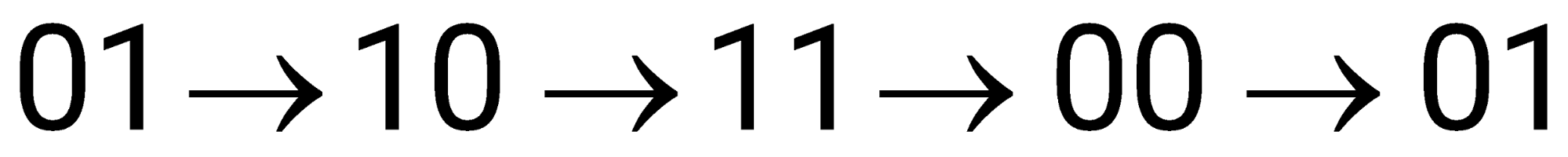

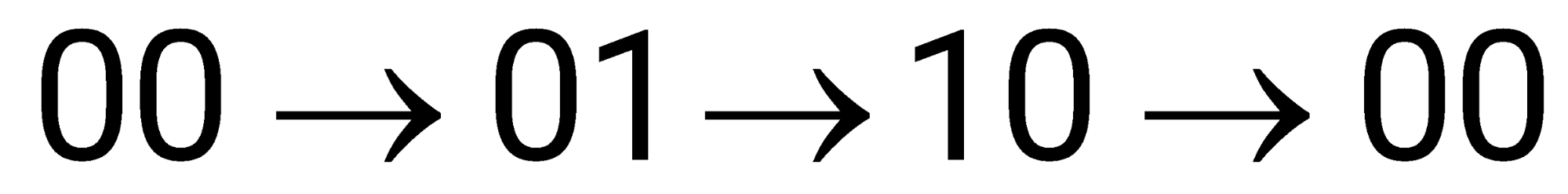

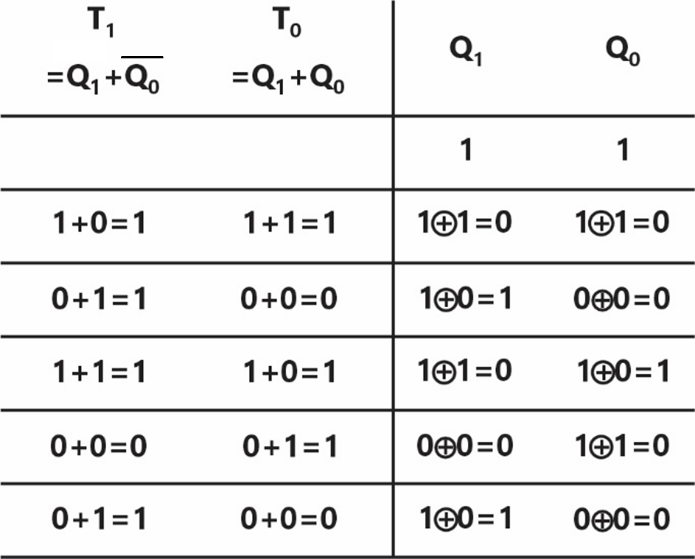

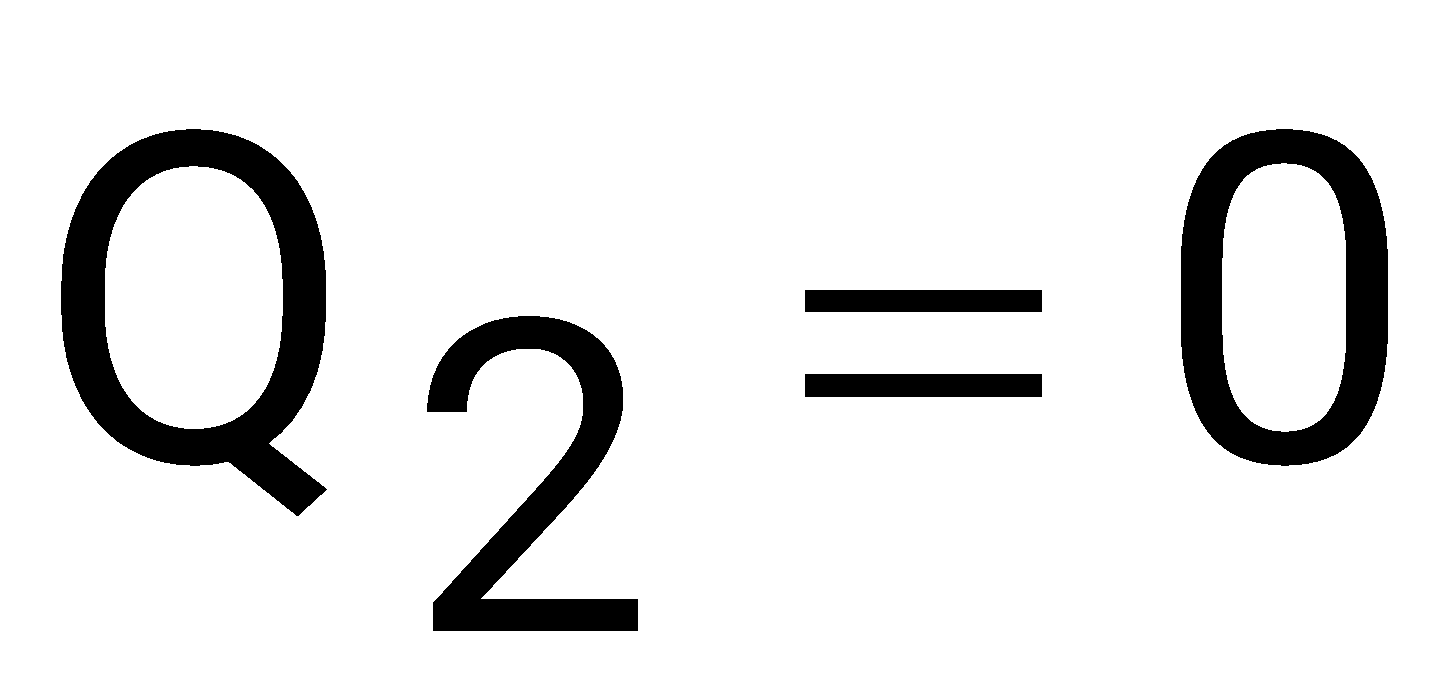

The sequence of states of the given synchronous sequential circuit is ________.

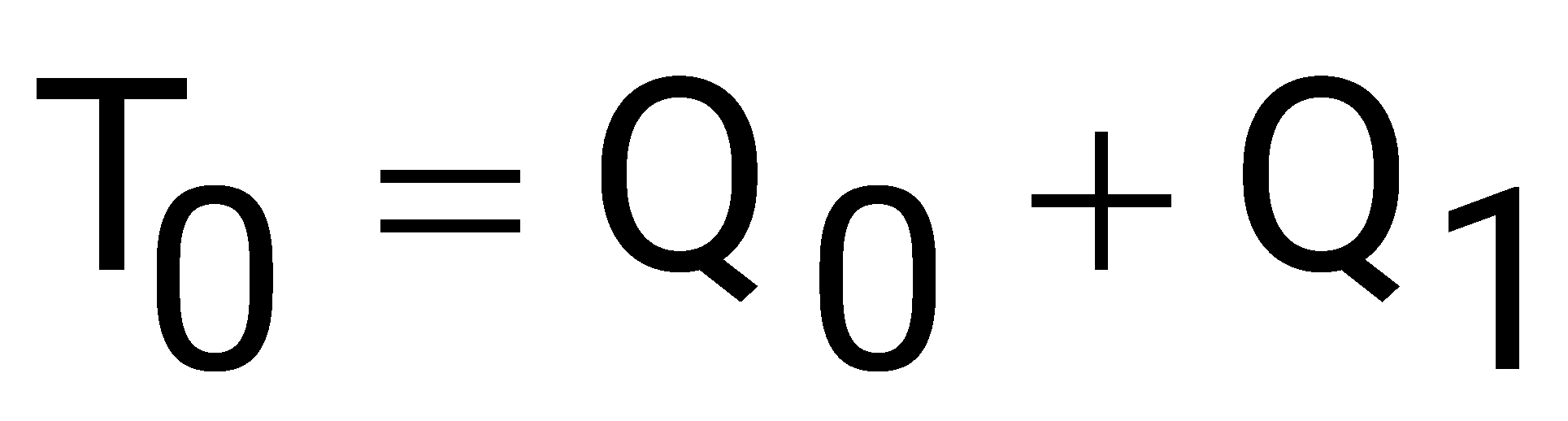

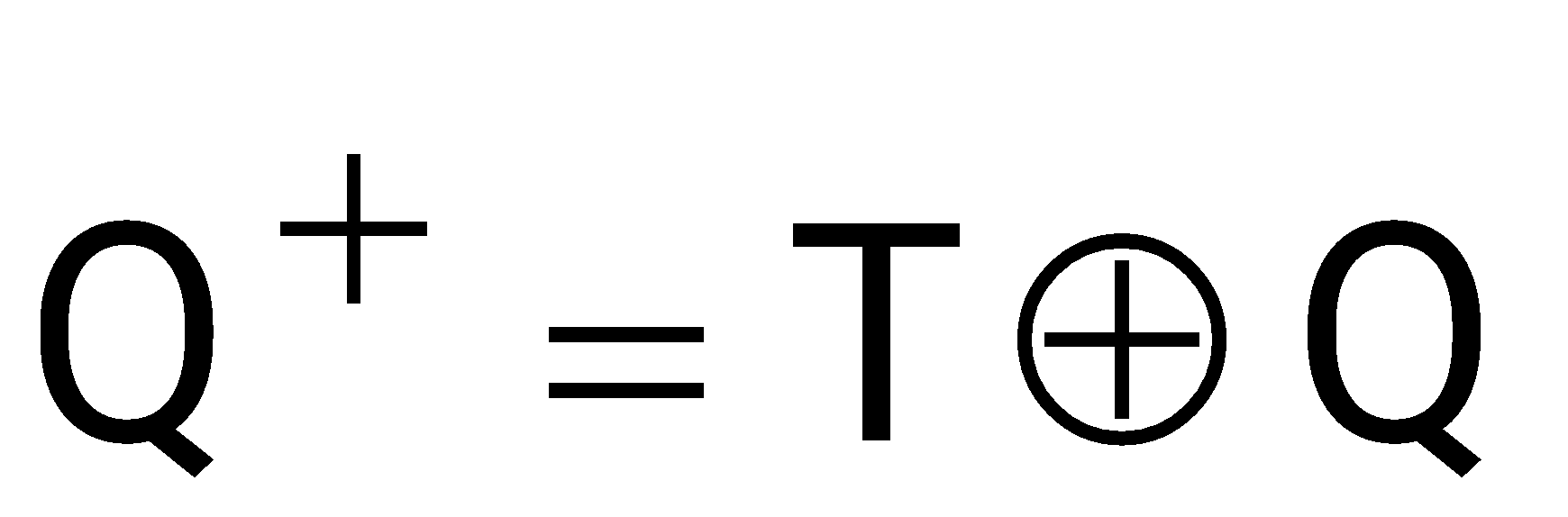

Based on the logic circuit given in the question,

and

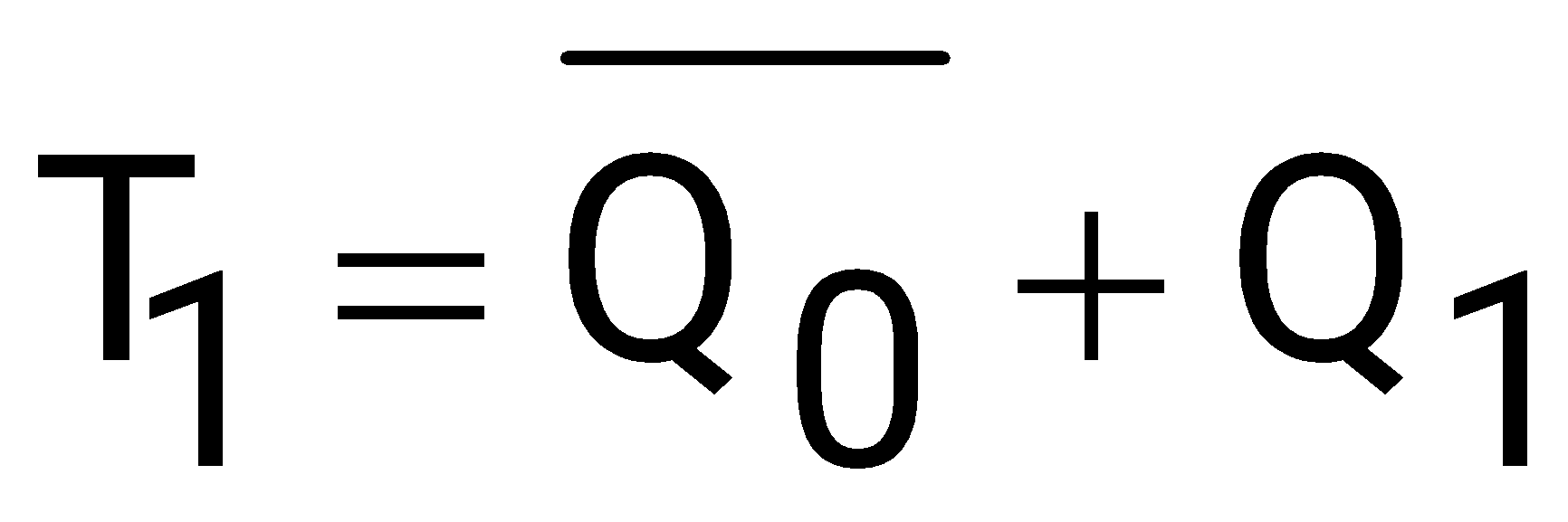

As per the characteristic equation of T-flipflop

So,

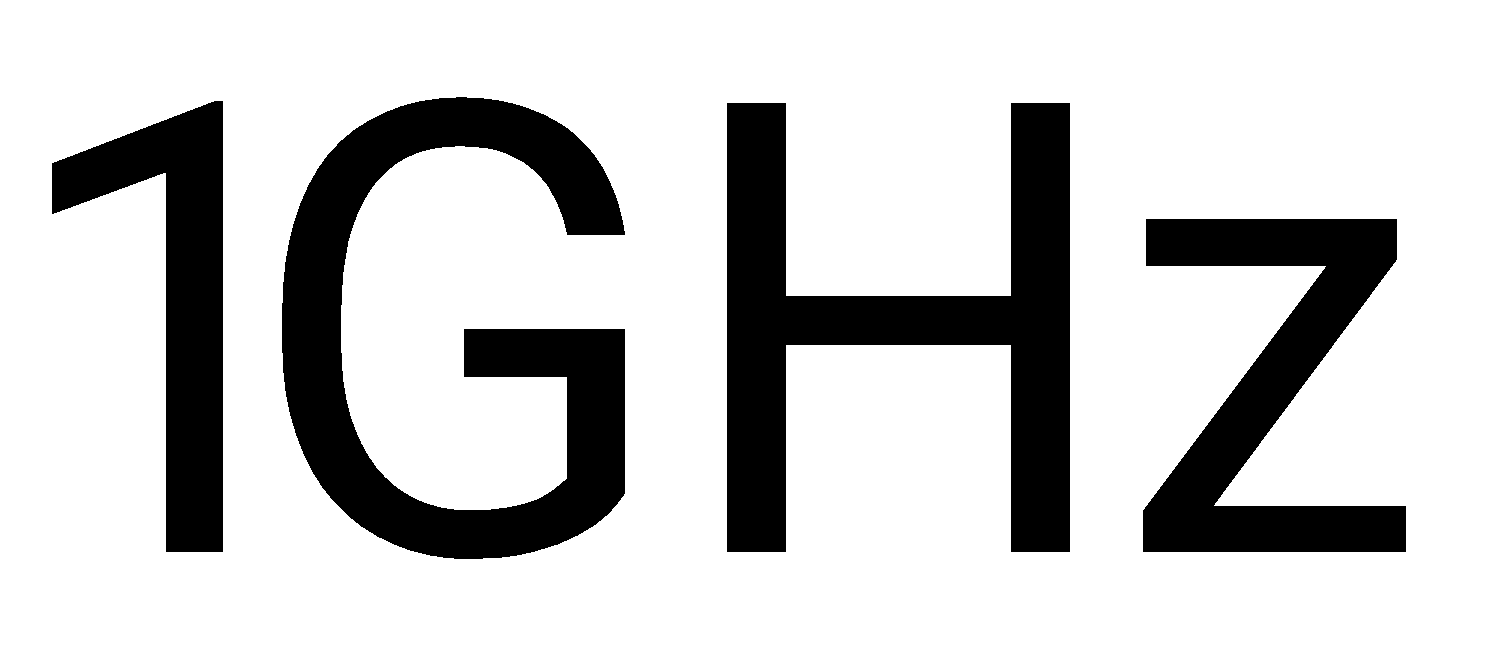

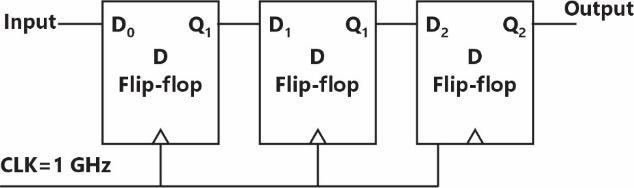

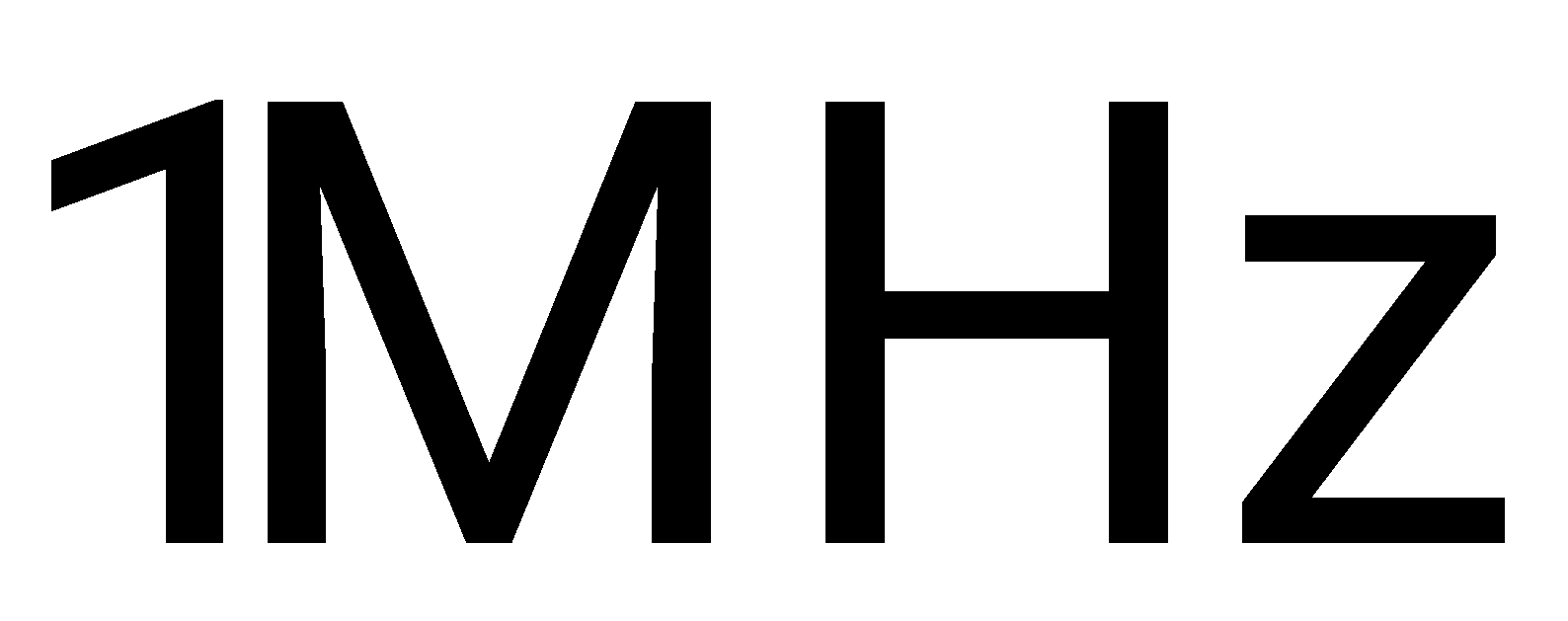

The synchronous sequential circuit shown below works at a clock frequency of . The throughput, in bits/s, and the latency, in ns, respectively, are

The given circuit is a type of serial input serial output.

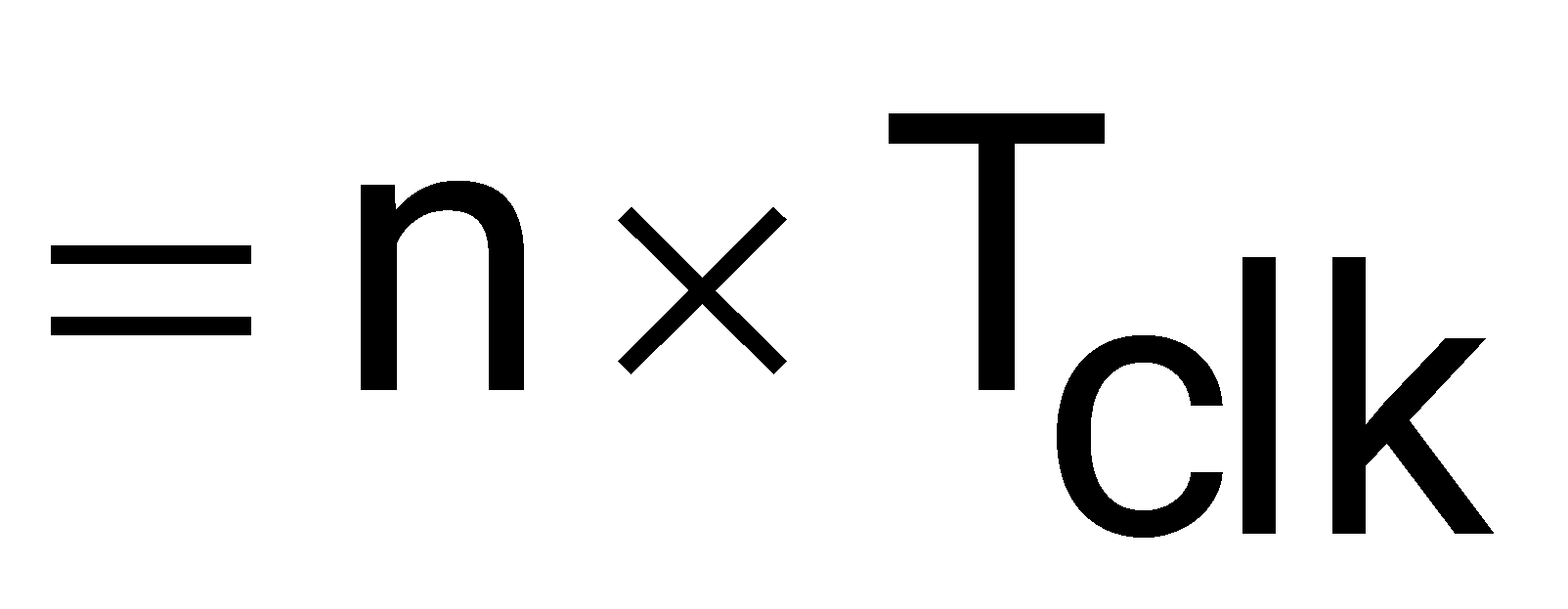

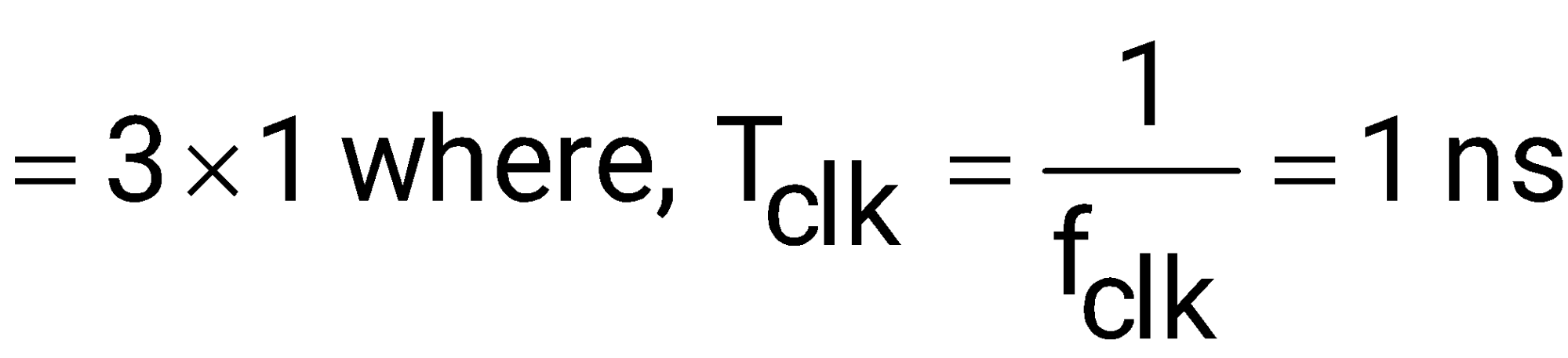

The latency is given by the formula.. Latency where, number of flip flops

The Throughput is given by the formula. Throughput= Number of bits/sec

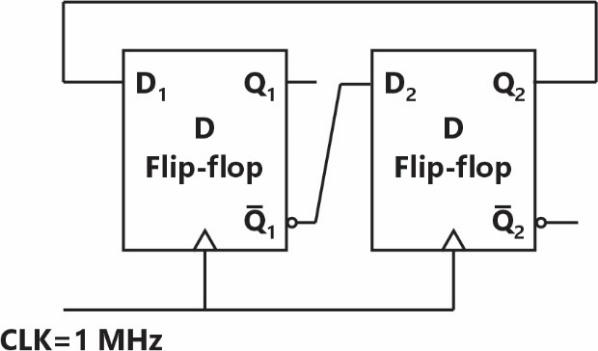

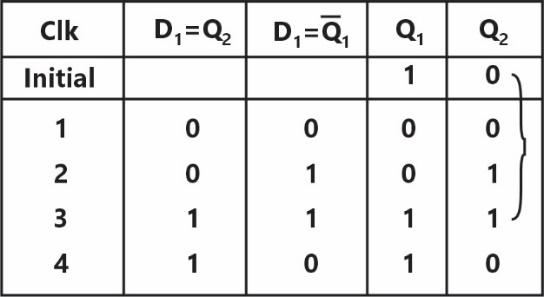

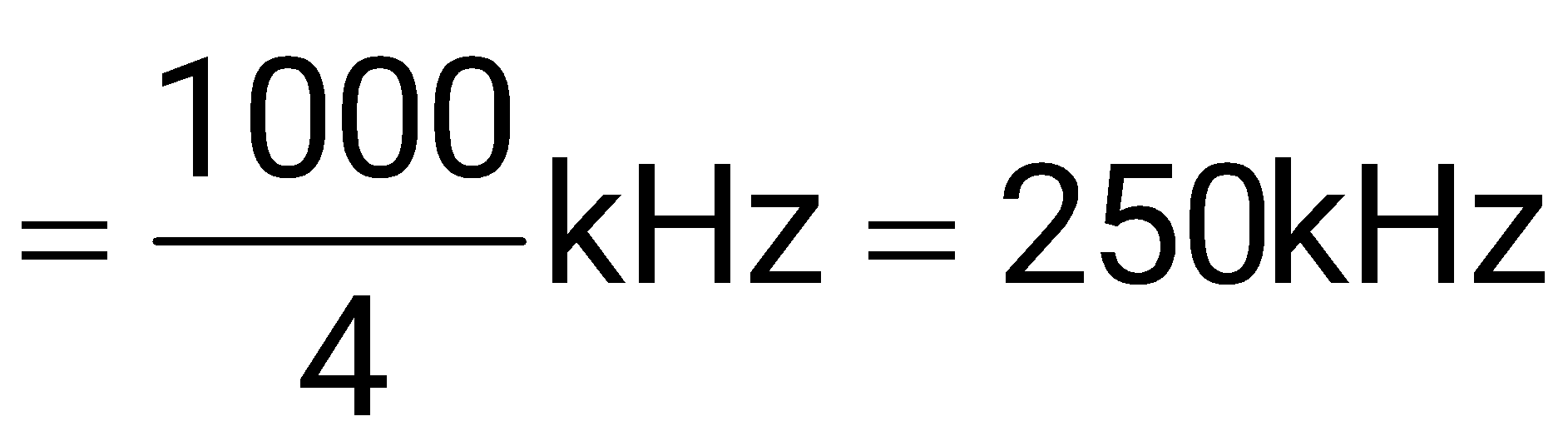

In a given sequential circuit, initial states are and . For a clock frequency of , the frequency of signal in , is ________. (rounded off to the nearest integer).

Given, initial states, and

Clock frequency,

As after 4 CLK pulses the sequential circuit repeats itself so its MOD no. 4.

The frequency of signal