Analog Electronics

OP-AMP and its Applications

Practice questions from OP-AMP and its Applications.

4

Total0

Attempted0

Correct0

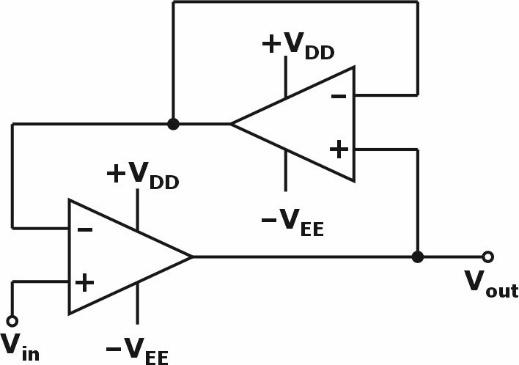

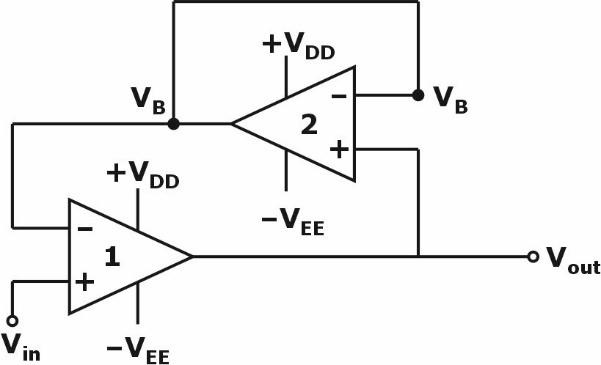

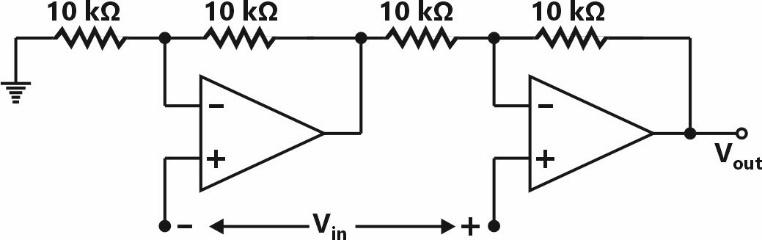

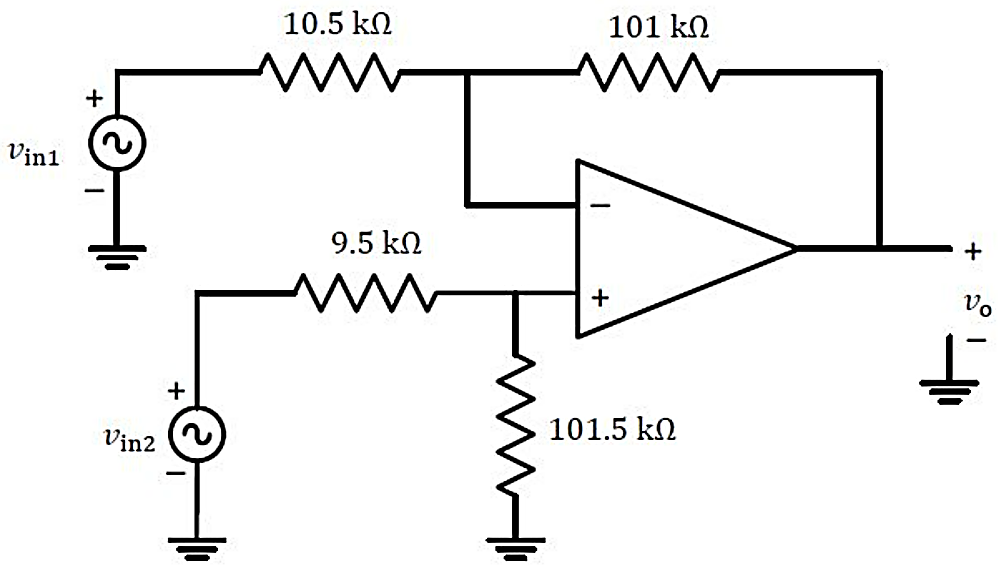

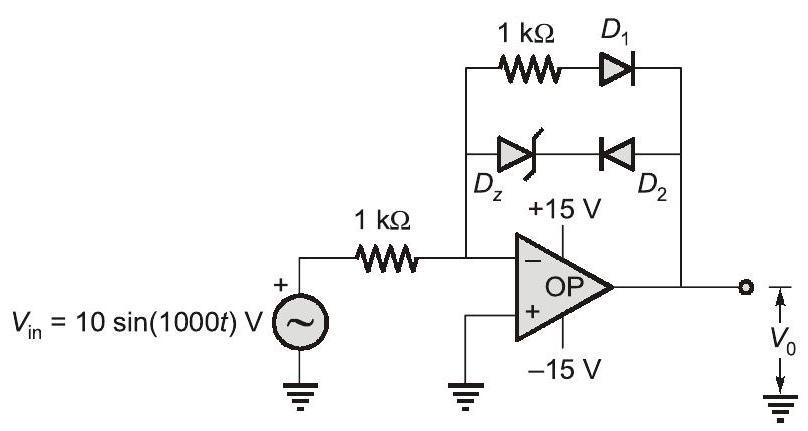

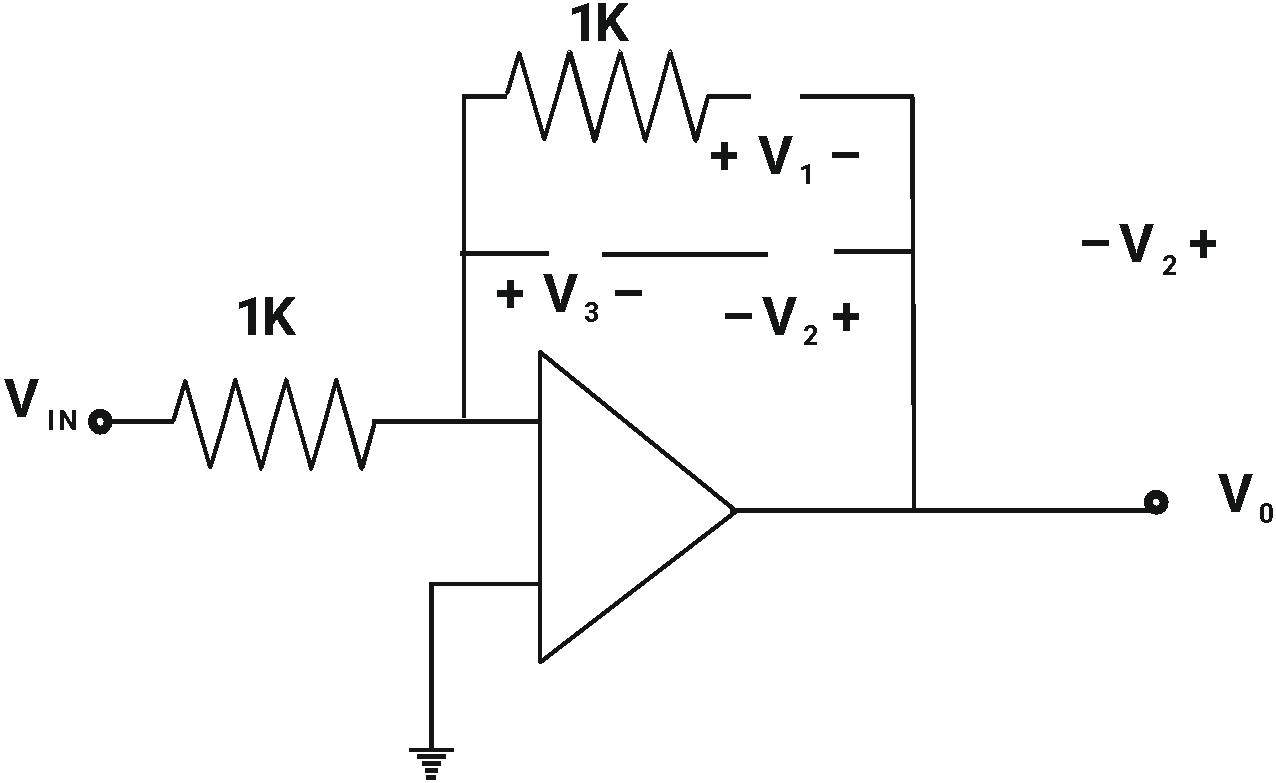

IncorrectAssuming ideal op-amps, the circuit represents a

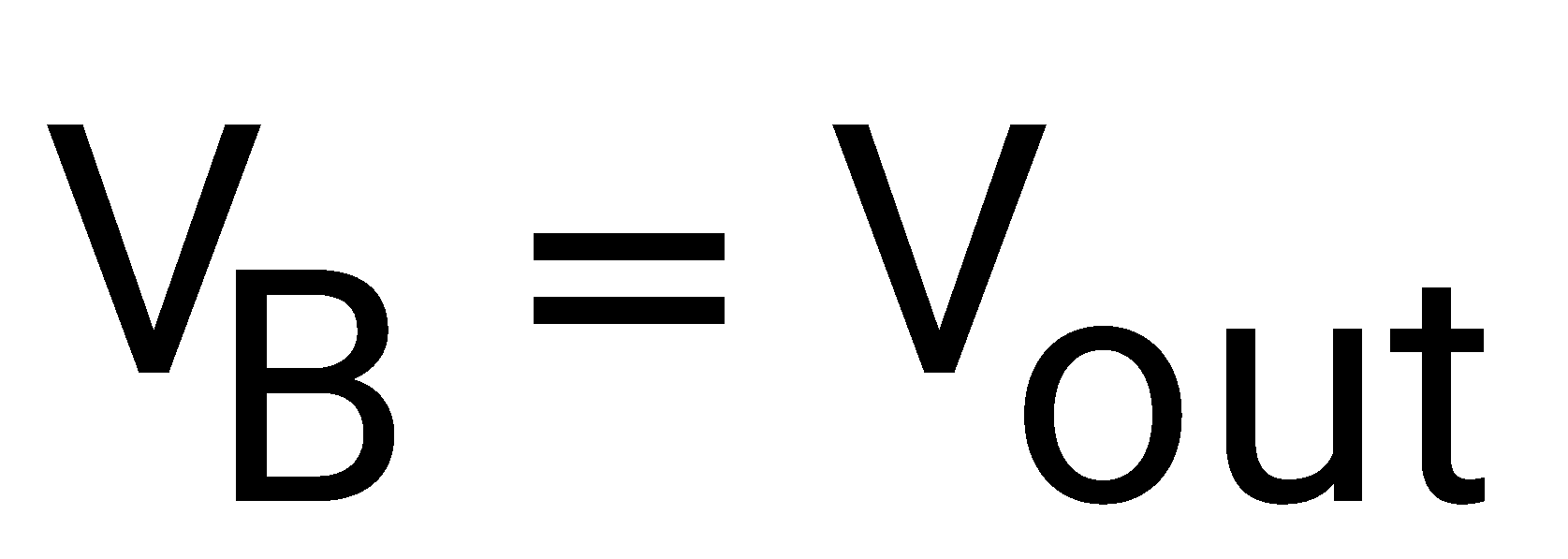

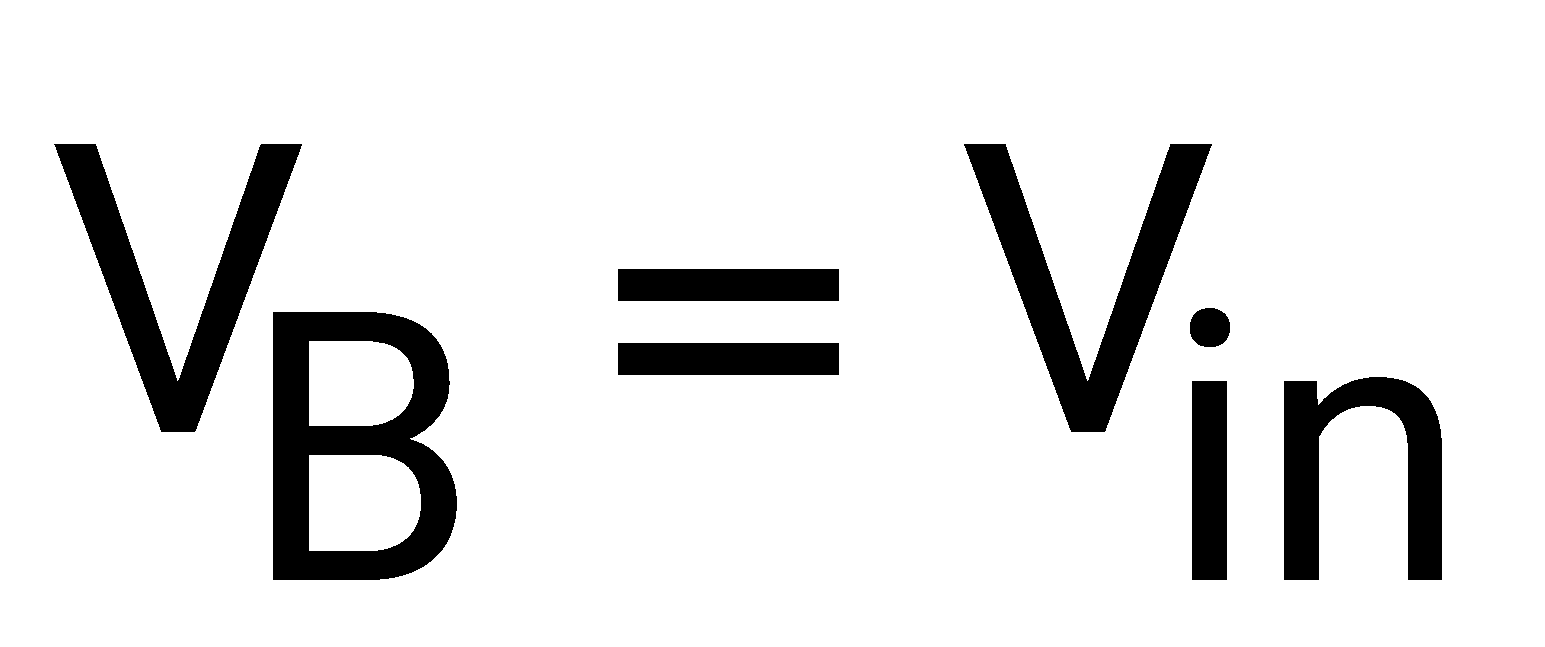

Using virtual short analysis,

&

Option (d) is correct.

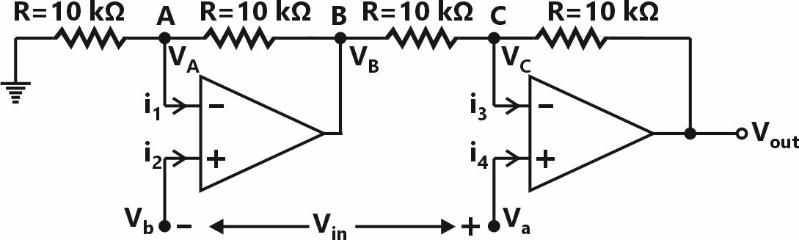

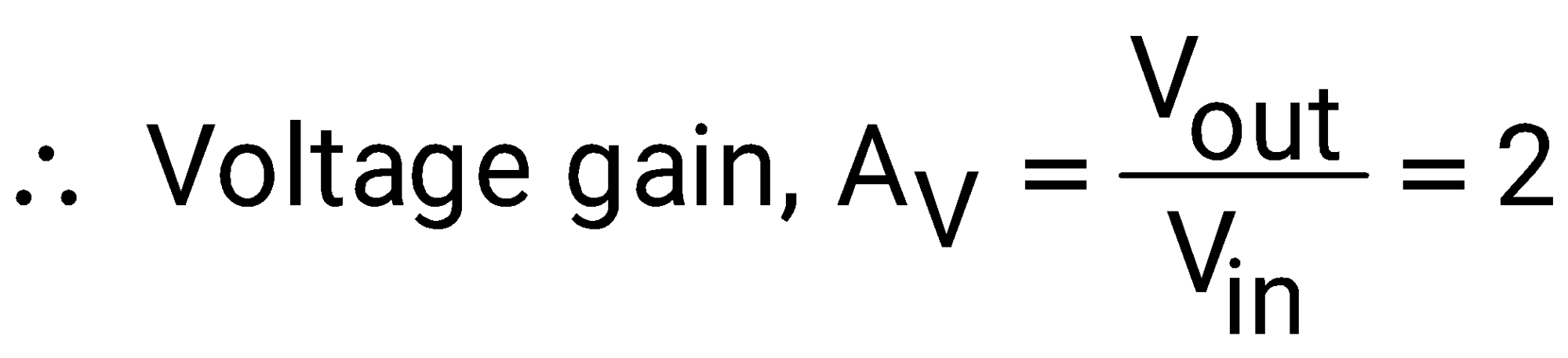

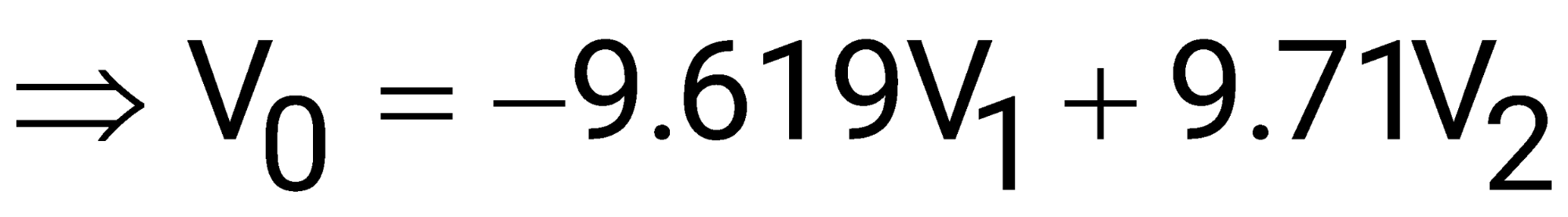

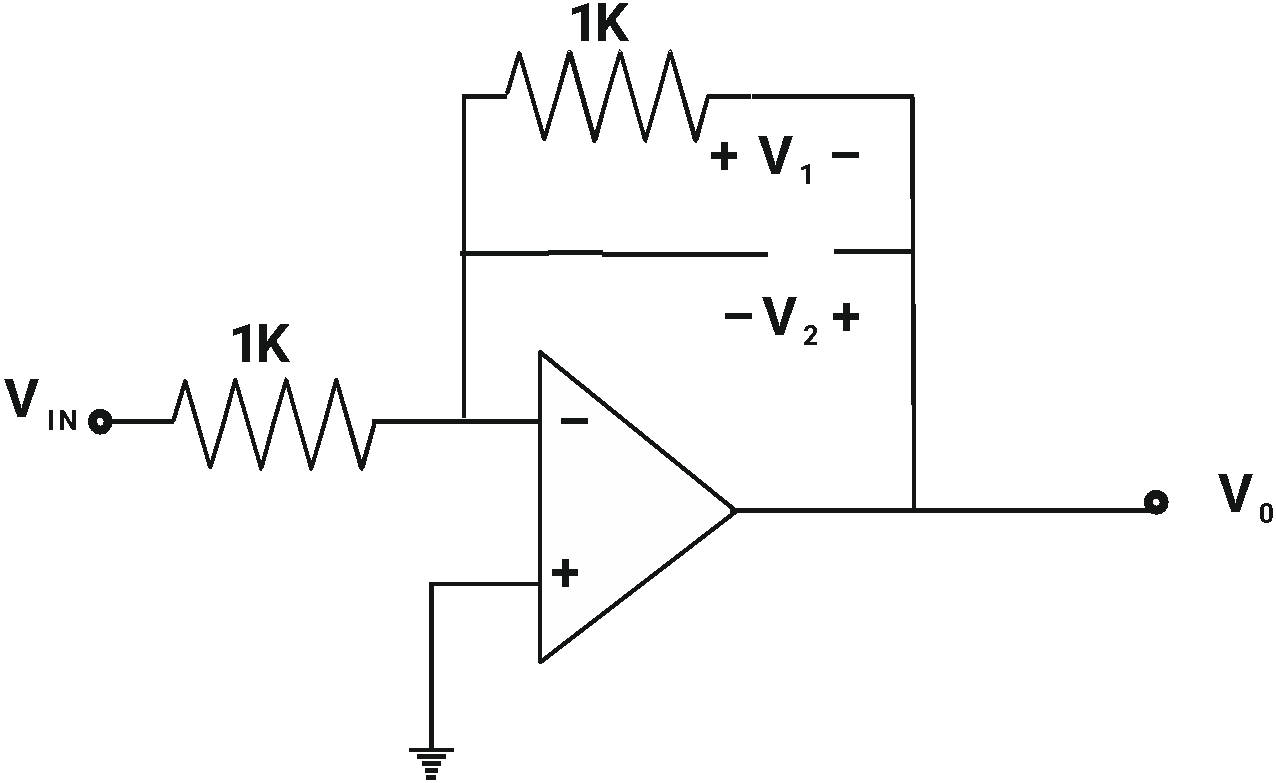

The op-amps in the following circuit are ideal. The voltage gain of the circuit is ________ (round off to the nearest integer).

For ideal op-amps,

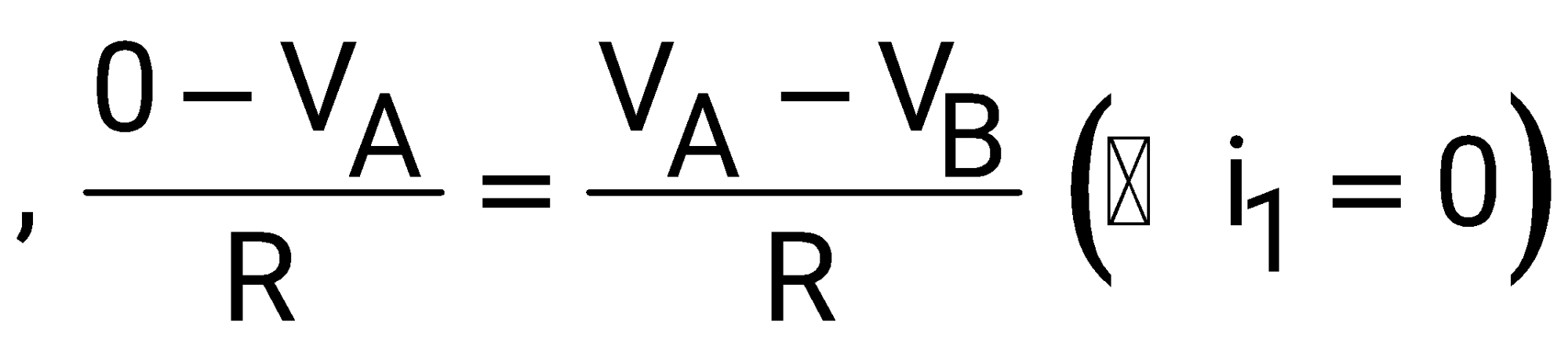

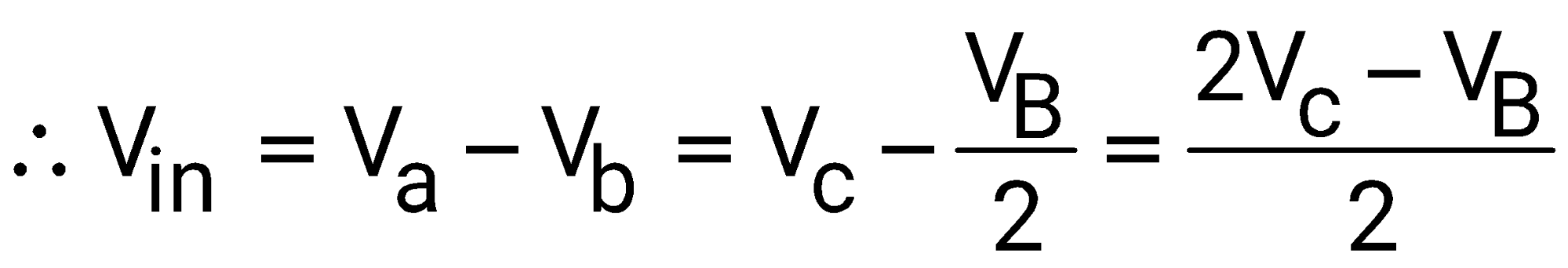

Using at Node A

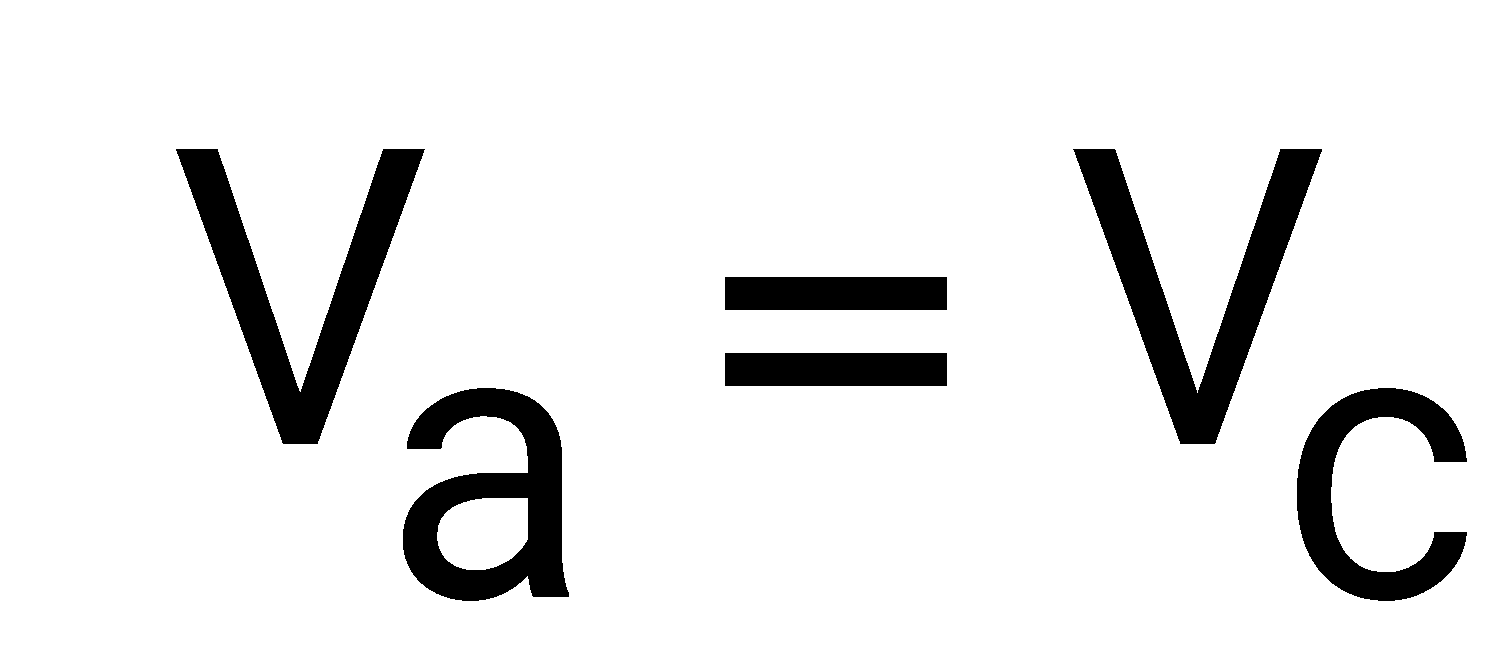

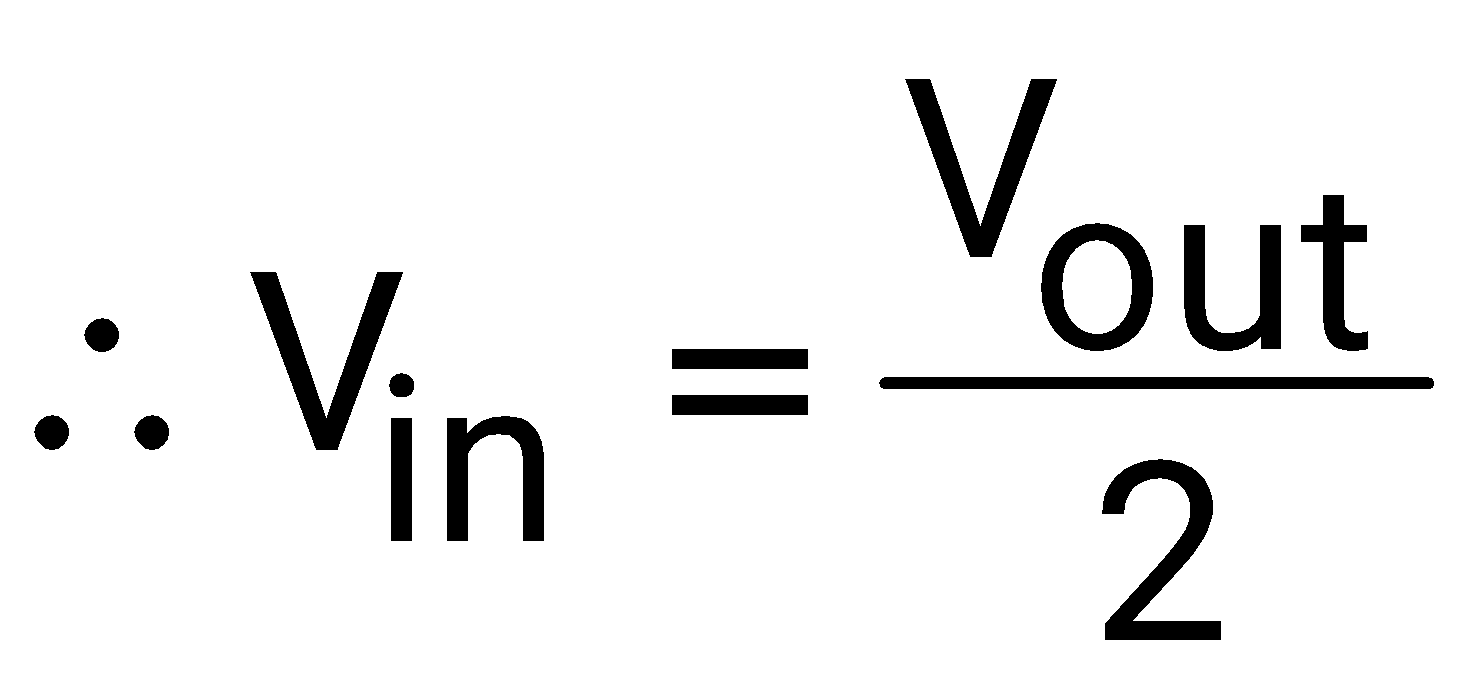

Using Virtual short concept,

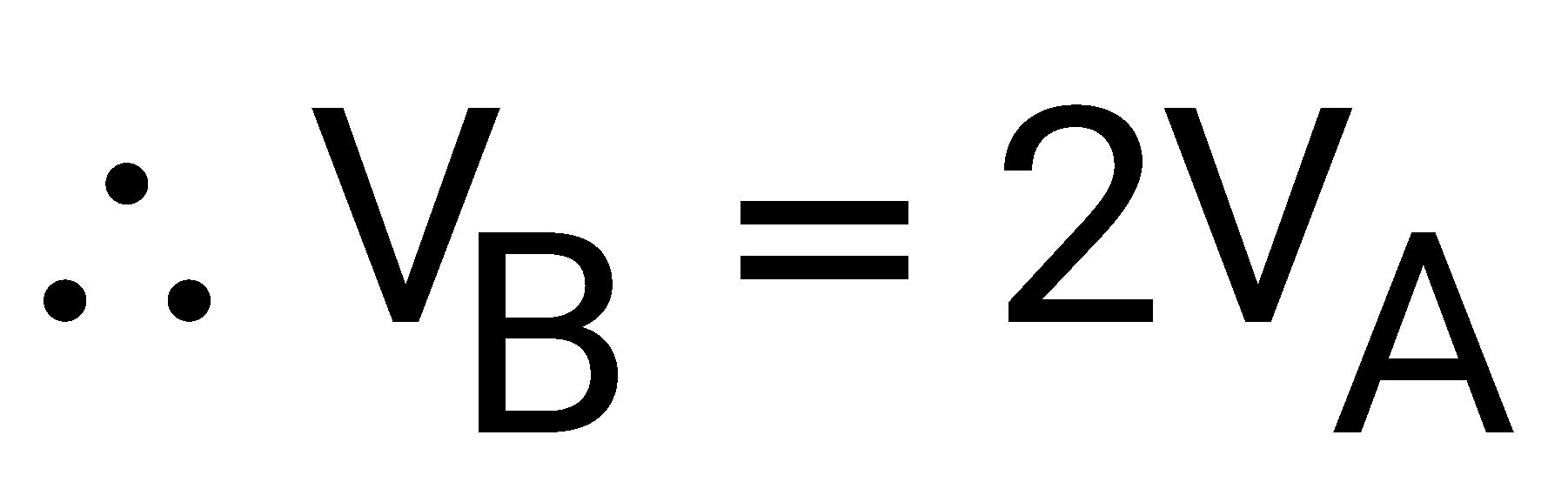

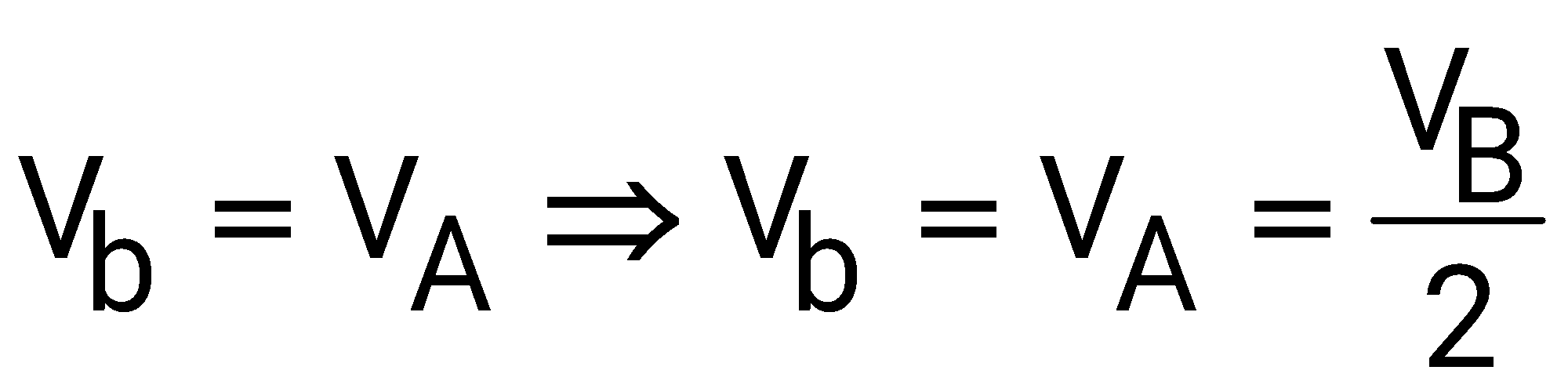

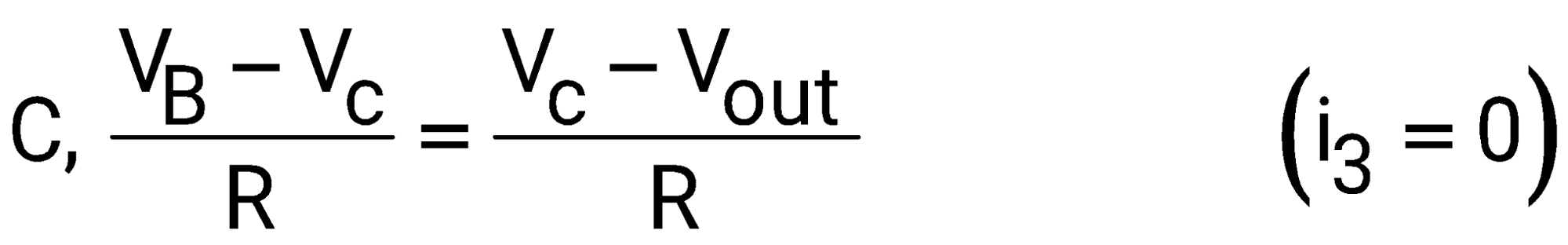

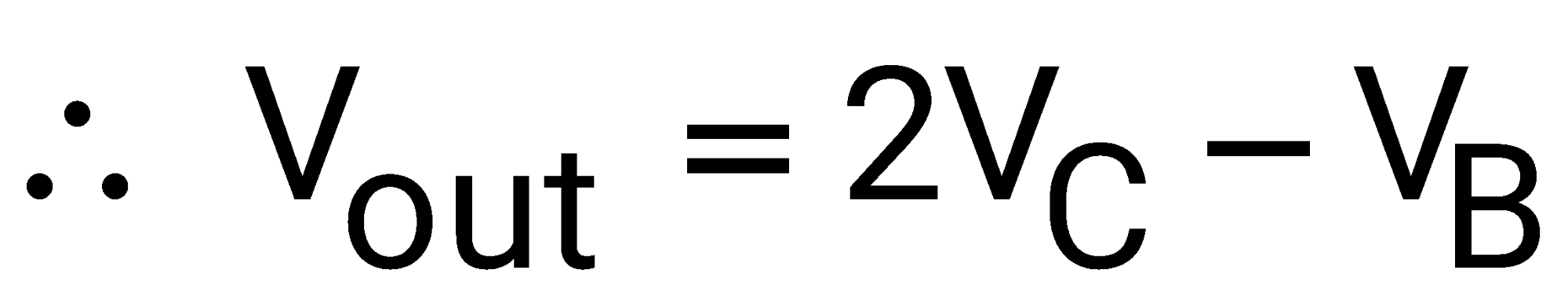

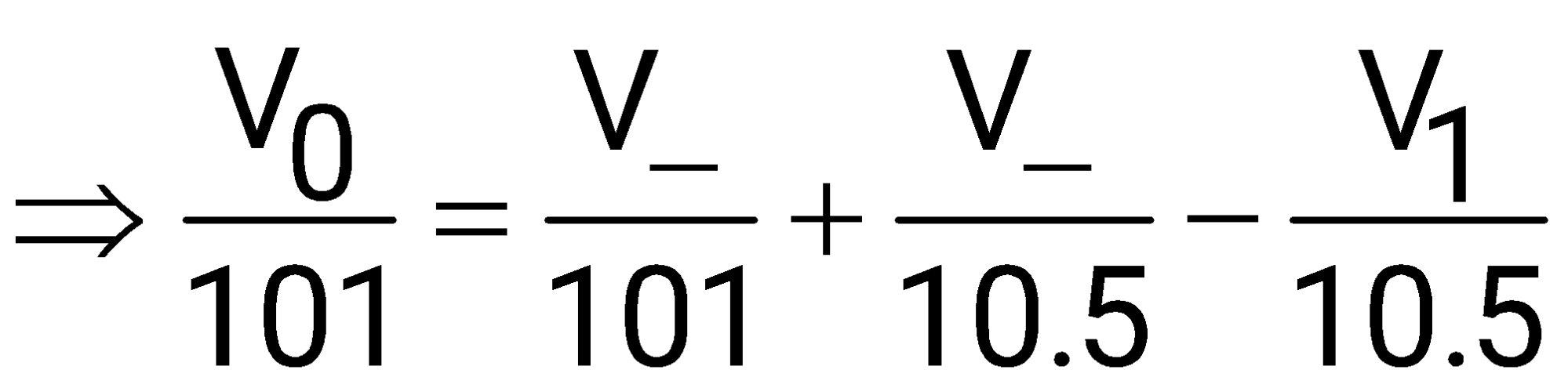

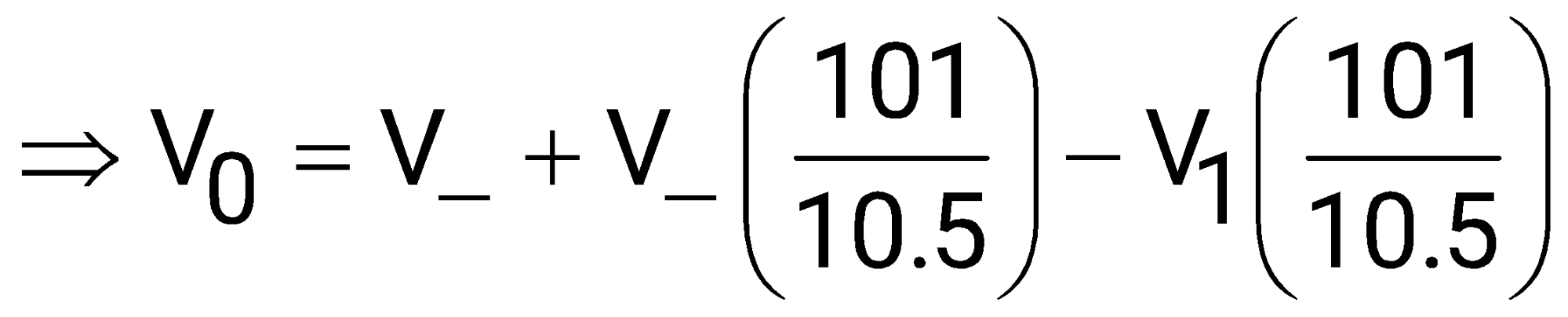

Using at Node

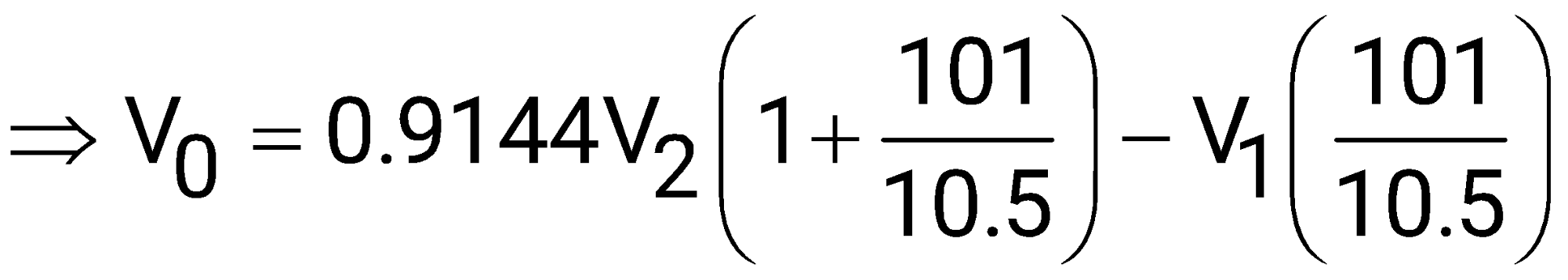

Using virtual short concept,

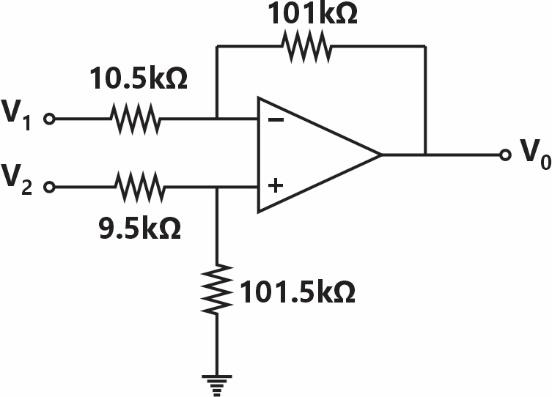

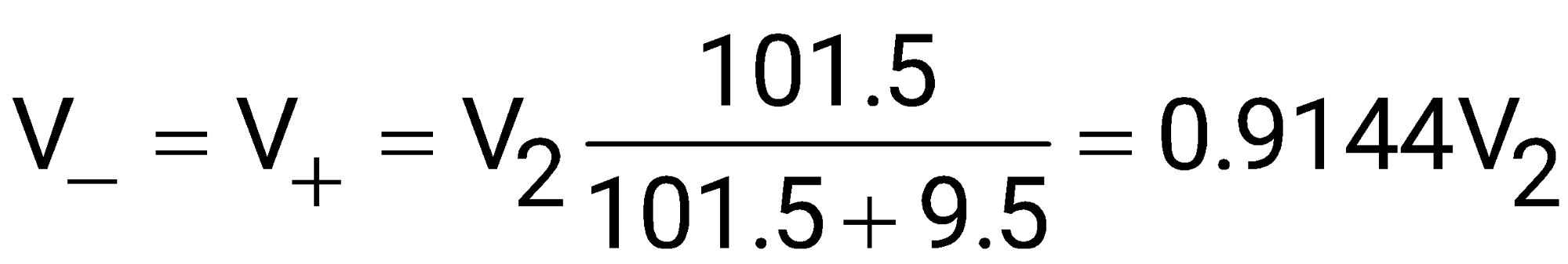

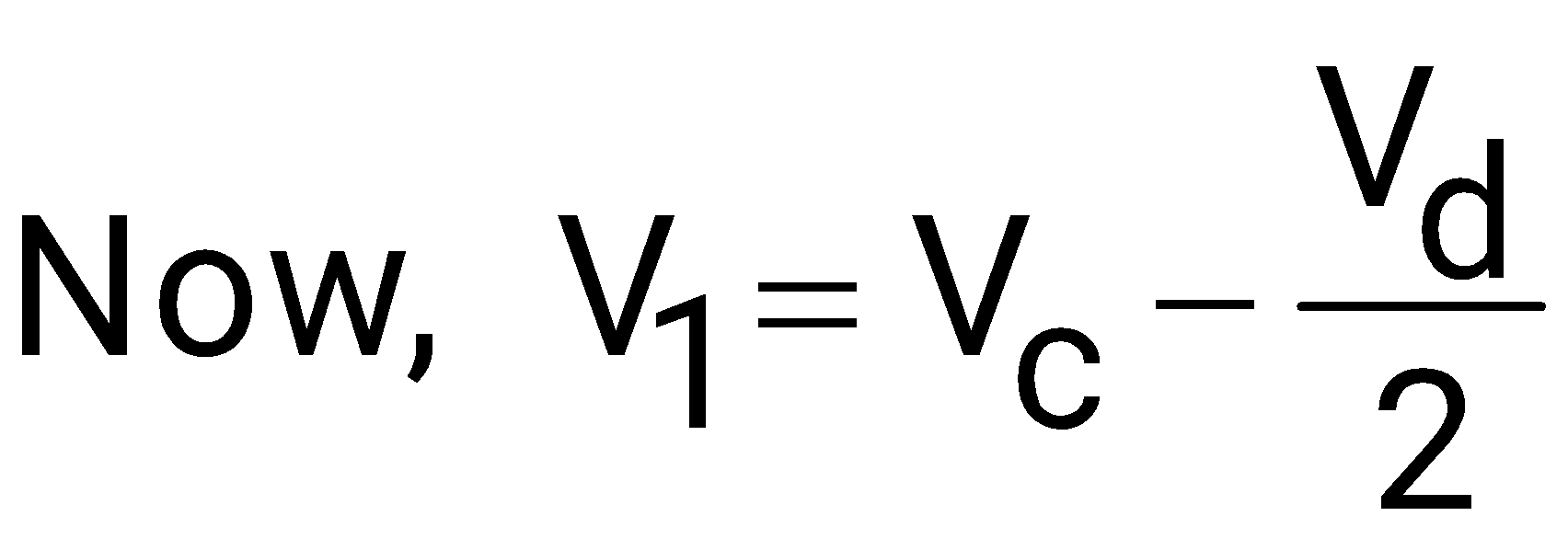

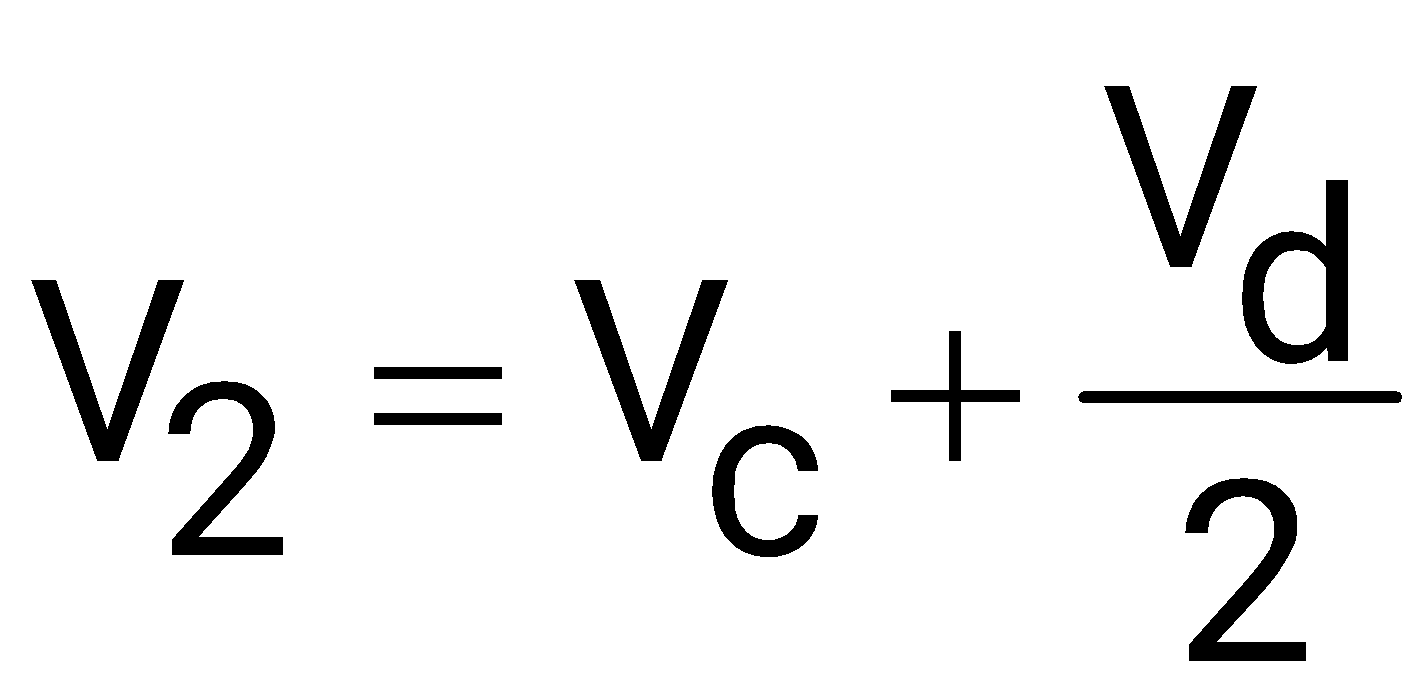

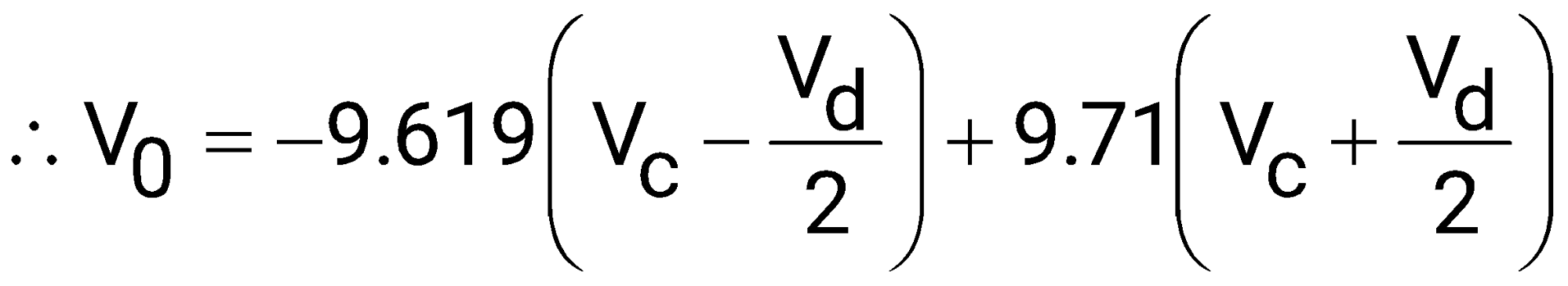

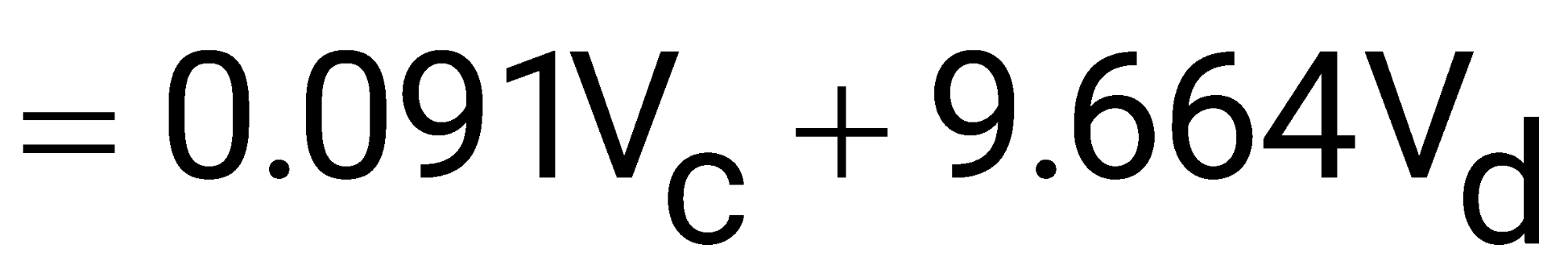

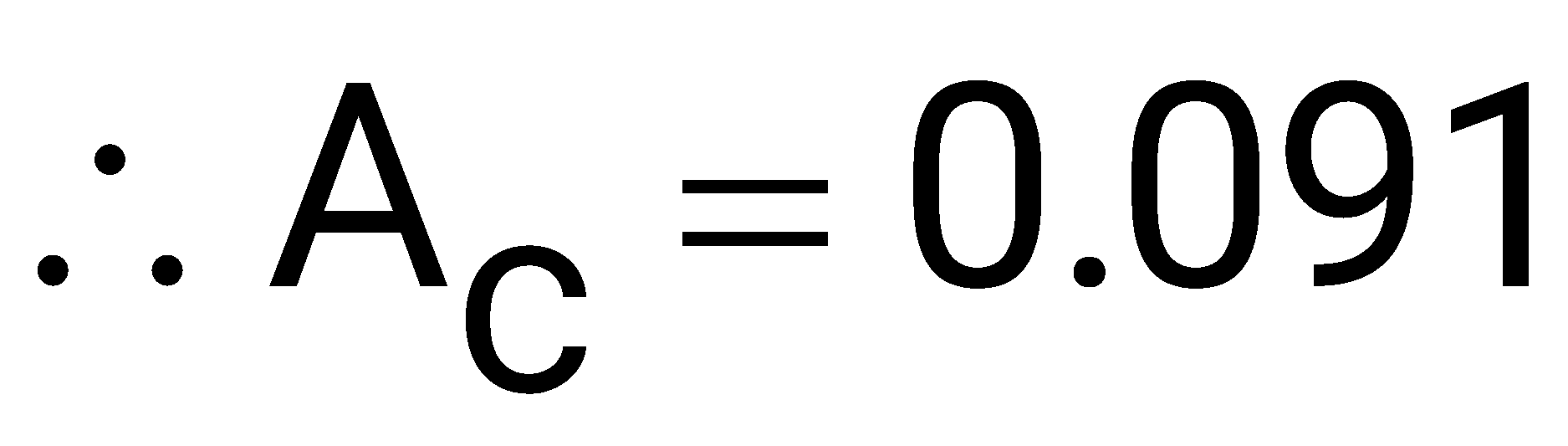

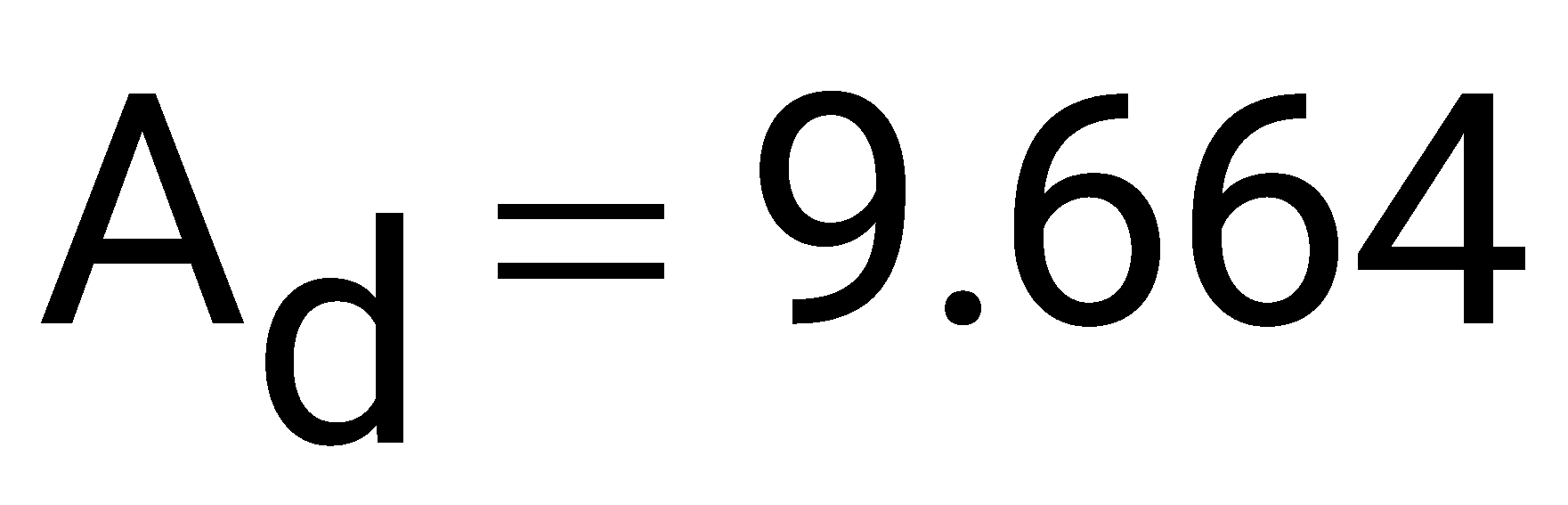

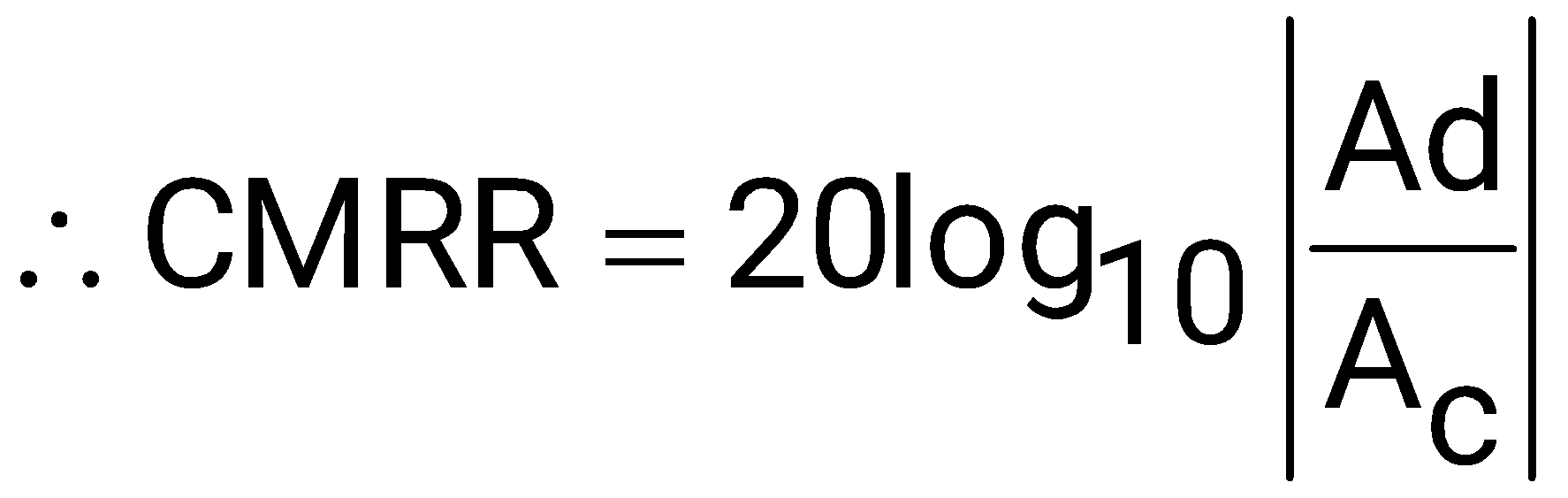

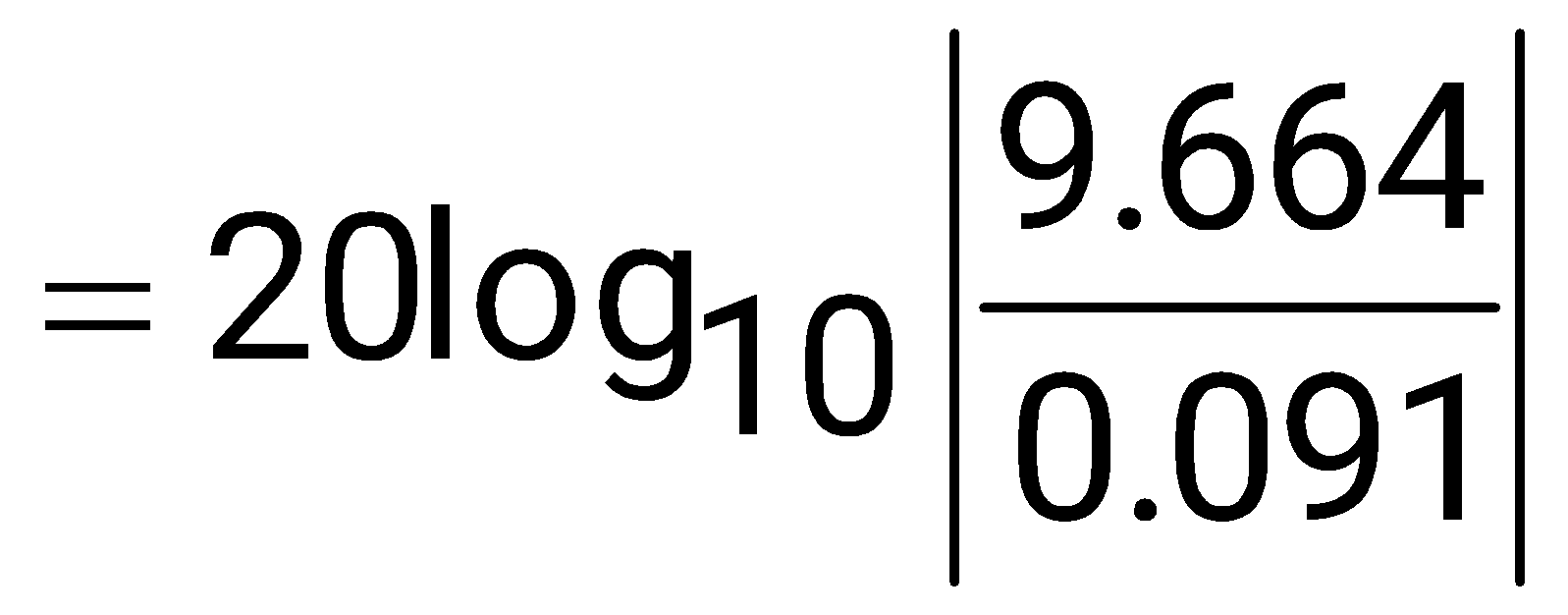

A difference amplifier is shown in the figure. Assume the op-amp to be ideal. The CMRR (in ) of the difference amplifier is ________ (rounded off to 2 decimal places).

By virtual short,

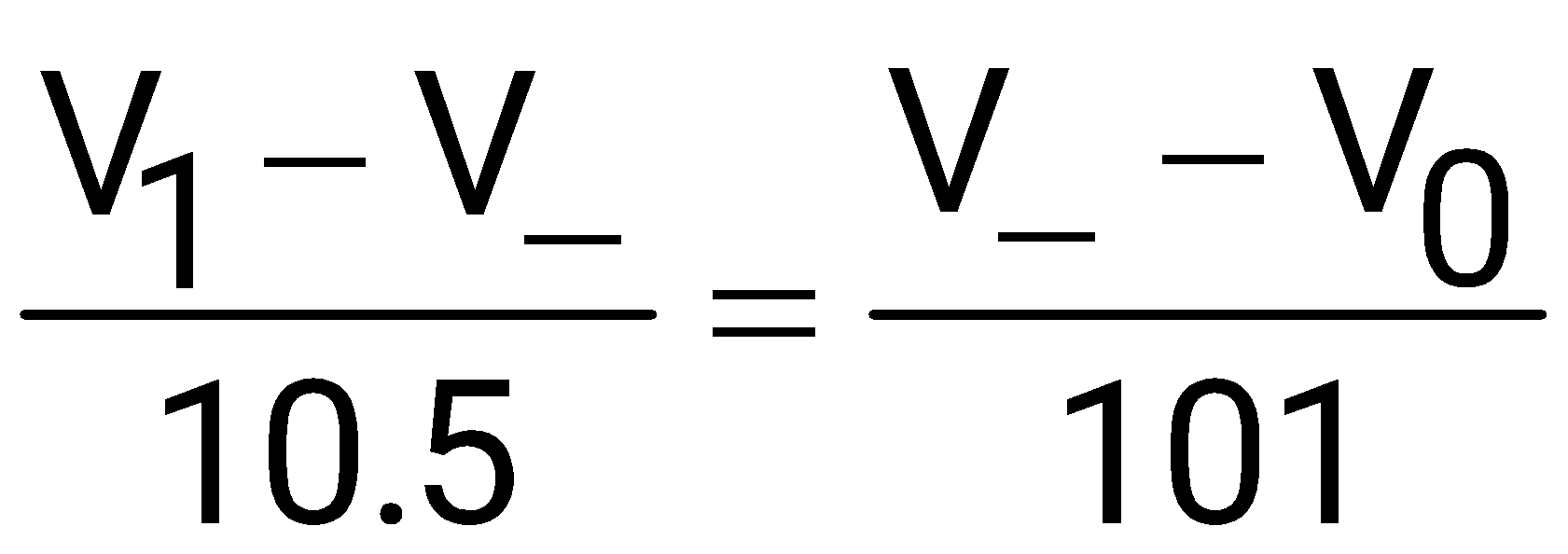

By KCL,

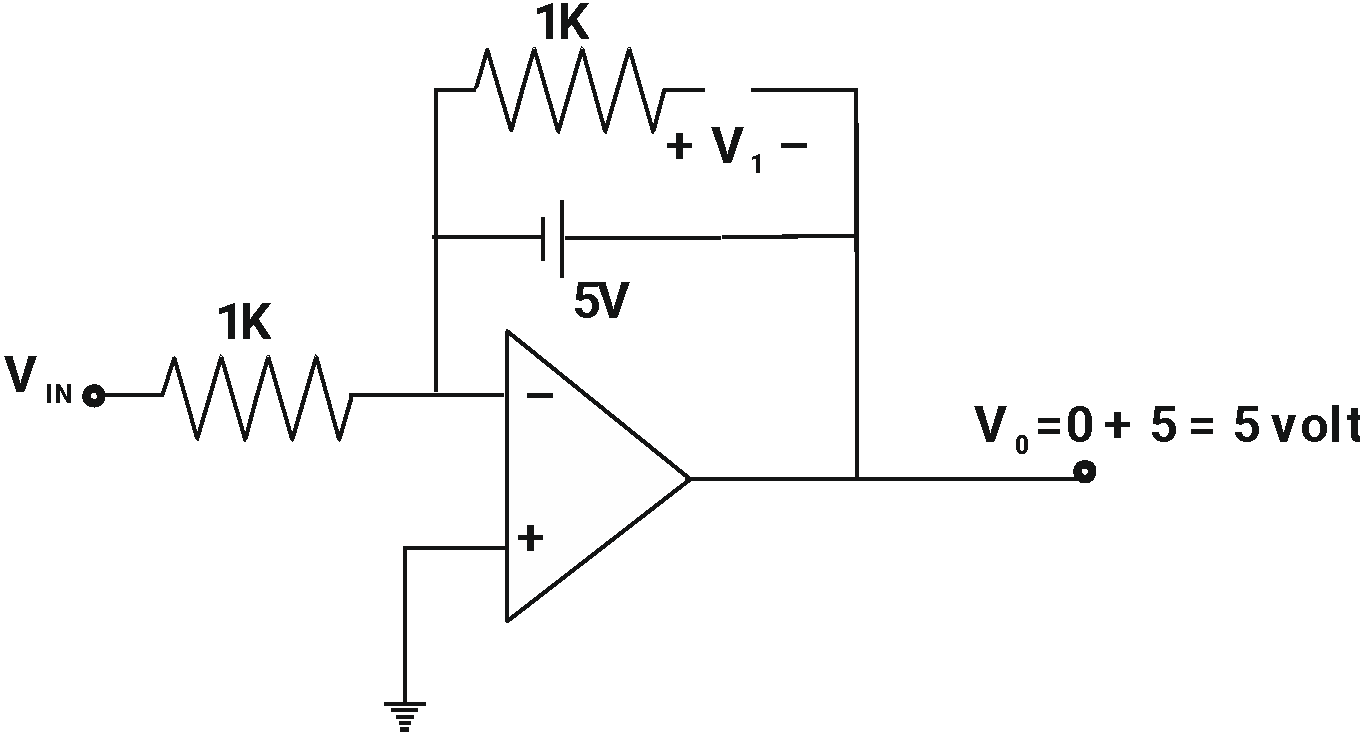

Consider the OP AMP based circuit shown in the figure. Ignore the conduction drops of diodes and . All the components are ideal and the breakdown voltage of the Zener is . Which of the following statements is true?

Applying open circuit test

Due to absence of feedback op-amp acts as comparator

V+ = 0 V- = VIN

during +ve half cycle VIN > 0 V- > V+

V0 = -VSAT

D1 & zener diode are forward biased & D2 is reverse biased

During -ve half cycle VIN < 0 V- < V+

V0 = VSAT = 15V

D2 is forward biased & D1 & Zener diode are reverse biased

Zener diode goes into BD.

During +ve half cycle

∴ minimum value of V0 = -10V

During -ve half cycle

∴ Maximum value of V0 = 5Volt