Digital Electronics

Data Converters

Practice questions from Data Converters.

20

Total0

Attempted0

Correct0

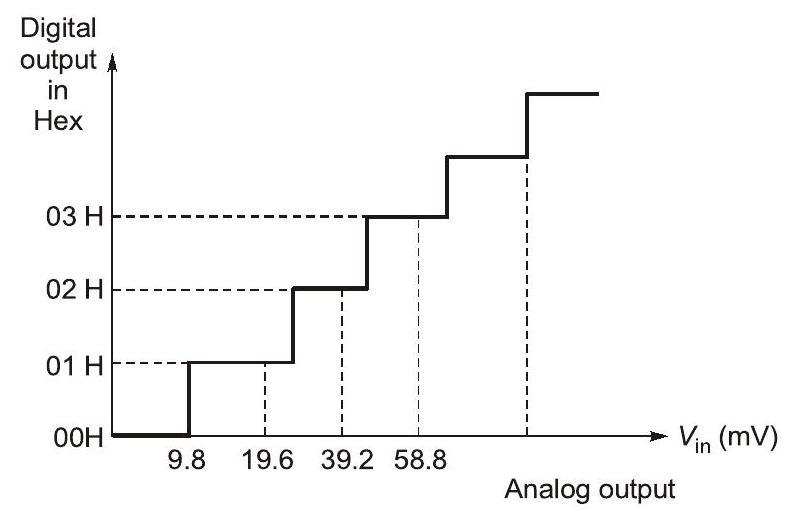

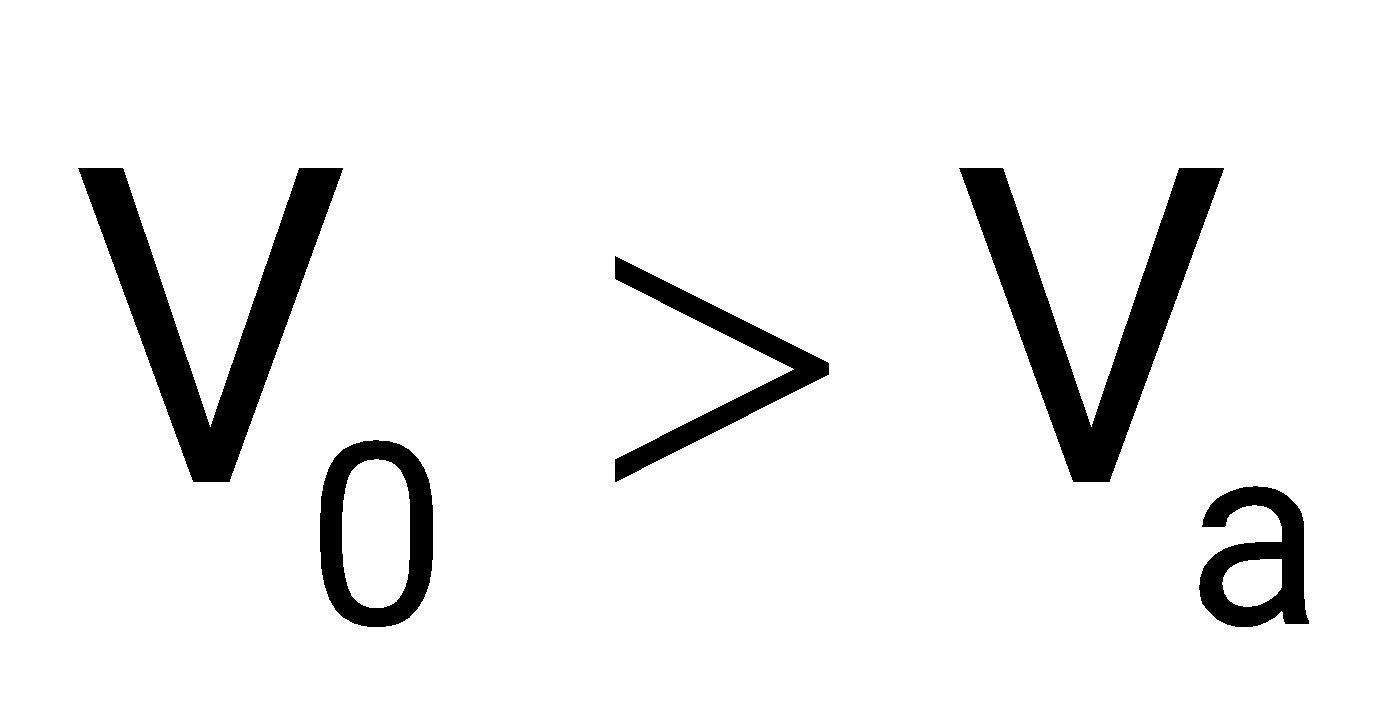

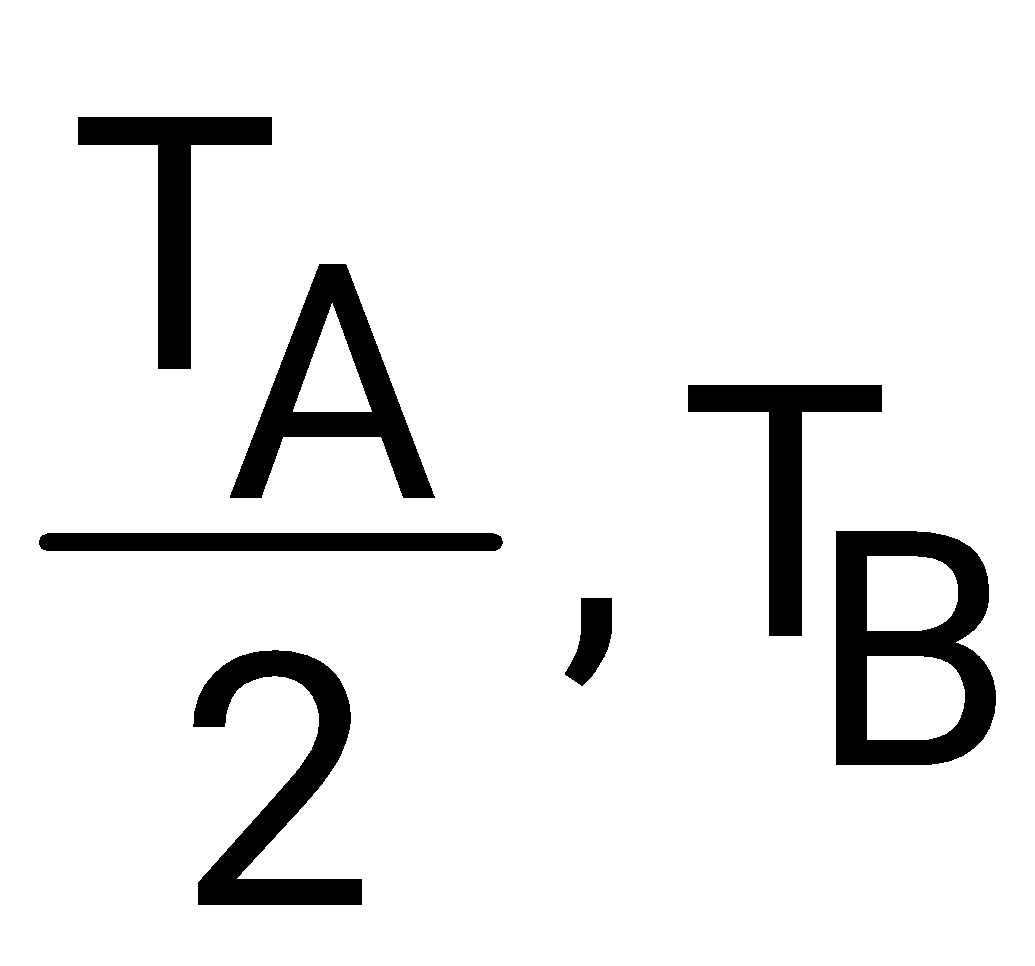

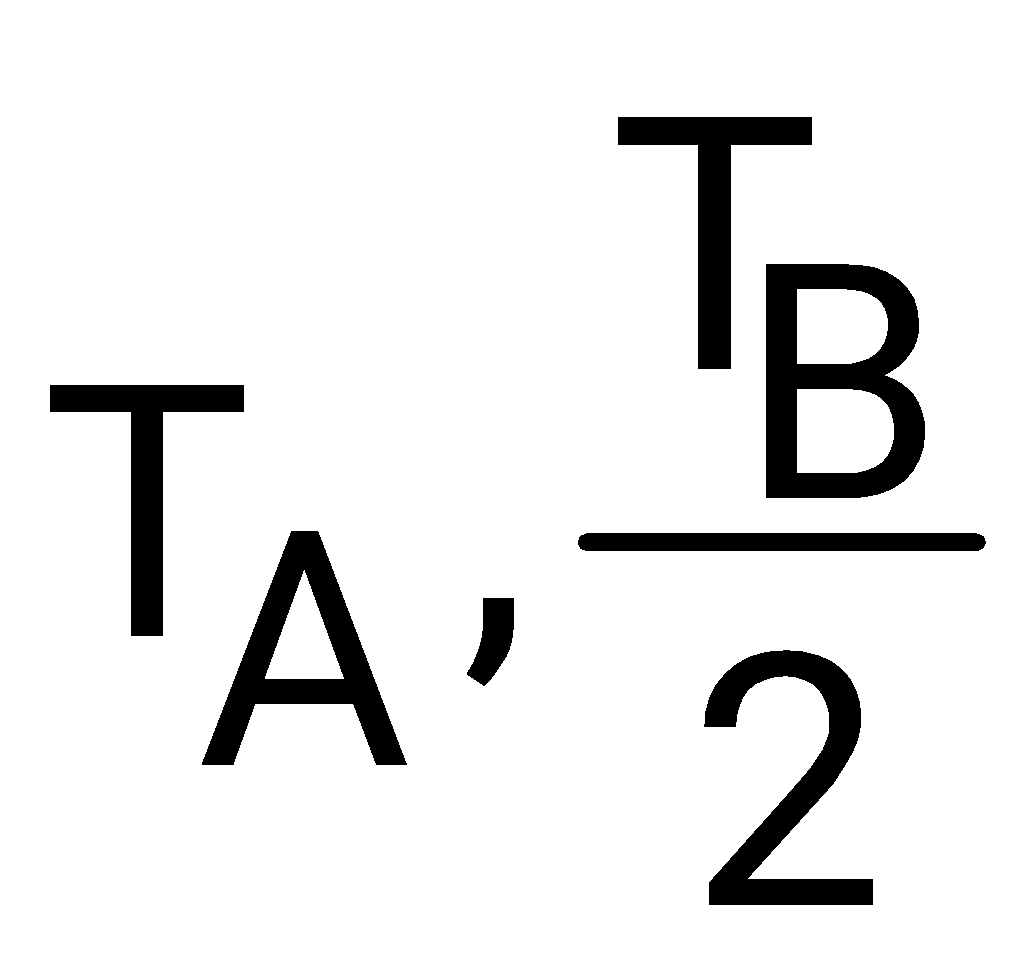

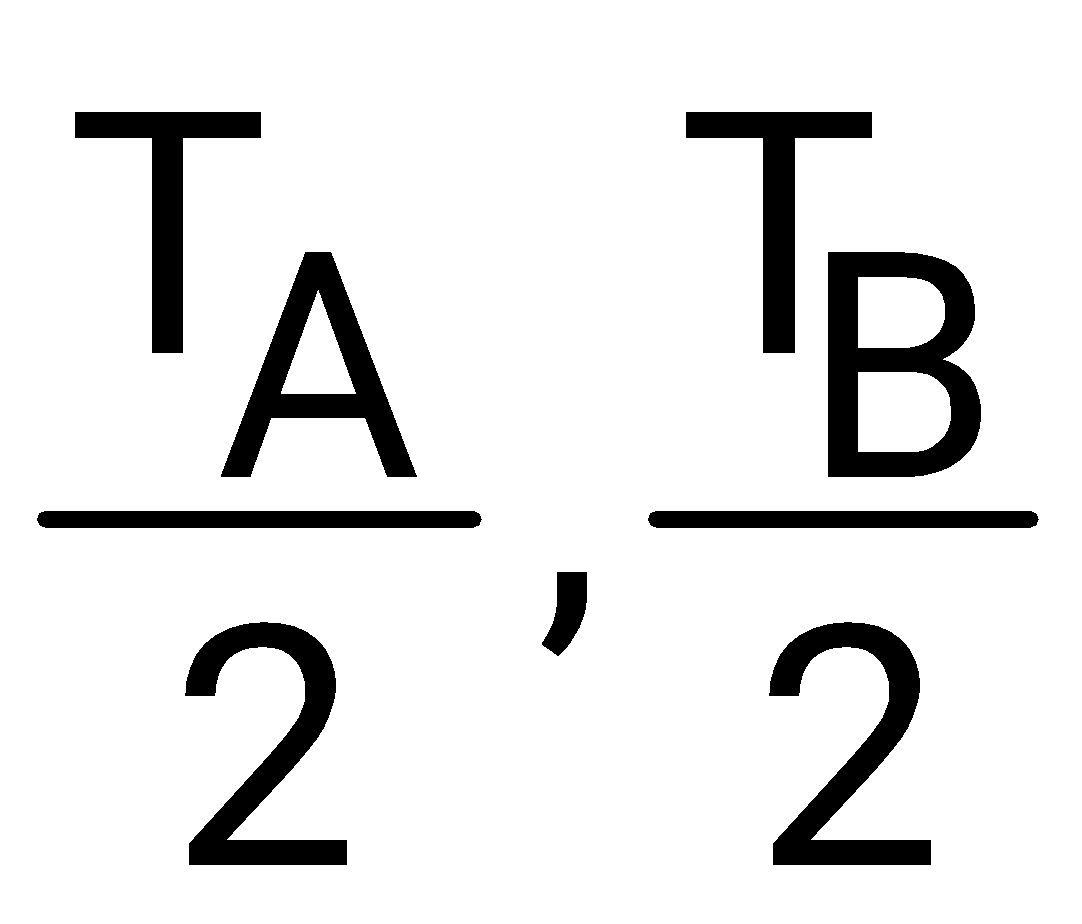

IncorrectAn 8-bit ADC converts analog voltage in the range of 0 to to the corresponding digital code as per the conversion characteristics shown in figure. For , which of the following digital output, given in hex, is true?

length of each interval or step size = 19.6 mV

Number of steps for given analog input

= 101.64

∴ The o/p makes a transition at middle of interval as can be seen from graph.

& 101.64 > 101.5 ∴ output will be hexadecimal value of 102

(102)10 = (66)H

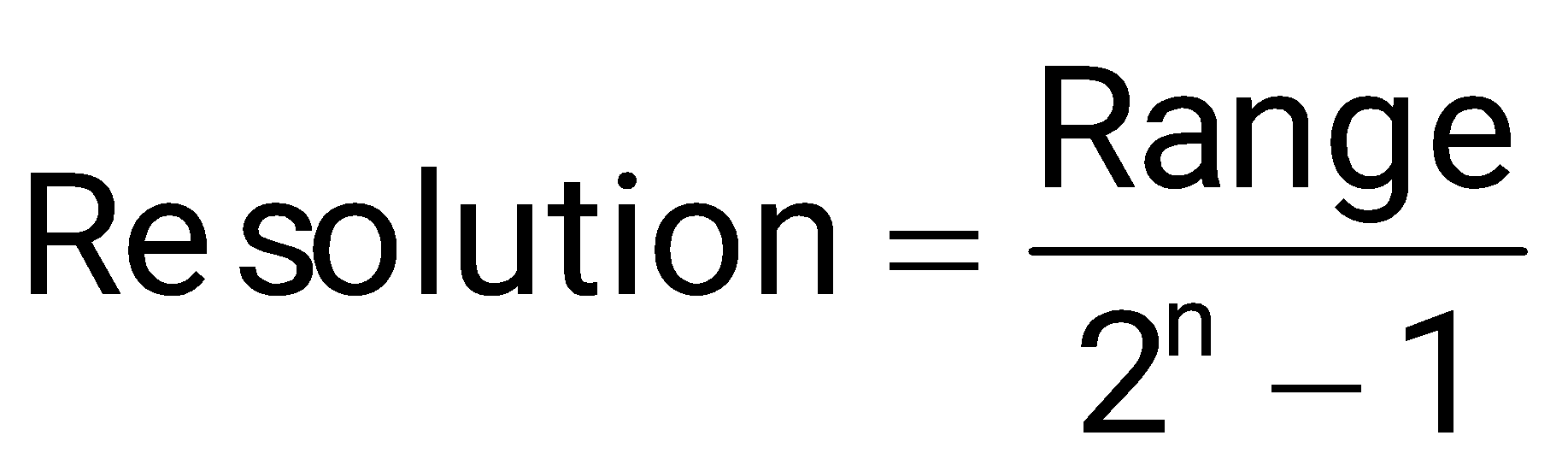

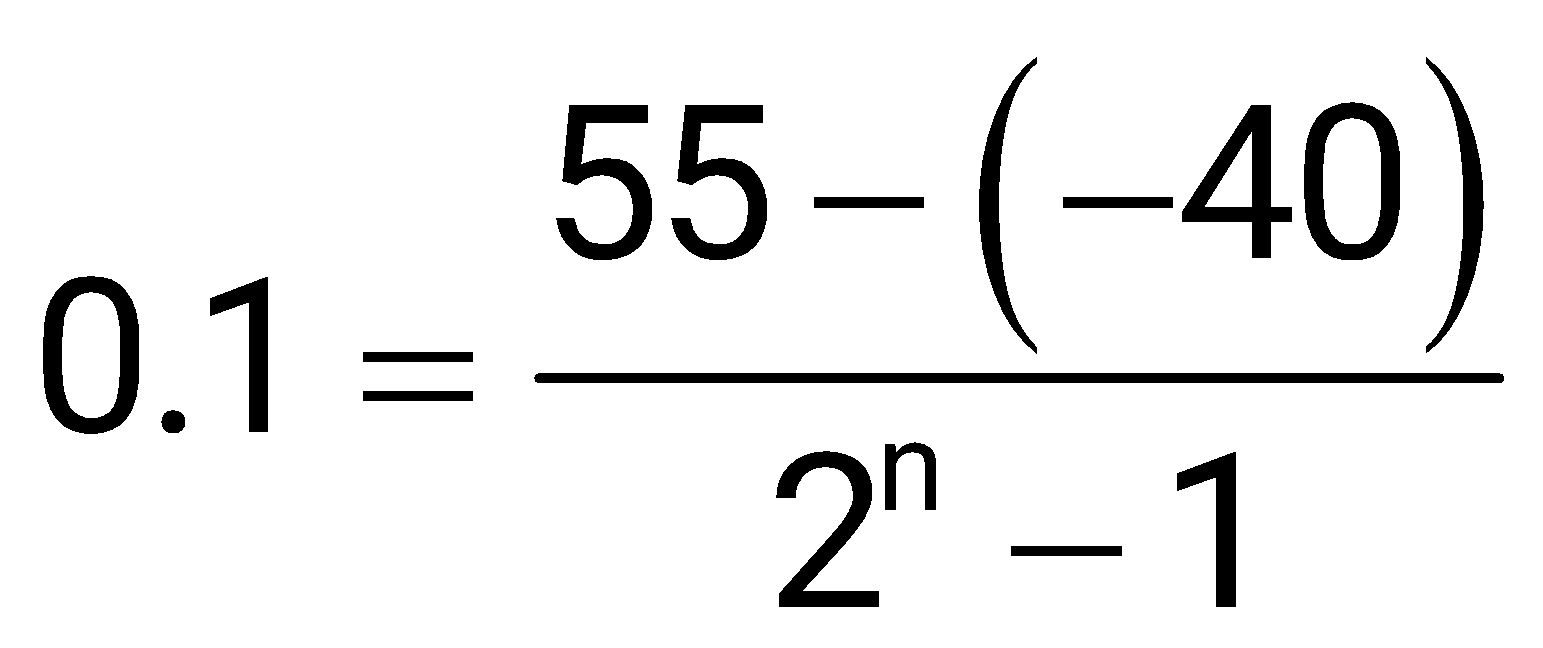

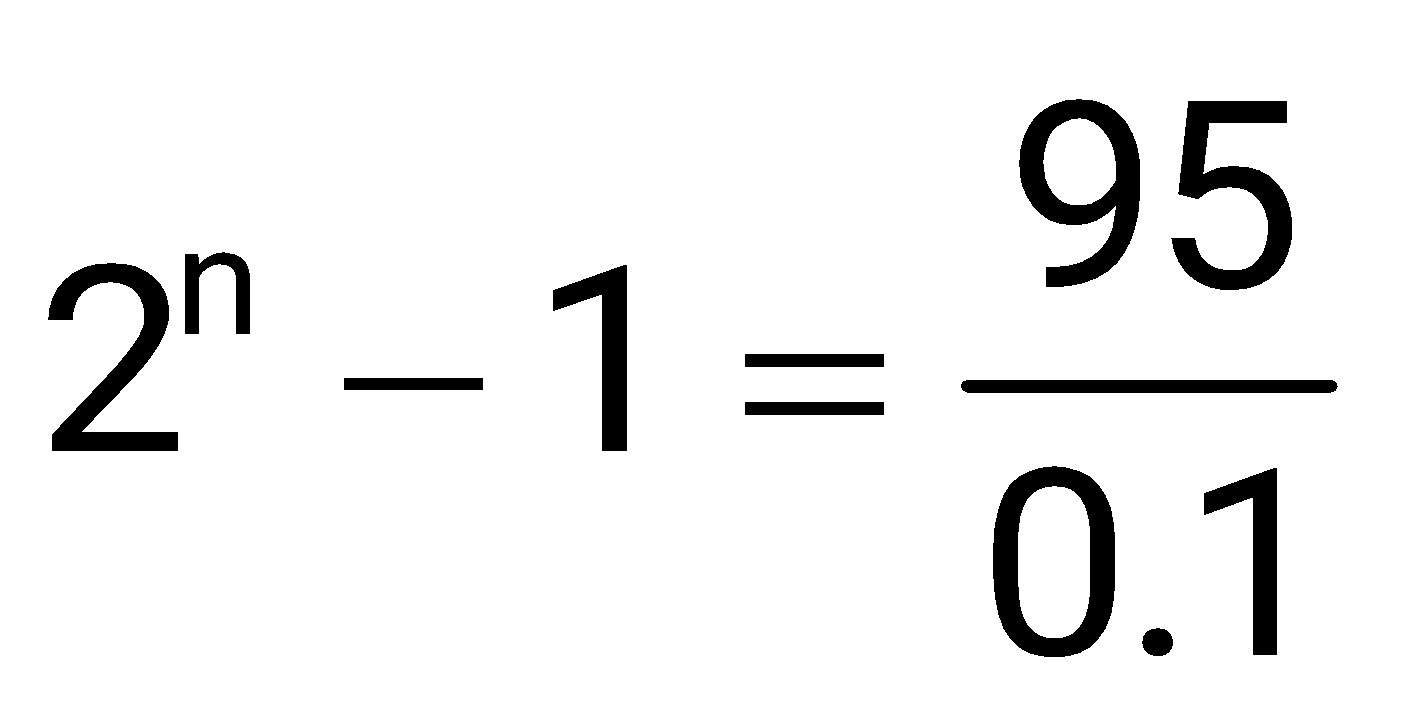

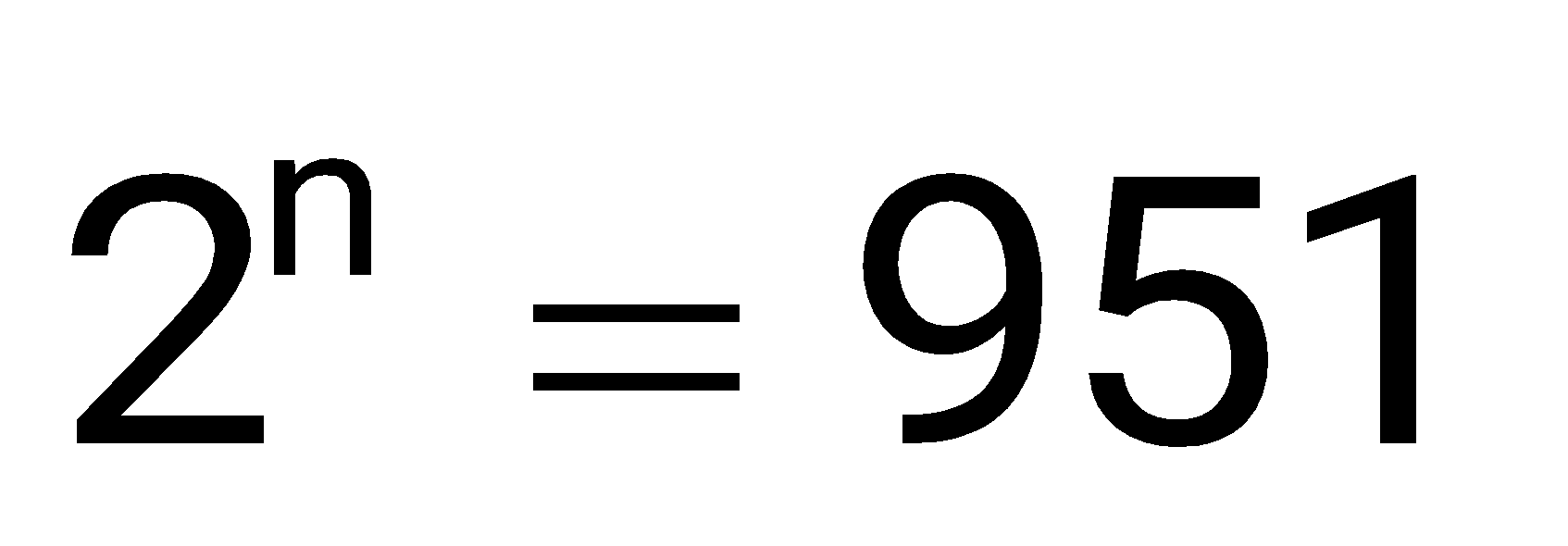

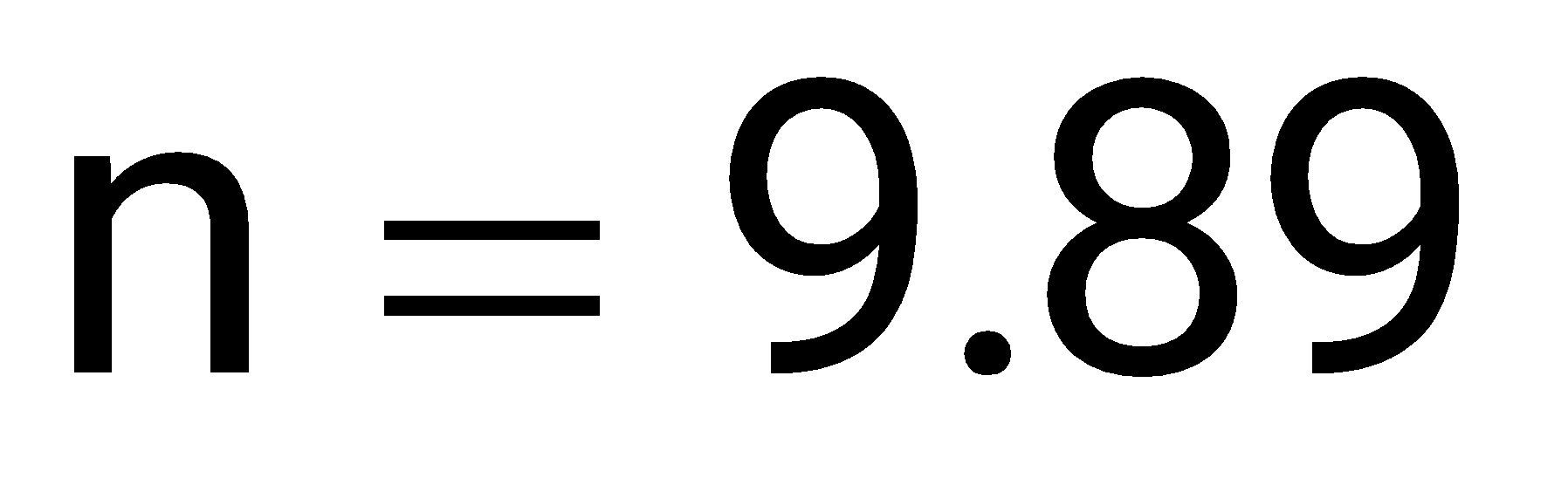

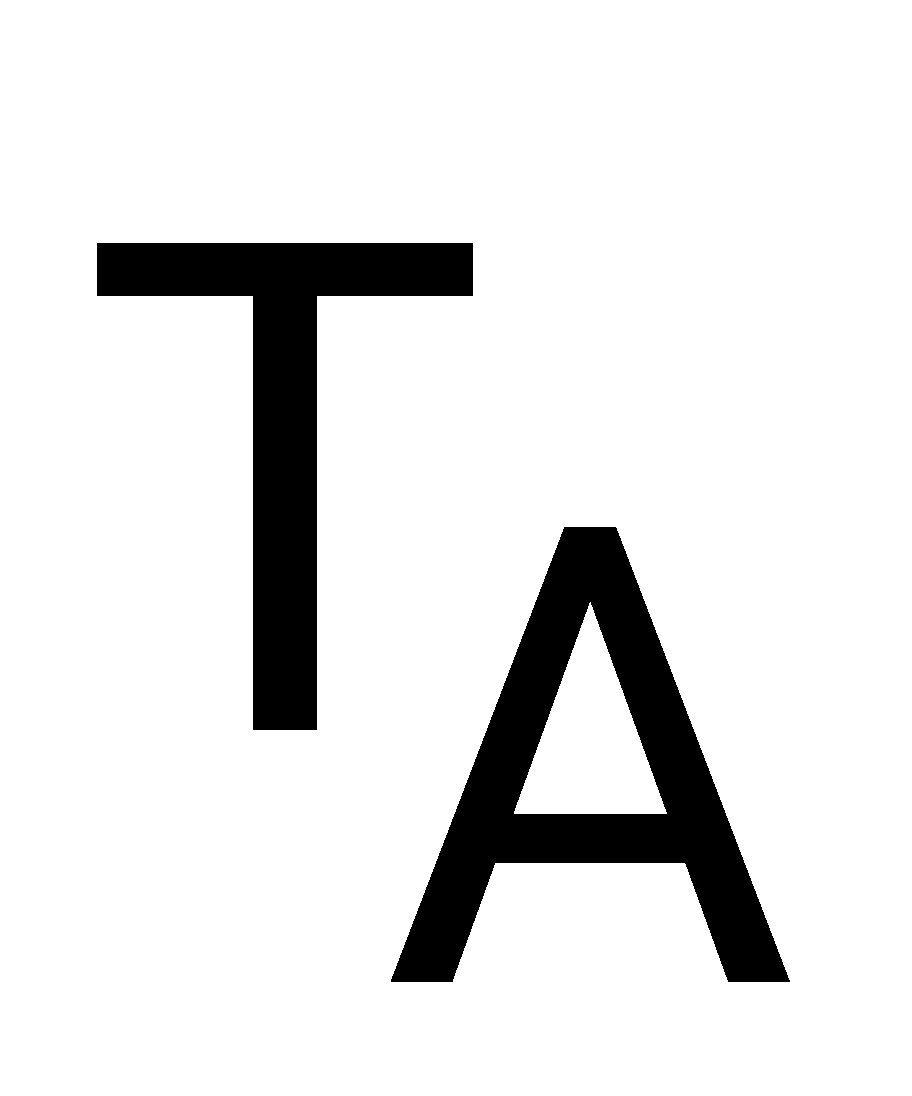

A temperature in the range of is to be measured with a resolution of . The minimum number of ADC bits required to get a matching dynamic range of the temperature sensor is

Nearest integer = 10

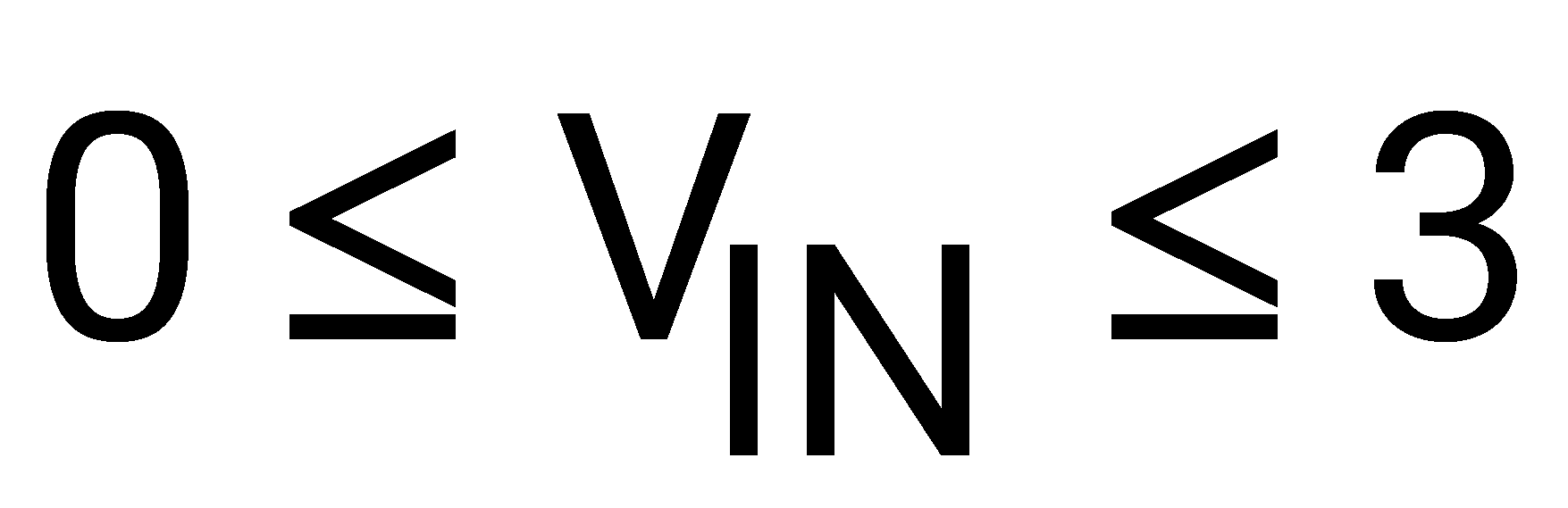

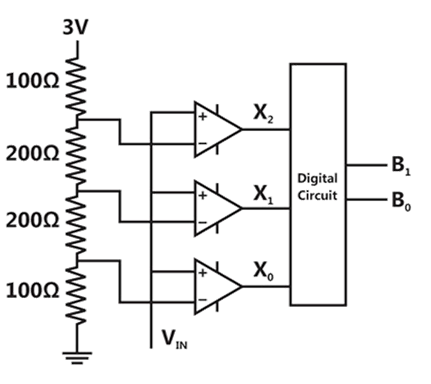

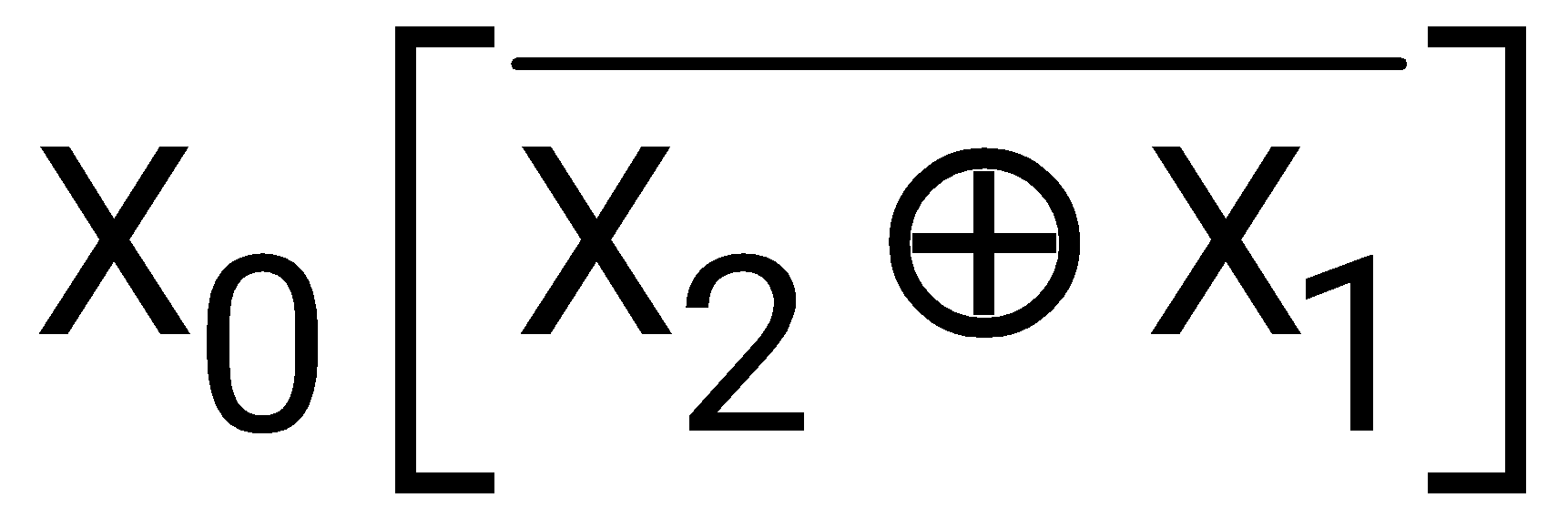

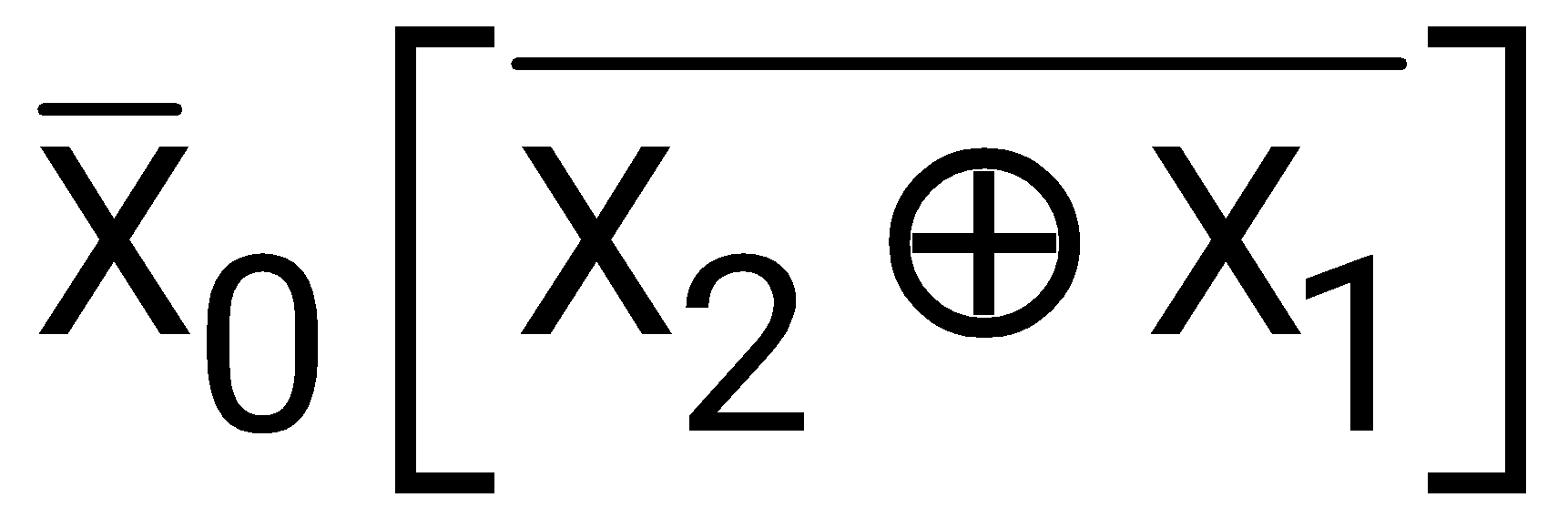

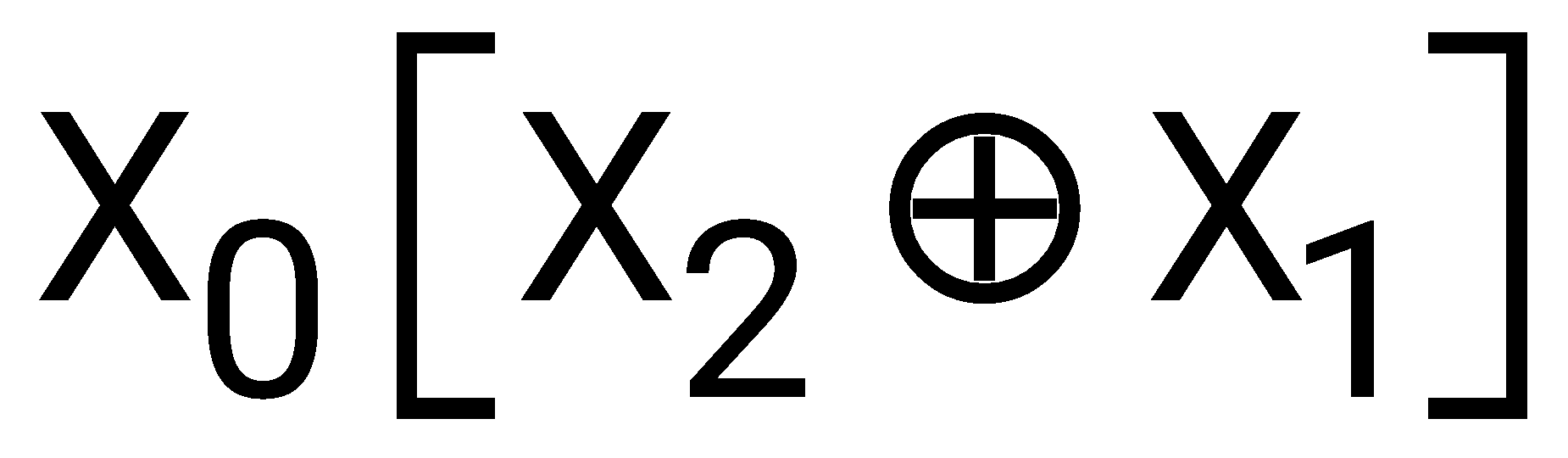

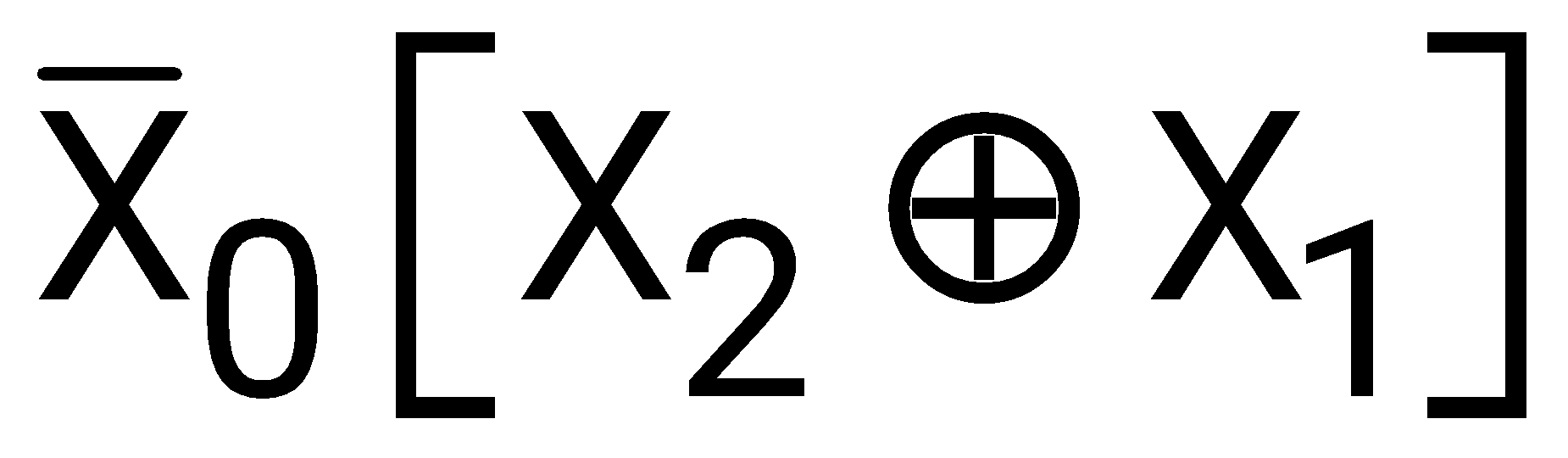

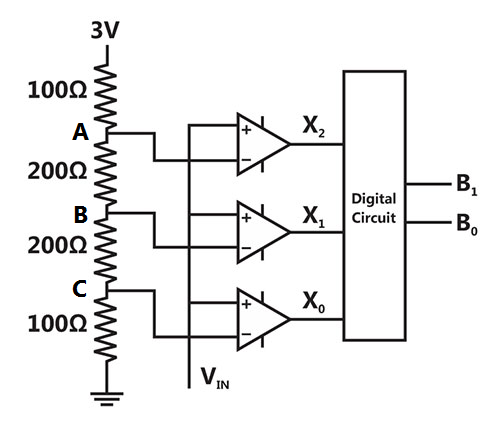

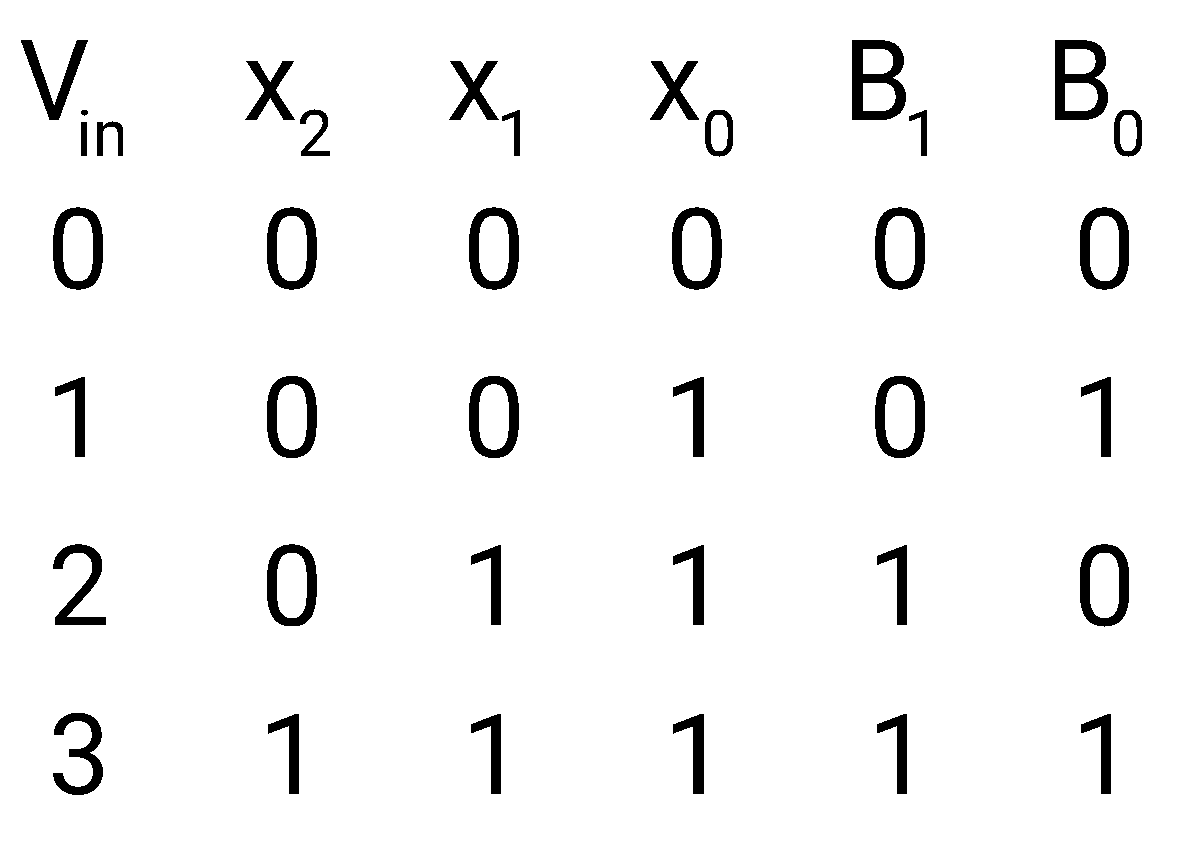

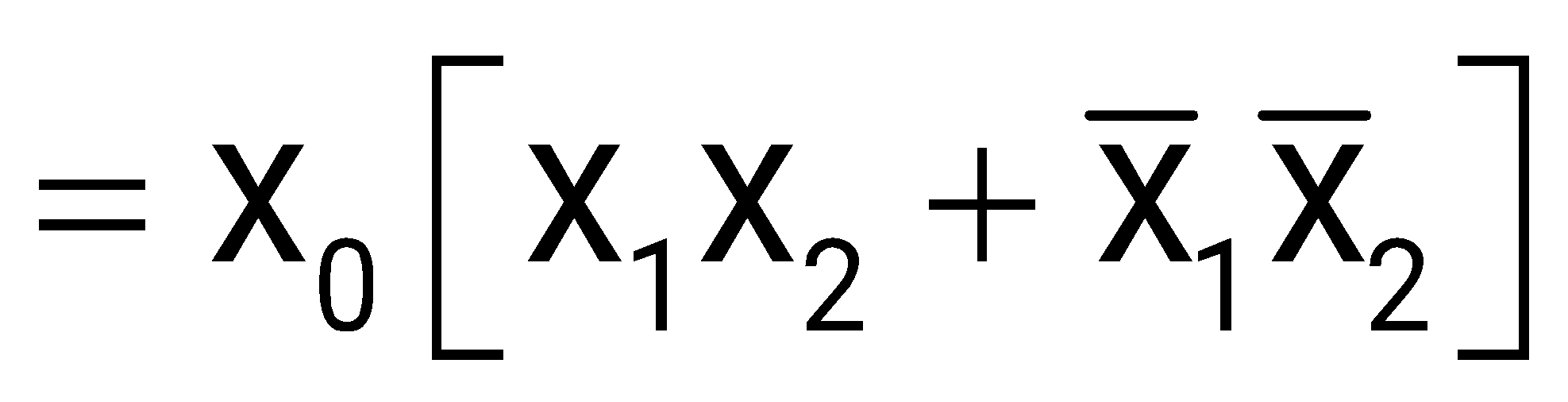

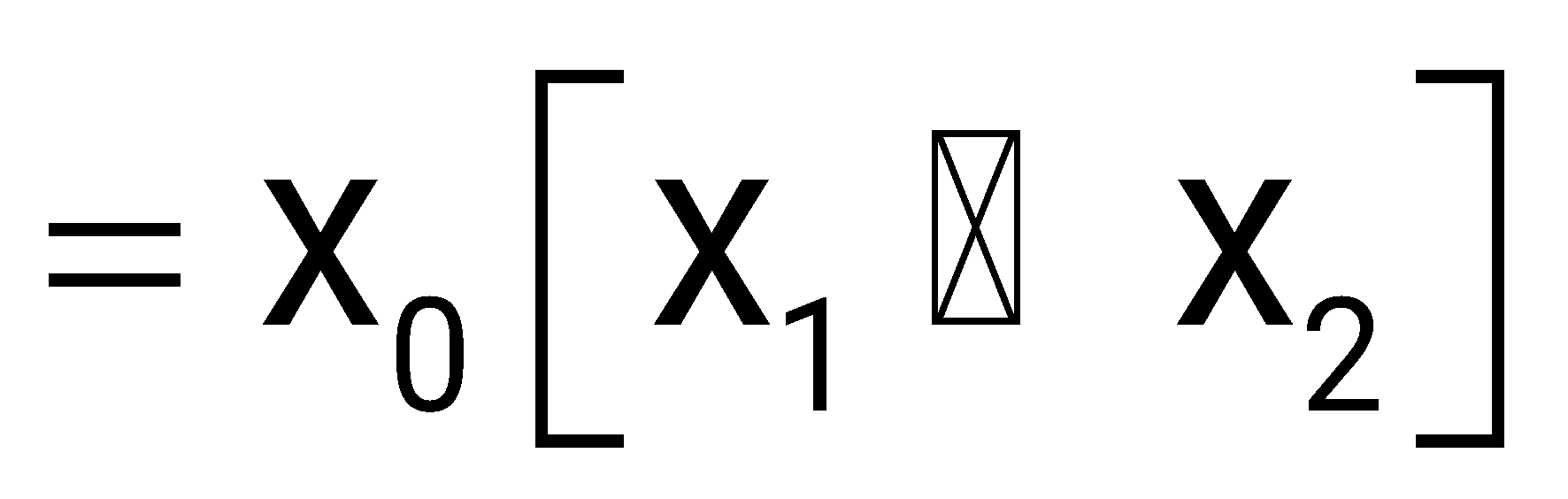

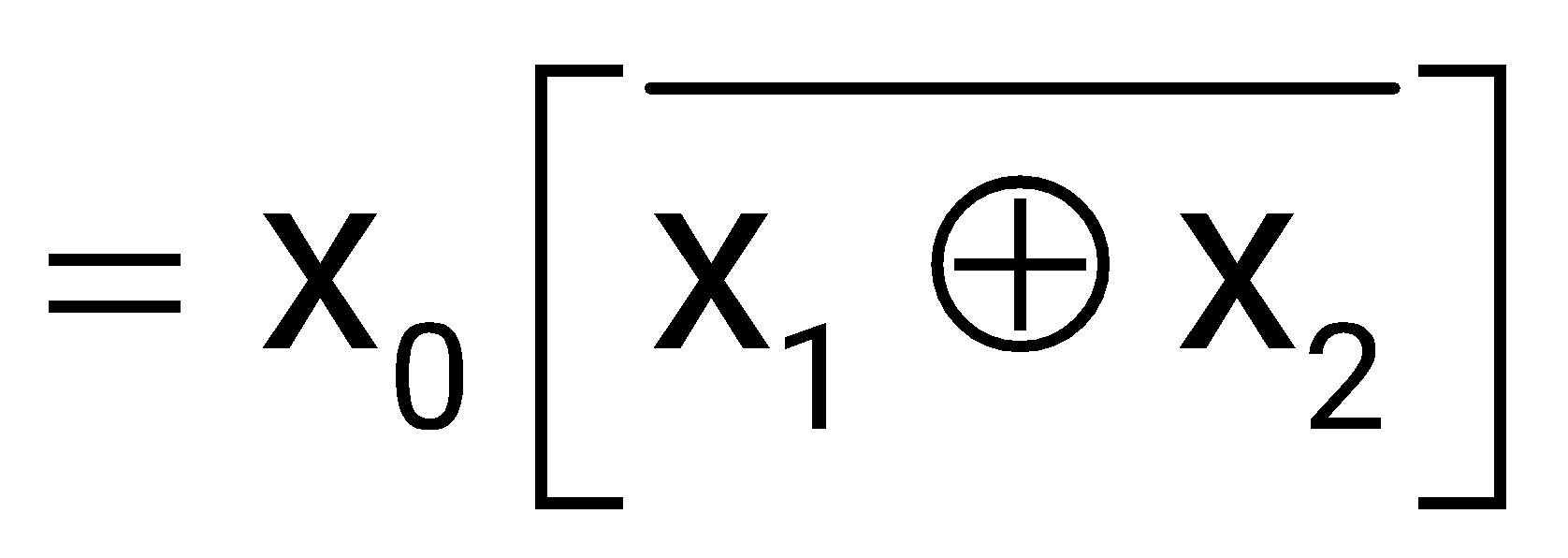

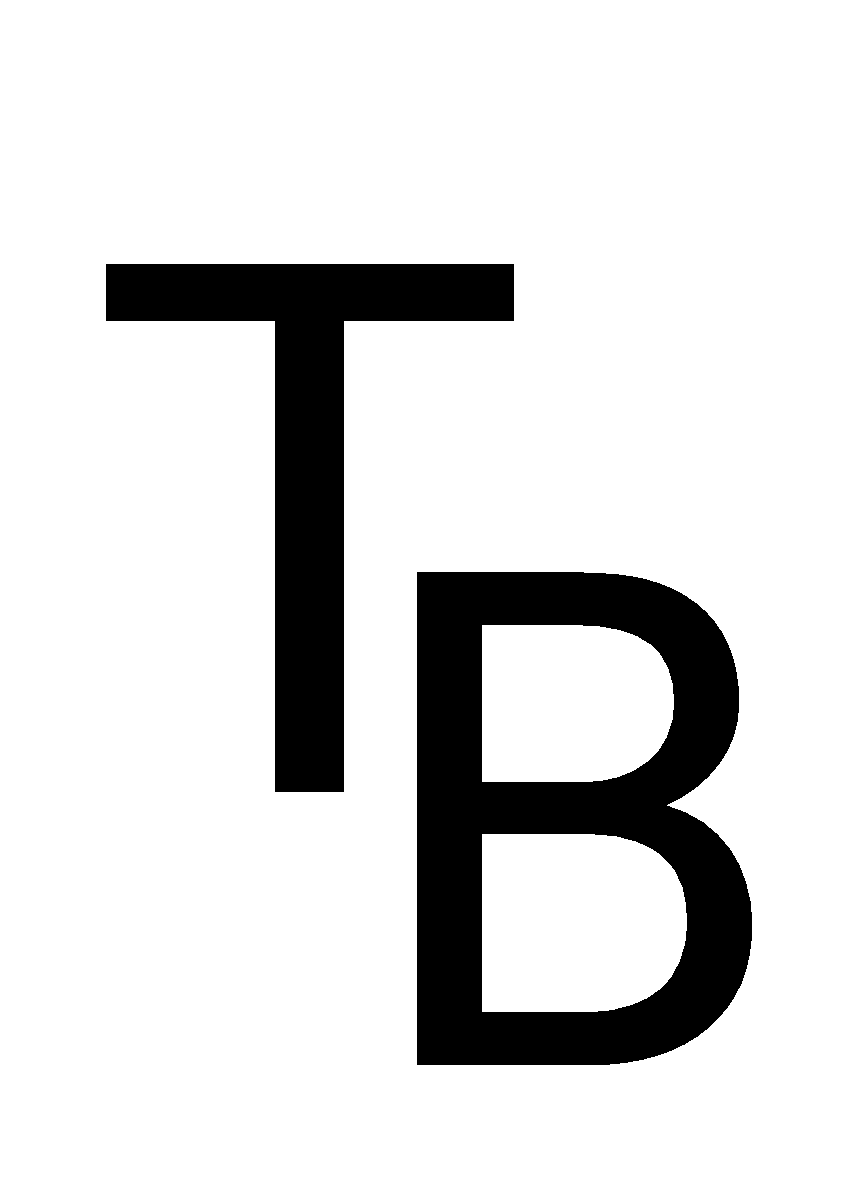

A 2-bit flash Analog to digital converter (ADC) is given below. The input is Volts. The expression for the LSB of the output as a Boolean function of and is

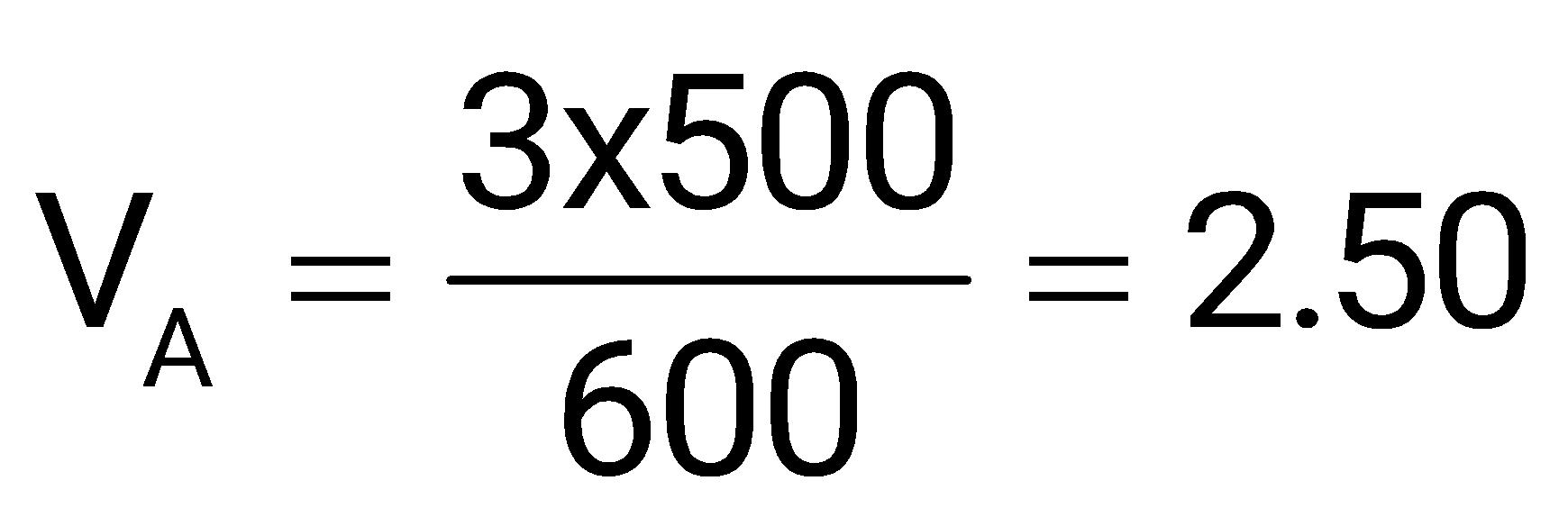

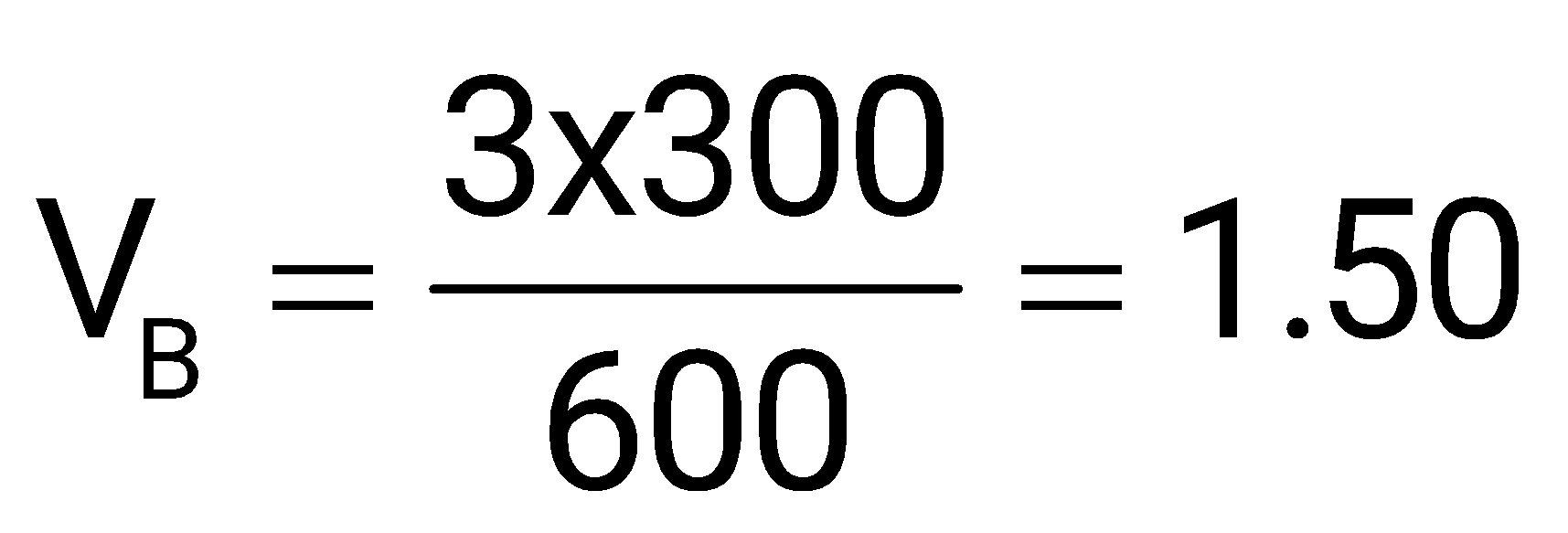

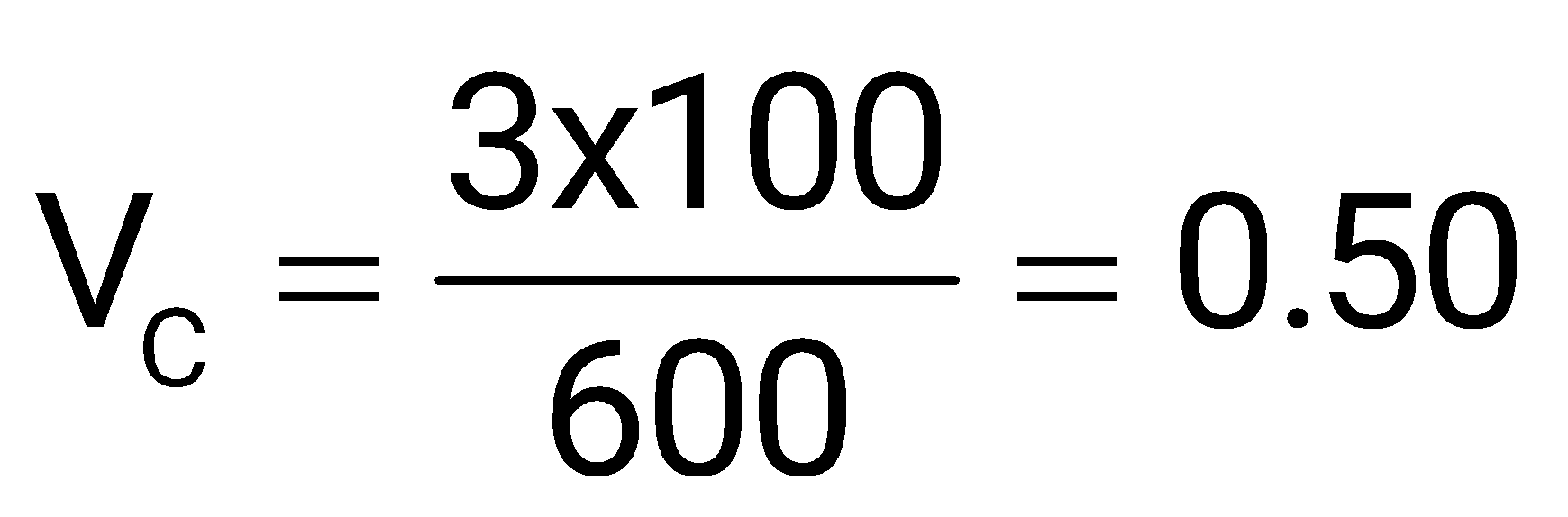

By potential divider rule:

V

V

V

An 8-bit, unipolar successive approximation register type ADC is used to convert 3.5V to digital equivalent output. The reference voltage is +5V. The output of the ADC, at the end of 3rd clock pulse after the start of conversion, is

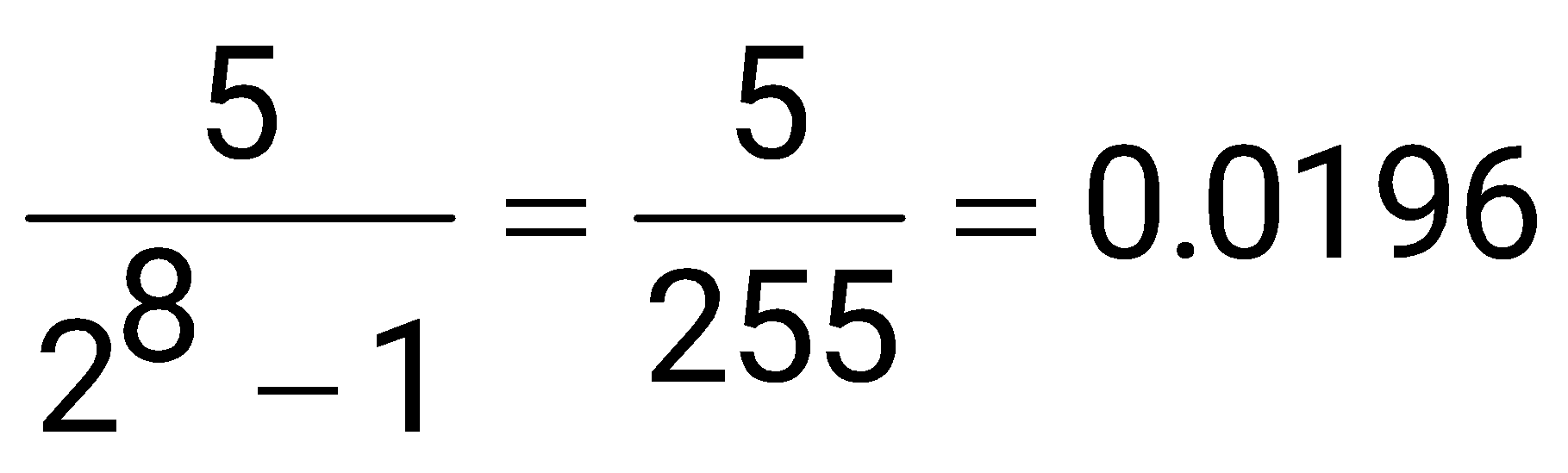

Resolution =

Output after 1st clock pulse = (10000000)2 = (128)10

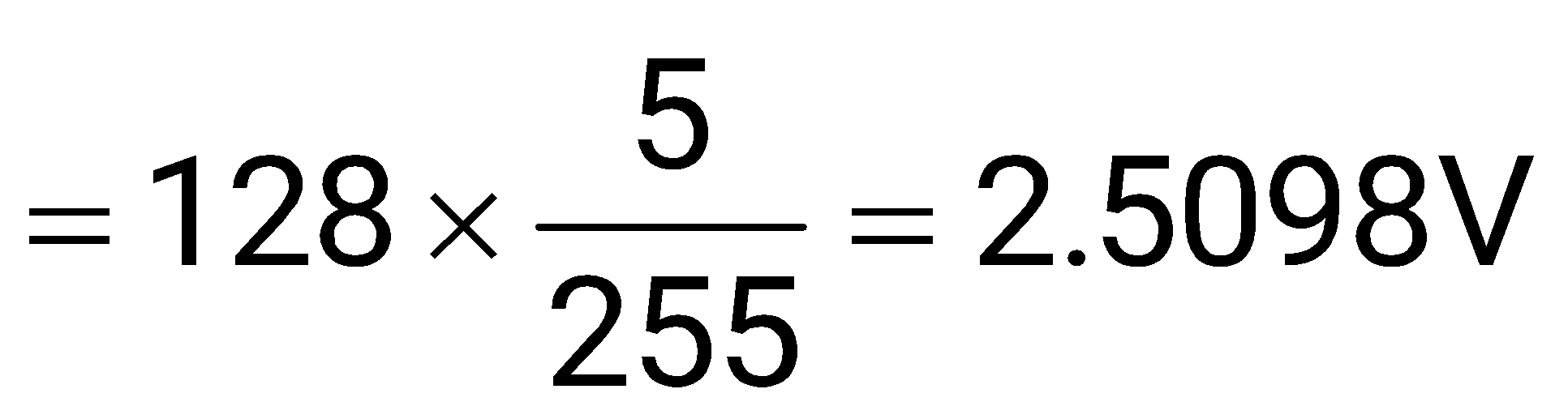

Voltage equivalent

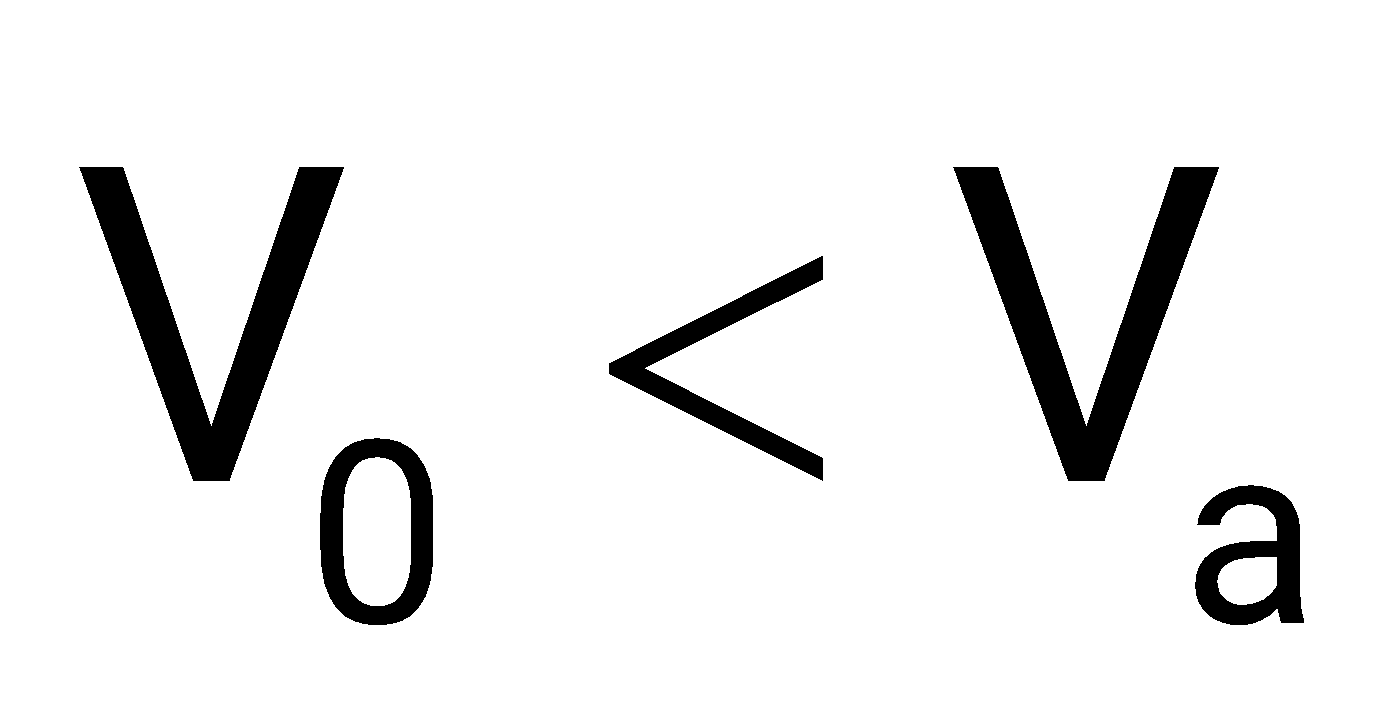

, so next bit will be set in the next clock cycle.

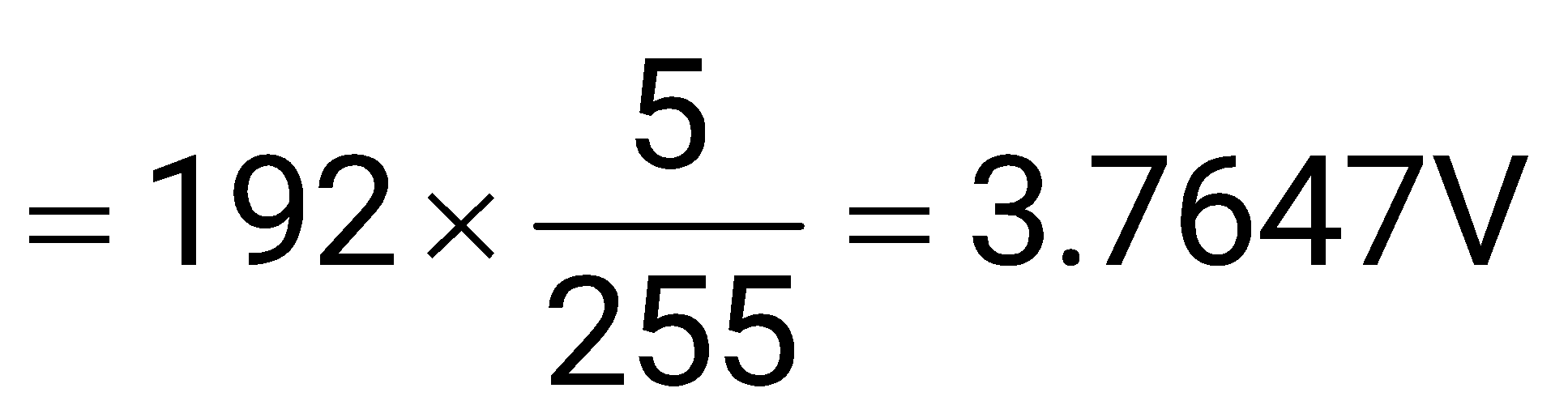

Output after 2nd clock pulse = (11000000)2 = (192)10

Voltage equivalent

, so this bit is reset and next bit will be set.

Therefore, output after 3rd clock pulse = (10100000)2

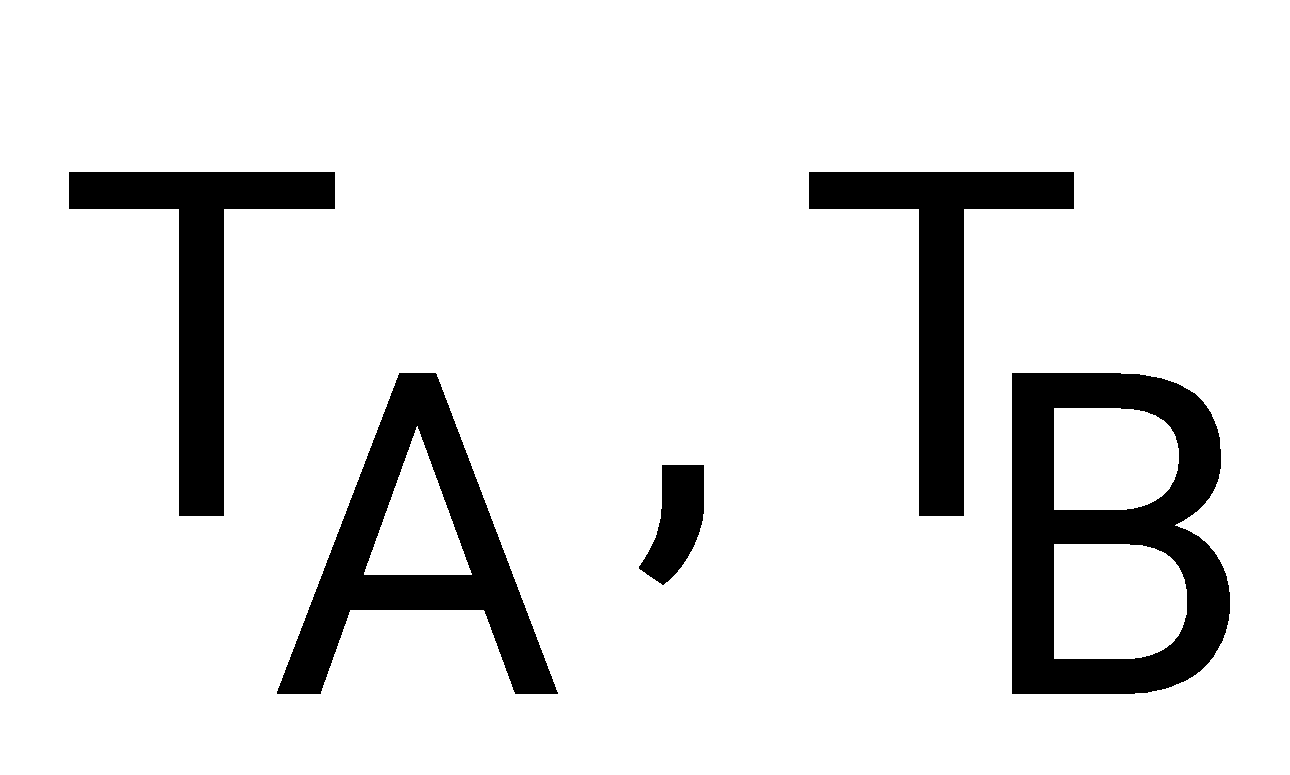

Two 8-bit ADCs, one of single slope integrating type and other of successive approximation type, take and times to convert 5V analog input signal to equivalent digital output. If the input analog signal is reduced to 2.5V, the approximate lime taken by the two ADCs will respectively be

In slope integrating type ADCs, the conversion time depends on the value of the input signal but in SAR the conversion time is independent of the magnitude of the input sampled value.

Hence option (b) is correct.

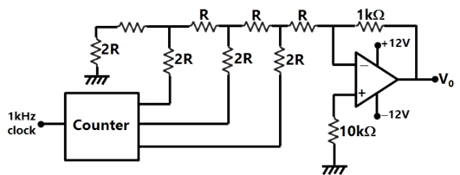

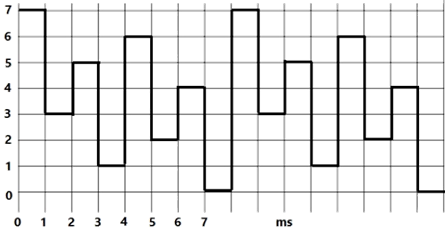

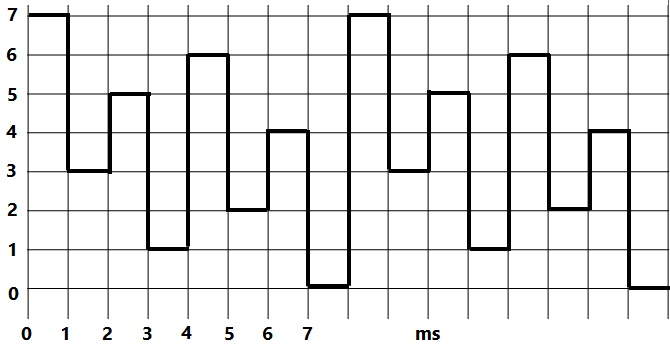

A student has made a 3-bit binary down counter and connected to the R- 2R ladder type DAC [Gain = (-1 kΩ/2R)] as shown in figure to generate a staircase waveform. The output achieved is different as shown in figure. What could be the possible cause of this error?

Since, it is a down counter it will count from 7 to 0. When the counter count is 7 (111) the DAC output is corresponding to 7 input (111) from the waveform.

When the down counter comes down to 6 (110), the DAC output is corresponding to 3 (011) and when the count comes down to 5 (101), the DAC output is corresponding to 5 (101).

So, from this we conclude that MSB of counter is connected to LSB of DAC and vice versa so the connection is not proper.

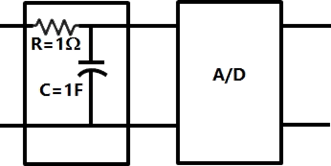

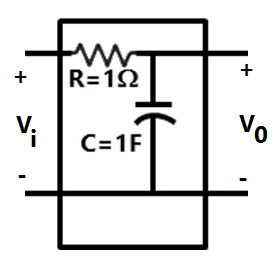

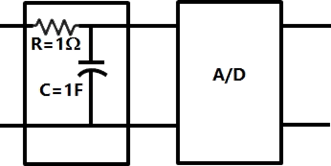

It is required to design an anti-aliasing filter for an 8 bit ADC. The filter is a first order RC filter with R = 1Ω and C = 1F. The ADC is designed to span a sinusoidal signal with peak to peak amplitude equal to the full range of the ADC.

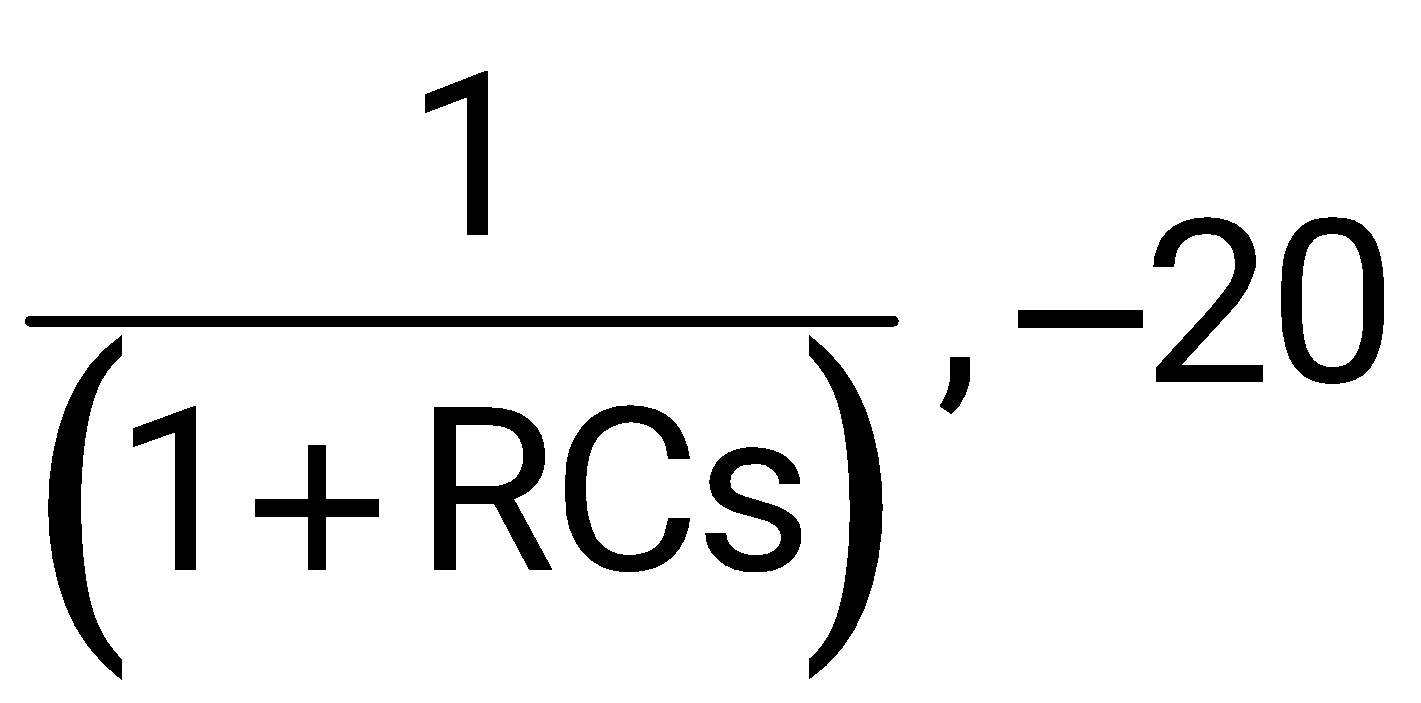

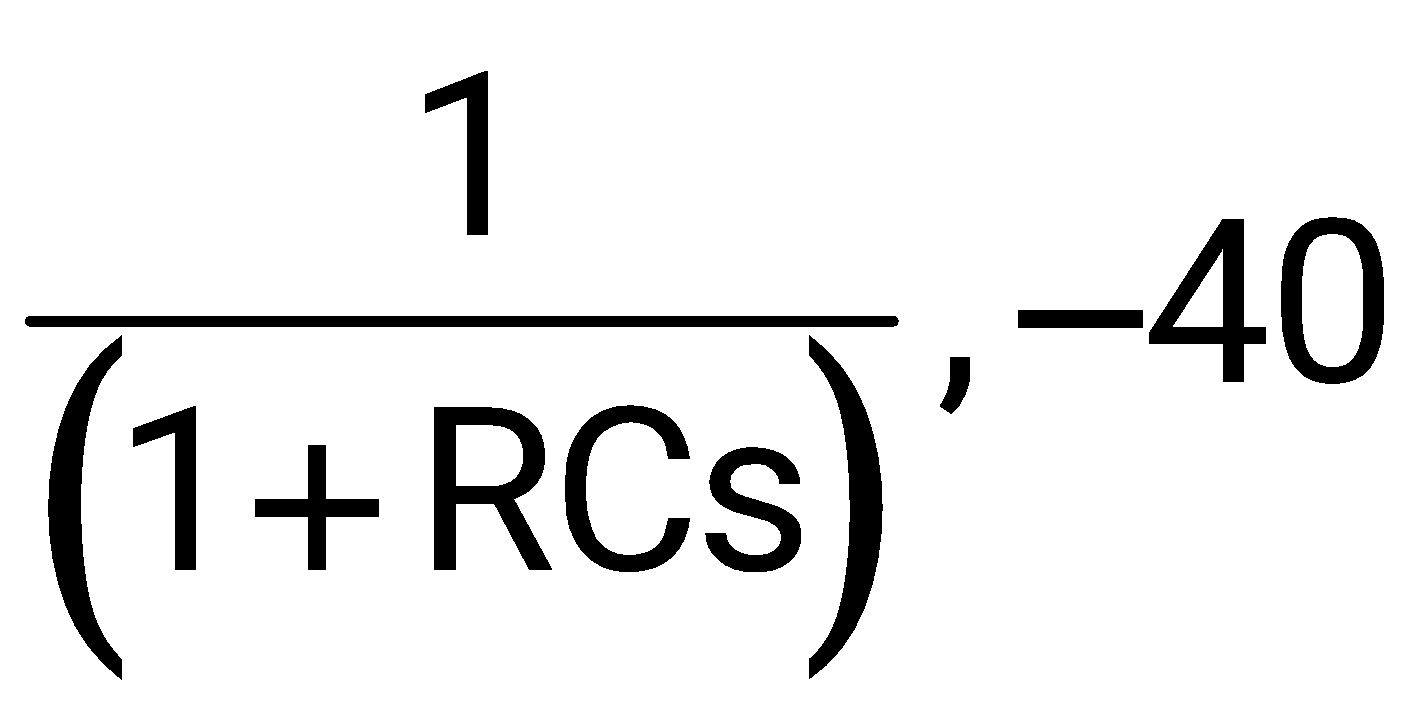

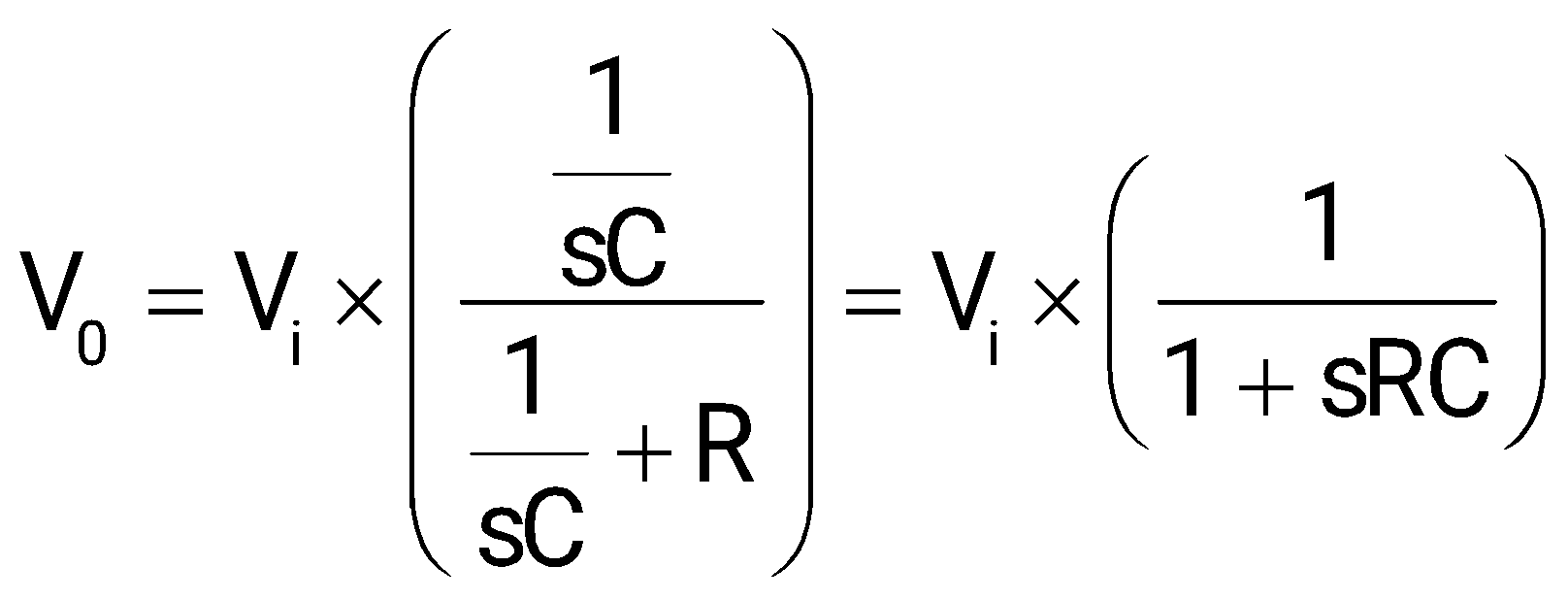

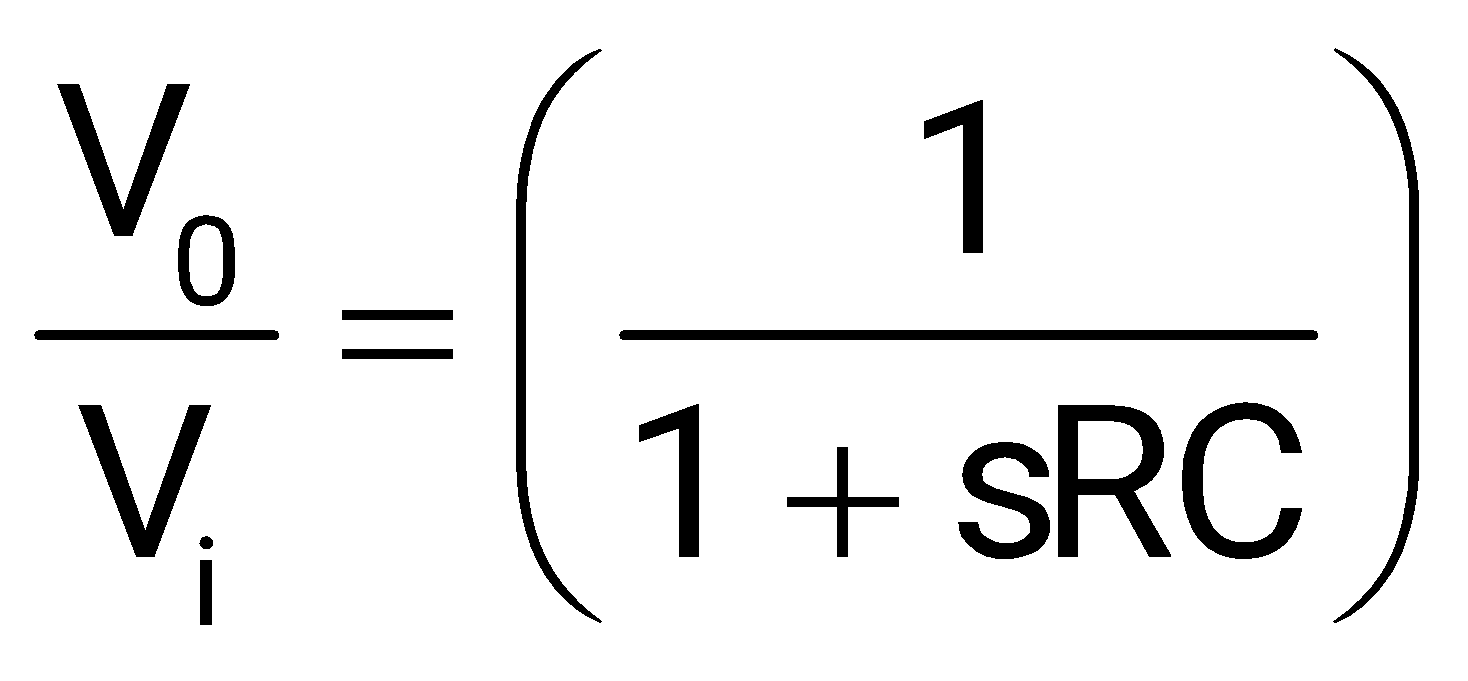

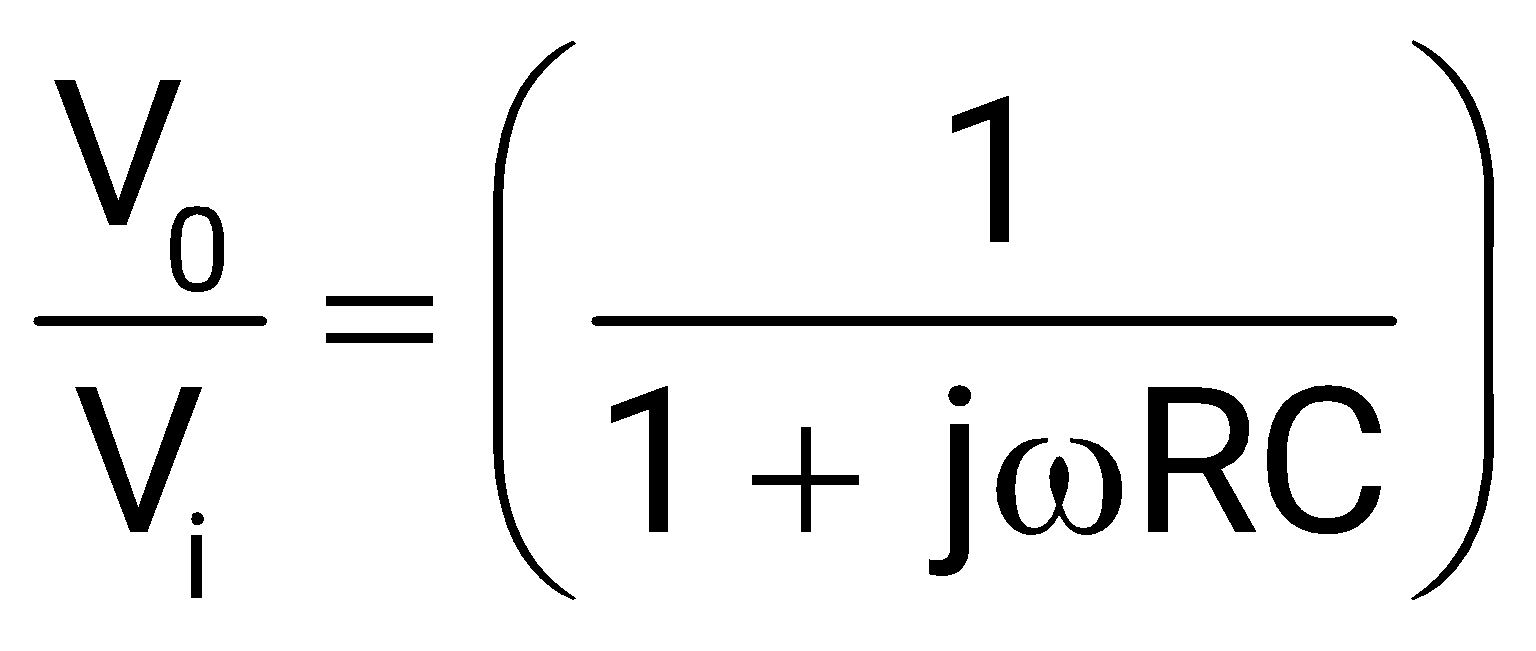

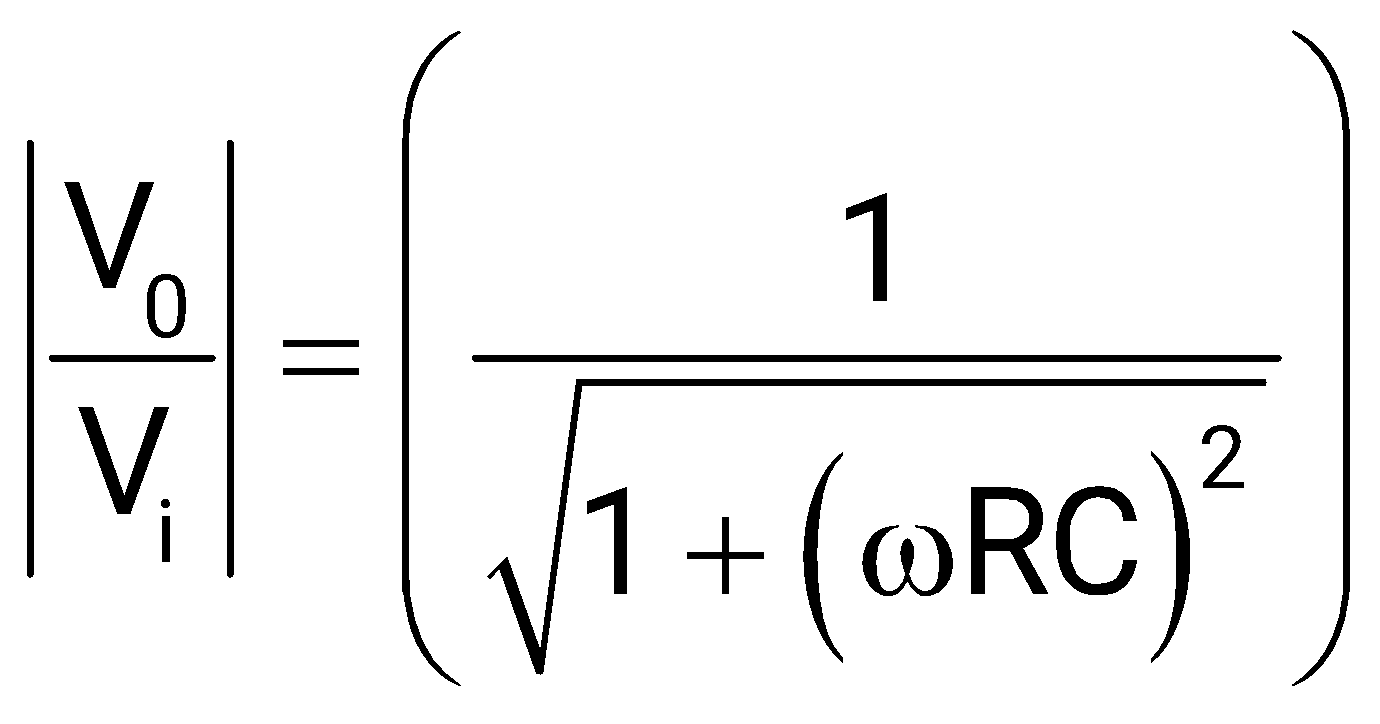

The transfer function of the filter and its roll off respectively are

Transfer function of RC Filter

For nth-order filter roll-off slope = “n x -20dB/decade”.

For first order filter roll off = -20dB/decade

It is required to design an anti-aliasing filter for an 8 bit ADC. The filter is a first order RC filter with R = 1W and C = 1F. The ADC is designed to span a sinusoidal signal with peak to peak amplitude equal to the full range of the ADC.

What is the SNR (in dB) of the ADC? Also find the frequency (in decades) at the filter output at which the filter attenuation just exceeds the SNR of the ADC.

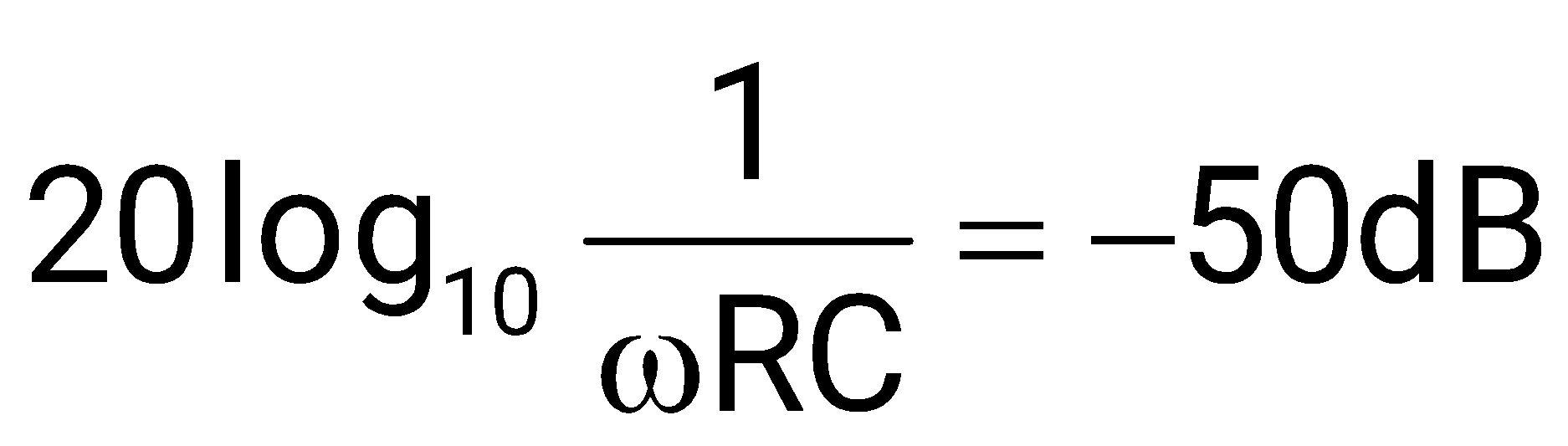

SNR for ADC = 6.02N+1.76dB

For 8 bit ADC

SNR=49.92 dB

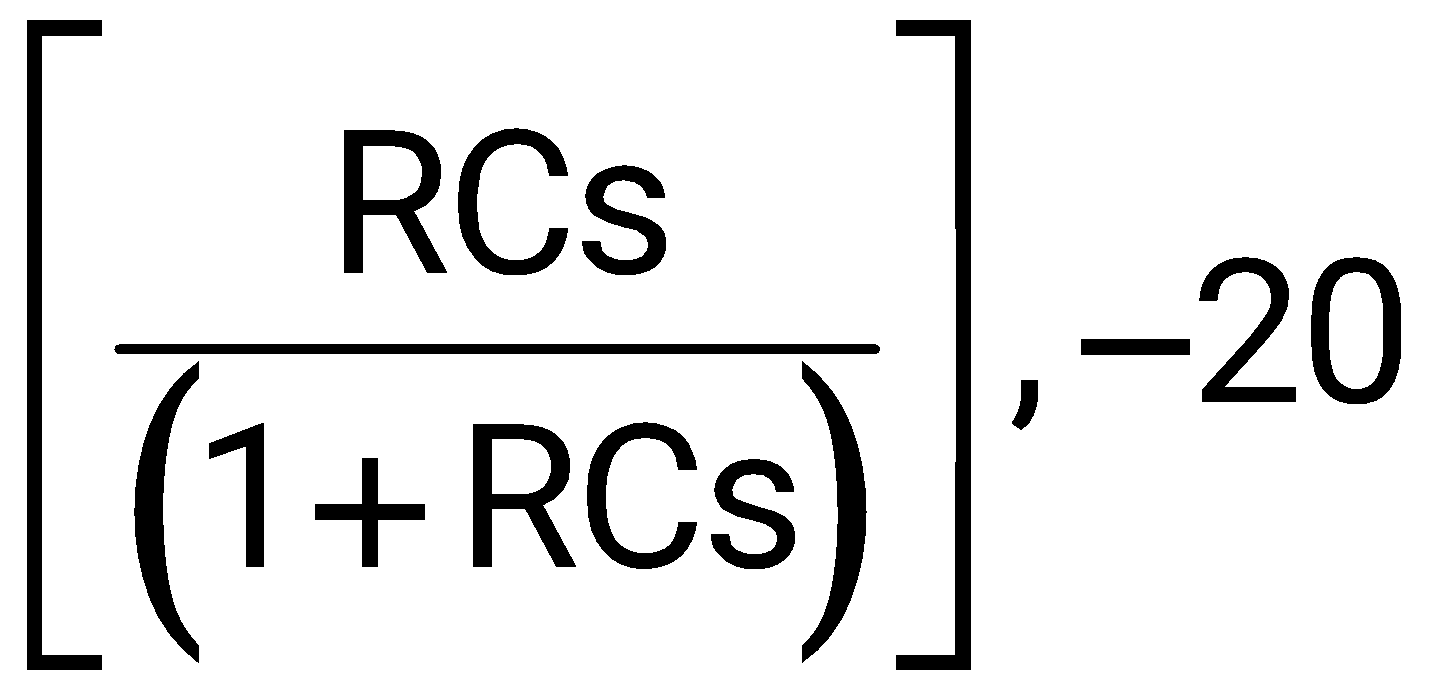

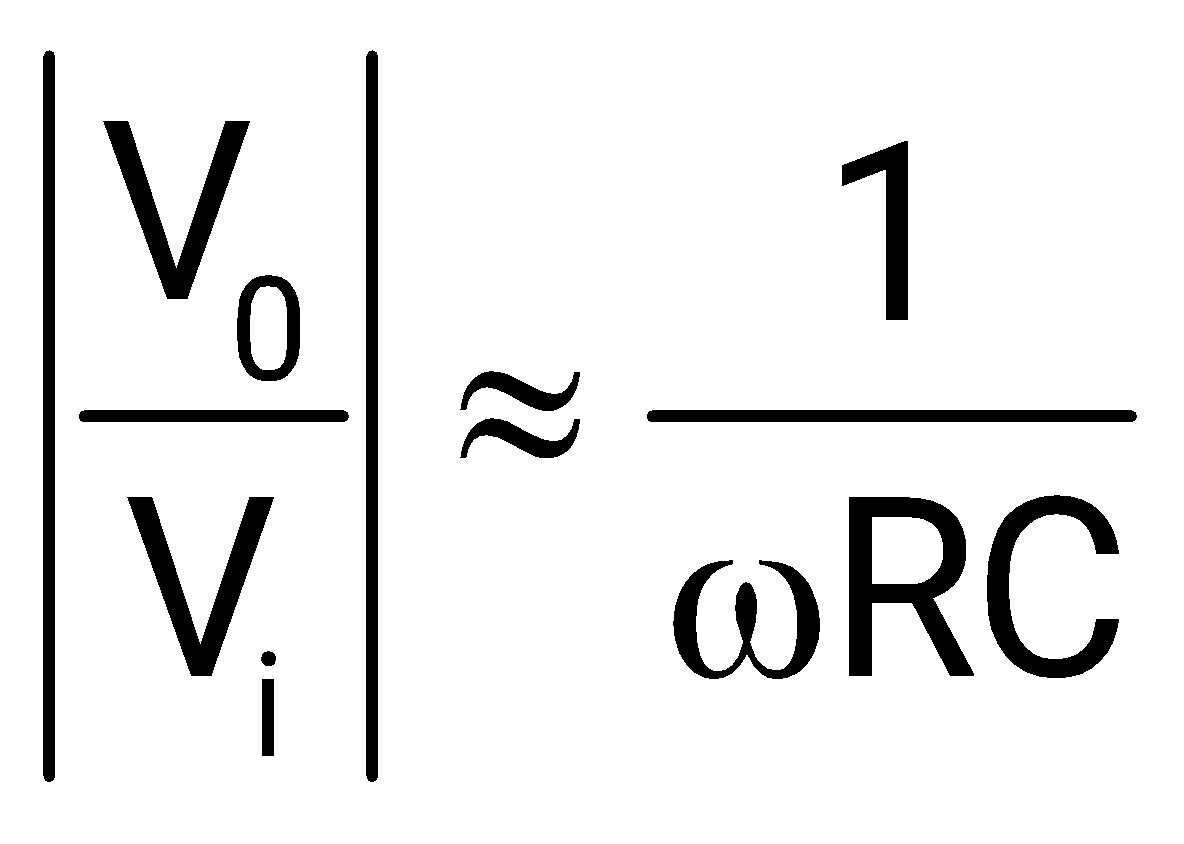

Transfer function of RC Filter

At high frequency

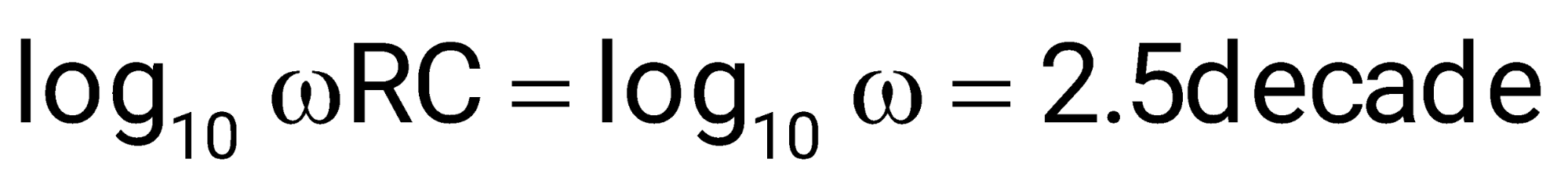

Attenuation in dB =

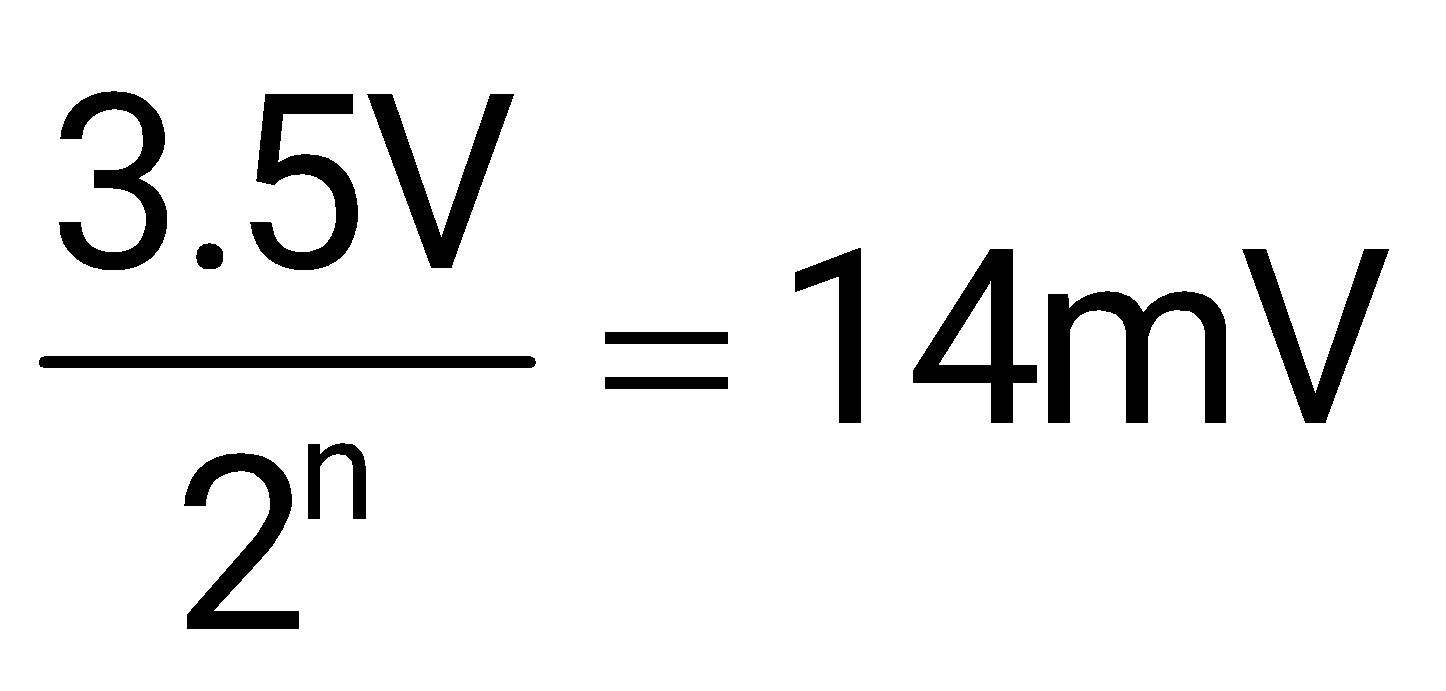

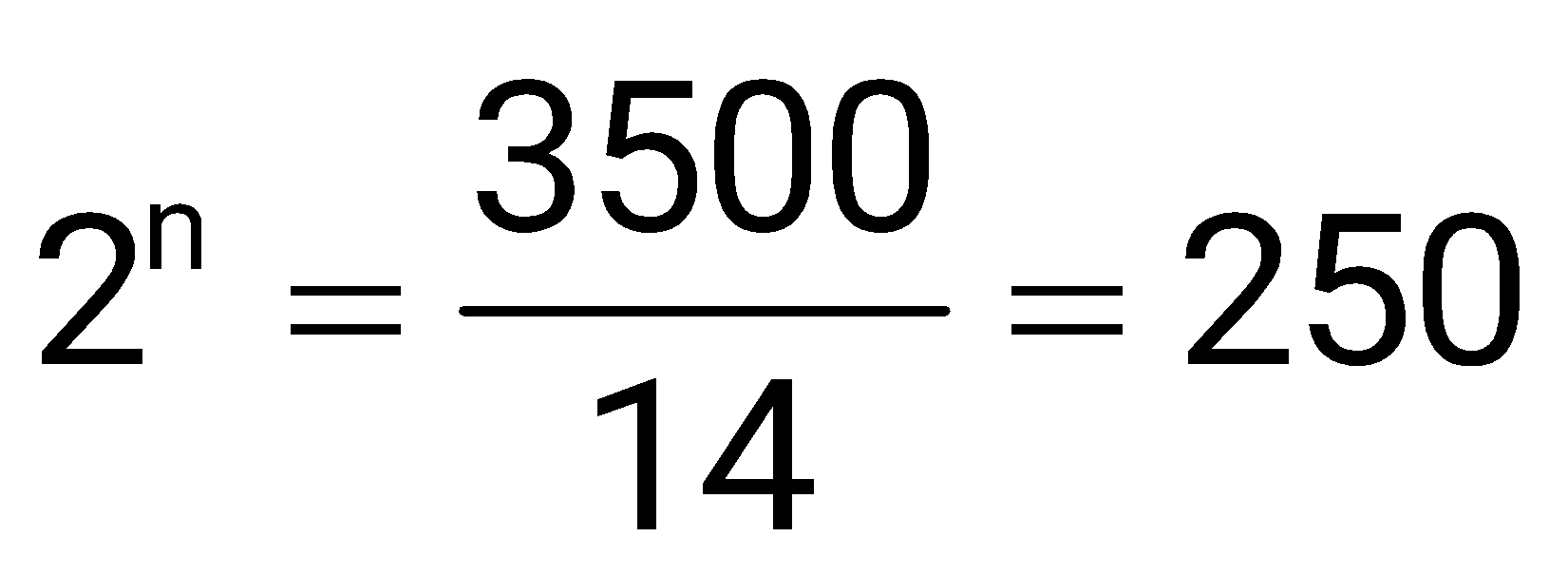

A digital-to-analog converter with a full-scale output voltage of 3.5V has a resolution close to 14 mV. Its bit size is:

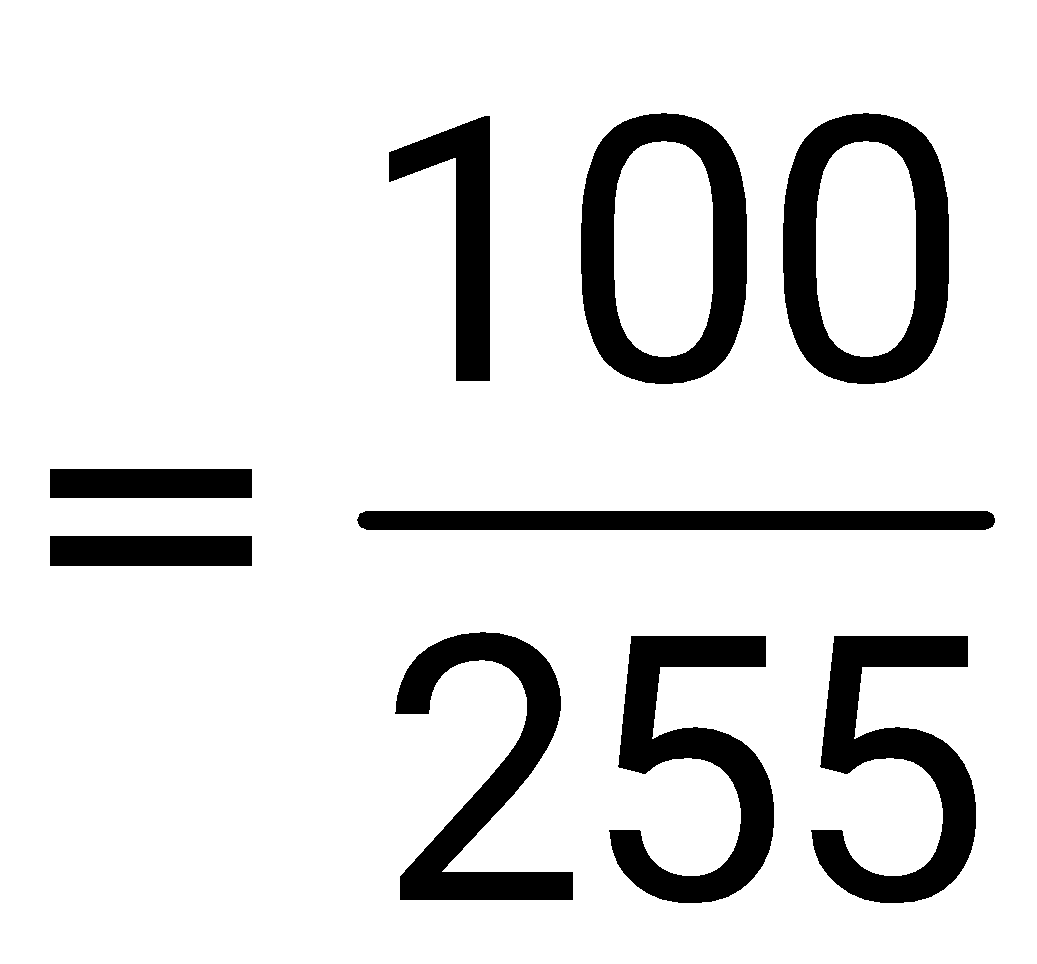

Resolution=

Thus, .

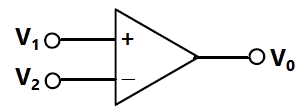

The voltage comparator shown in figure can be used in as

For V1 >V2 , Output V0 is high

For V1 <V2 , Output V0 is low

Since the output V0 has only two states high and low which can be represented by 1 bit.

Hence this can be used as 1 bit quantizer in the analog-to-digital conversion

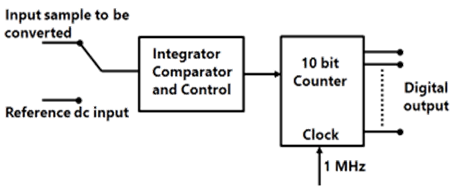

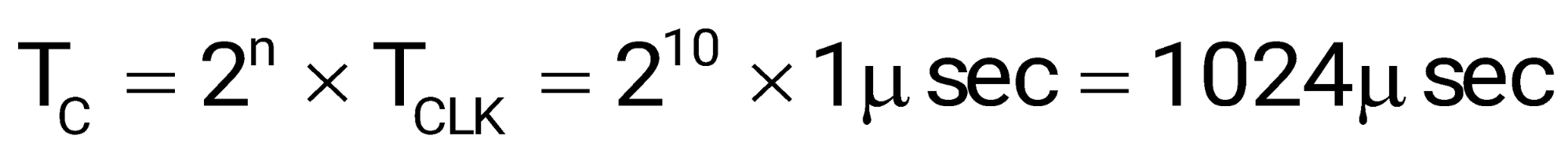

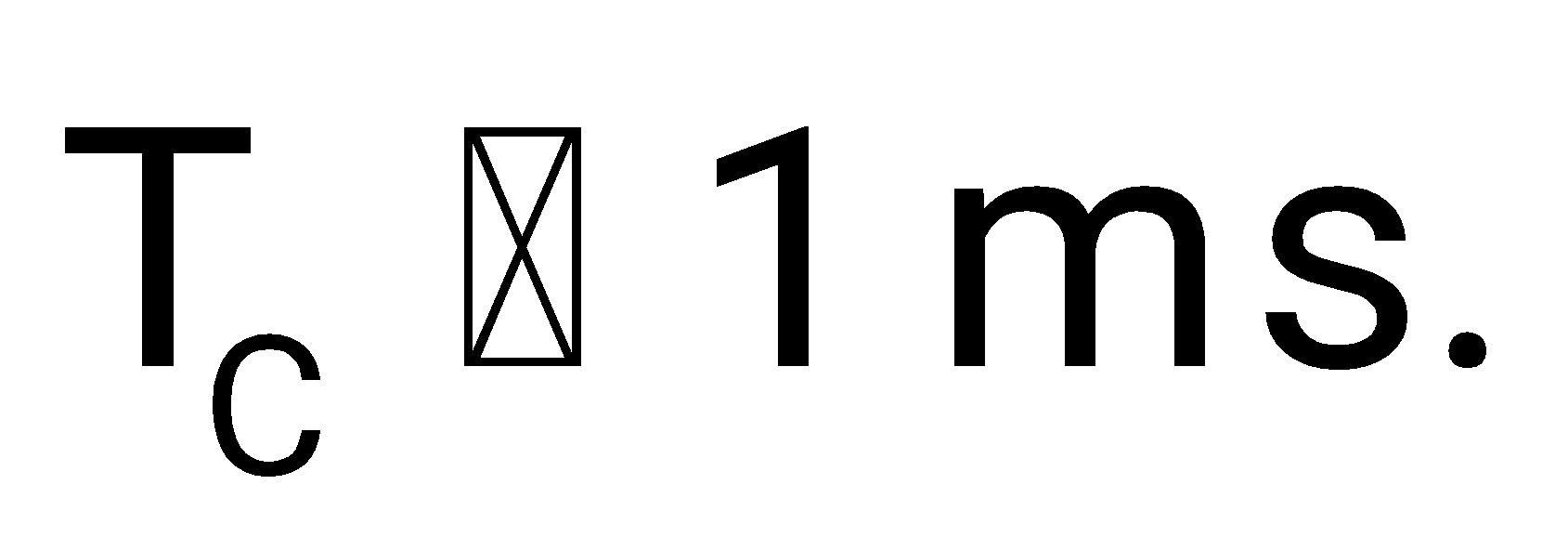

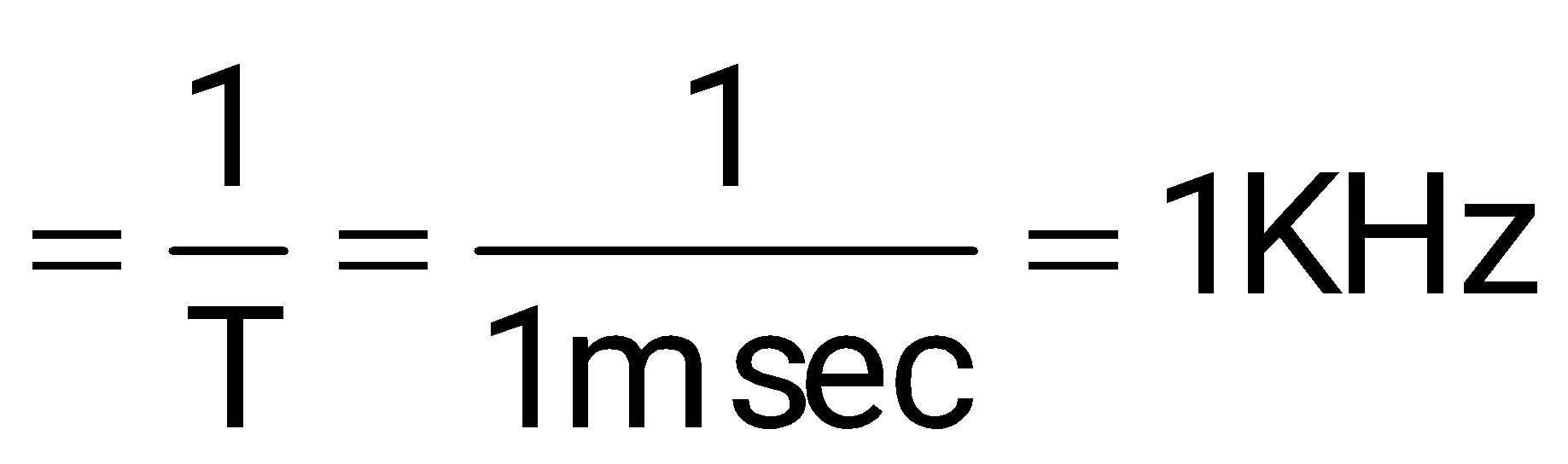

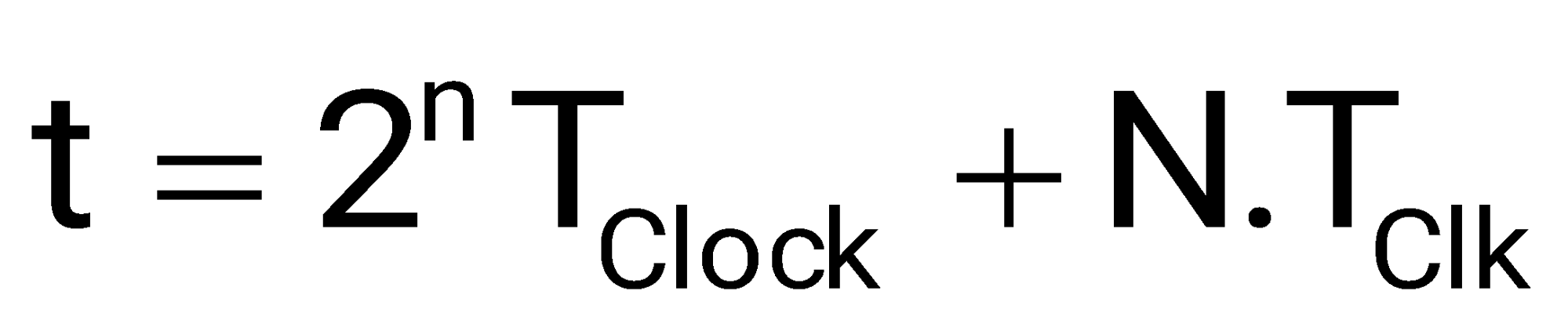

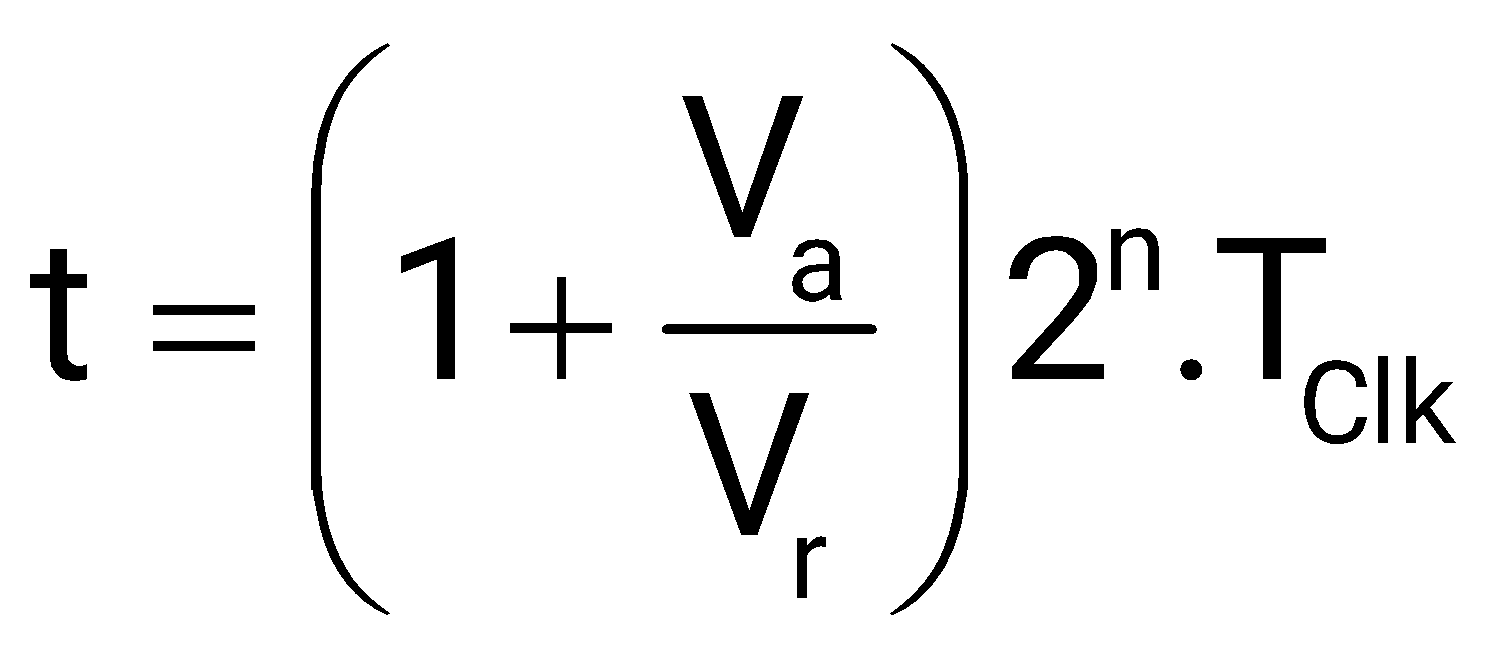

The simplified block diagram of a 10-bit A/D converter of dual slope integrator type is shown in figure. The 10-bit counter at the output is clocked by a 1MHz clock. Assuming negligible timing overhead for the control logic, the maximum frequency of the analog signal that can be converted using this A/D converter is approximately

Minimum conversion time of dual slope ADC

Maximum sampling frequency

Among the following four, the slowest ADC (analog-to-digital converter) is

The increasing order of speed of the comparator is given by,

Integrating type < Counting < Successive Approximation type< Flash type

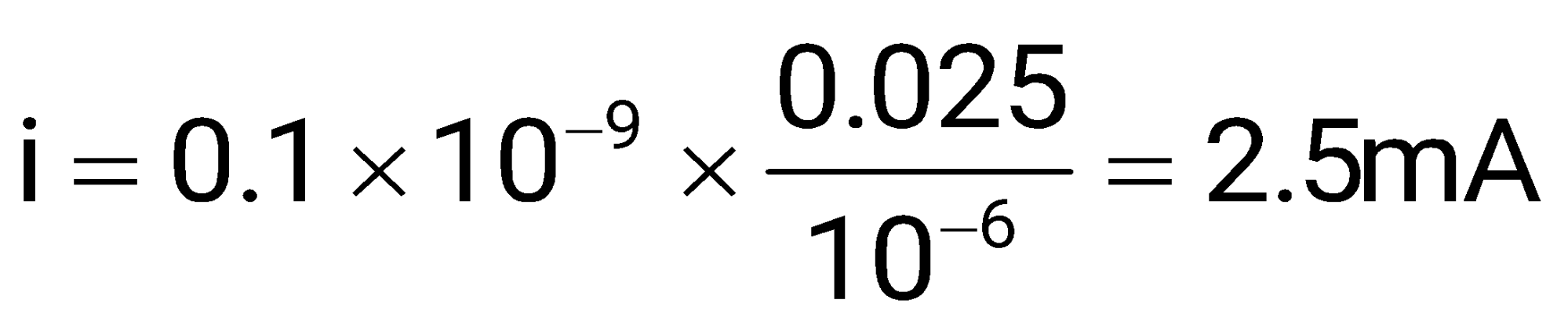

A sample-and-hold (S/H) circuit, having a holding capacitor of 0.1nF, is used at the input of an ADC (analog-to-digital converter). The conversion time of the ADC is 1µsec, and during this time, the capacitor should not lose more than 0.5% of the charge put across it during the sampling time. The maximum value of the input signal to the S/H circuit is 5V. The leakage current of the S/H circuit should be less than

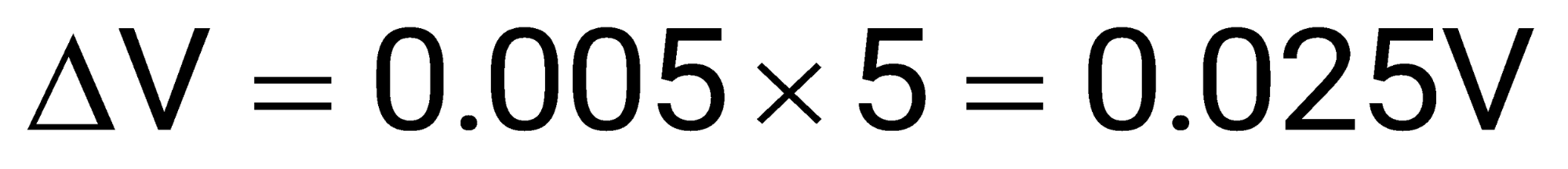

Change in voltage during sampling time = 0.5% of 5V

Leakage current through the capacitor =

Where is the sampling time

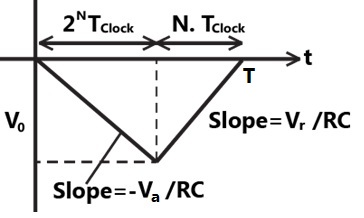

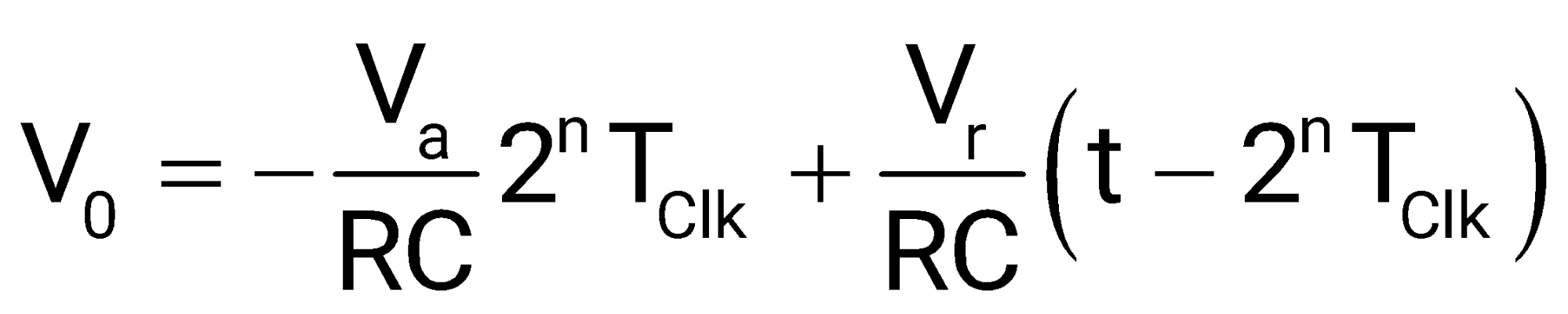

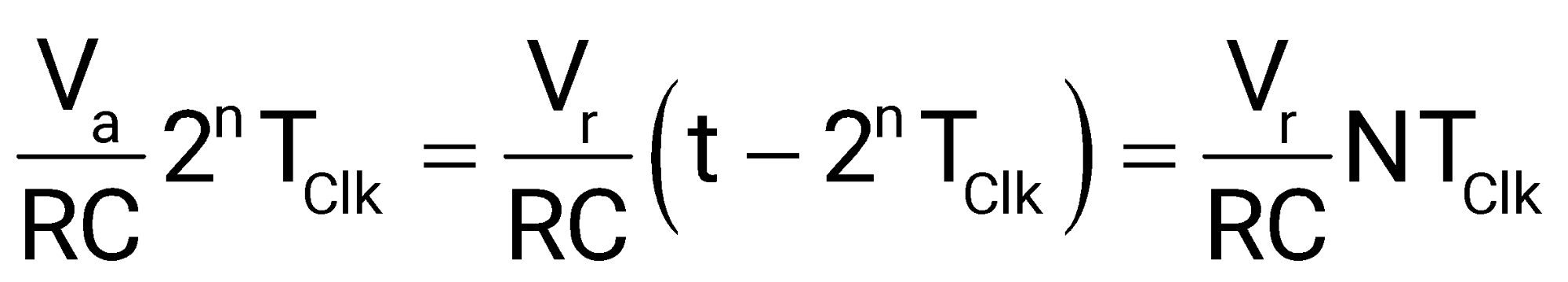

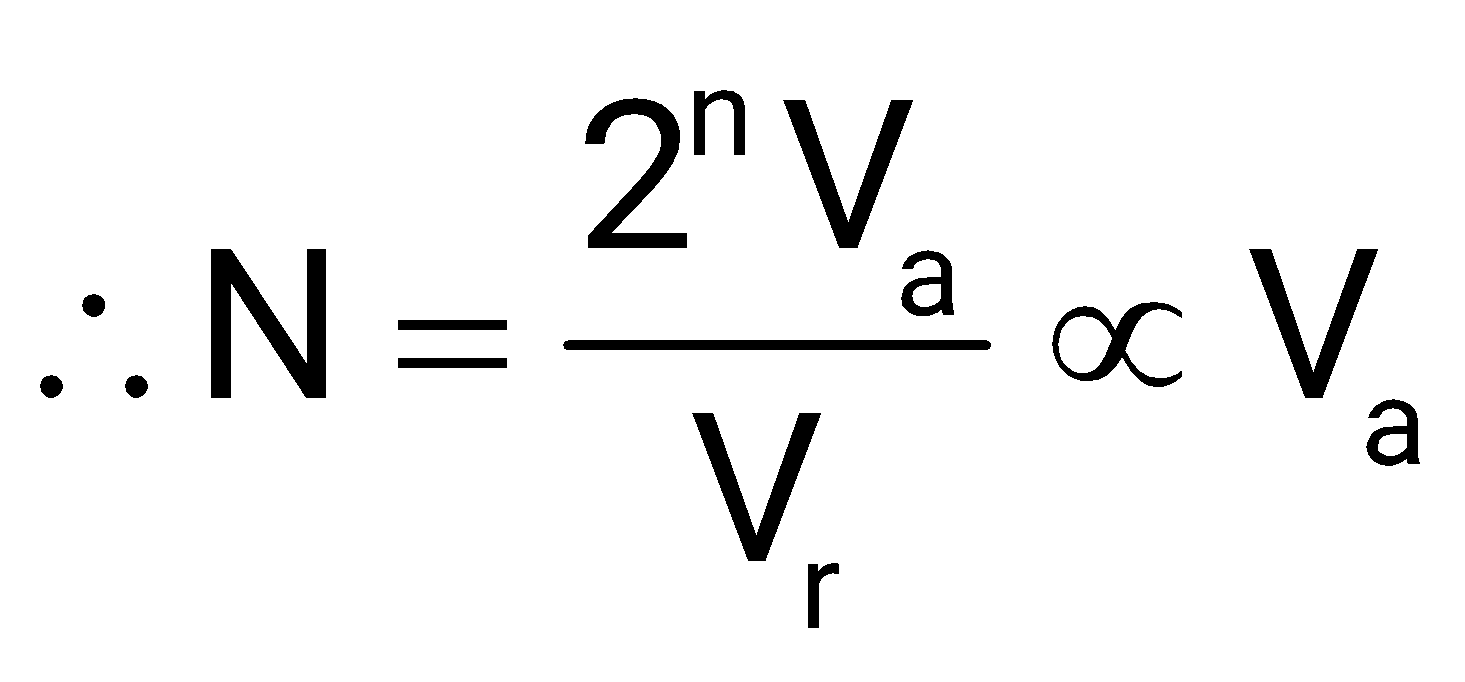

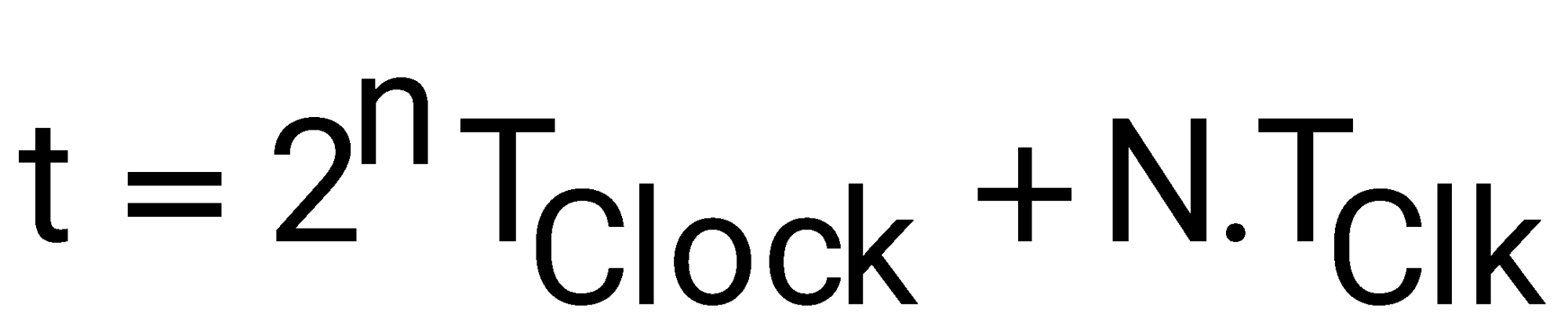

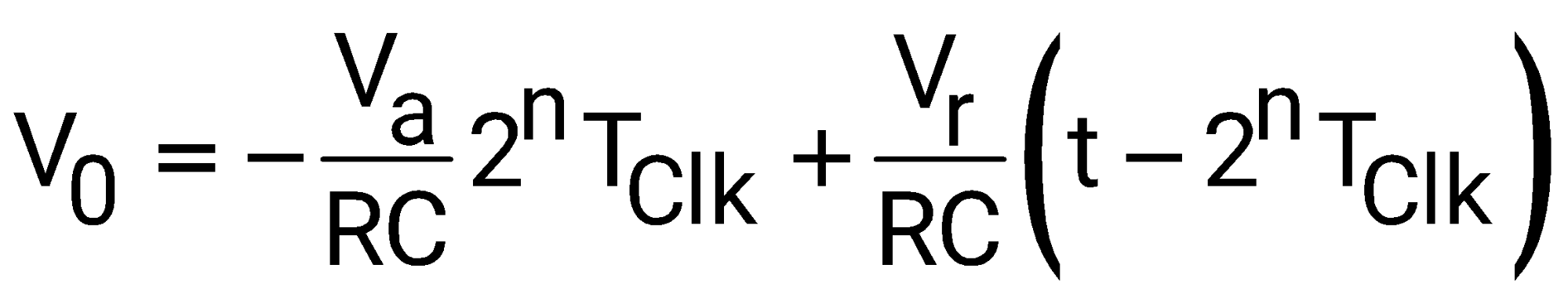

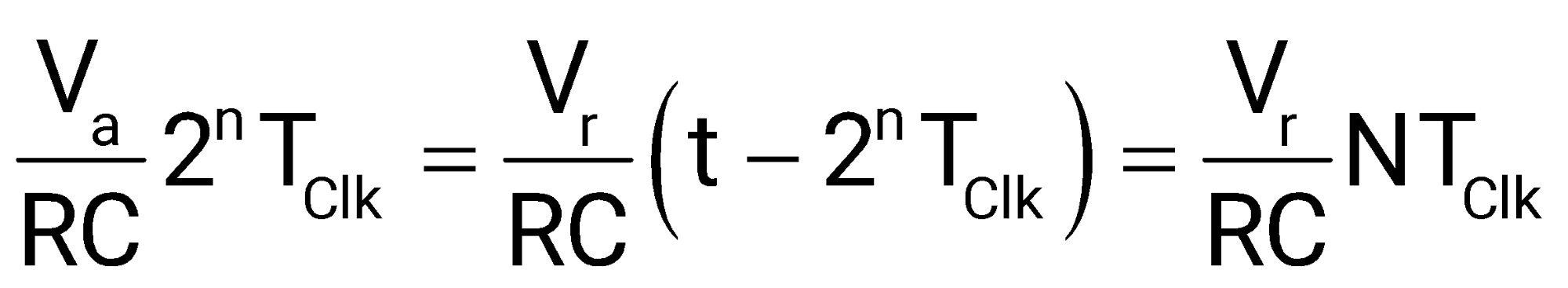

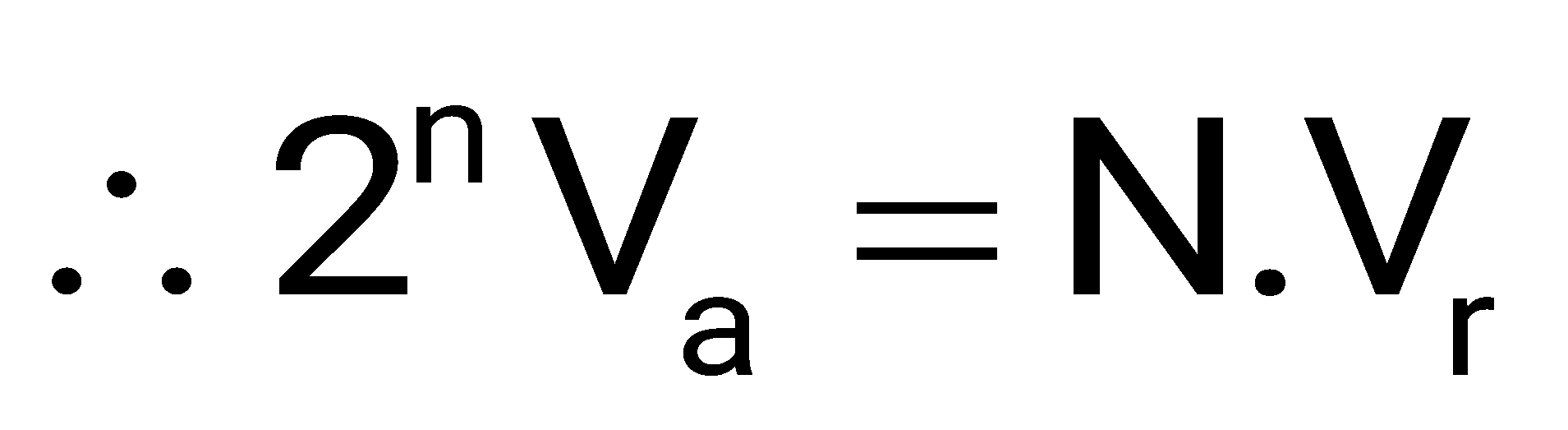

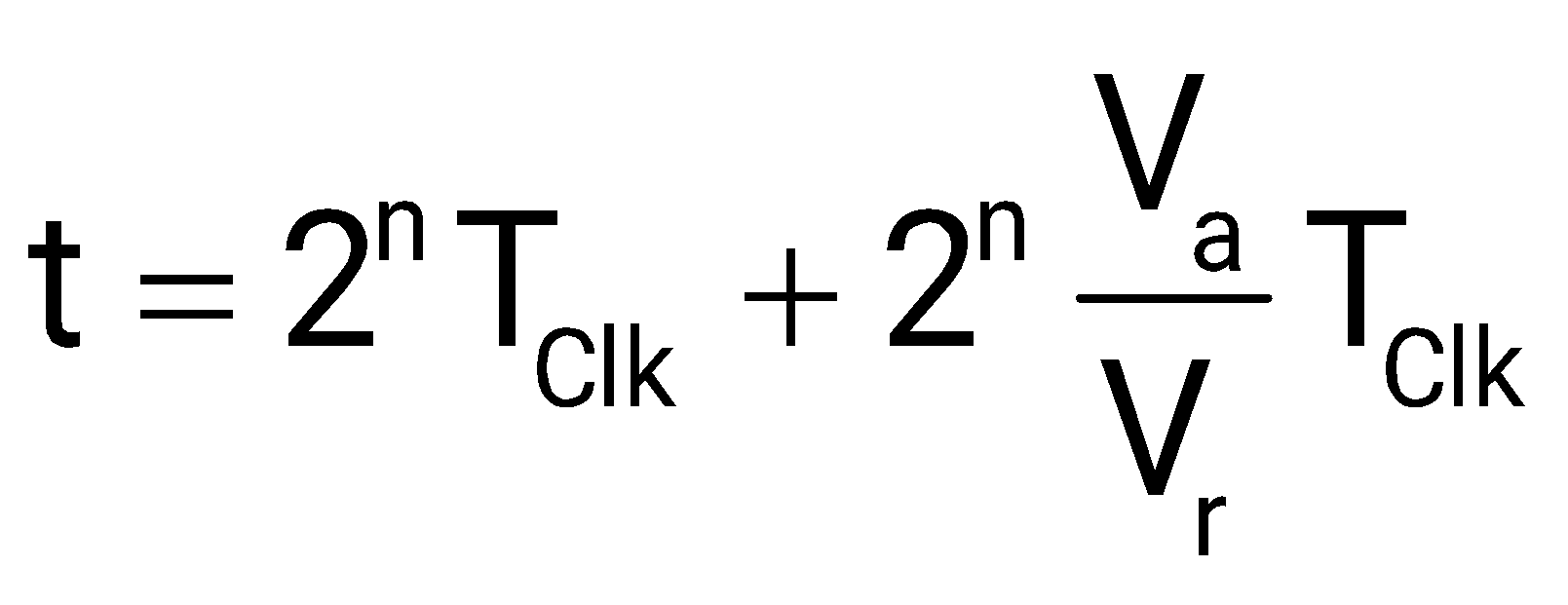

A dual slope analog-to-digit converters uses an N-bit counter. When the input signal is being integrated, the counter is allowed to count up to a value

In dual slope ADC

We know that total conversion line

N can be obtained as

At t=T, V0 =0

Hence total number of count is proportional to Va.

A digit, 2 V full scale slope ADC has its integration time set to 300ms. If the input to the ADC is (1+1sin314t)V, then the ADC output will be

A 3.5 digit ADC just implies that it can count from 0 to 1999.The integration time and the clock rate of the counter are related such that a full-scale input (1.999V) gives 1999 counts. From this, you can infer that the clock speed is 2000 counts/300 ms = 6667 Hz. Therefore, a half-scale input will give half the count in the counter, or 1000 counts.

The only reason the integration time was given was so that you would realize that it incorporates only whole cycles of the AC frequency, and since the mean value of a sine wave is zero, it contributes nothing to the final reading.

The number of comparisons carried out in a 4-bit flash-type A/D converter is_________?

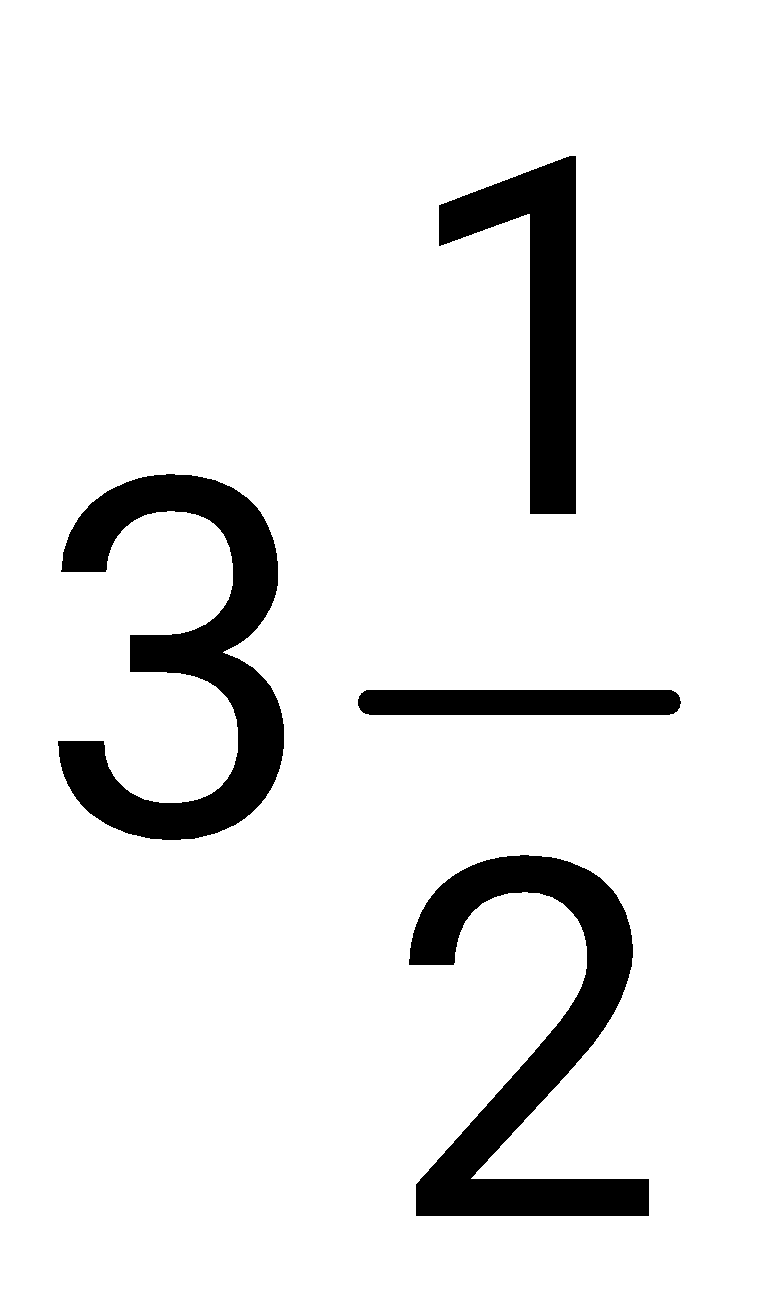

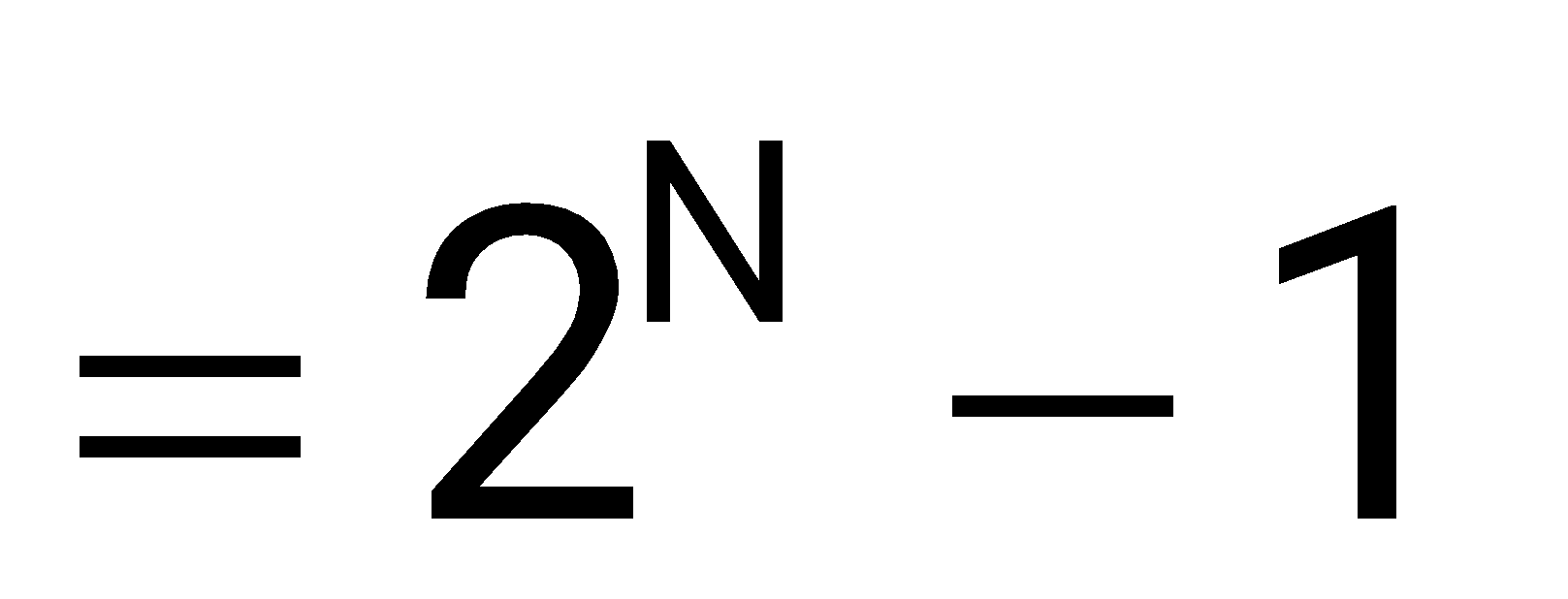

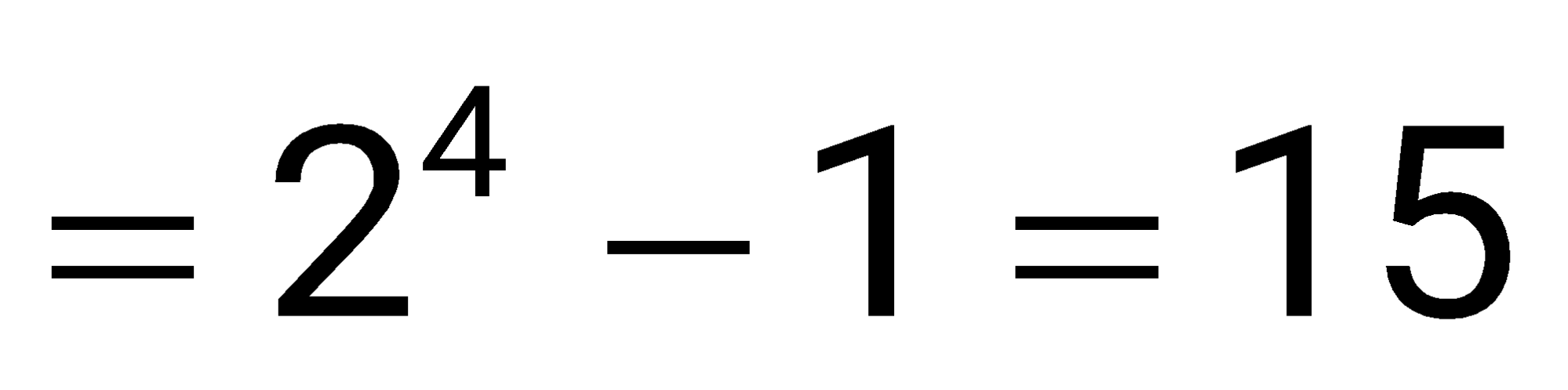

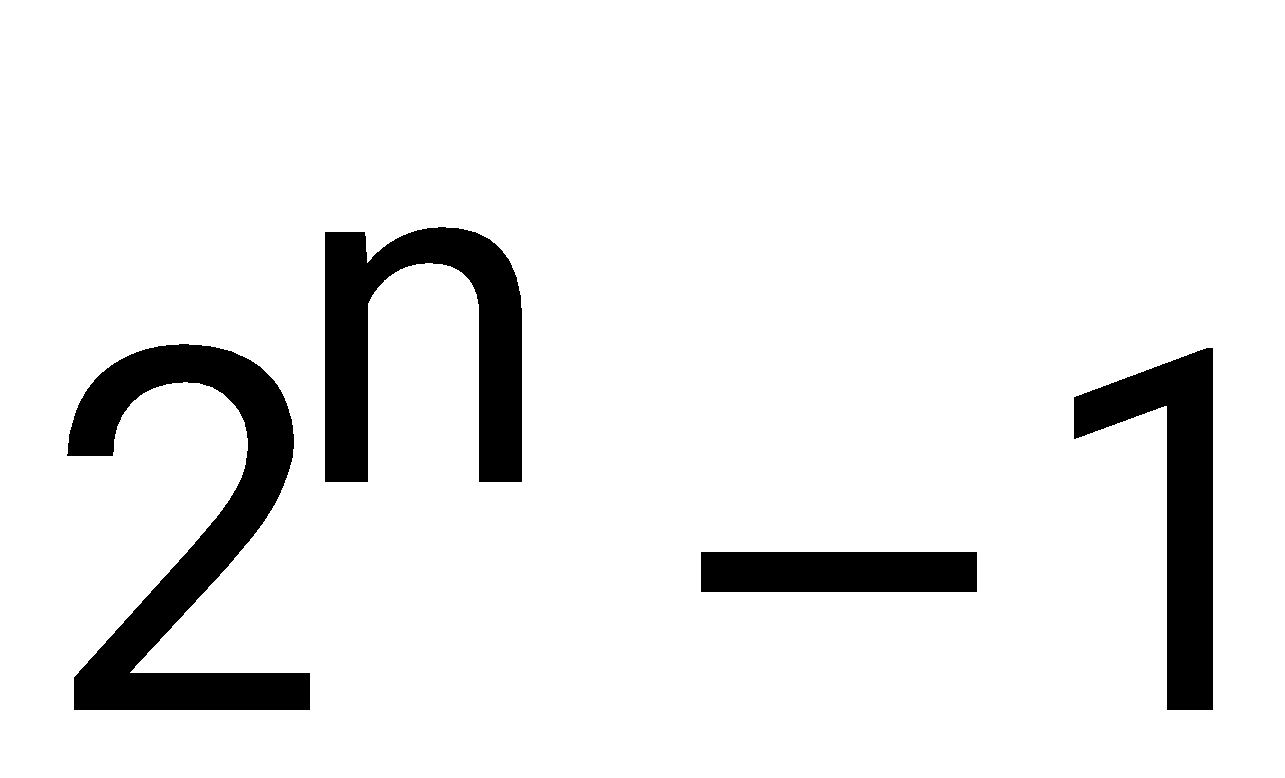

For an N-bit Flash comparator ADC,

Number of comparators

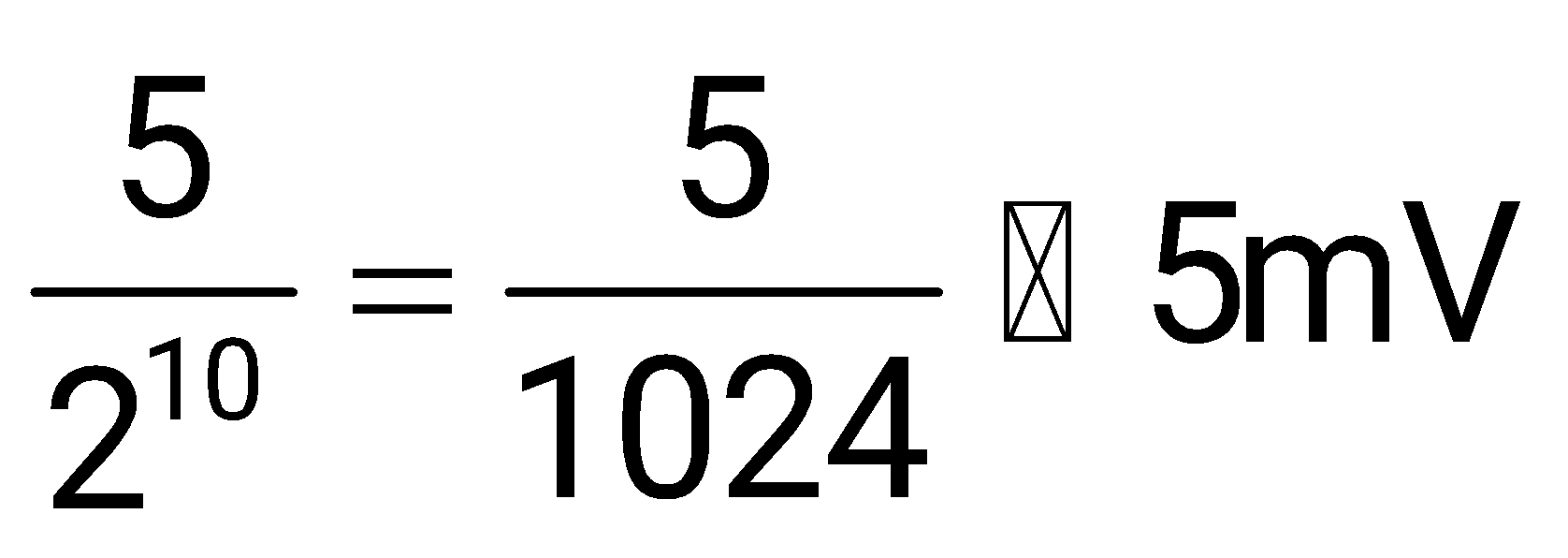

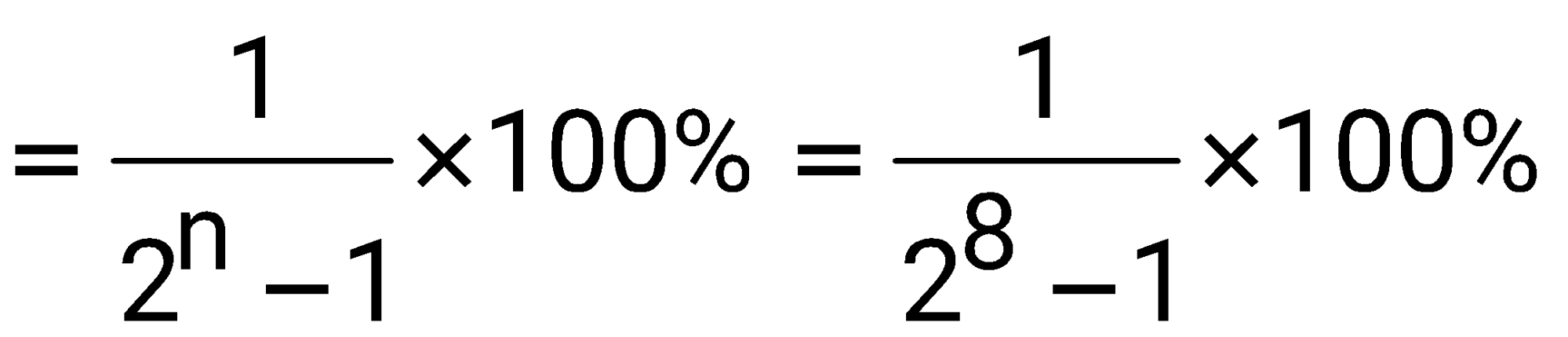

A 10 bit A/D converter is used to digitize an analog signal in the 0 to 5V range. The maximum peak to peak ripple voltage that can be allowed in the D.C. supply voltage is

Resolution=.

The maximum peak to peak ripple variation in DC supply voltage cannot exceed the LSB or the resolution of the ADC. So maximum peak to peak ripple voltage=5mV

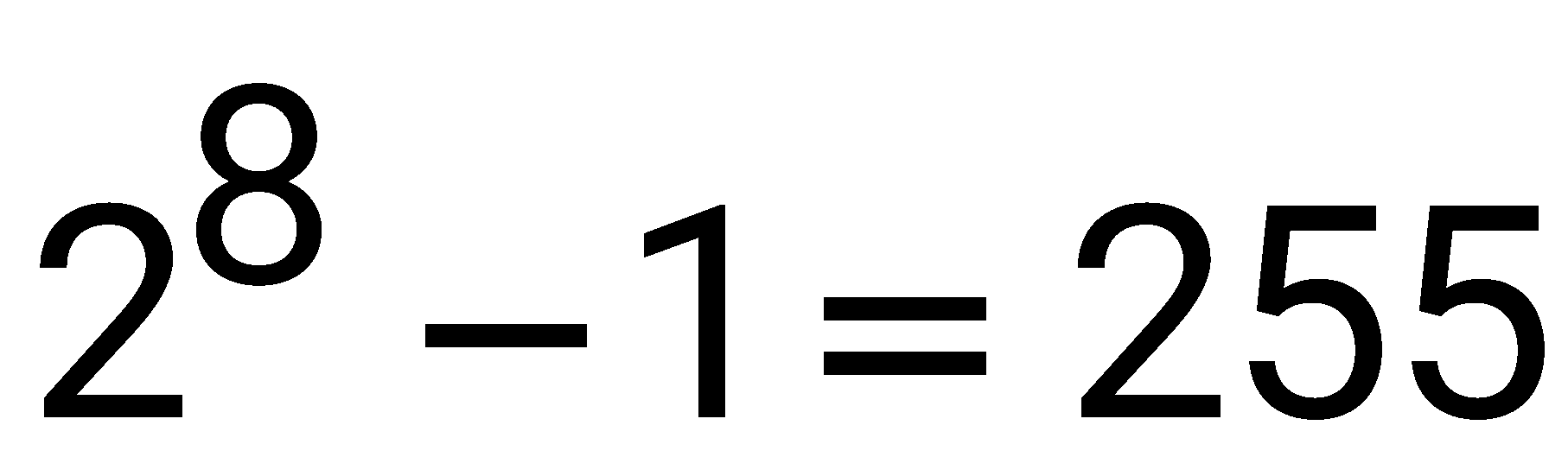

The number of comparators needed in a parallel conversion type 8-bit A to D converter is

For n bit parallel Analog to digital converter

No of comparator required=

So for 8-bit= comparators.

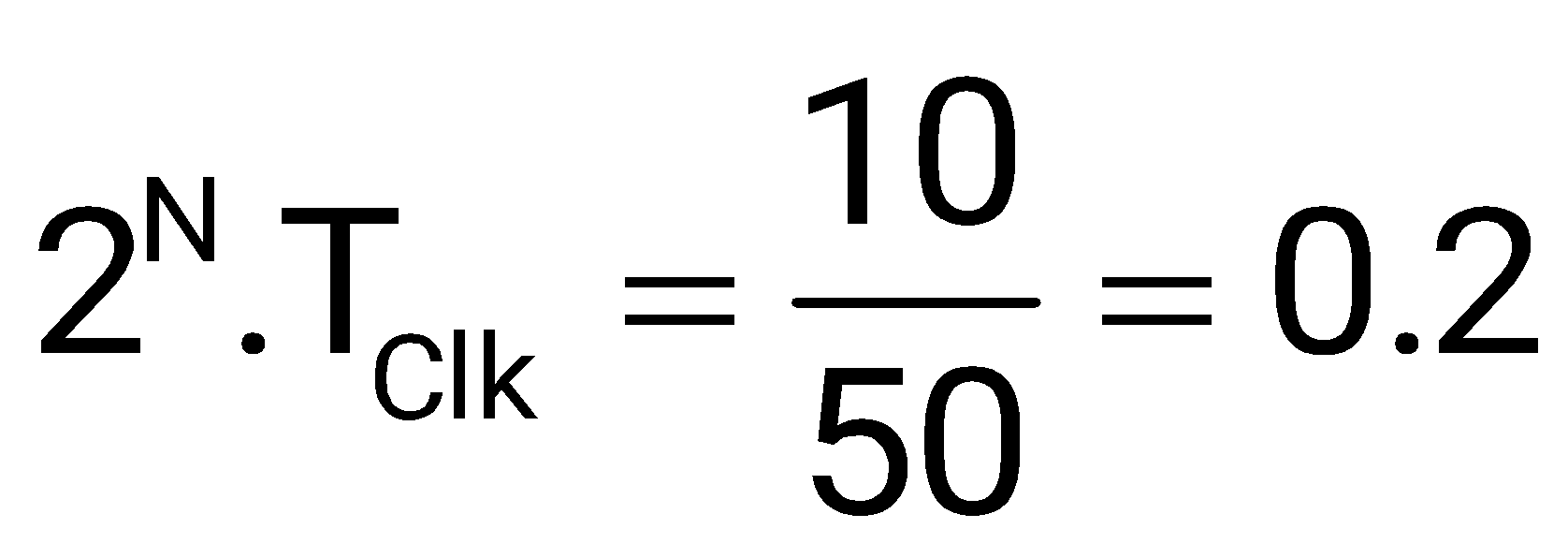

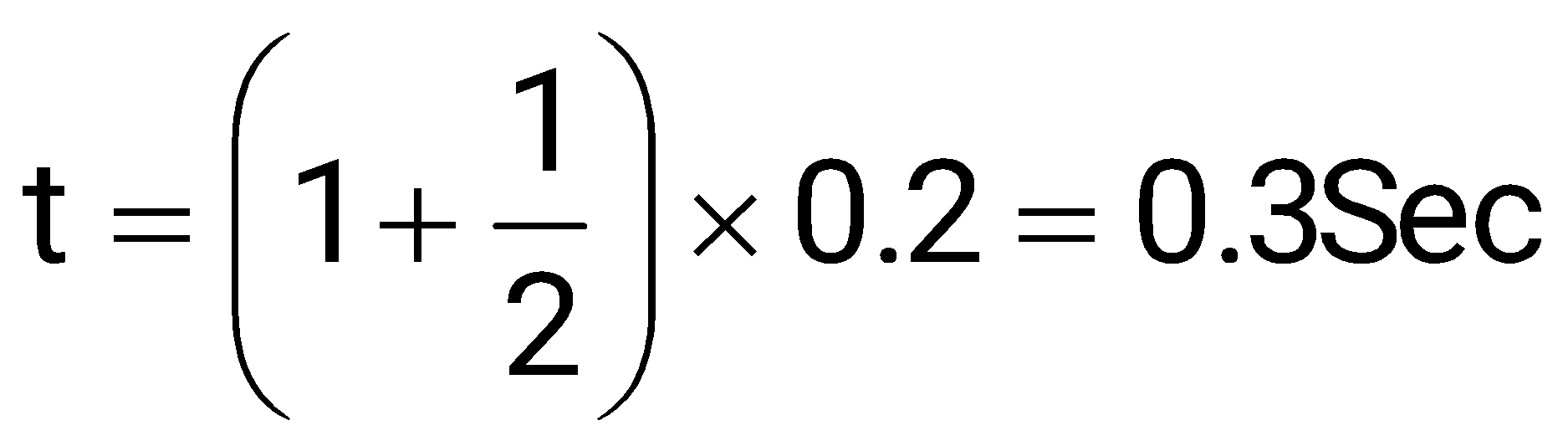

In a dual slope integrating type digital voltmeter the first integration is carried out for 10 periods of the supply frequency of 50 Hz. If the reference voltage used is 2 V, the total conversion time for an input 1V is ___________ sec

In dual slope ADC

We know that total conversion line

N can be obtained as

At t=T, V0 =0

Given

Since the first integration is carried out for 10 periods of supply frequency,