Digital Electronics

Combinational Circuits

Practice questions from Combinational Circuits.

26

Total0

Attempted0

Correct0

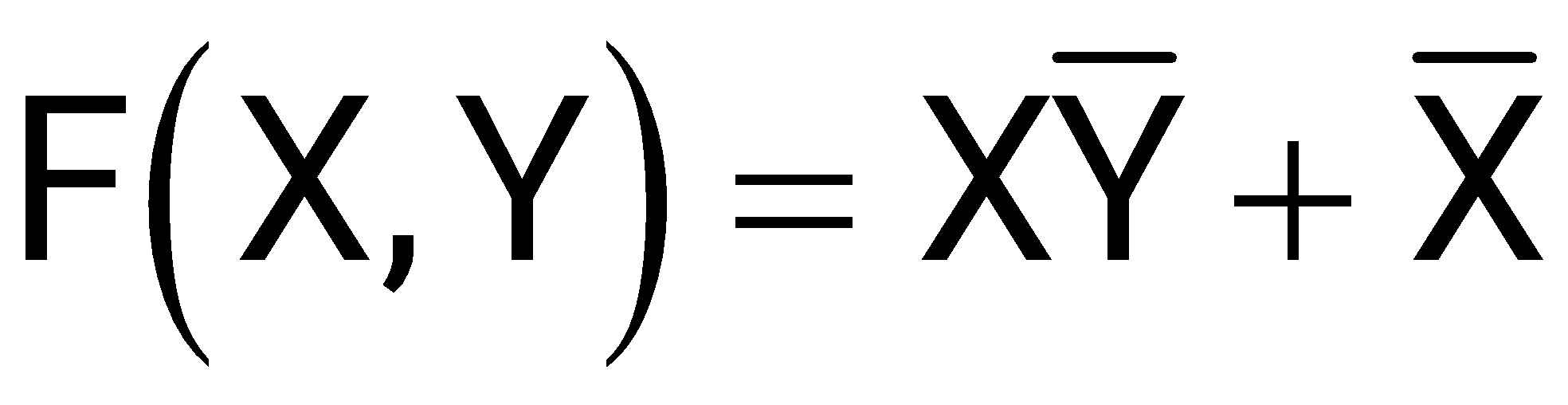

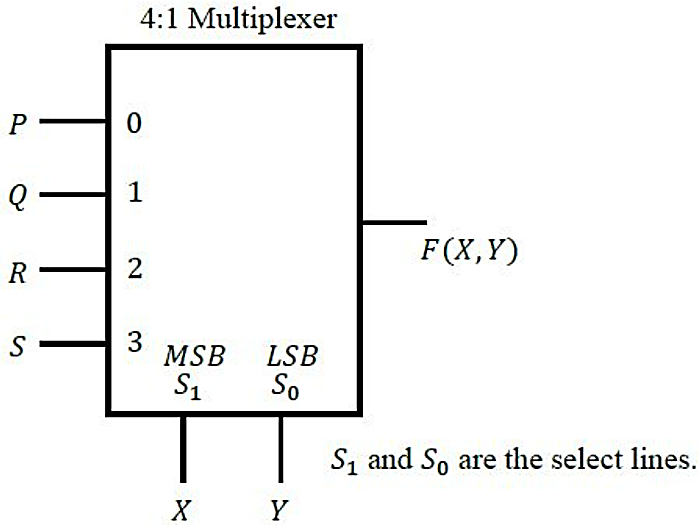

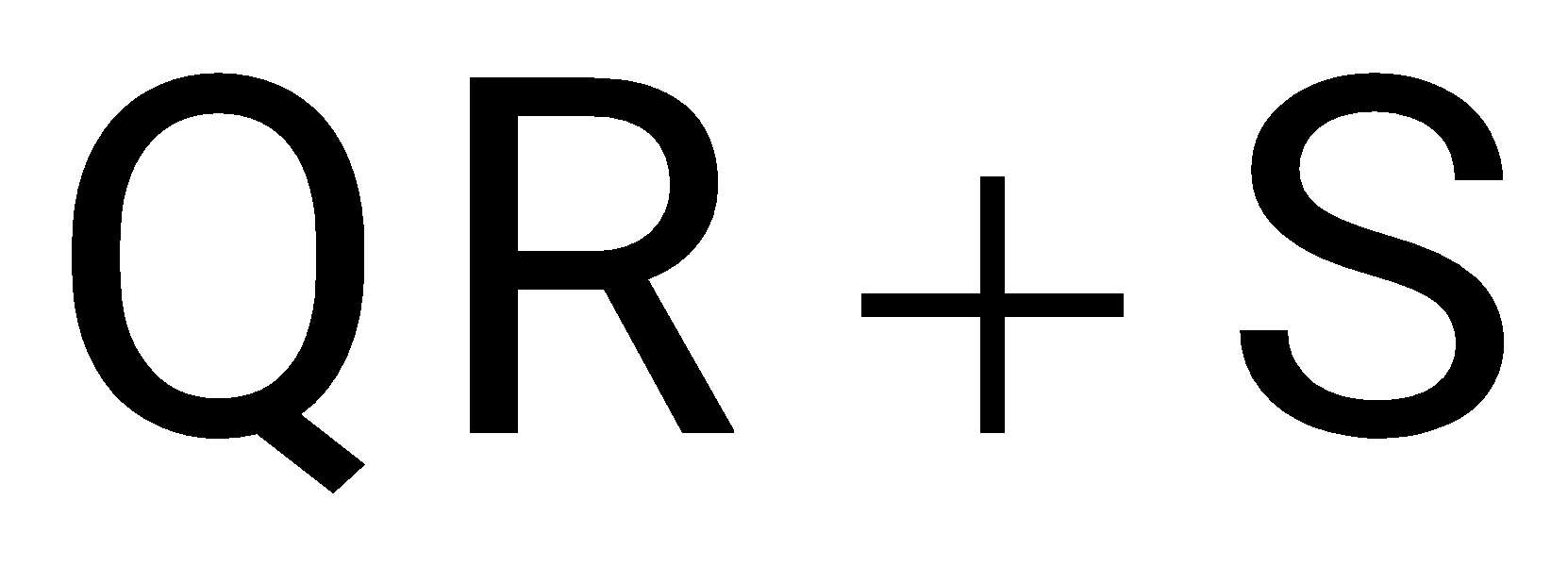

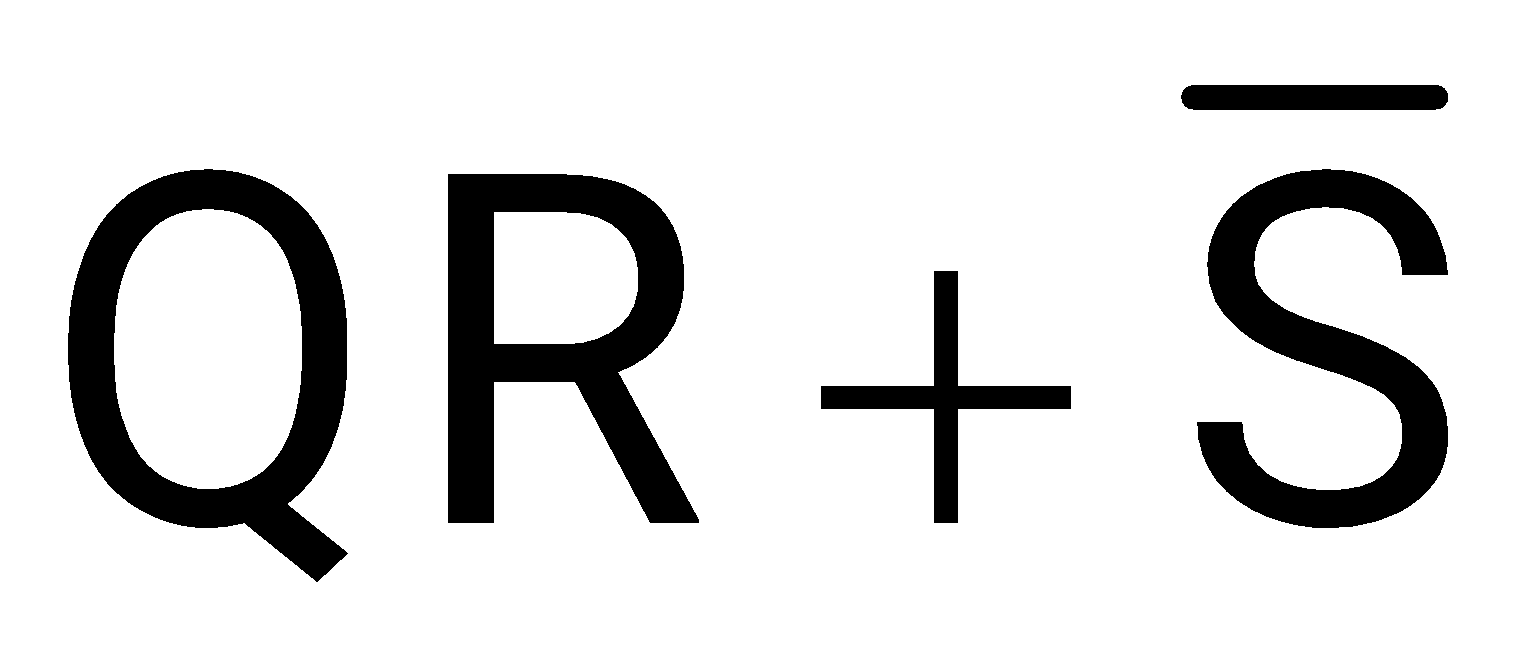

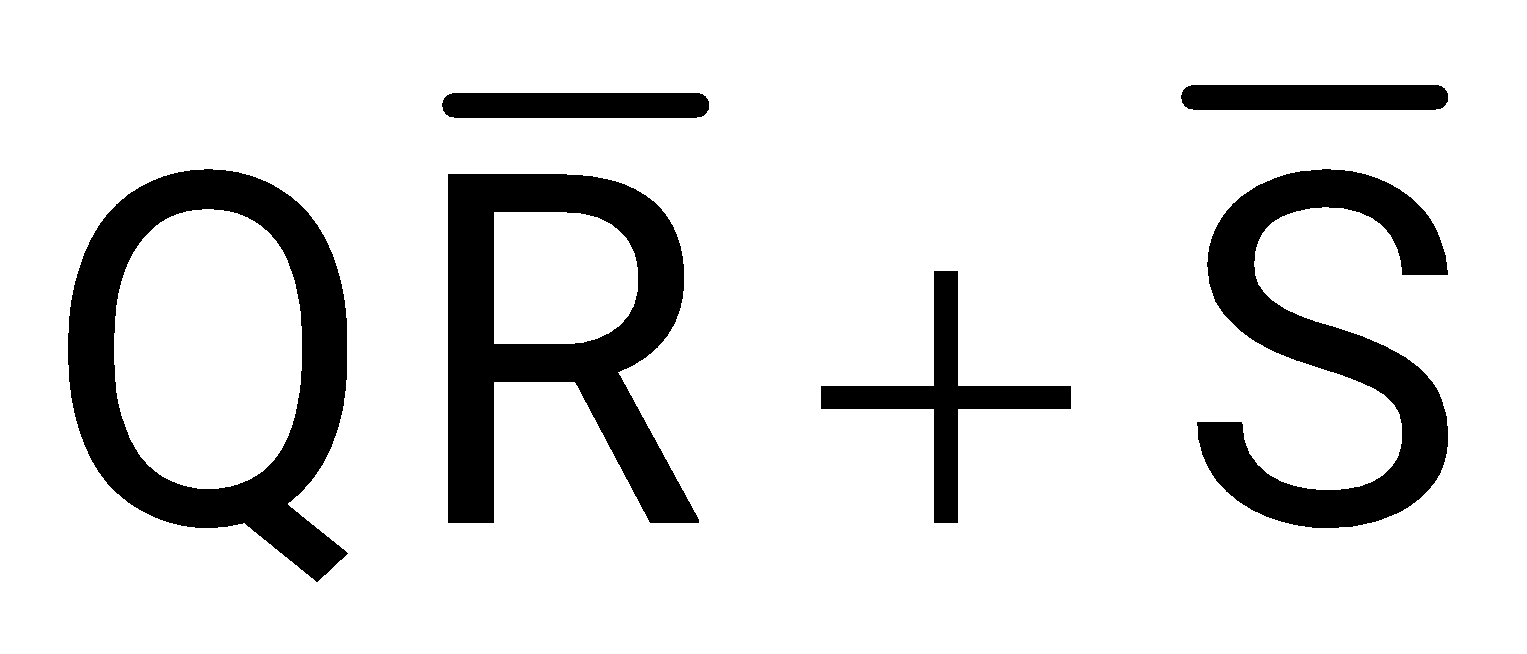

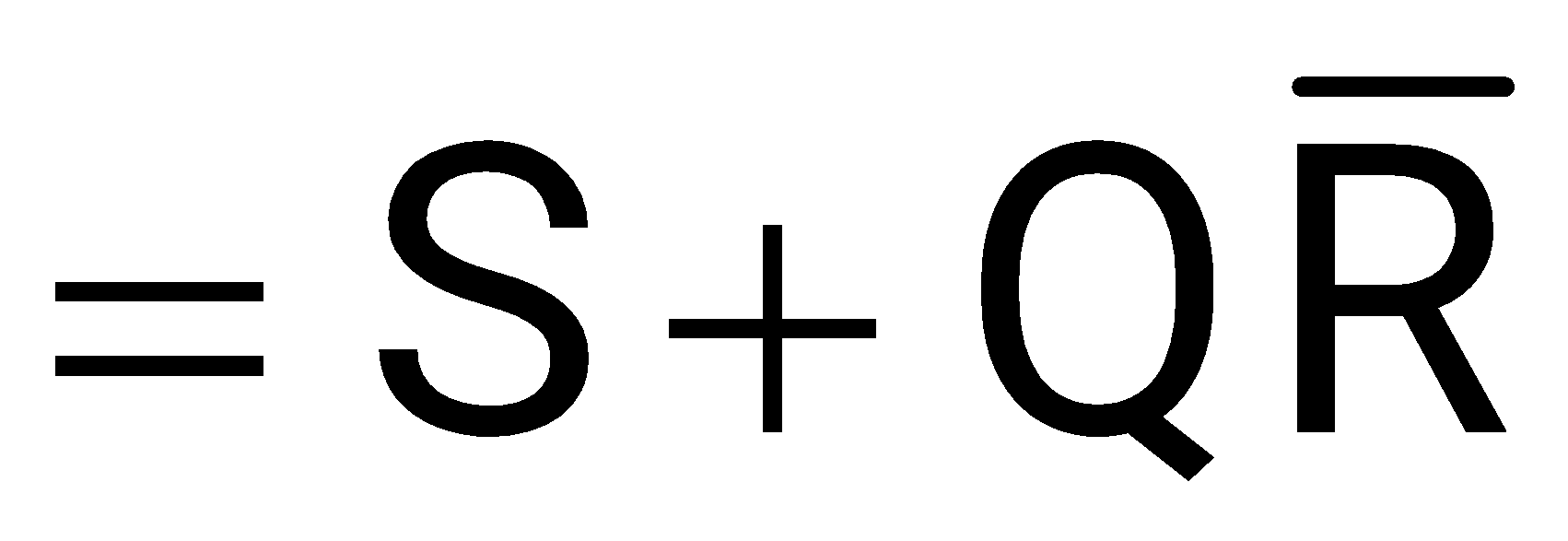

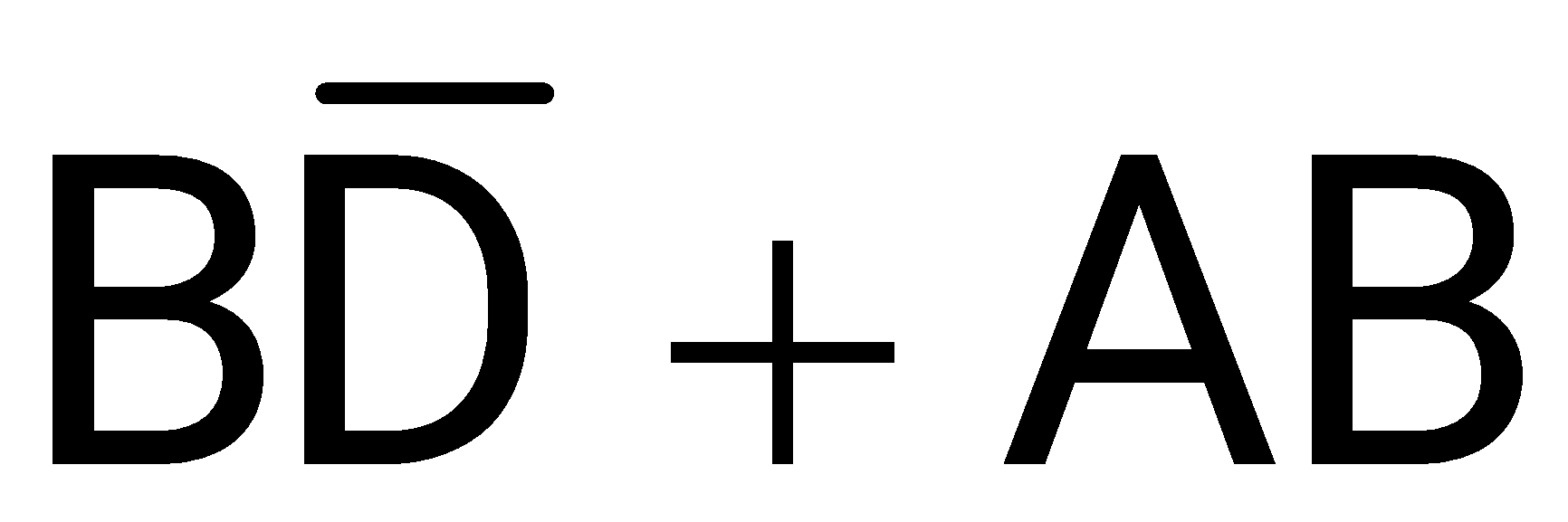

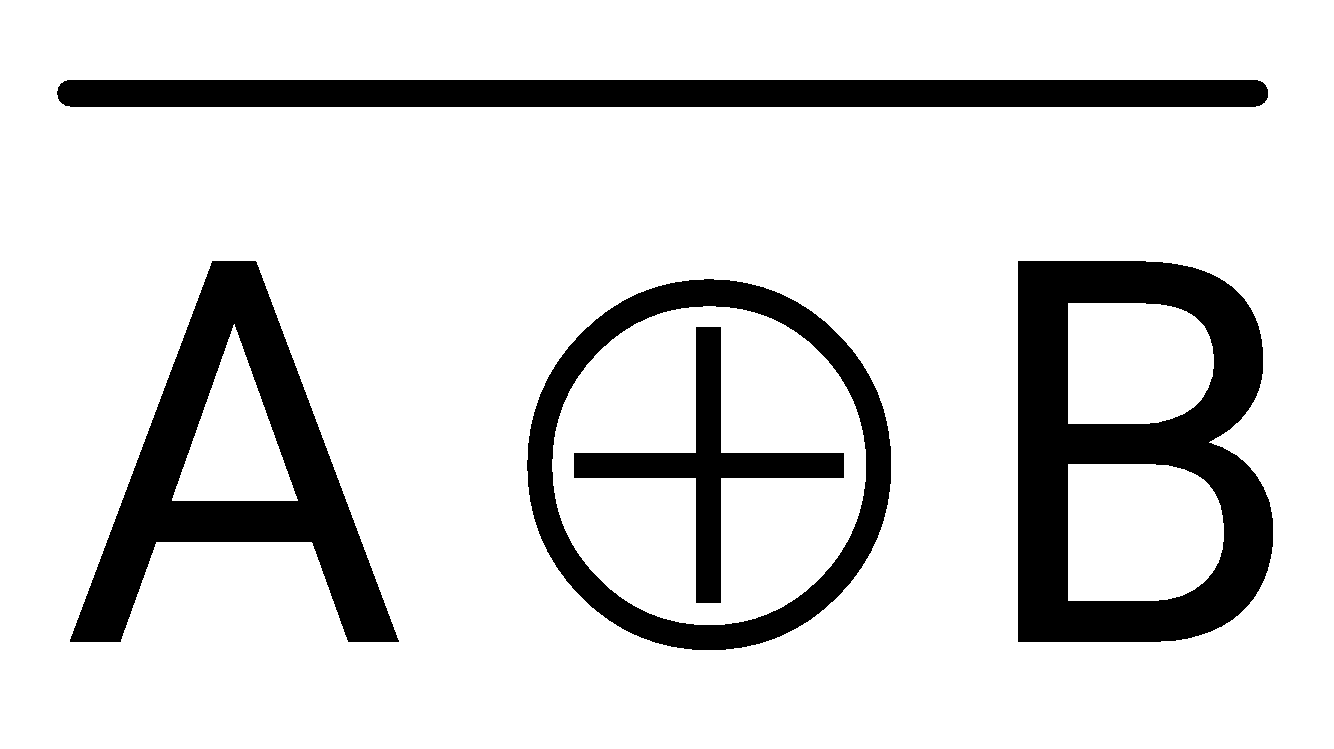

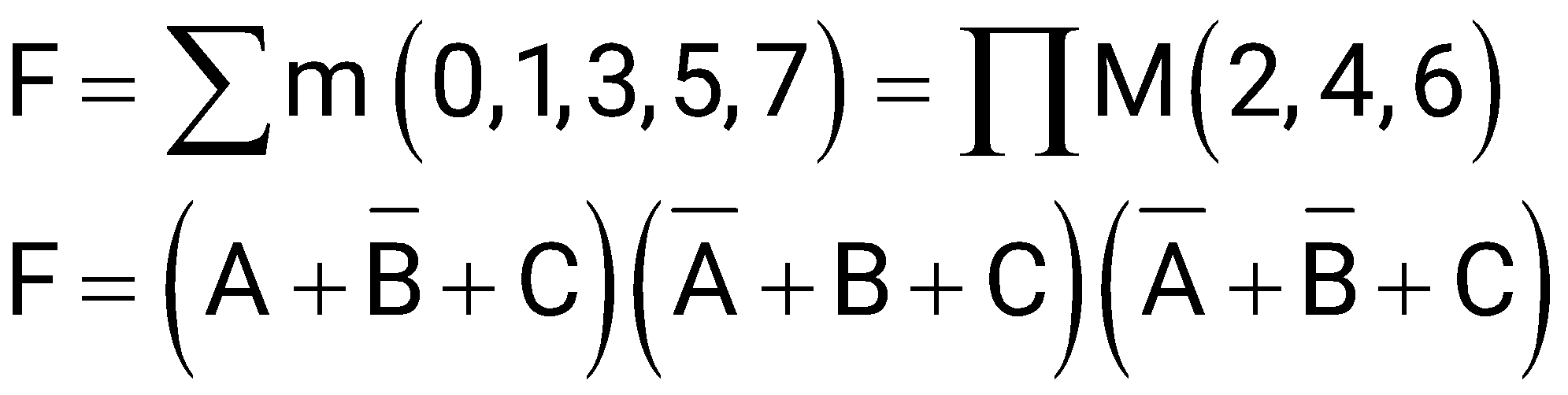

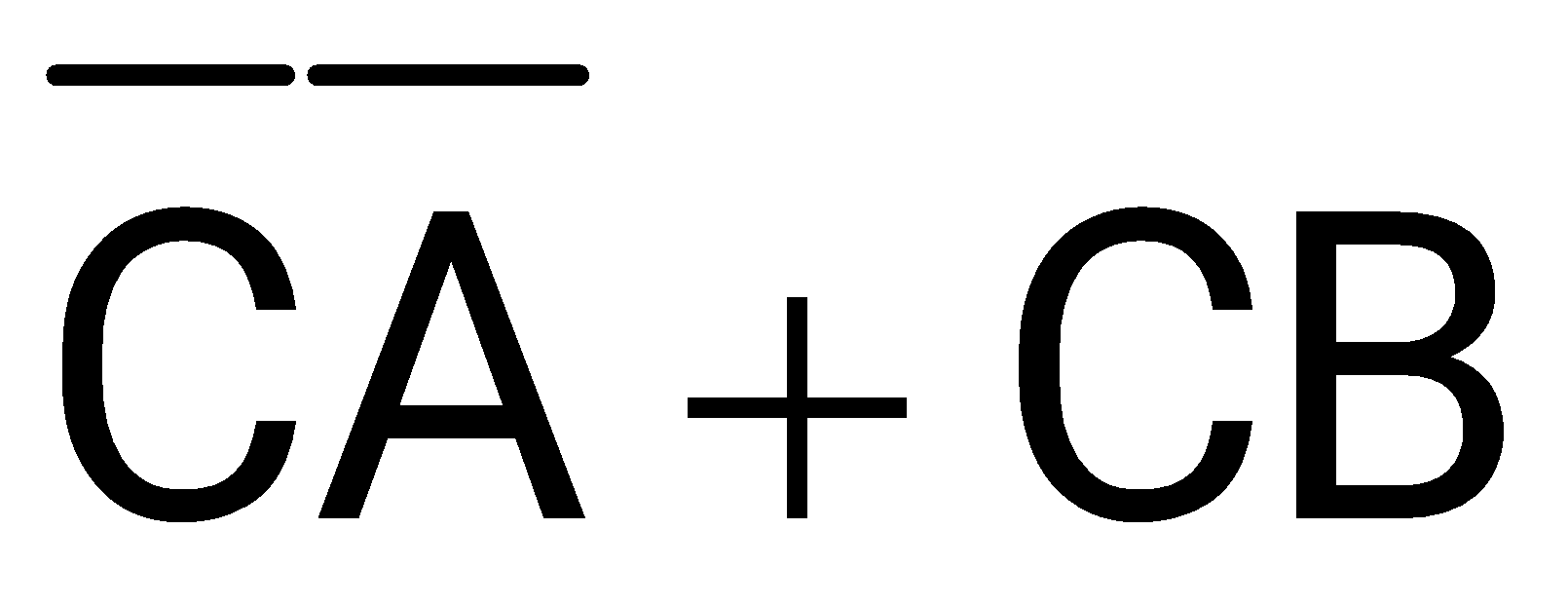

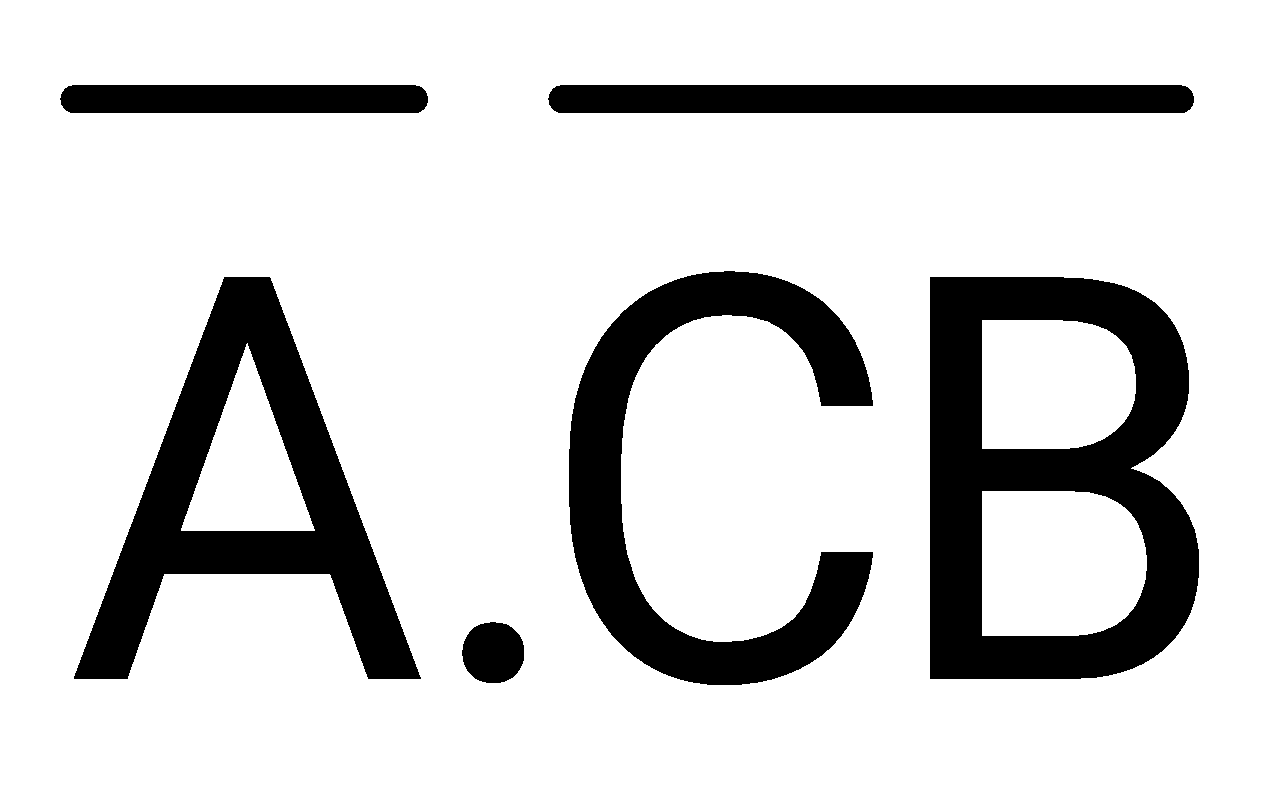

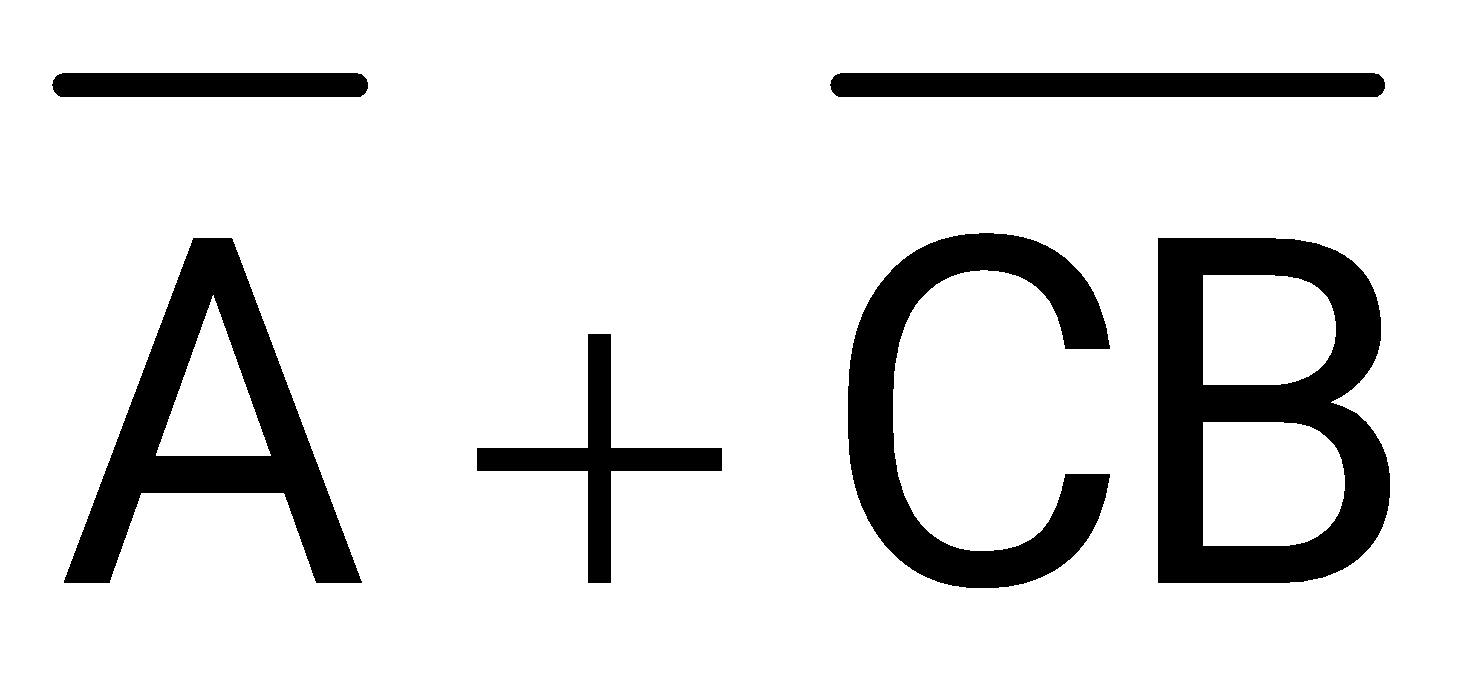

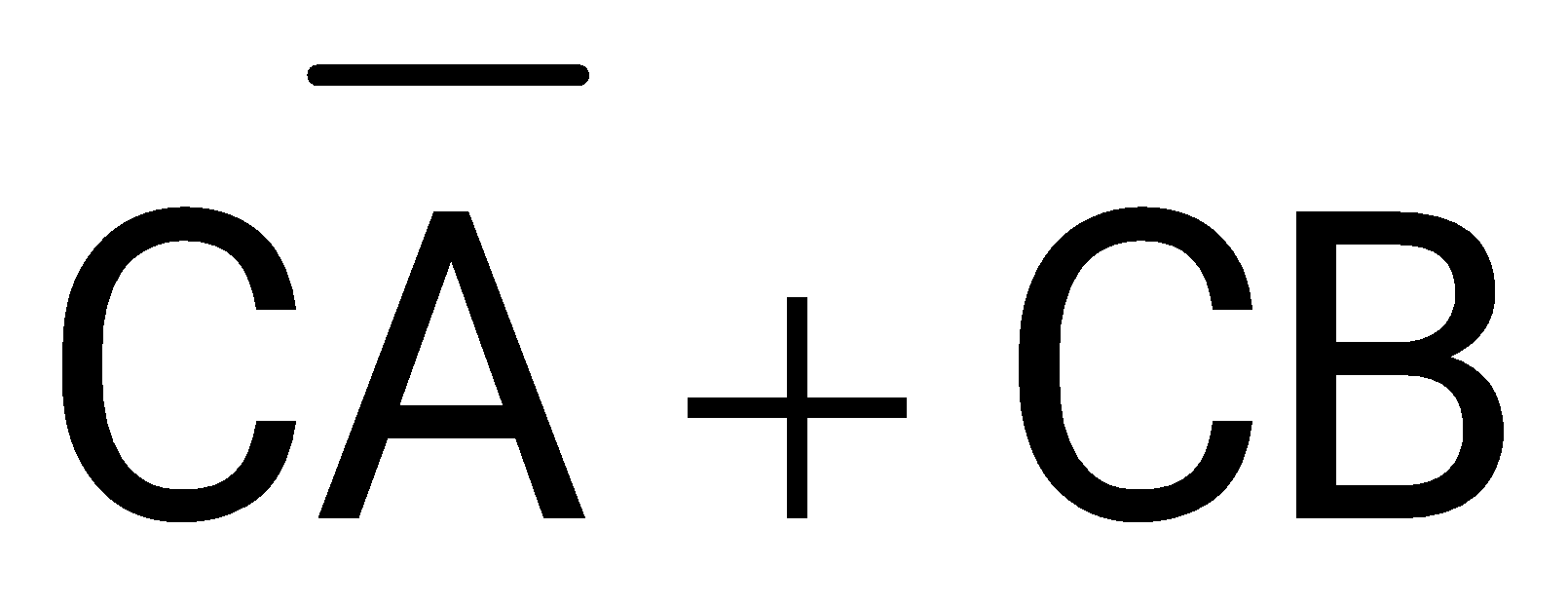

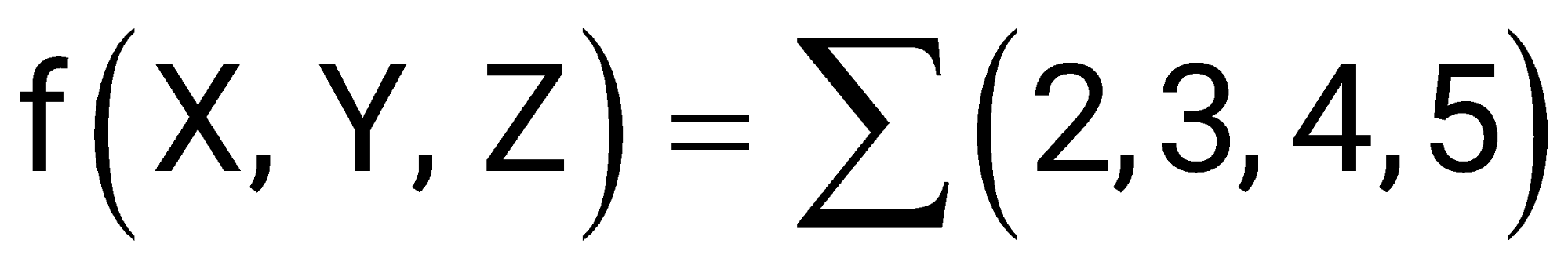

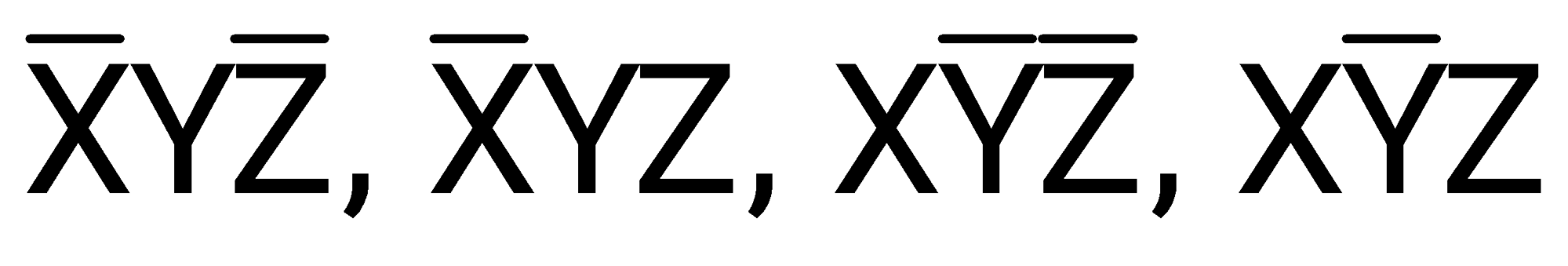

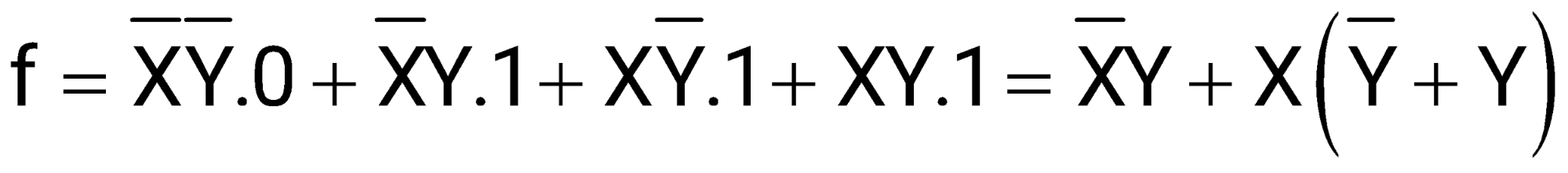

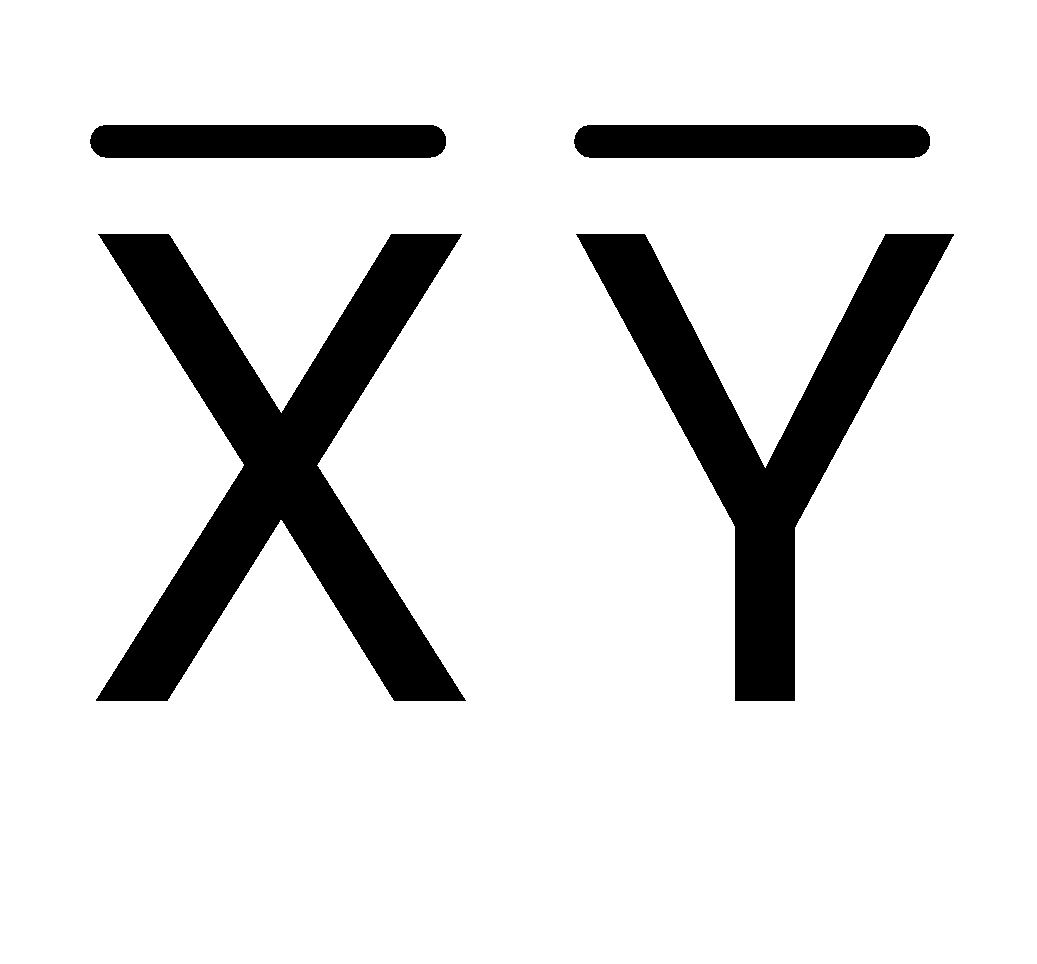

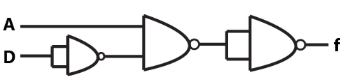

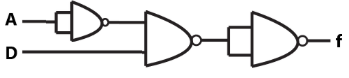

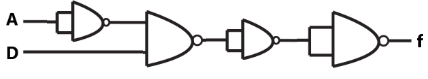

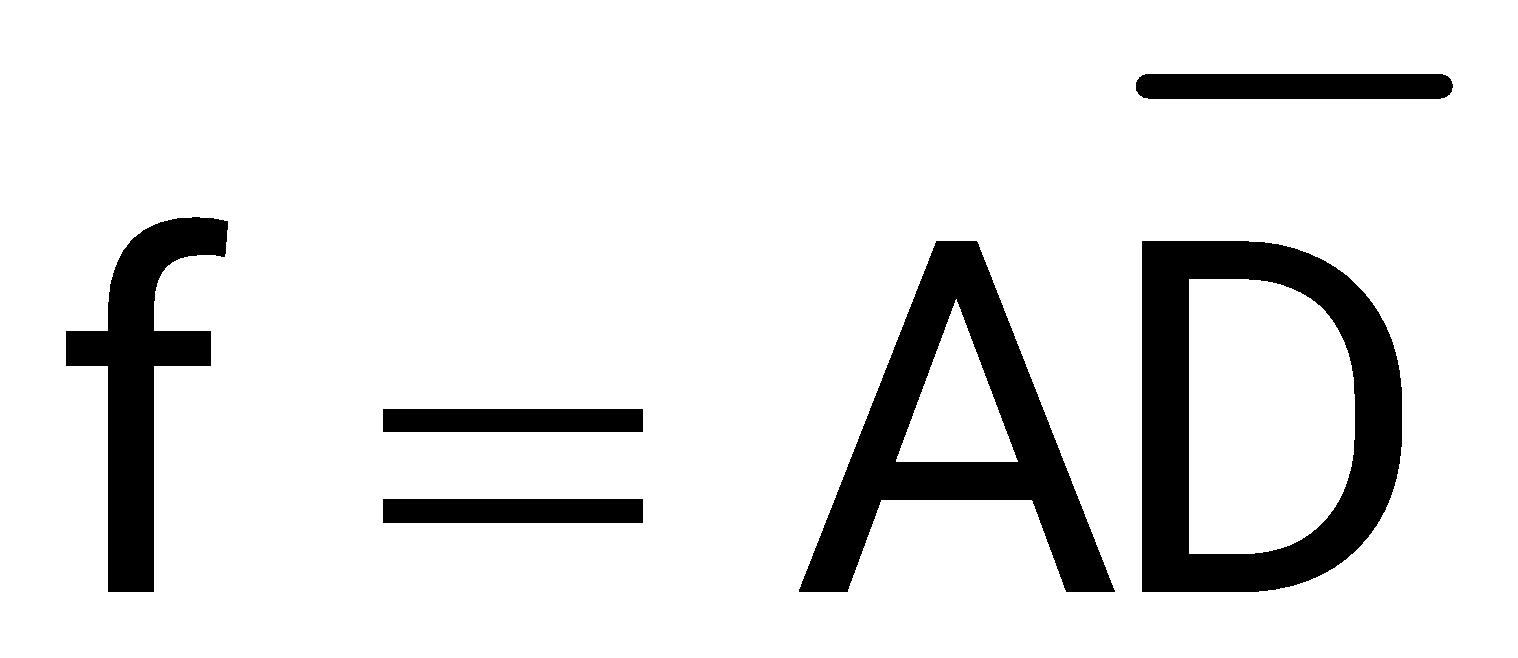

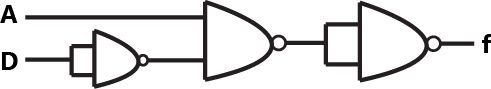

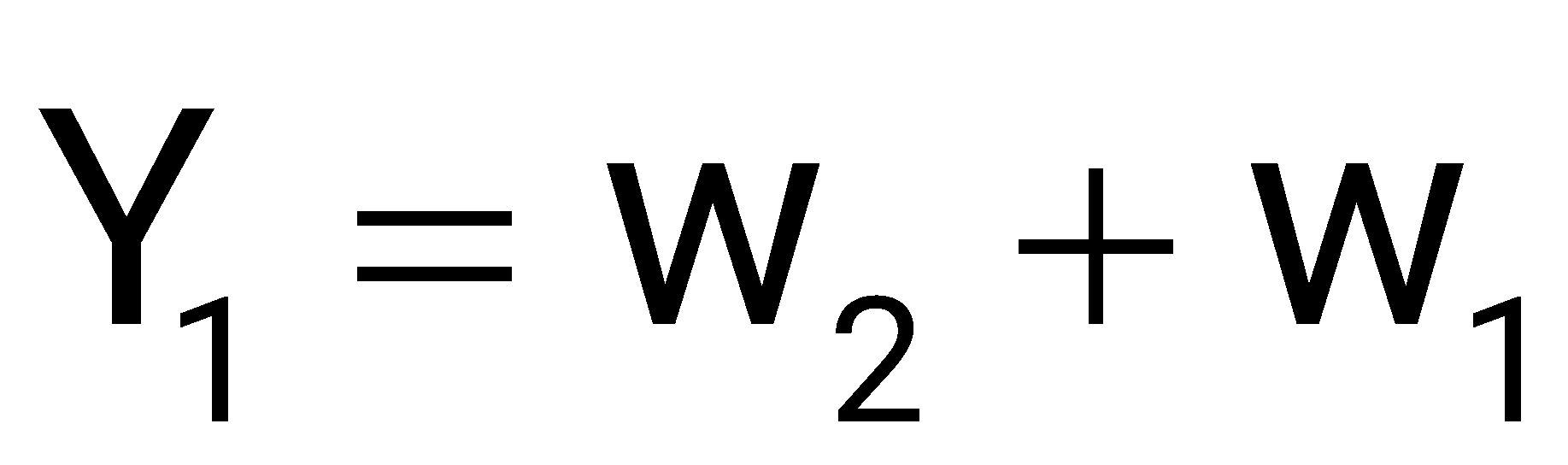

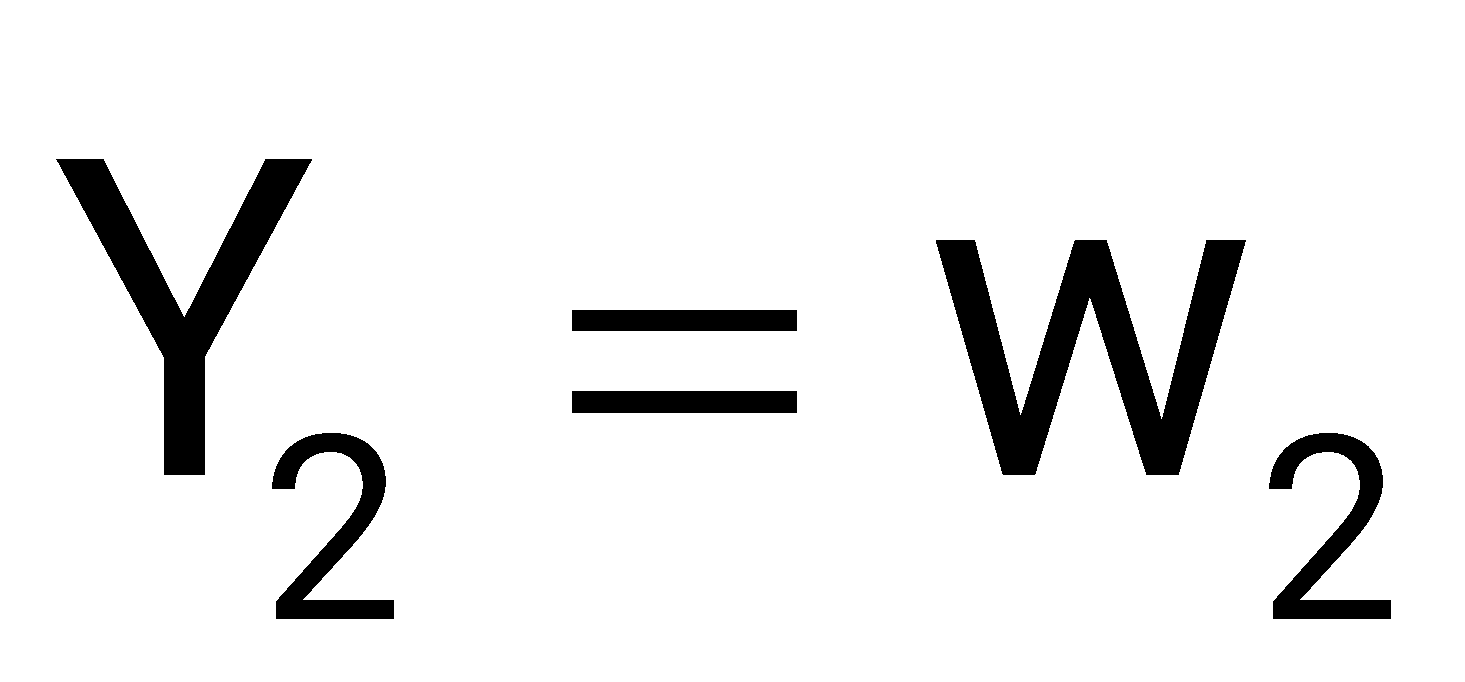

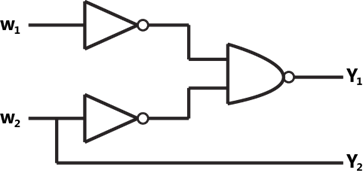

IncorrectTo obtain the Boolean function , the inputs in the figure should be

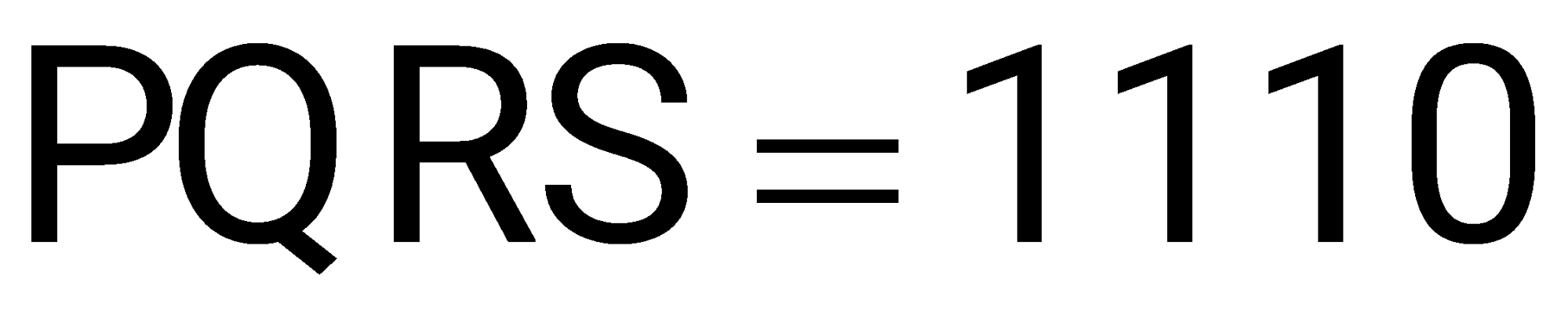

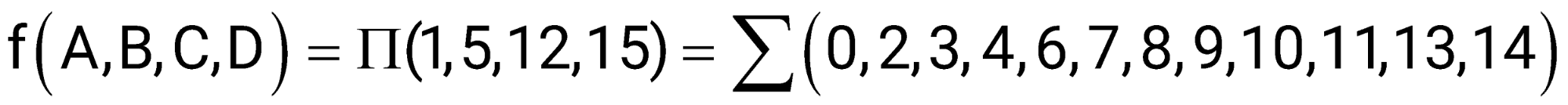

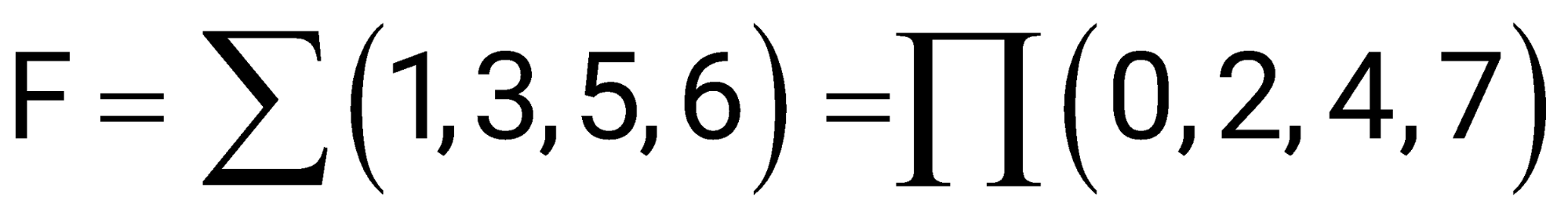

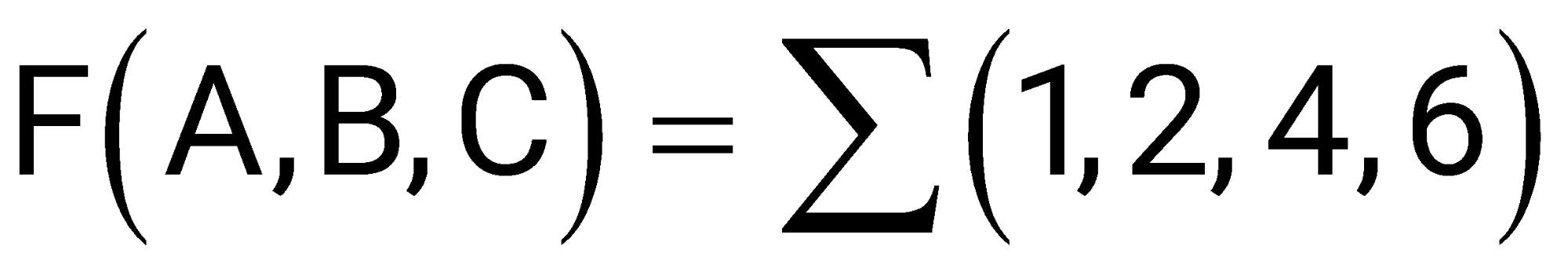

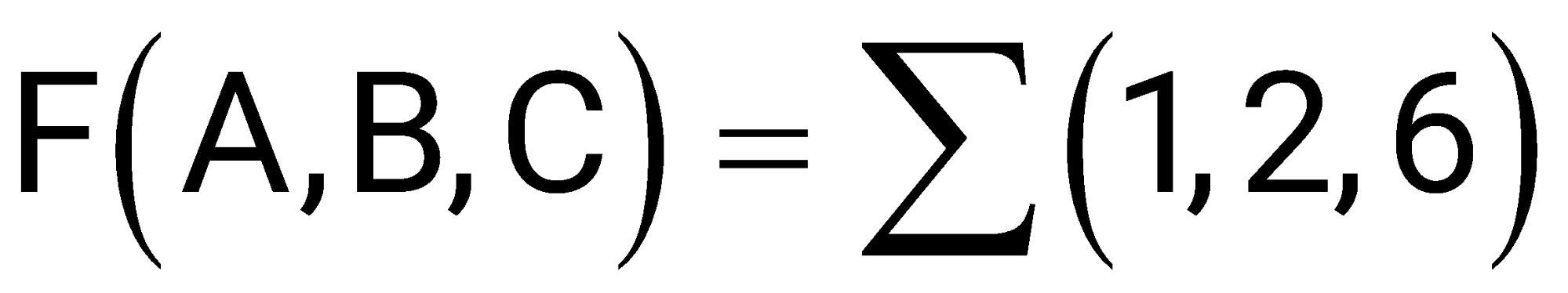

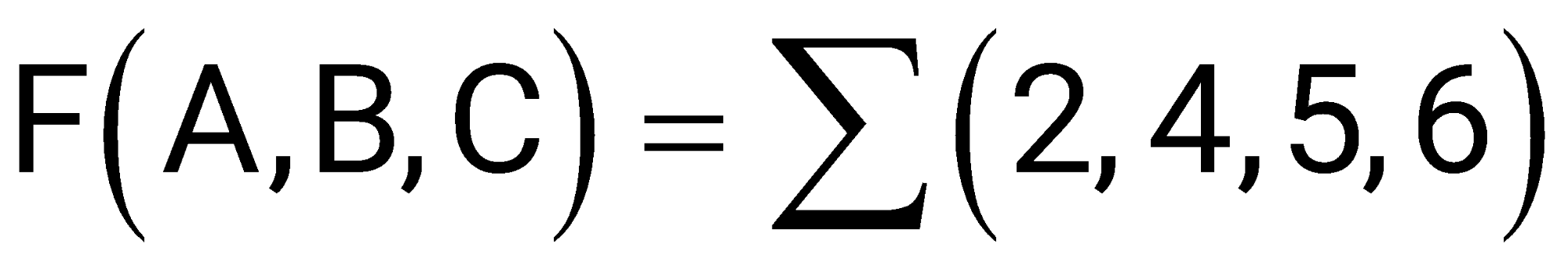

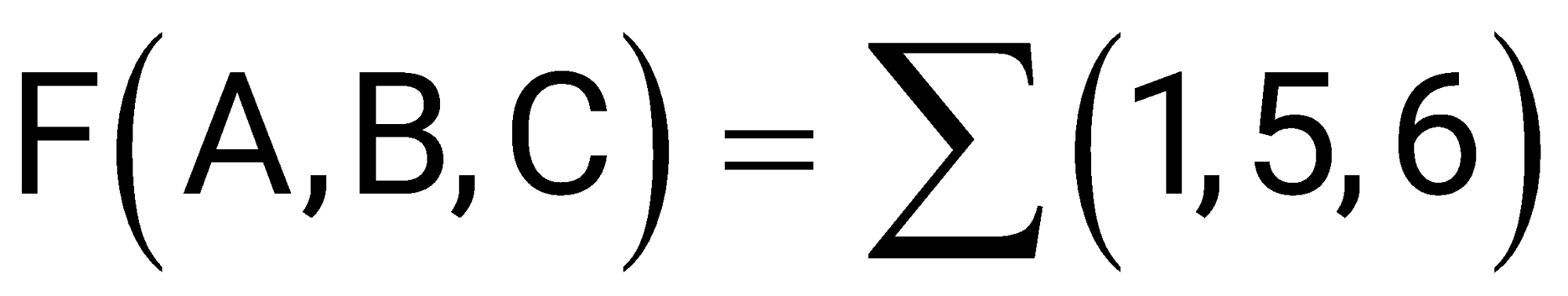

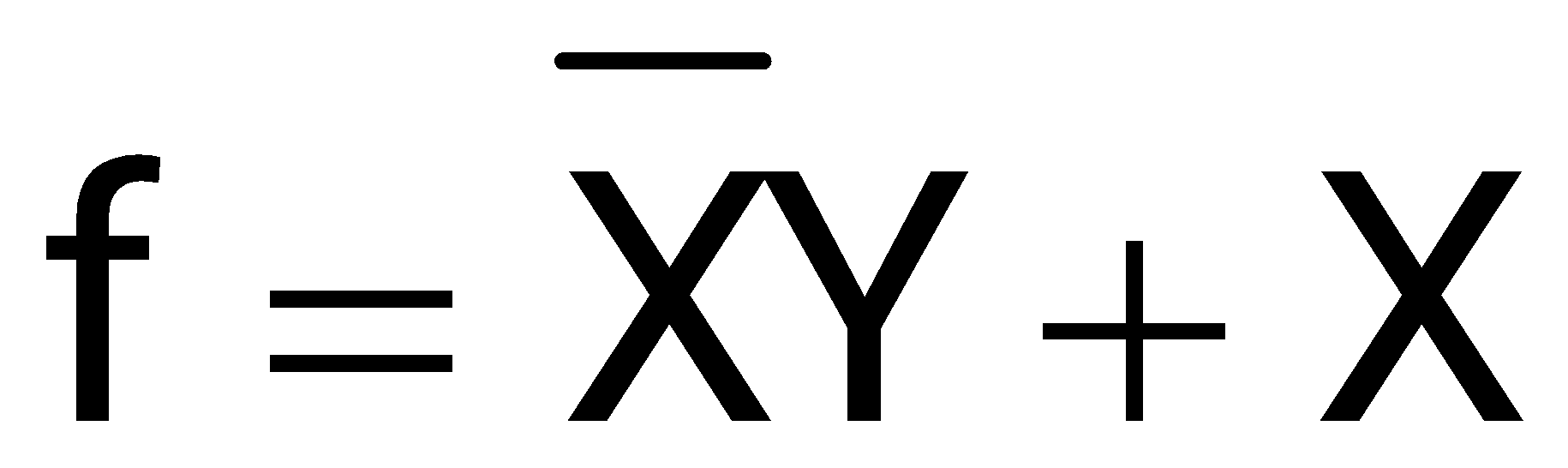

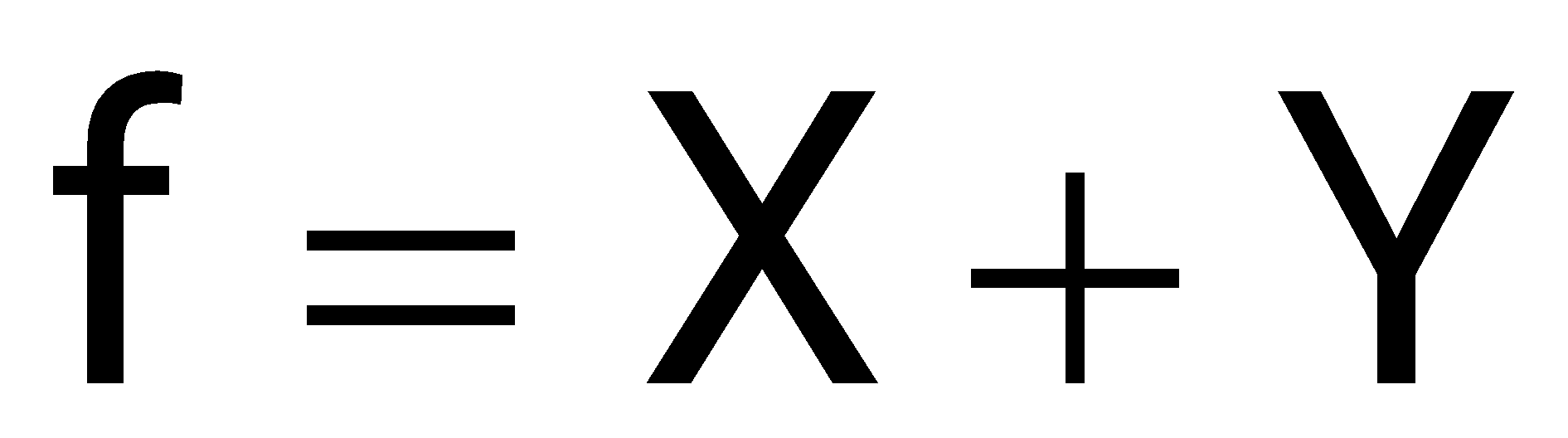

If

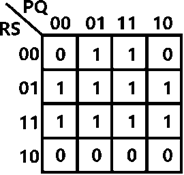

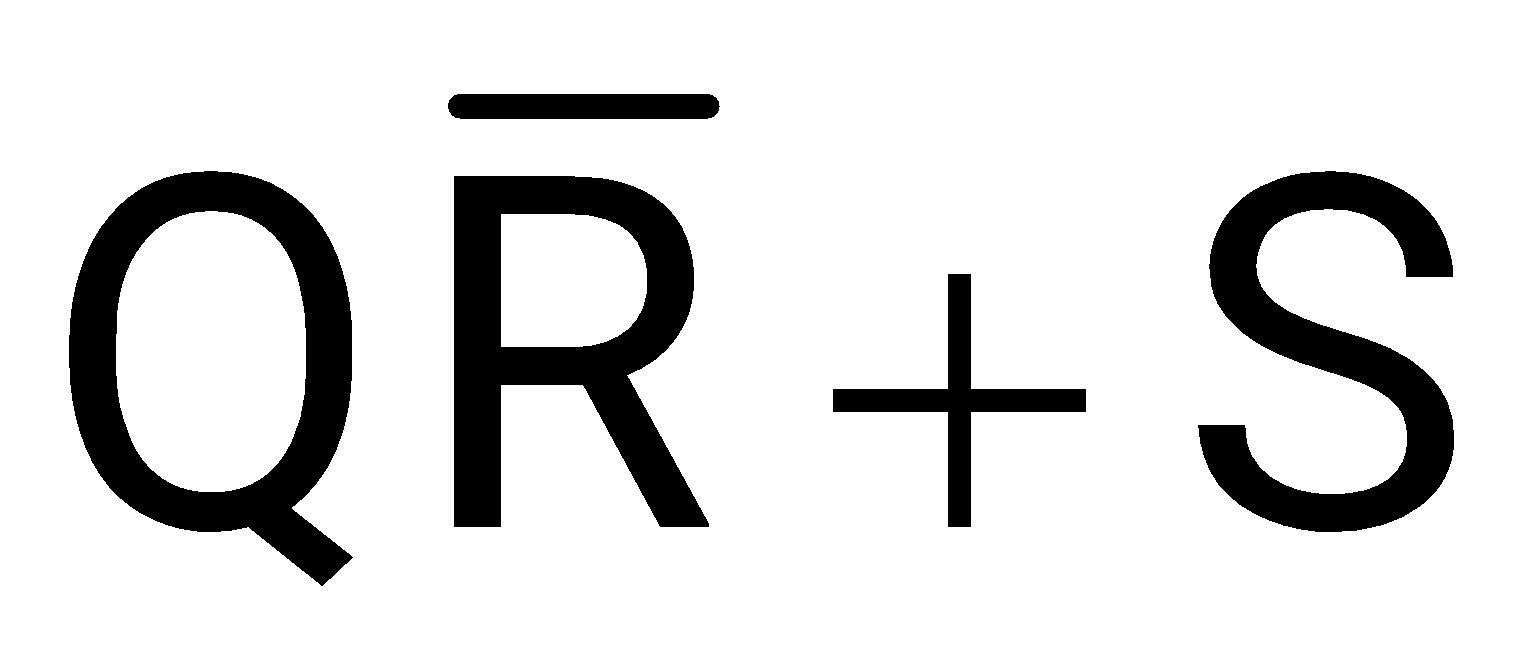

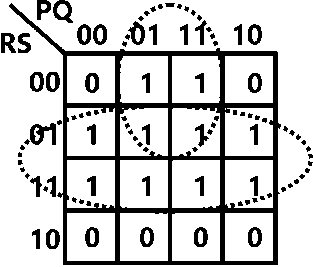

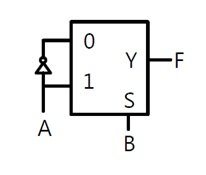

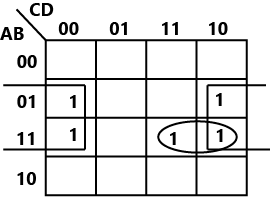

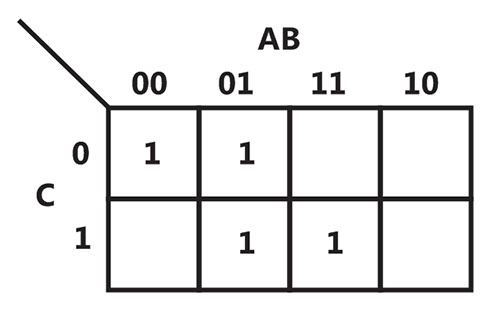

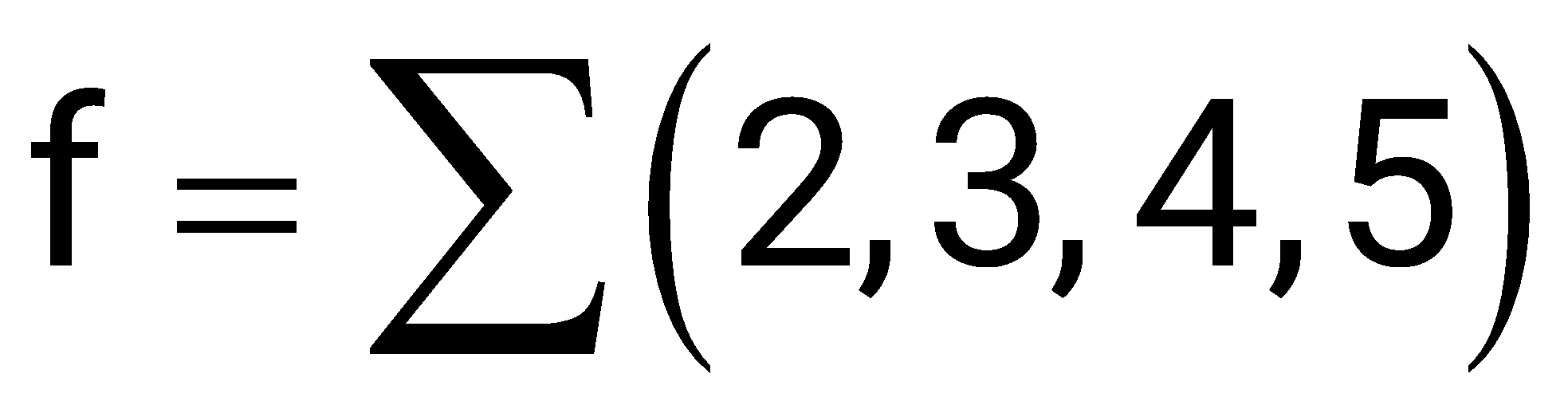

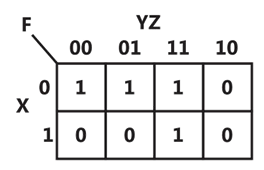

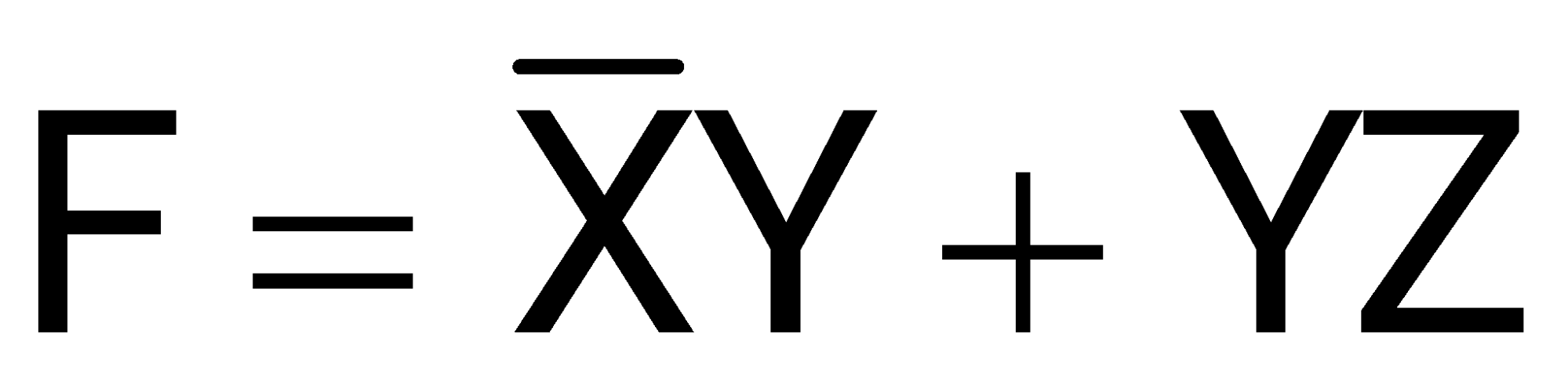

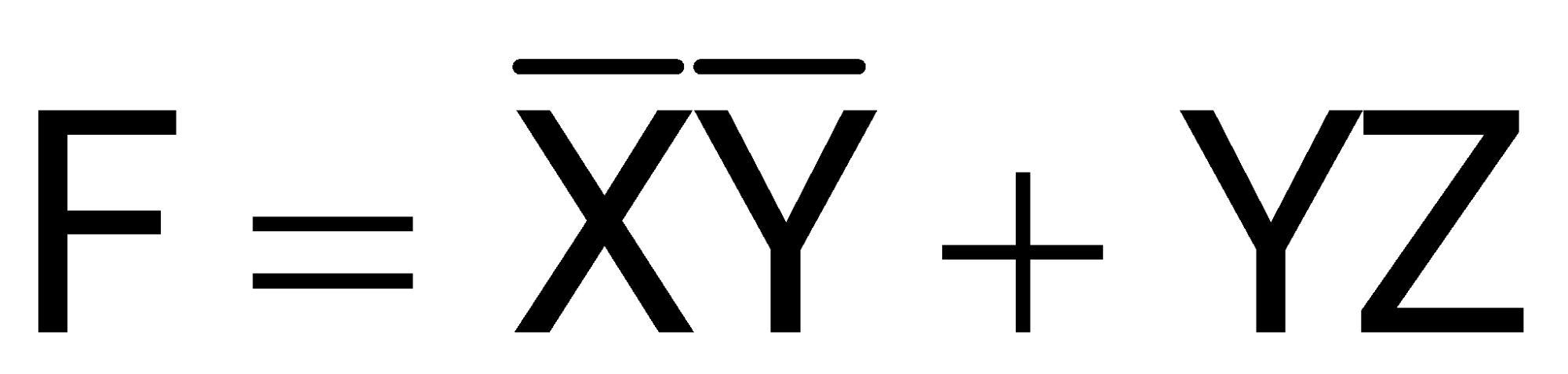

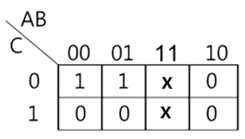

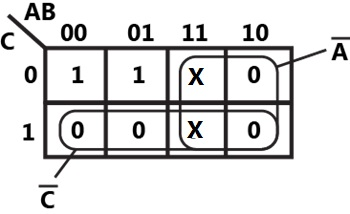

The output expression for the Karnaugh map shown below is

Function

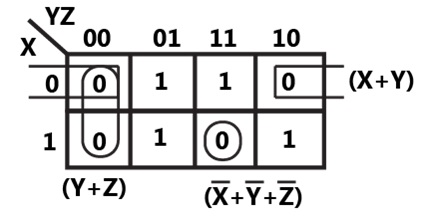

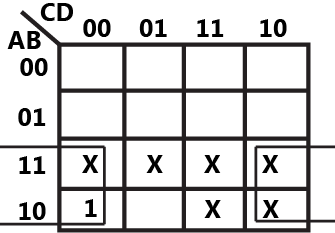

The output expression for the Karnaugh map shown below is

The given k-map is

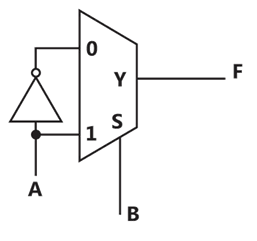

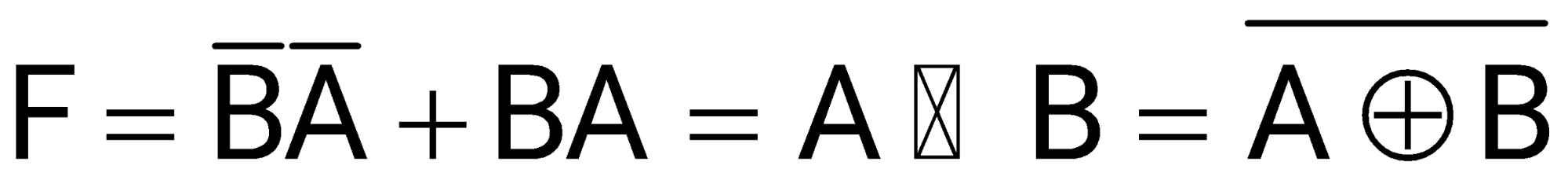

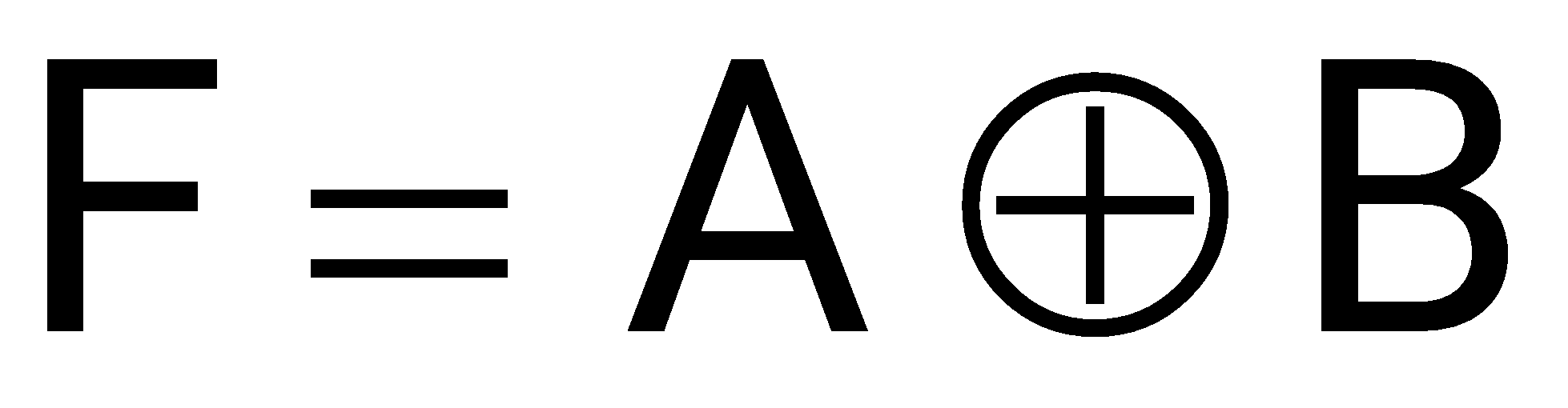

Consider the following circuit which uses a 2-to-1 multiplexer as shown in the figure below. The Boolean expression for output F in terms of A and B is

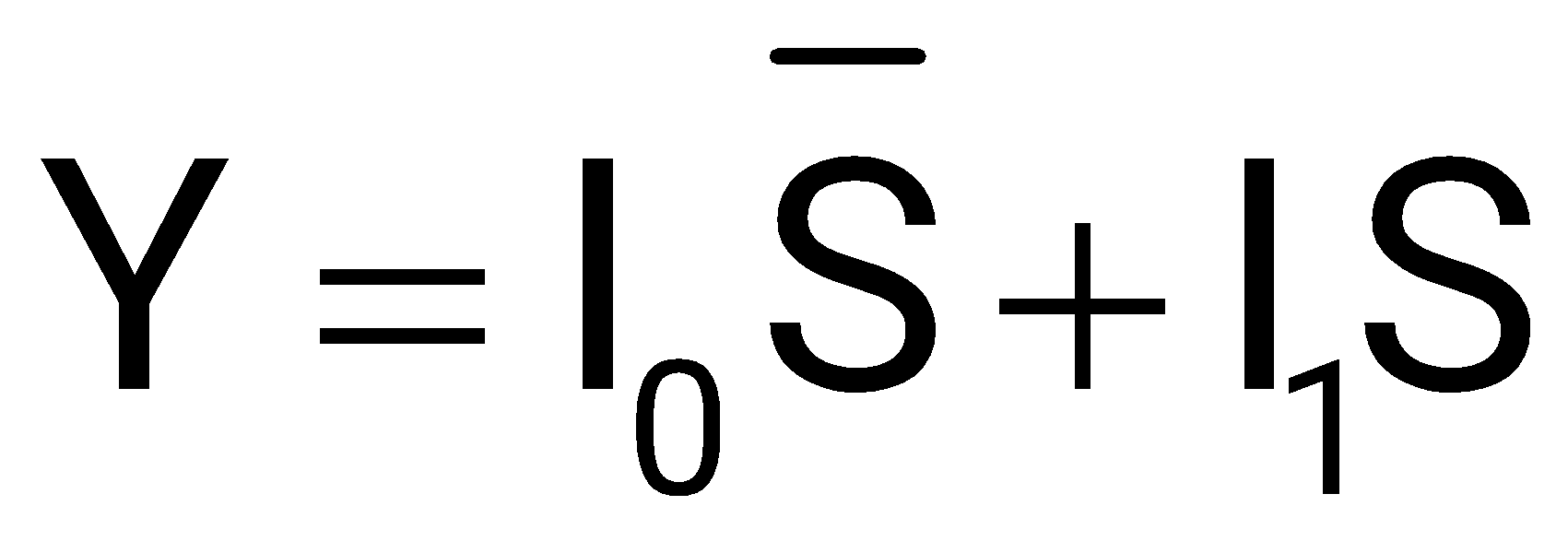

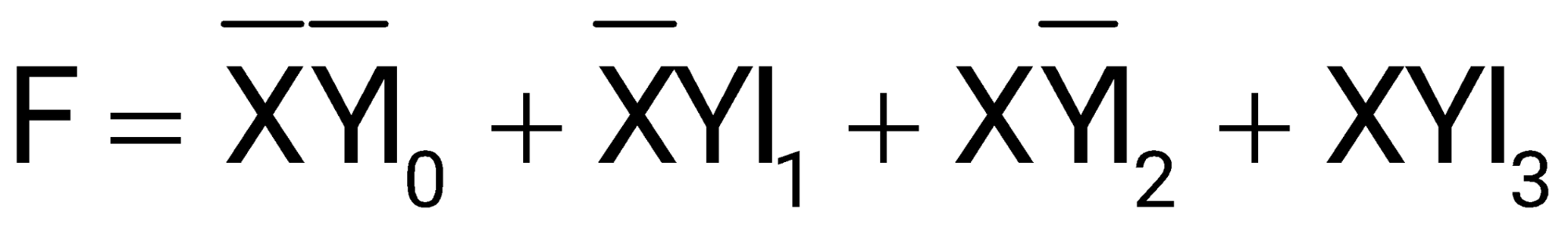

The input output relation of a multiplexer is,

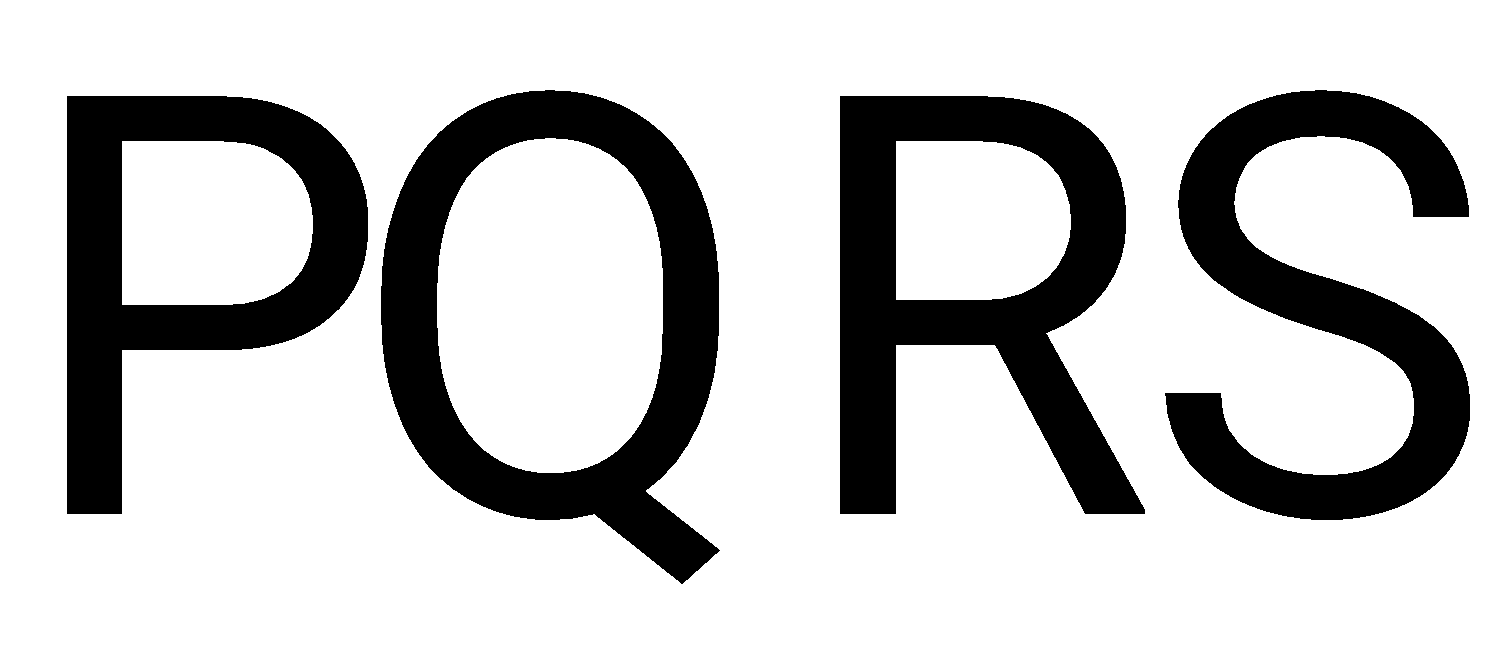

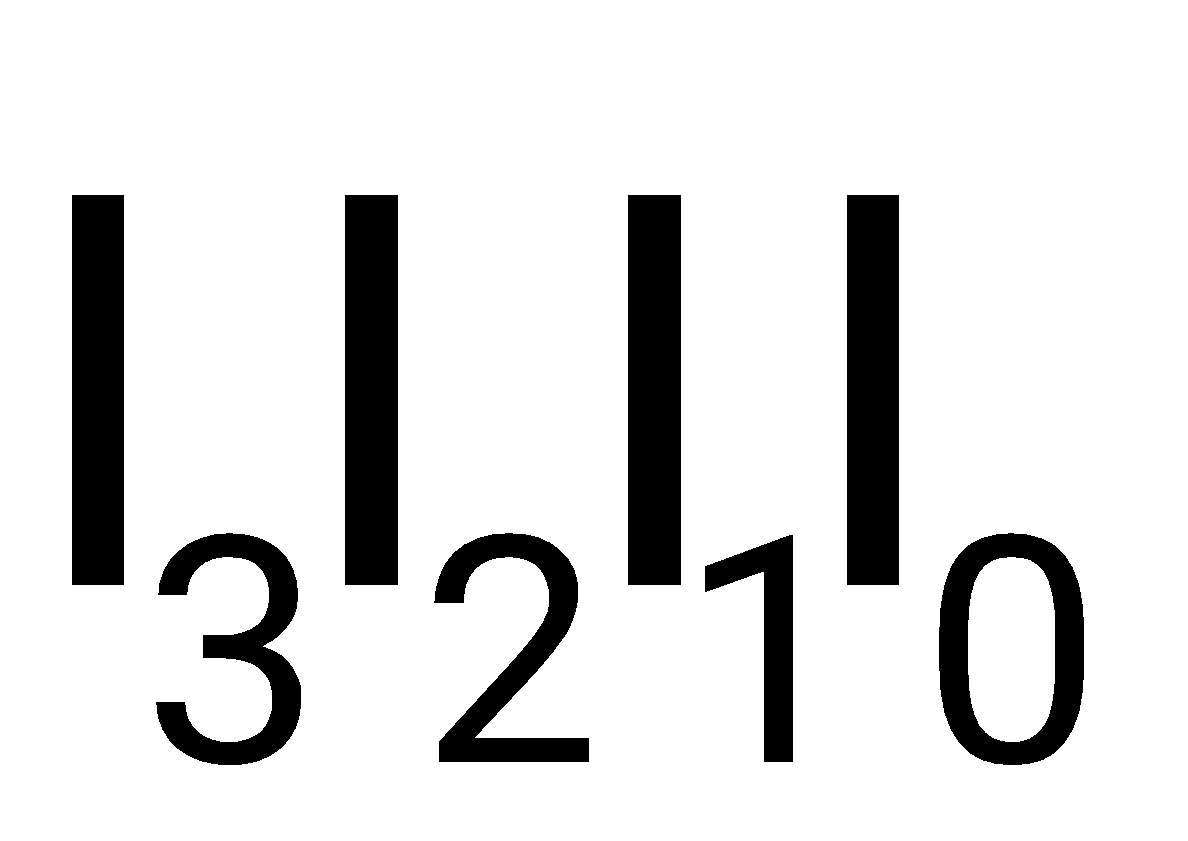

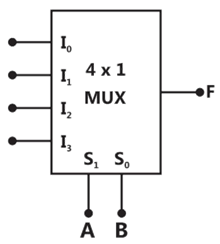

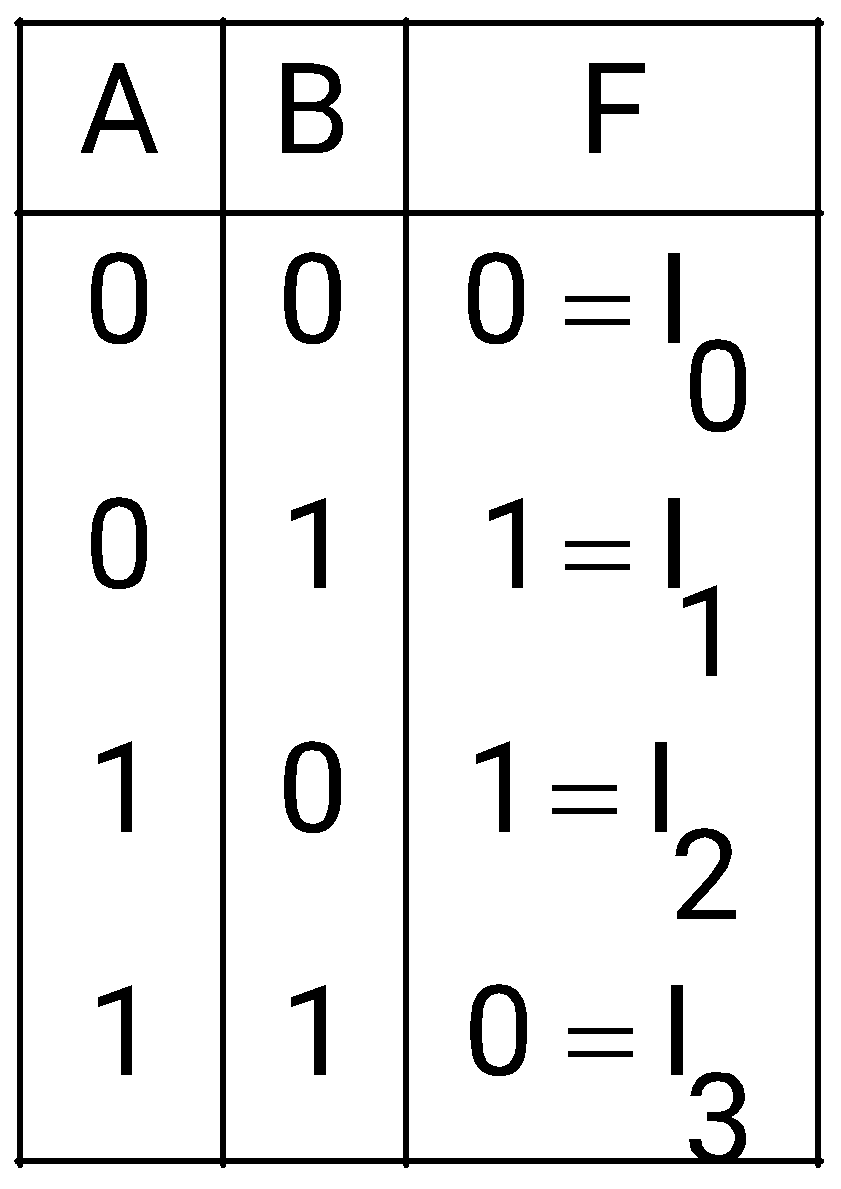

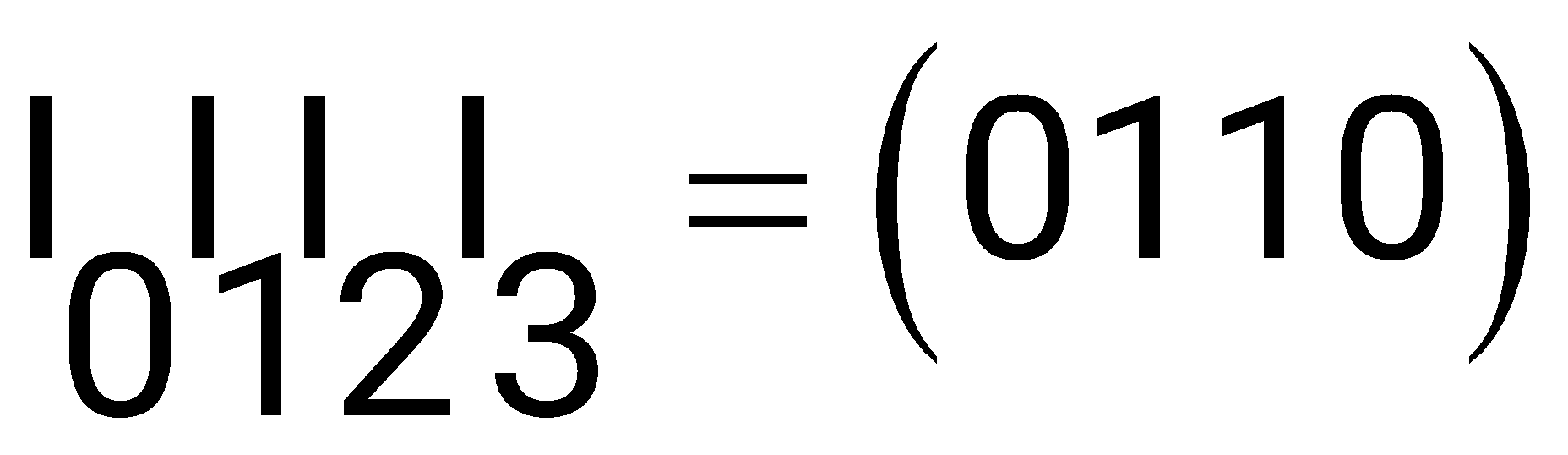

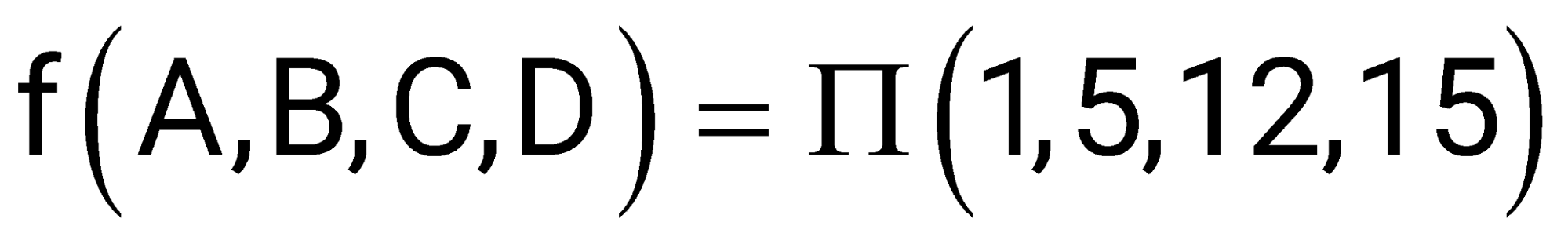

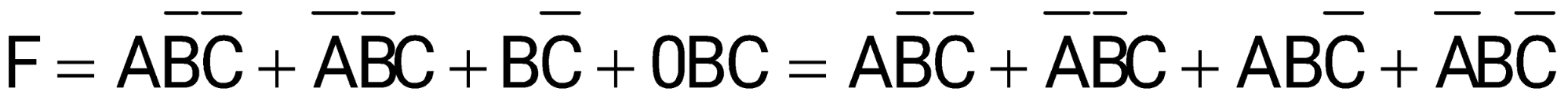

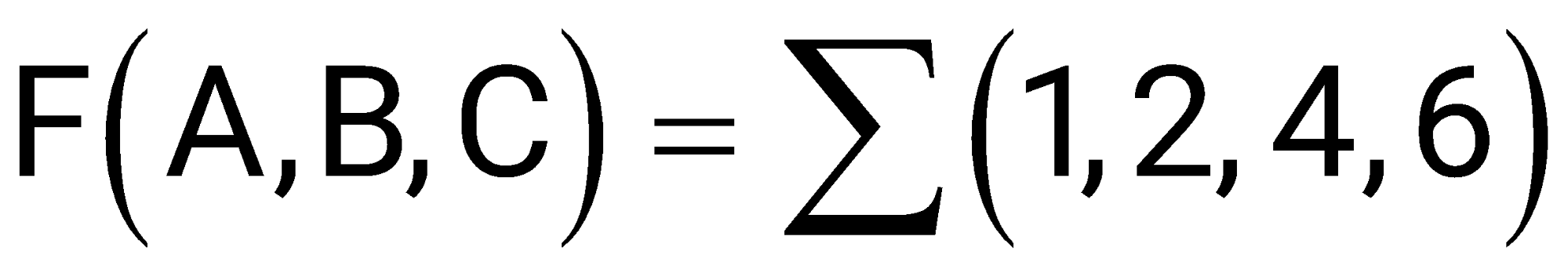

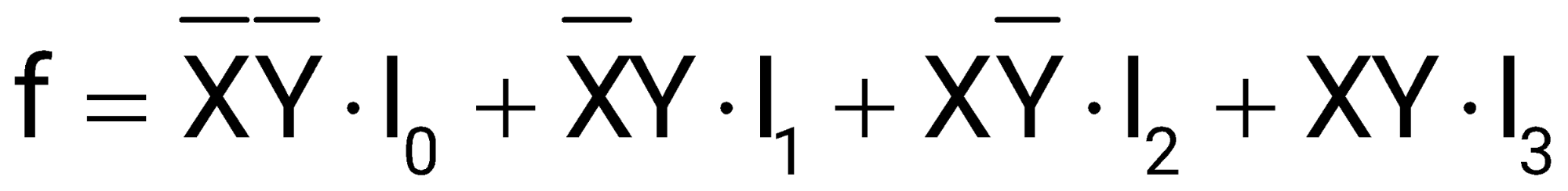

In the 4 x 1 multiplexer, the output F is given by. Find the required input .

For

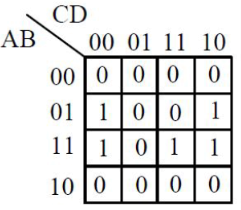

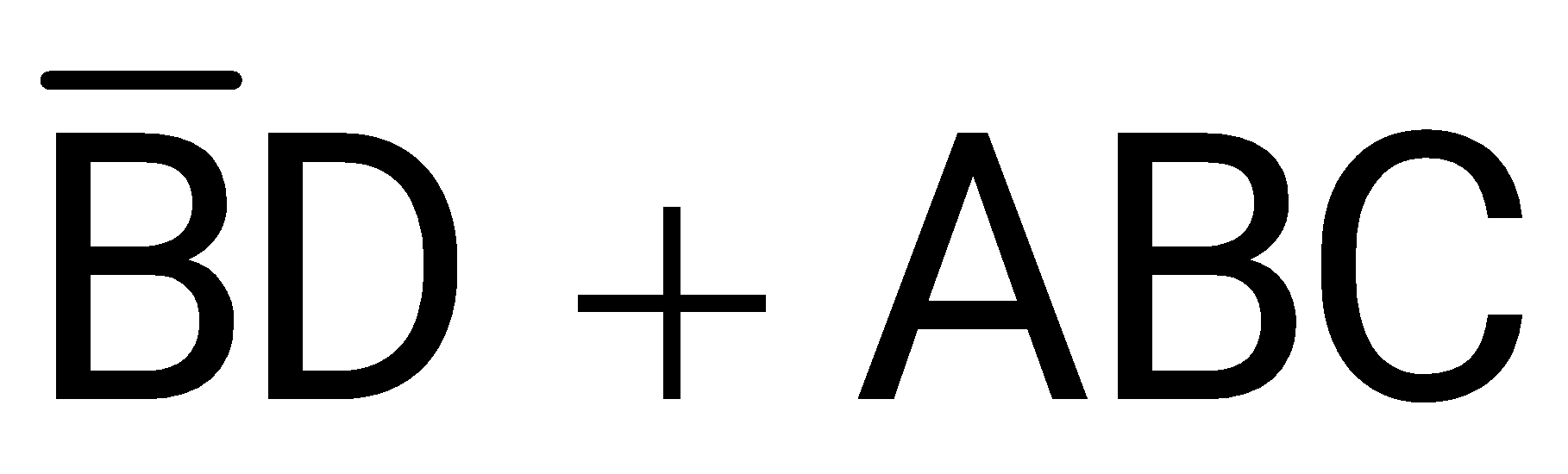

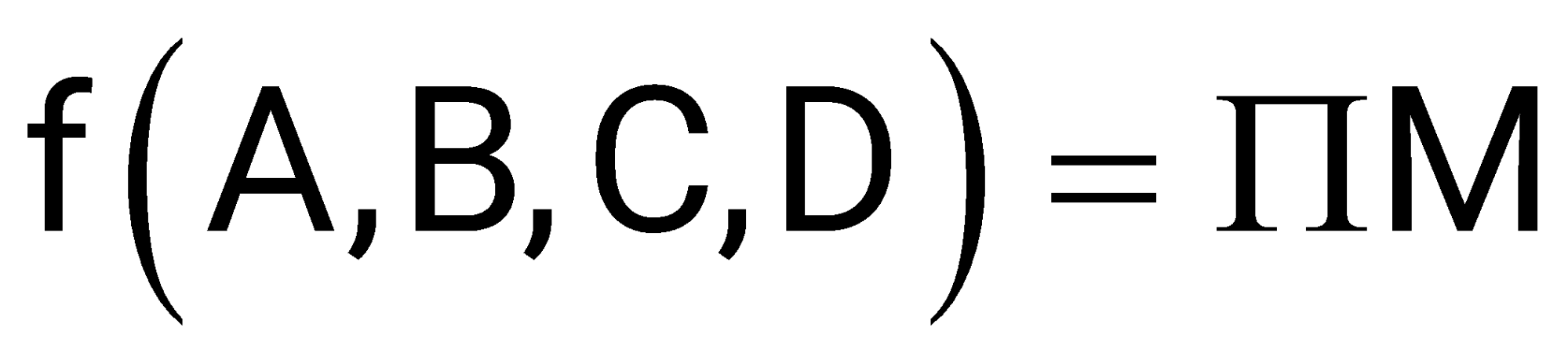

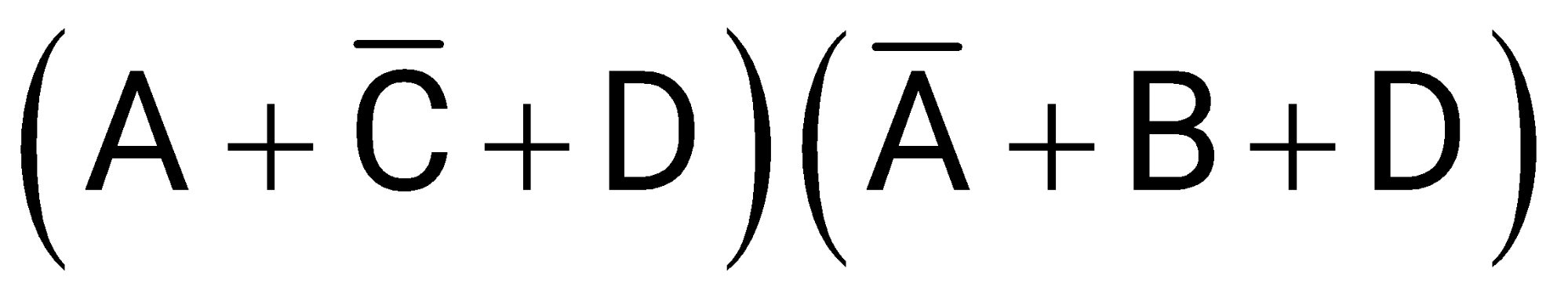

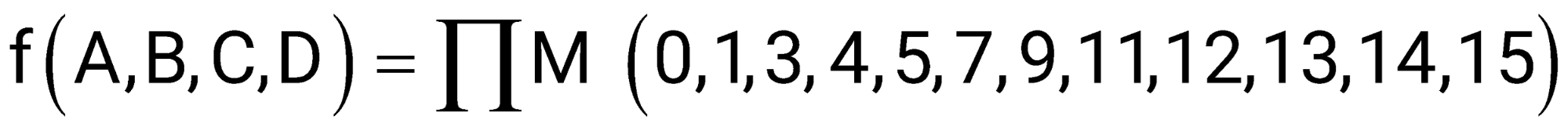

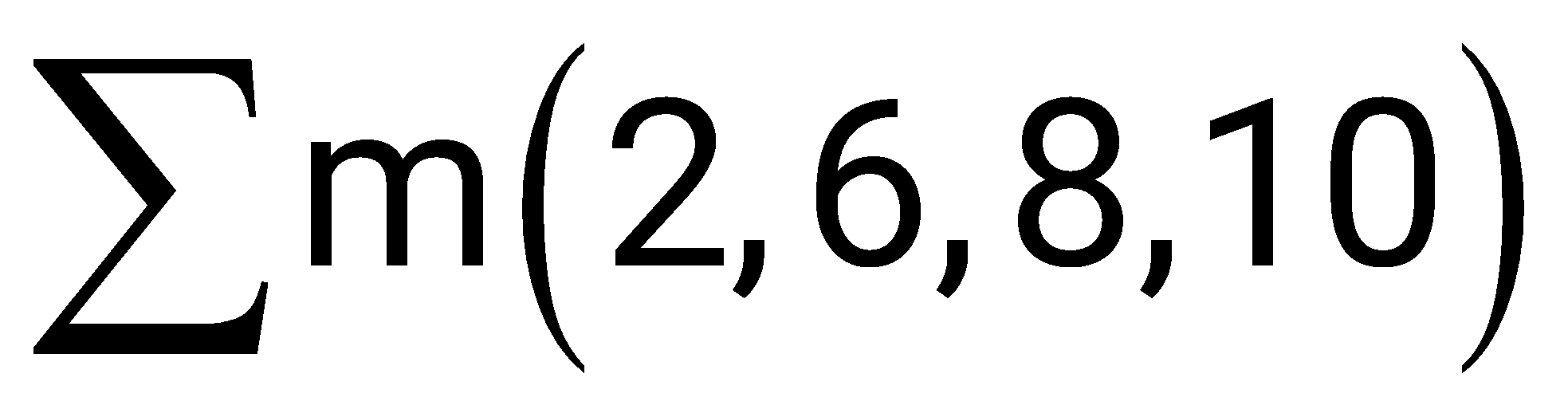

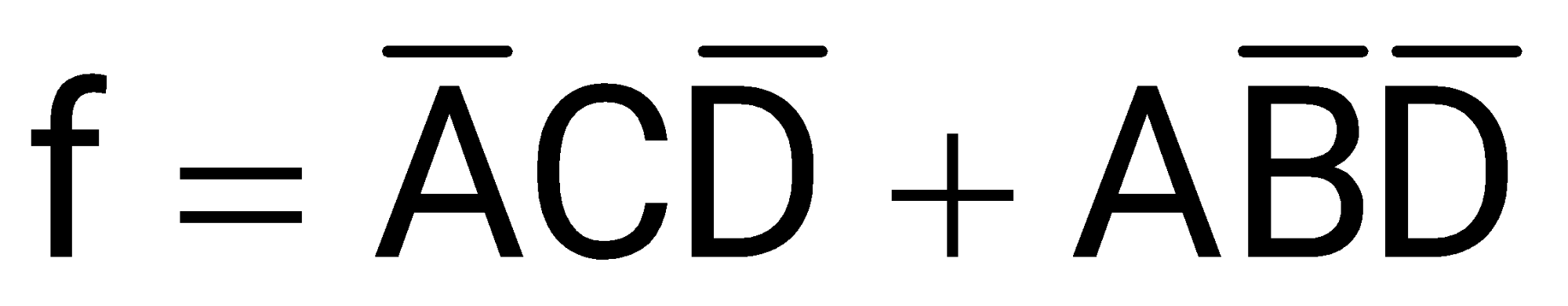

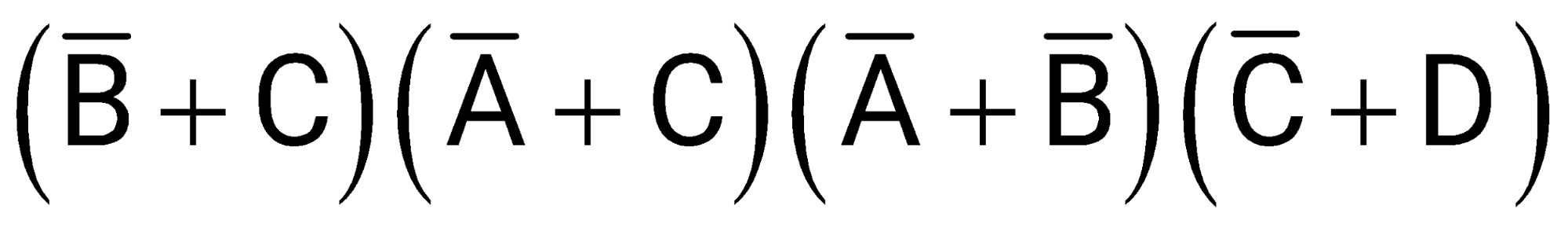

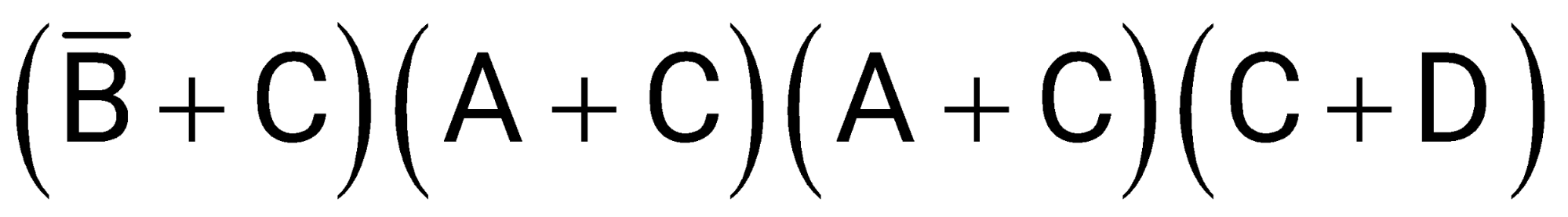

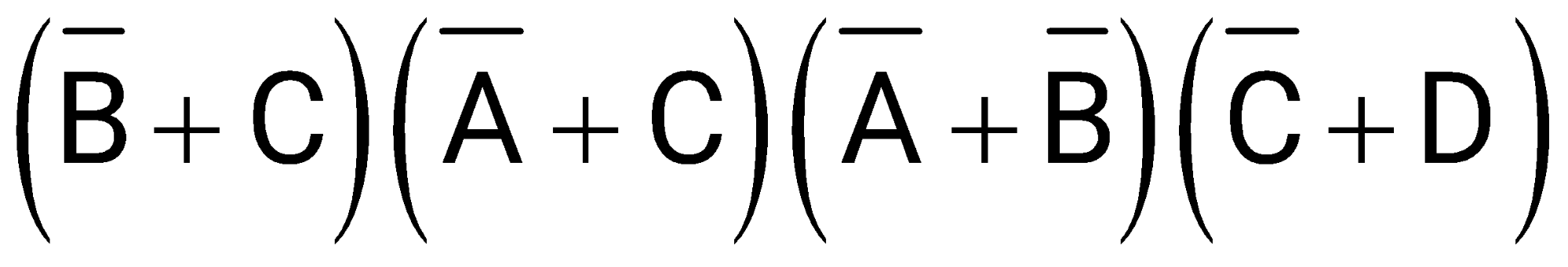

(0,1,3,4,5,7,9,11,12,13,14,15) is a maxterm representation of a Boolean function f(A,B,C,D) where A is the MSB and D is the LSB. The equivalent minimized representation of this function is

=

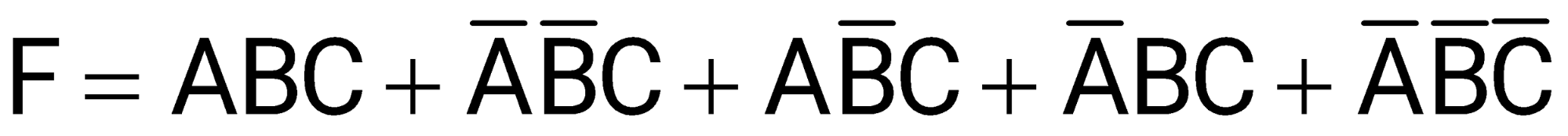

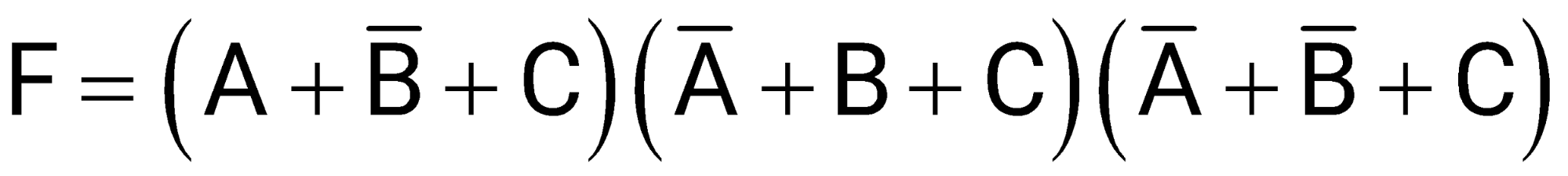

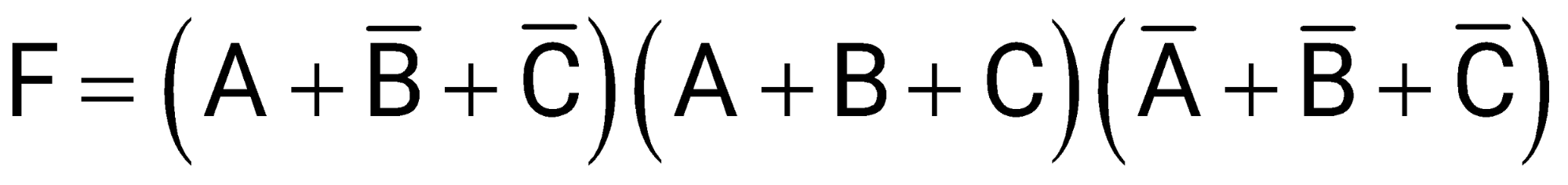

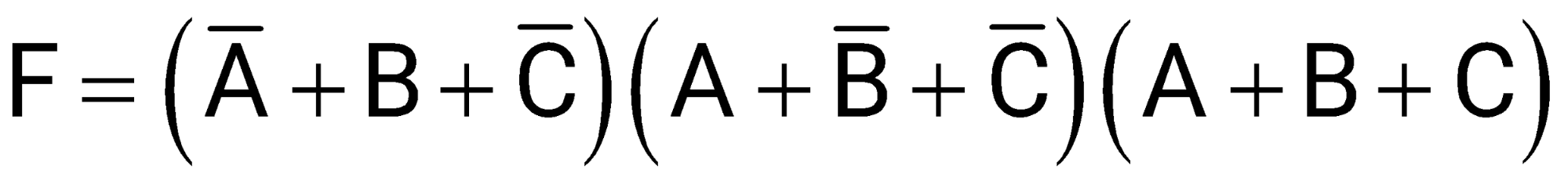

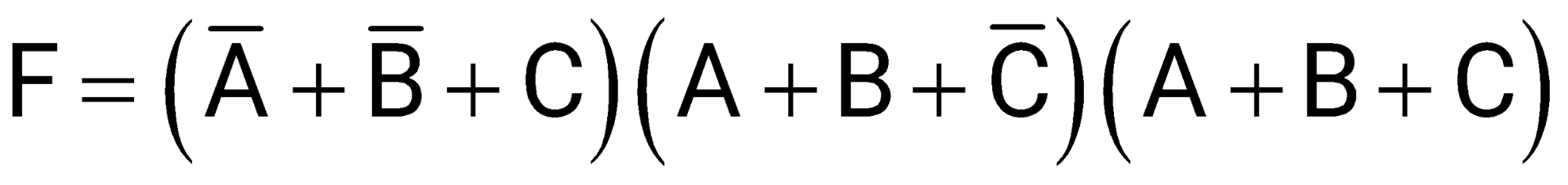

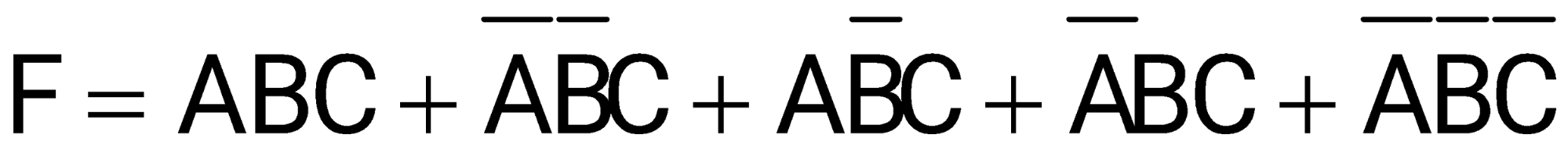

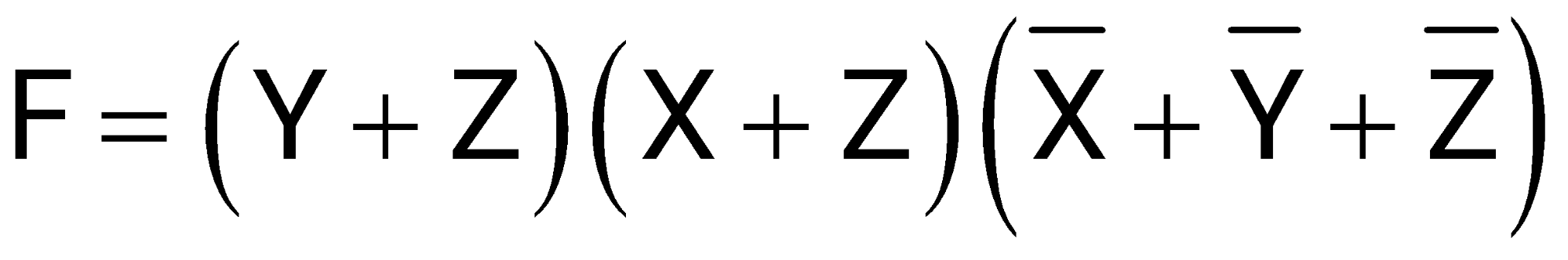

Consider the following sum of products expression, F.

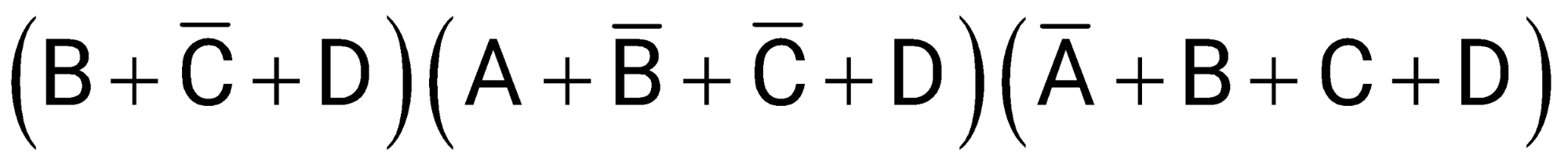

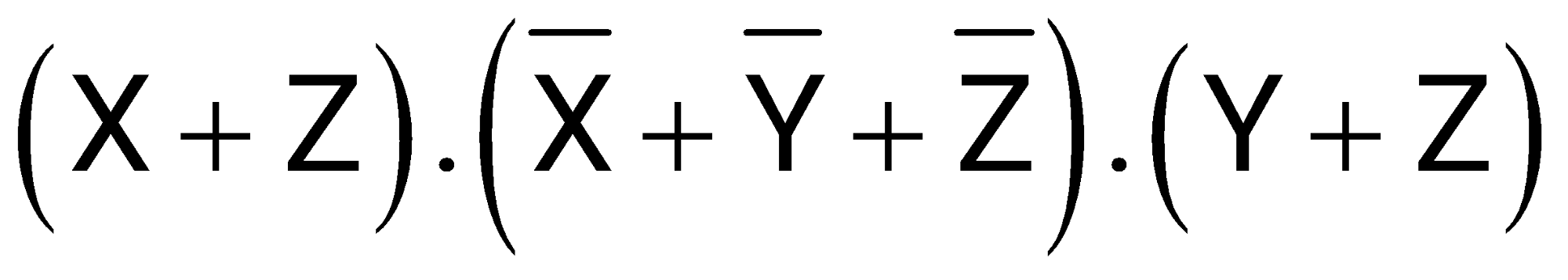

The equivalent product of sums expressions is

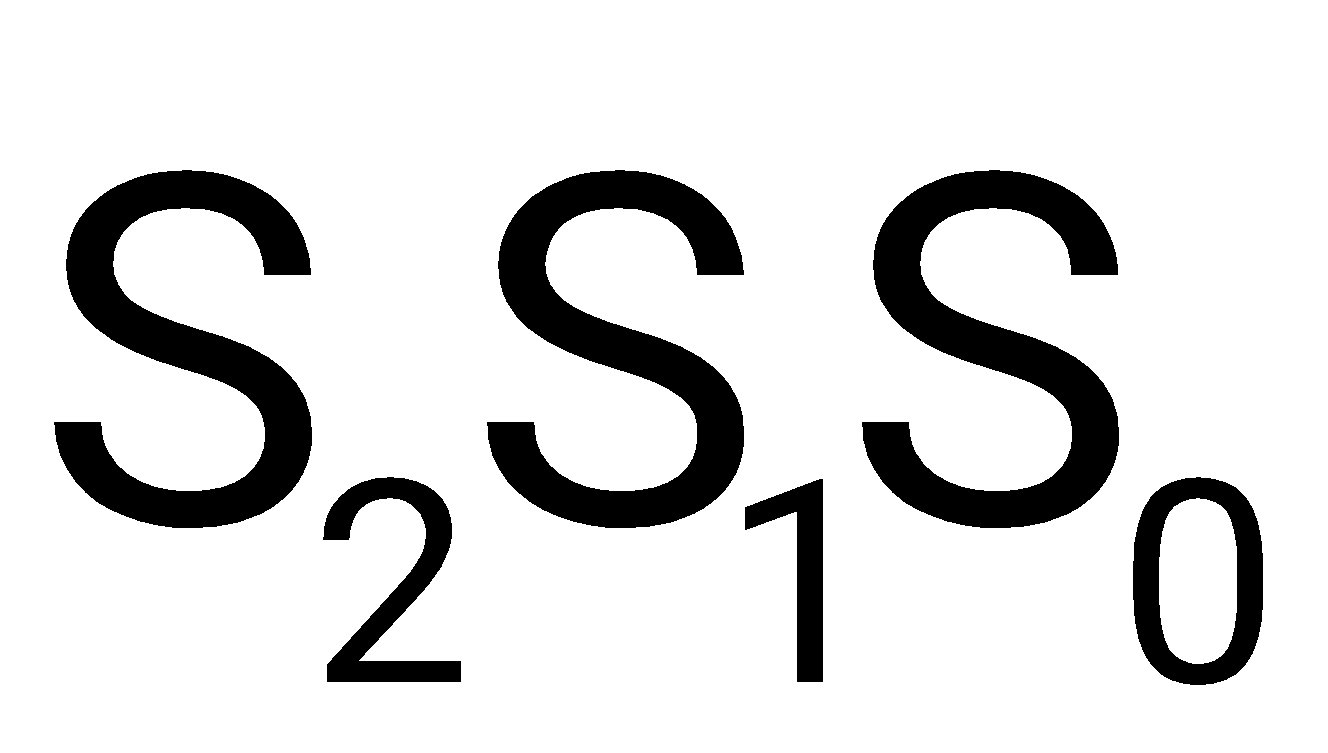

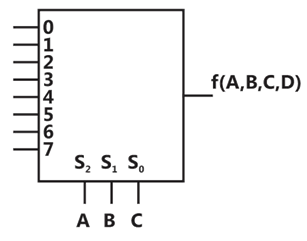

A Boolean function is to be implemented using an 8 x 1 multiplexer (A is MSB), The inputs ABC are connected to the select inputs of the multiplexer respectively.

Which one of the following options gives the correct inputs to pins 0,1,2,3,4,5,6,7 in order?

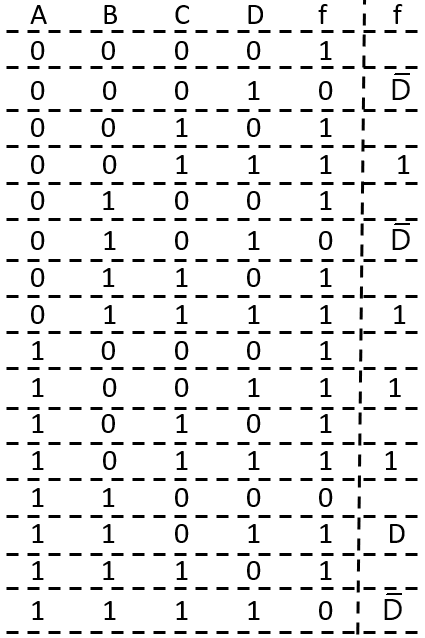

Truth table looks like:

Inputs are

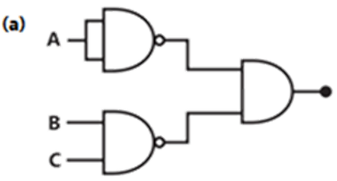

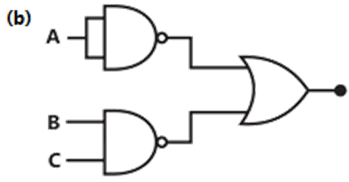

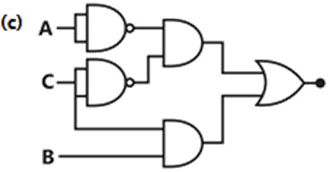

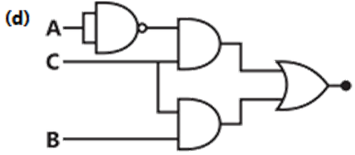

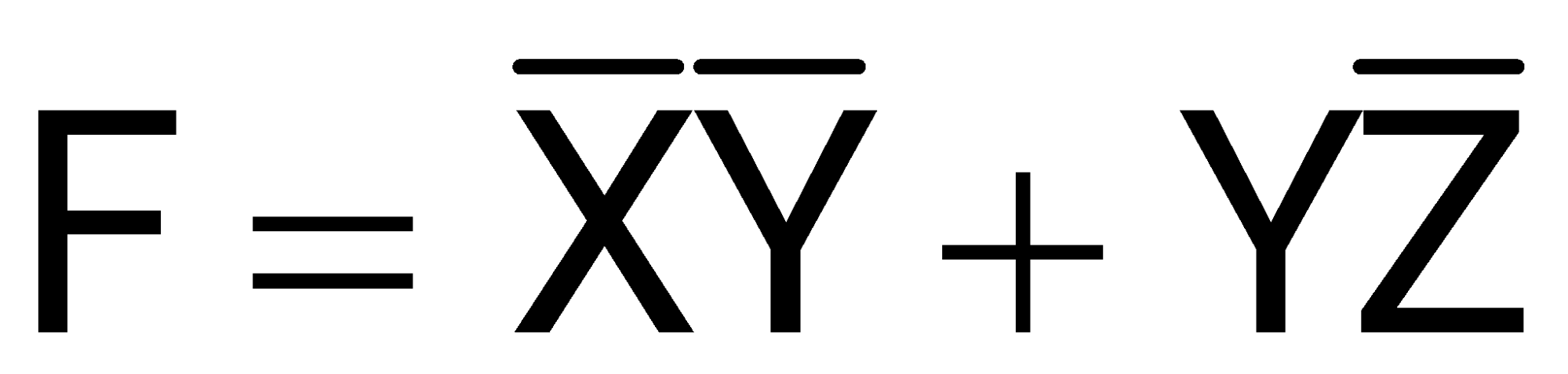

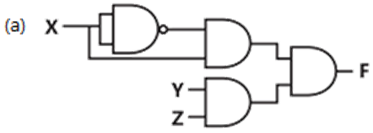

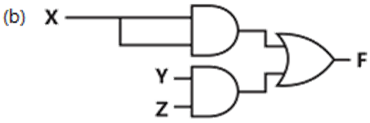

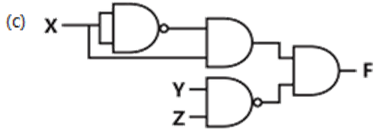

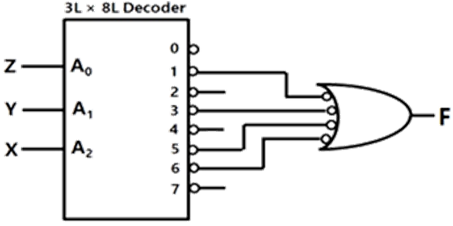

Which of the following logic circuits is a realization of the function F whose Karnaugh map is shown in figure

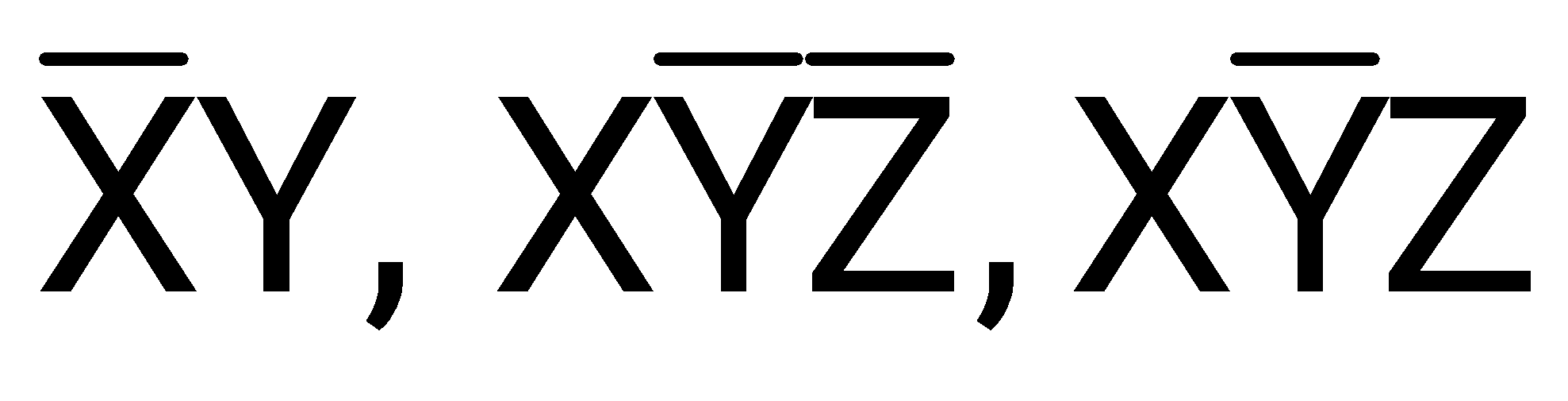

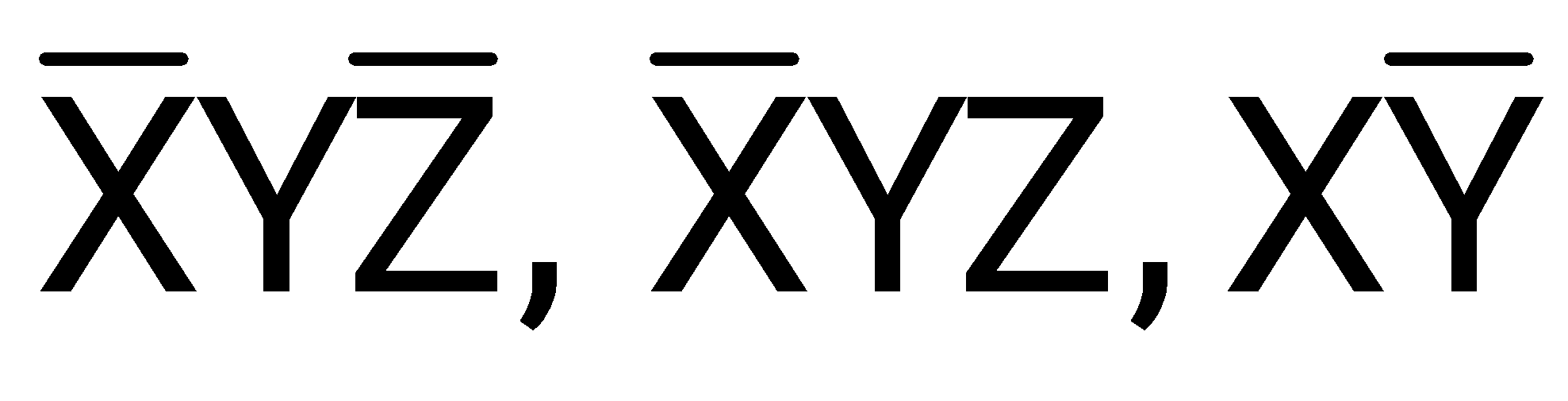

The given K-Map is shown below,

All the minterms can be covered in terms of two pairs and the

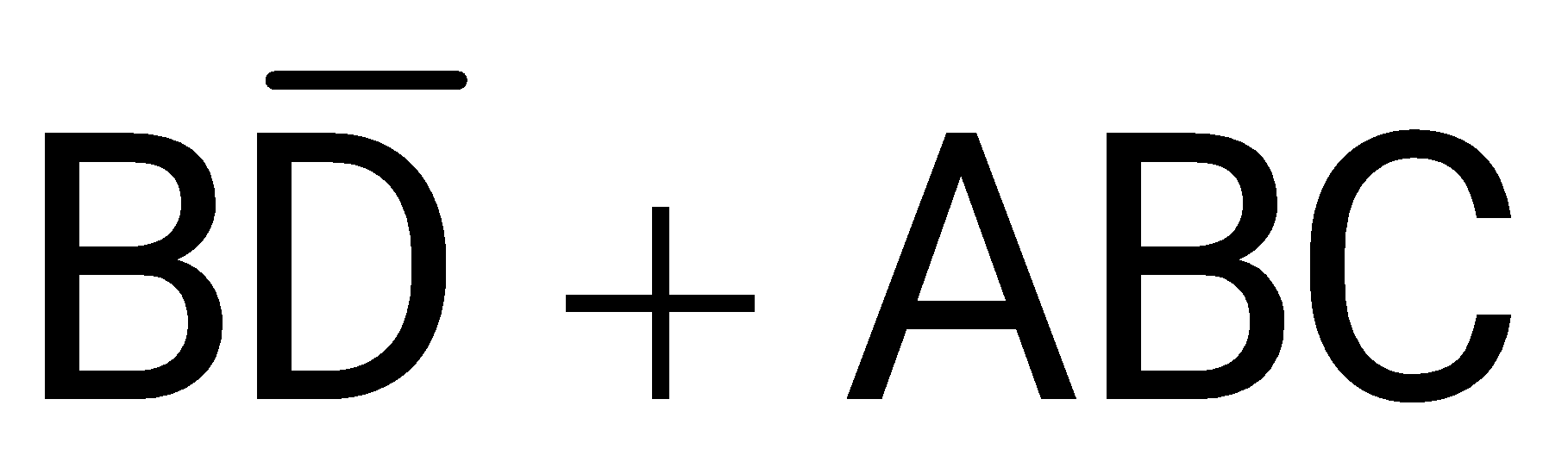

Minimized Boolean expression is,

F =

The Boolean expression for different options is,

Option A:

Option B:

Option C:

Option D:

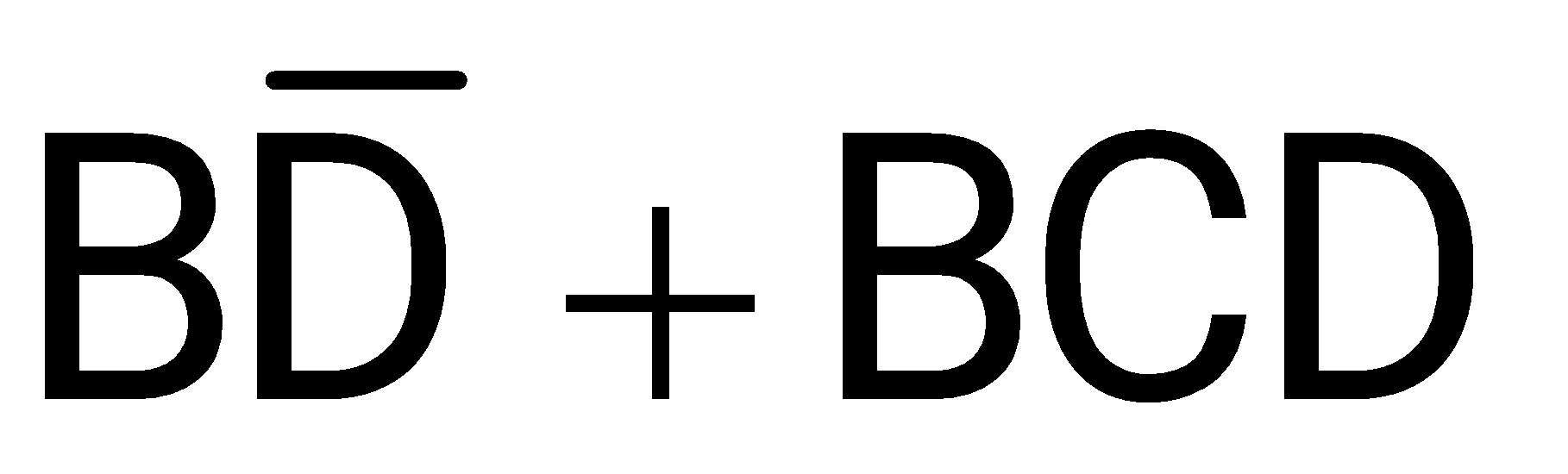

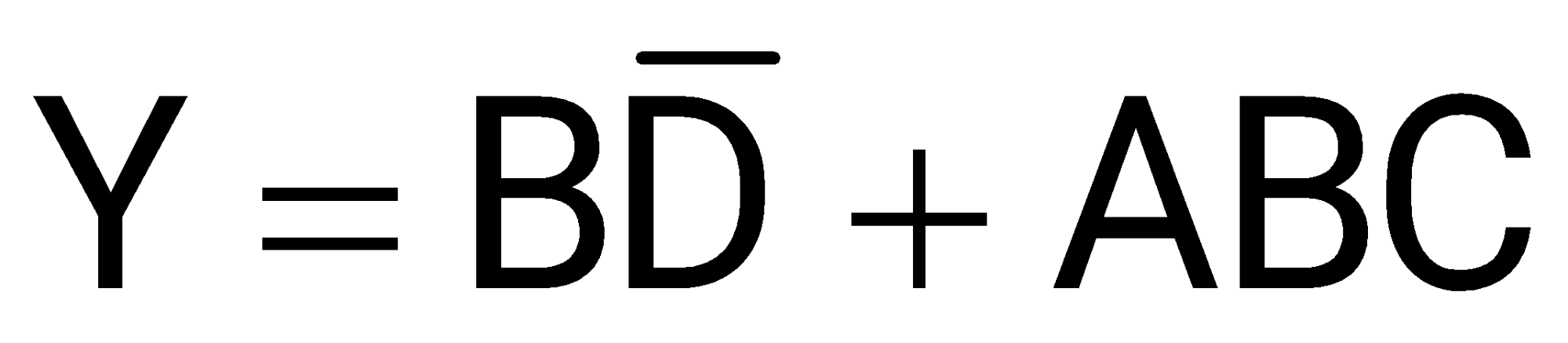

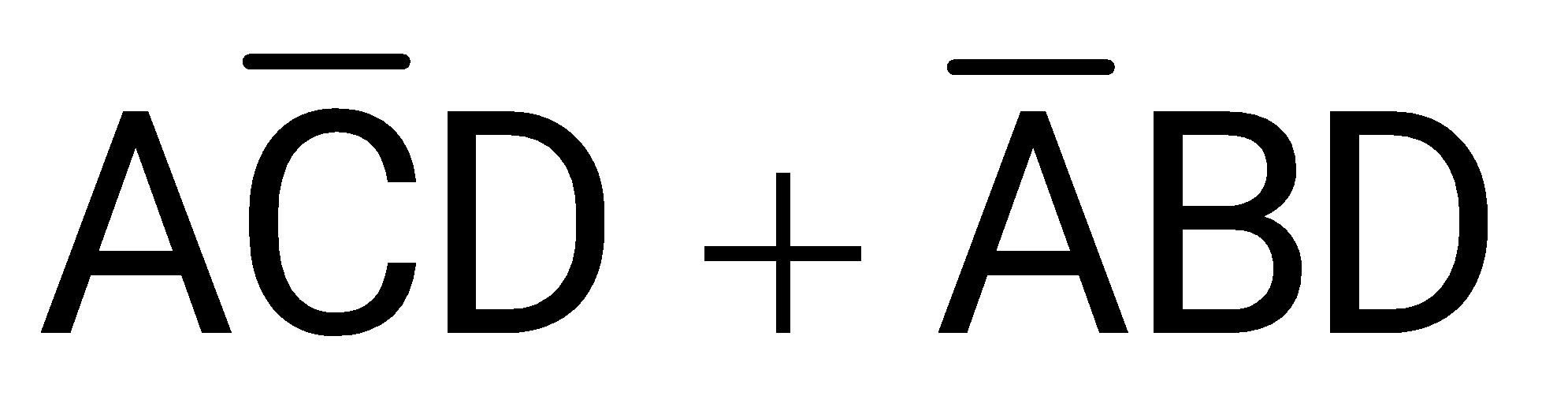

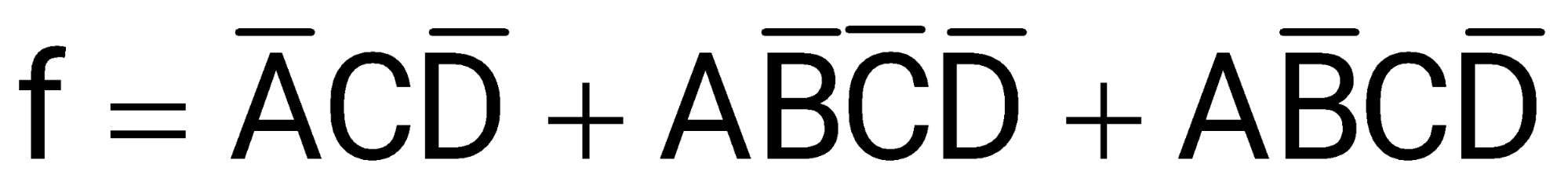

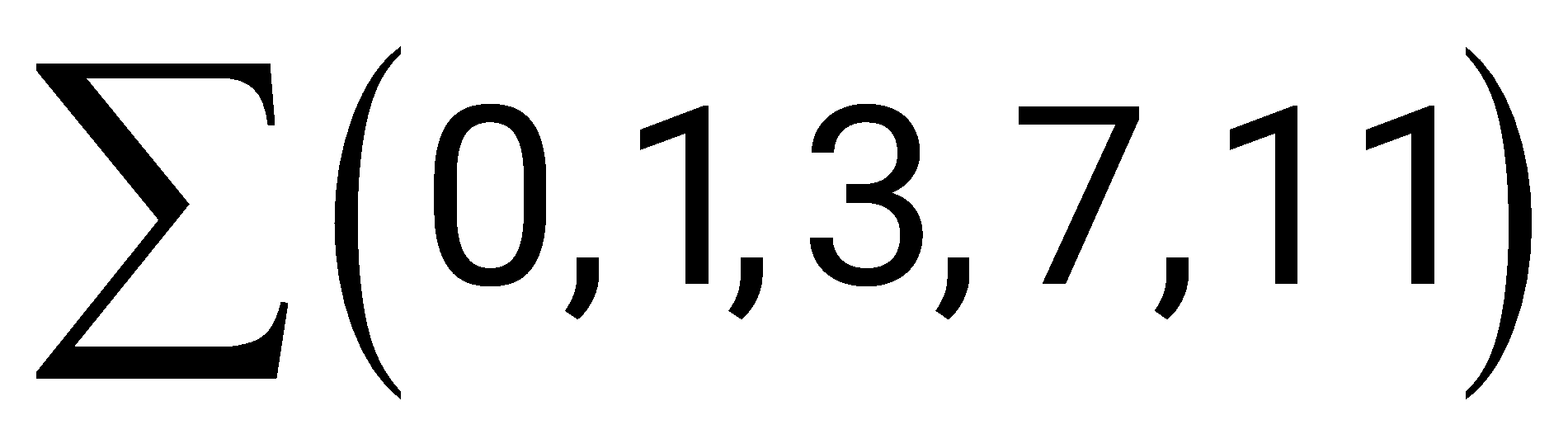

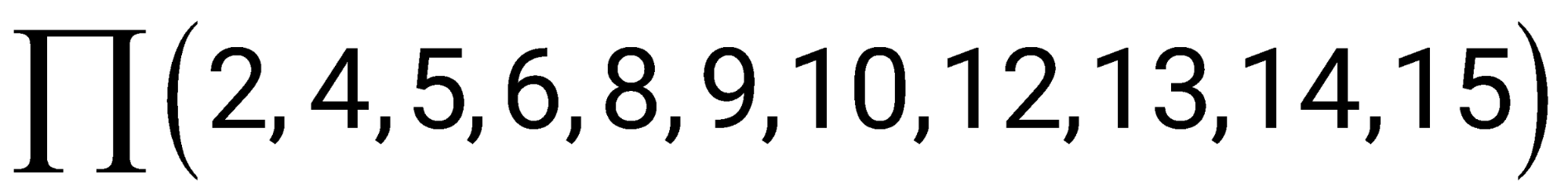

The SOP (sum off products) form of a Boolean function is , where inputs are A, B, C, D (A is MSB, and D is LSB). The equivalent minimized expression of the function is

F(A,B,C,D) = =

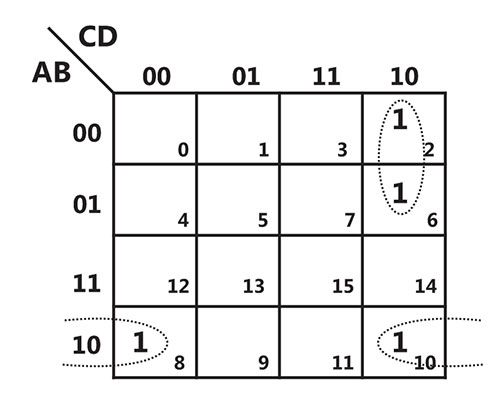

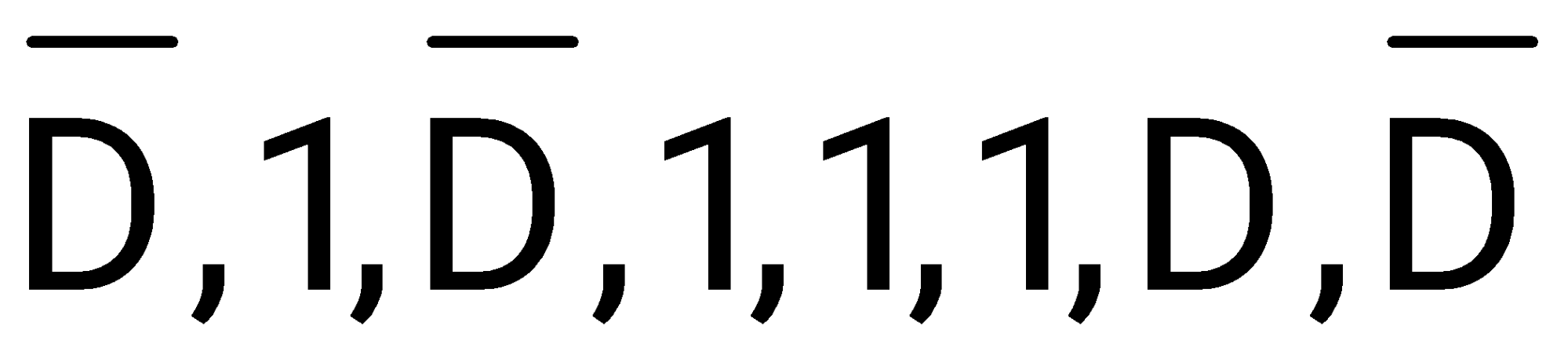

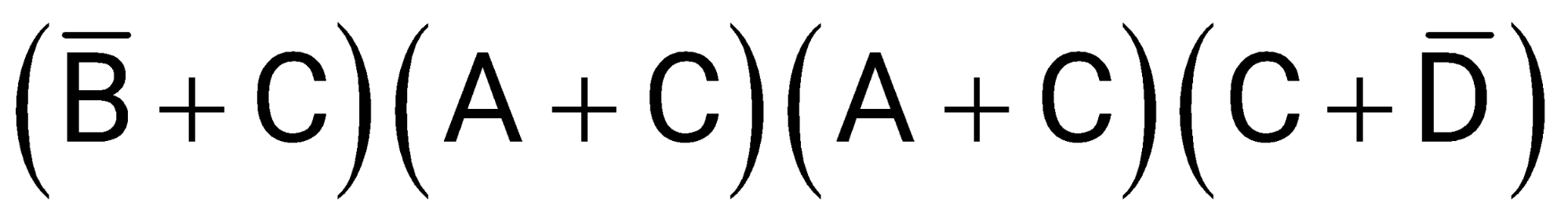

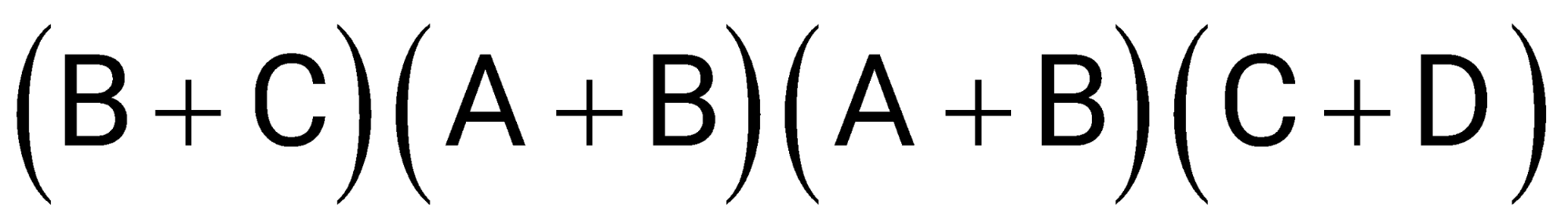

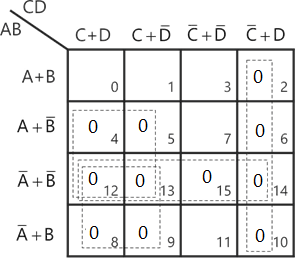

The k-map for POS implementation is shown below,

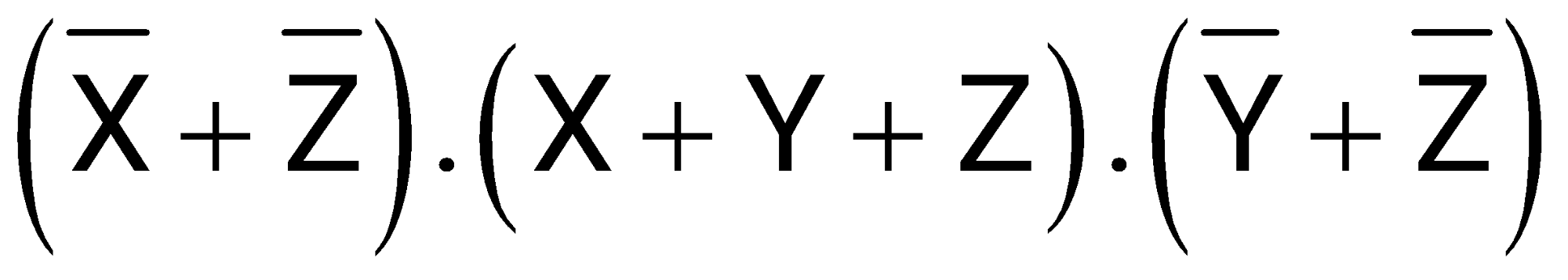

From the K-Map,

F(A,B,C,D) =

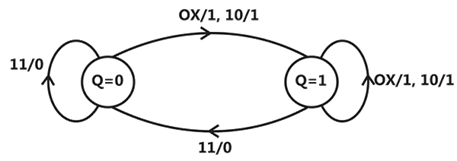

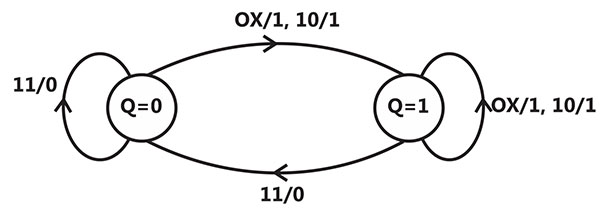

A state diagram of a logic gate which exhibits a delay in the output is shown in the figure, where X is the don’t care condition, and Q is the output representing the state.

The logic gate represented by the gate diagram is

This is the truth table of the gate mentioned in the diagram. From the truth table, we can see that the gate is clearly NAND Gate.

Note: While deriving the truth table no need to look at the state, we just need to focus on input-output combination.

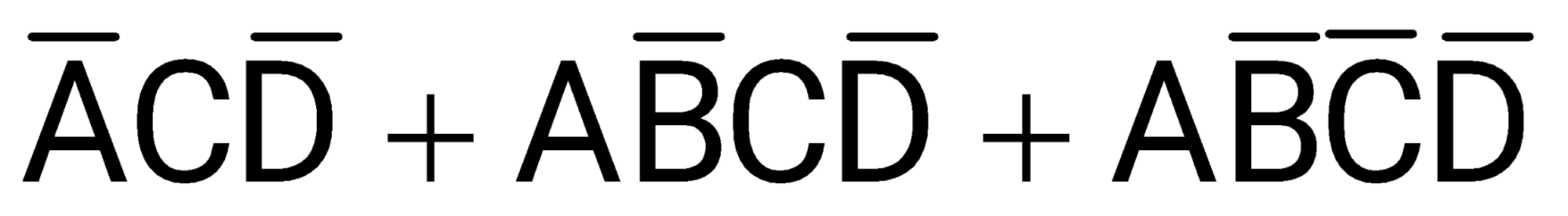

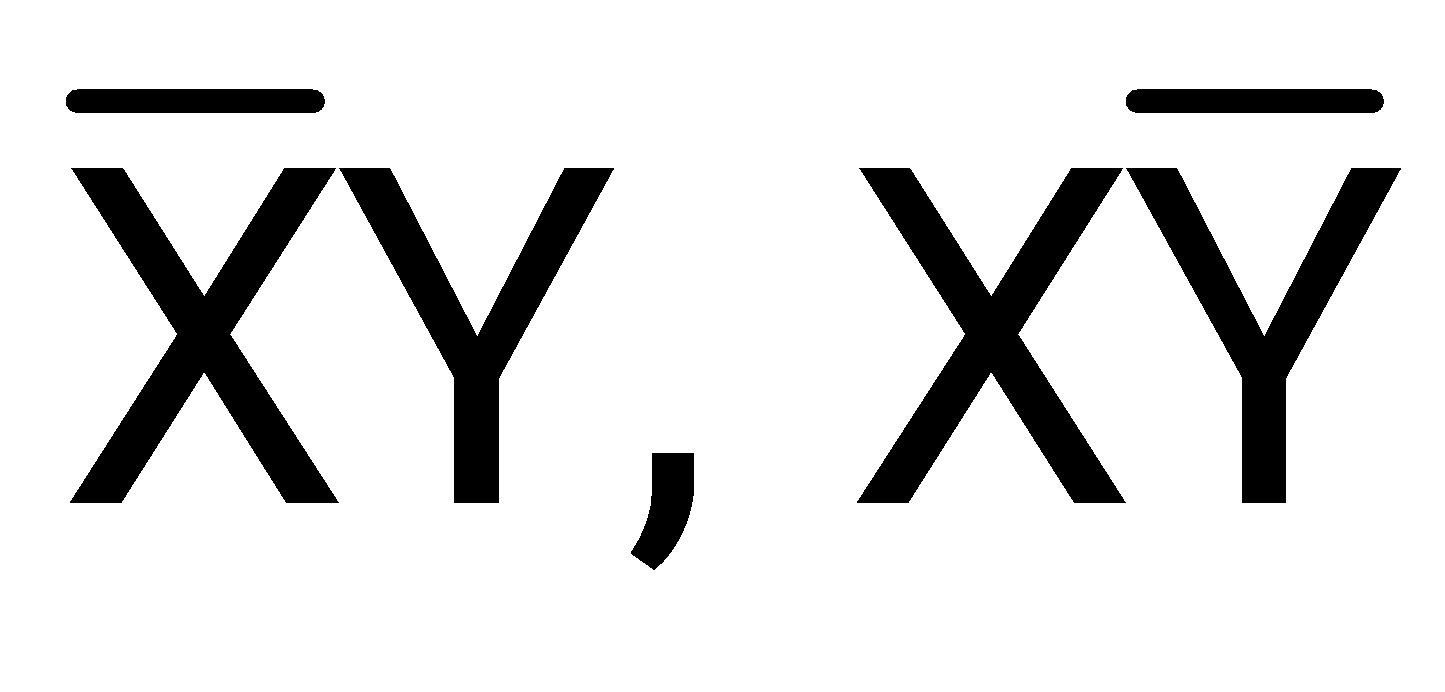

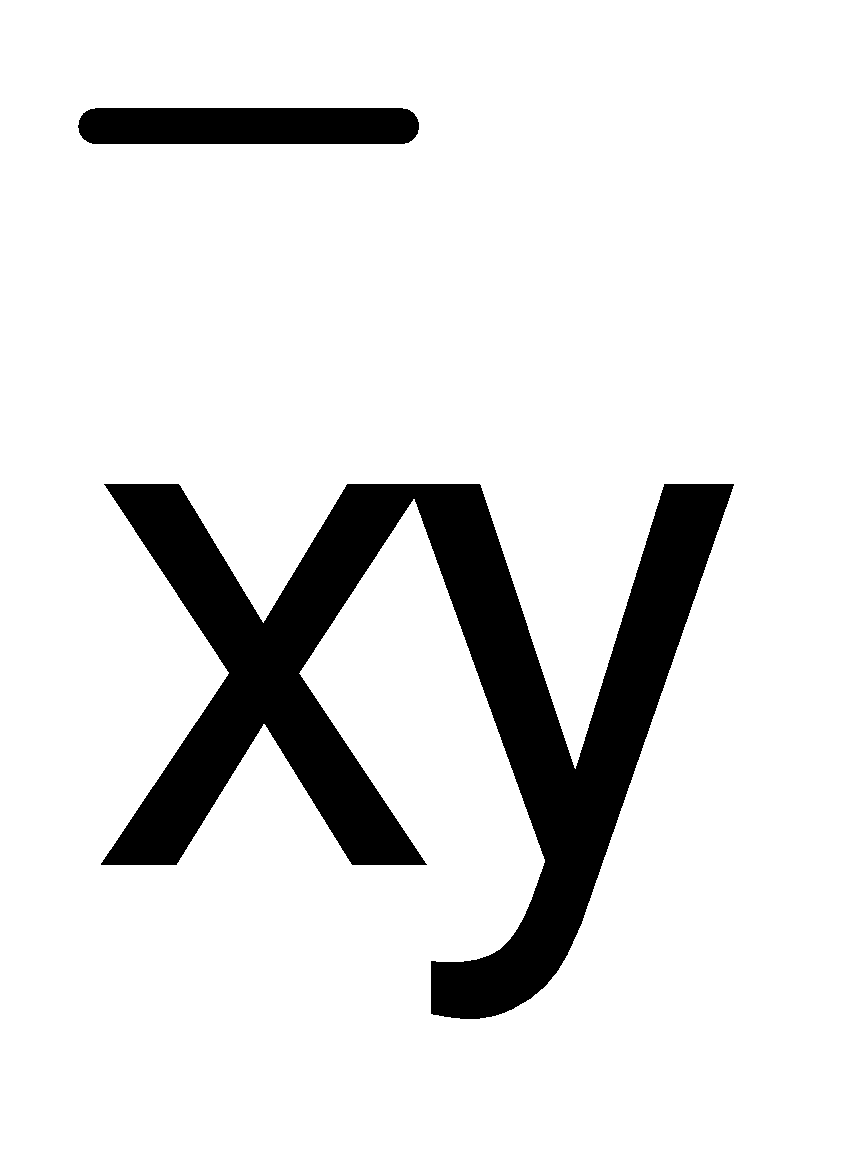

In the sum of products function, the prime implicant’s are

it is an implicant which is not a subset of another implicant.

So prime implicates are and

The output Y of a 2-bit comparator is logic 1 whenever the 2-bit input A is greater than the 2-bit input B. The number of combinations for which the output is logic 1, is

A>B

A=11 B=00, 01, 10 3

A=10 B=00, 01 2

A=01 B=00 1

A=00 B X 0

Total combination = 6

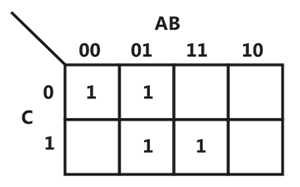

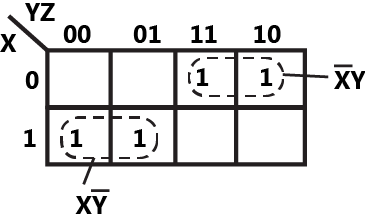

The following Karnaugh map represents a function F.

A minimized form of the function F is

Using K-map simplification, the minimized function in SOP form is given by,

The following Karnaugh map represents a function F.

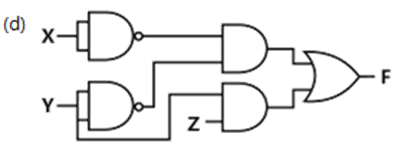

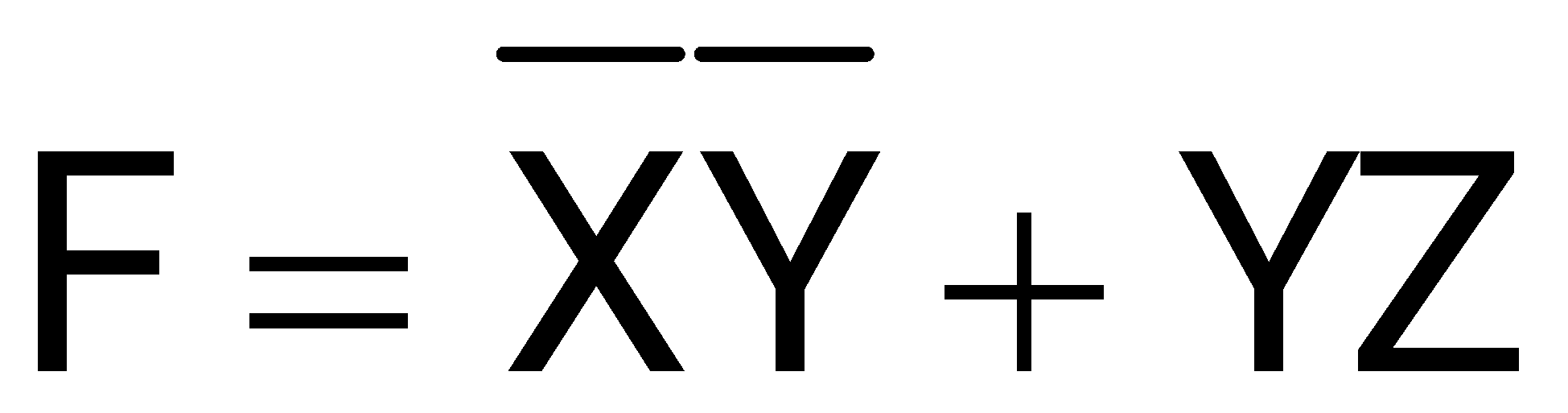

Which of the following circuits is a realization of the above function F?

Simplifying above K-Map

This is an AND-OR form

Or

SOP

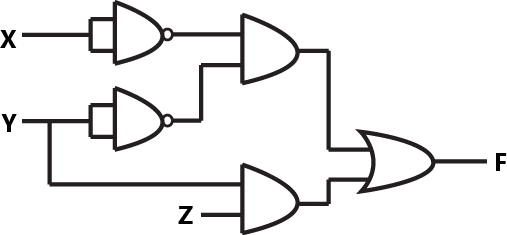

A 3 line to 8 line decoder, with active low outputs, is used to implement a 3-variable Boolean function as shown in the figure.

The simplified form of Boolean function F(A, B, C) Implemented in 'Product of Sum' form will be

Given output of the Decoder is active low

Input of the OR gate is bubbled input. So the OR gate can be treated as active high enabled.

Output of OR gate

Product of sum form

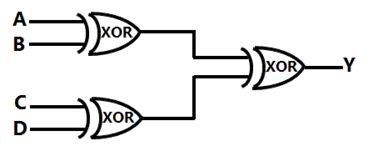

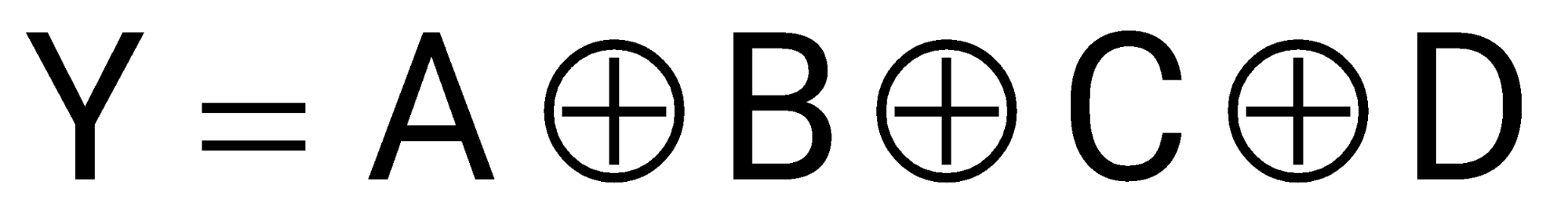

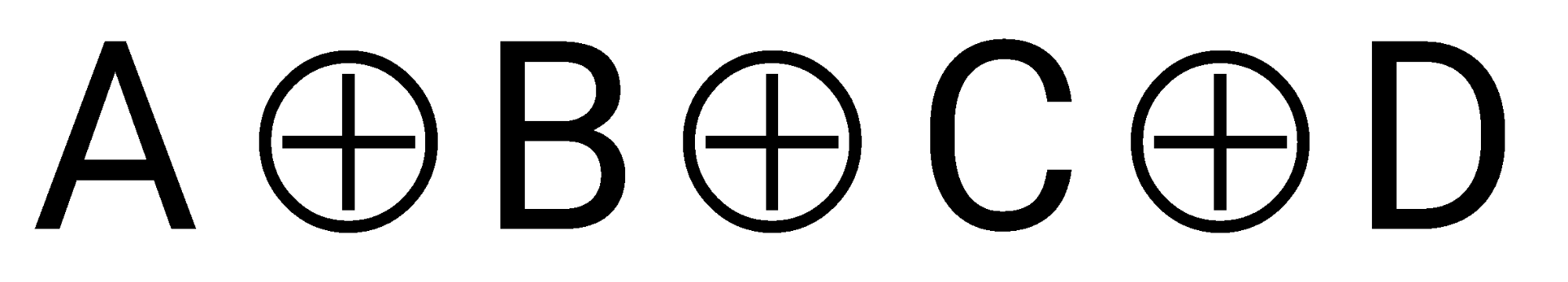

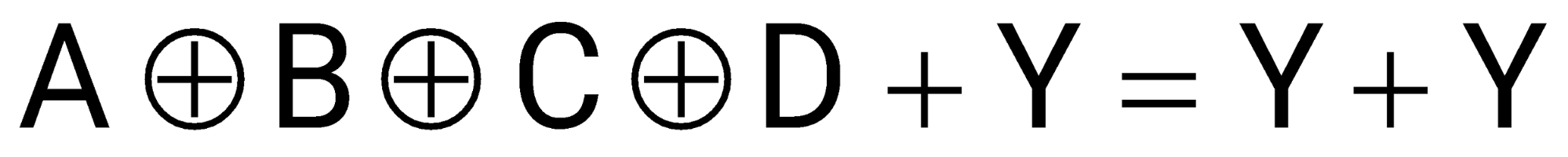

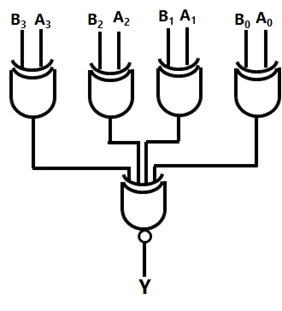

A, B, C and D are input bits, and Y is the output bit in the XOR gate circuit of the figure below. Which of the following statements about the sum S of A. B, C, D and Y is correct?

Expression of sum of 4 bits A, B, C and D is

Expression of Y=

Expression of S=

So, S is always zero or even

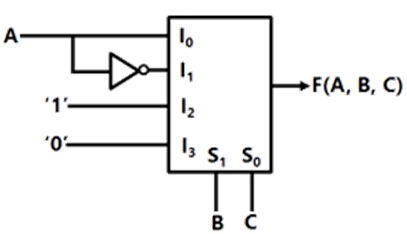

A 4 × 1 MUX is used to implement a 3-input Boolean function as shown in figure. The Boolean function F(A, B, C) implemented is

For 4x1 mux output = where X,Y = select lines

Here B and C are select lines

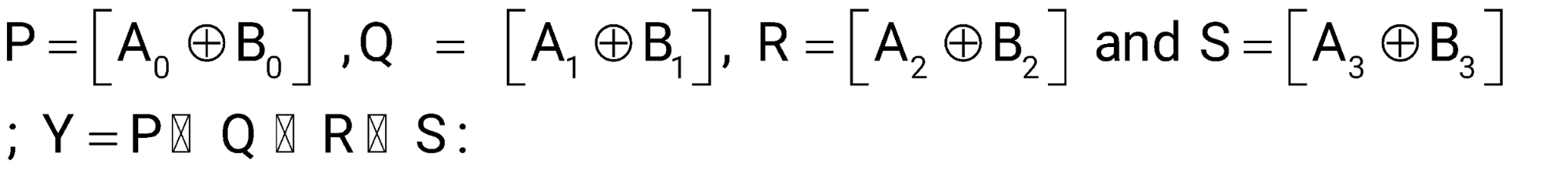

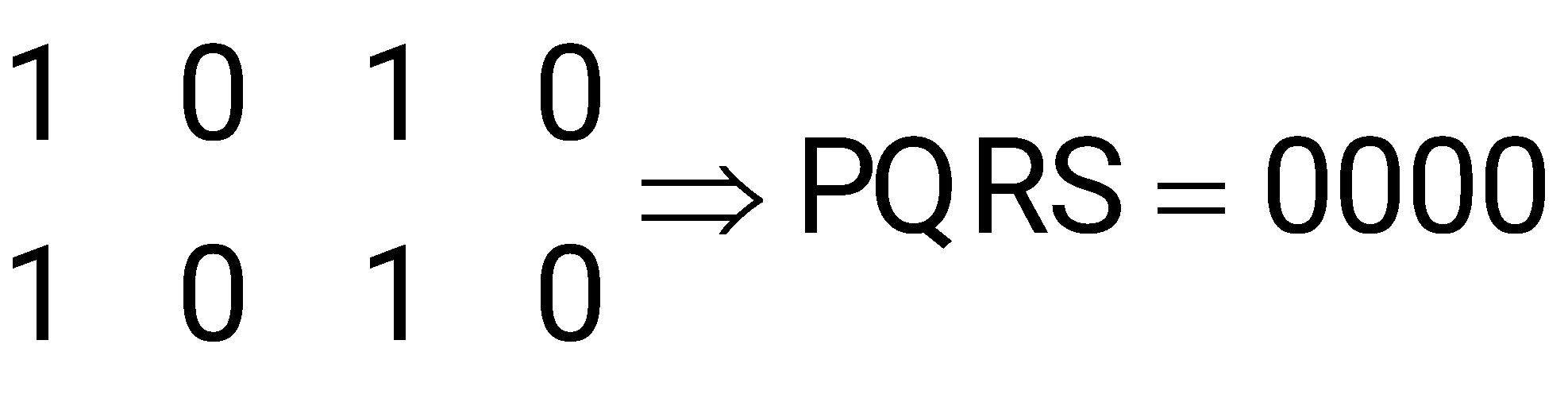

A digital circuit, which compares two numbers, is shown in figure. To get output Y = 0, choose one pair of correct input numbers.

When PQRS=odd numbers of 1 then only output Y will be logic 0

(a)

(b)

(c)

(d)

Only option (d) satisfy this condition

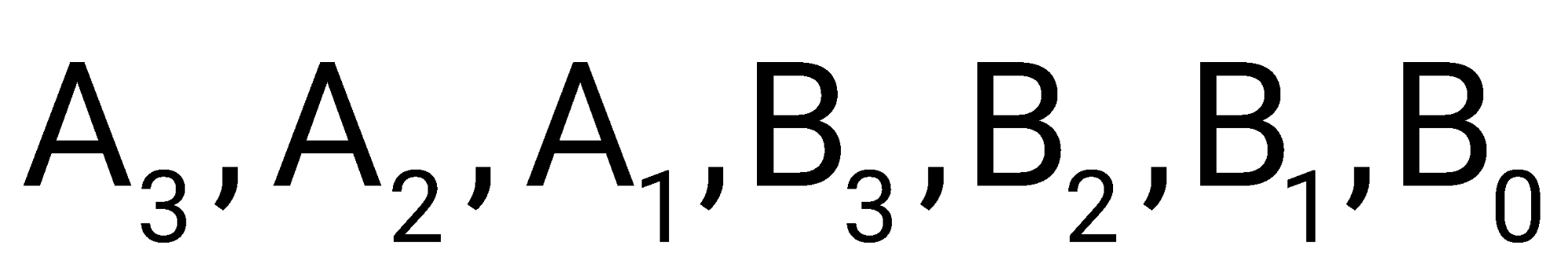

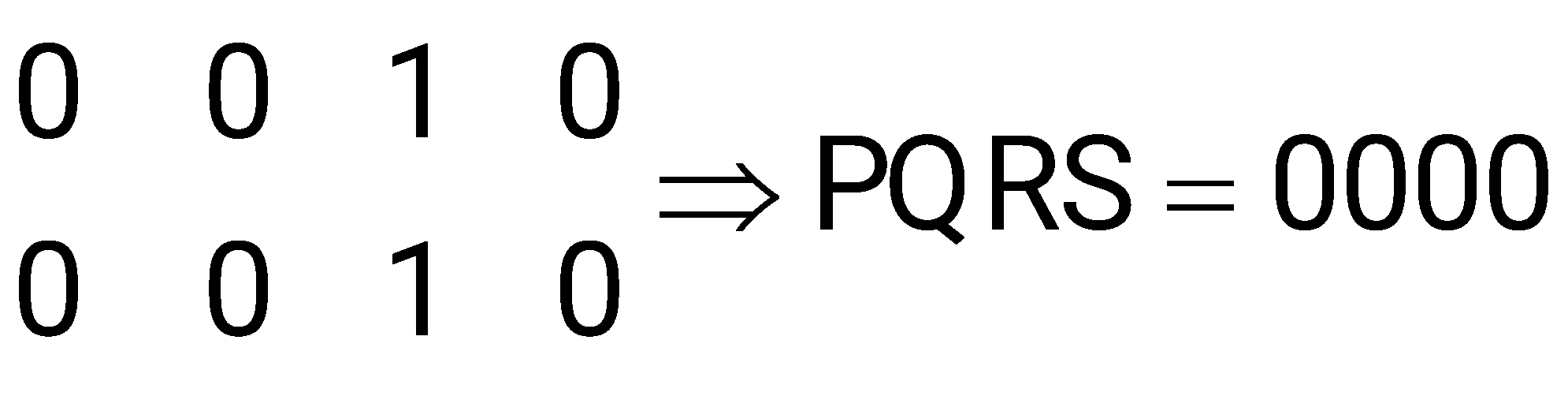

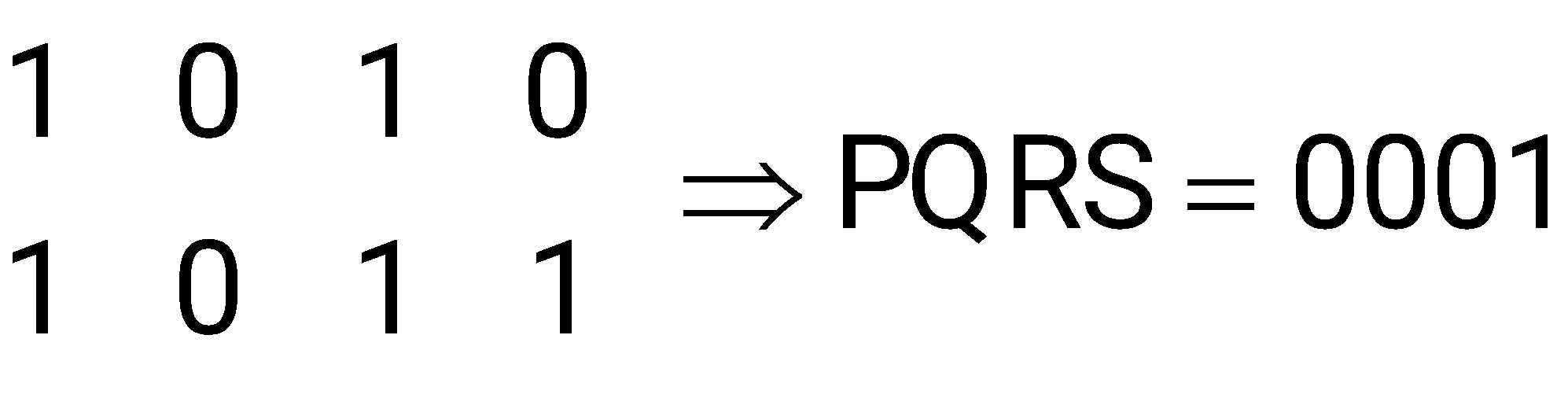

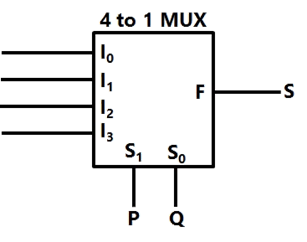

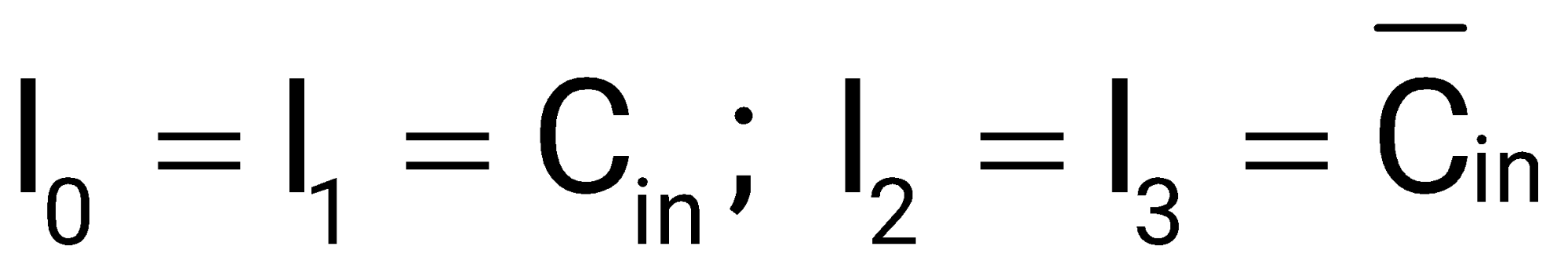

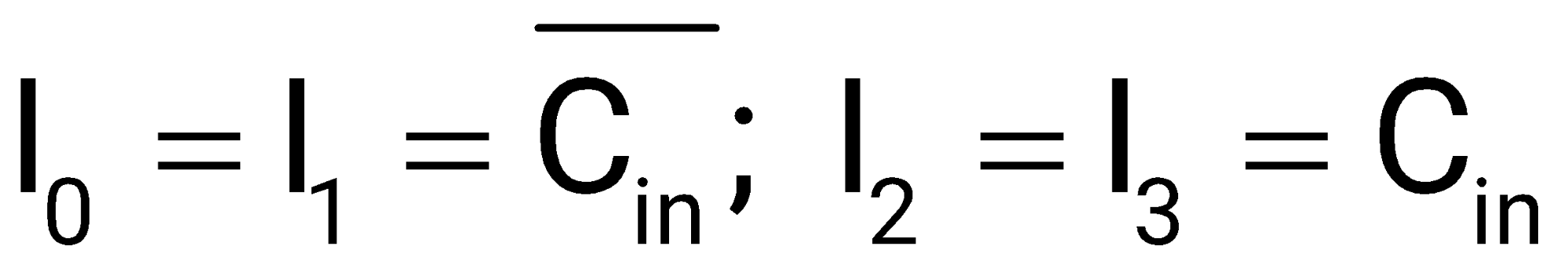

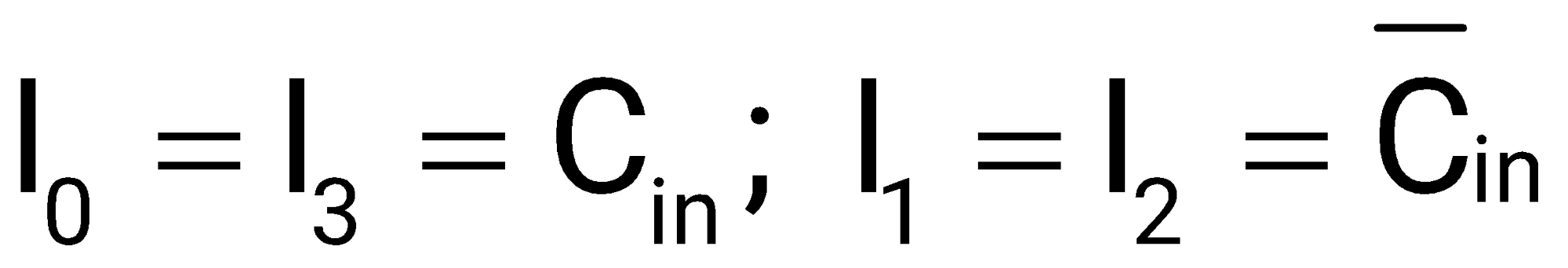

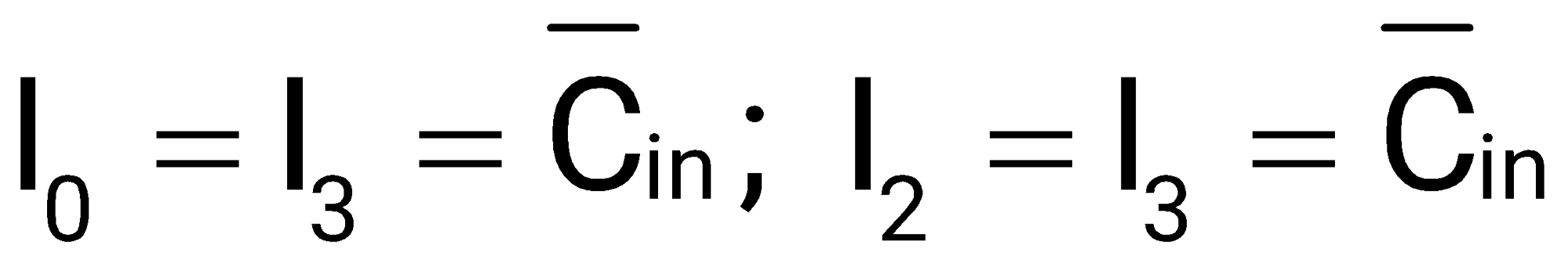

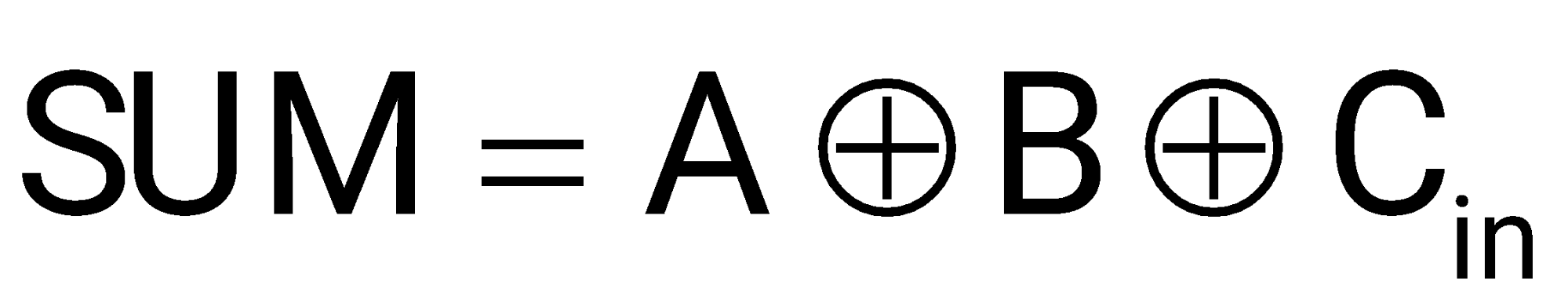

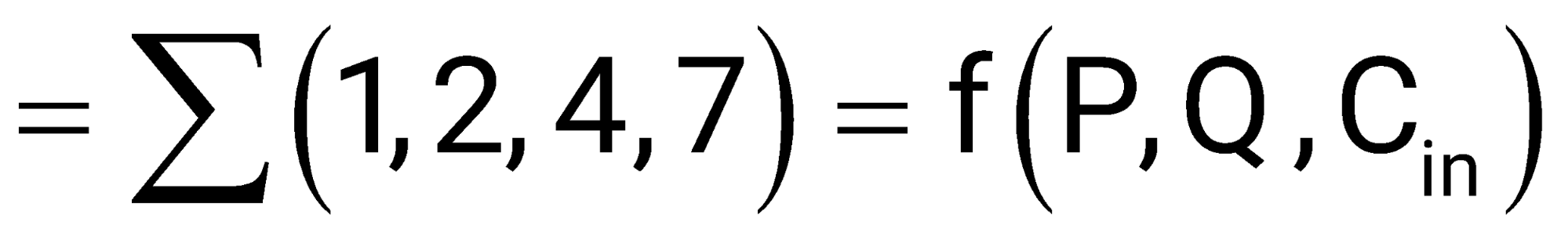

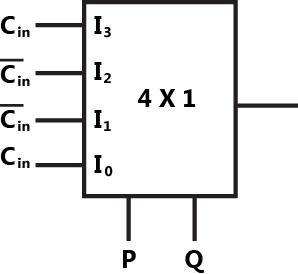

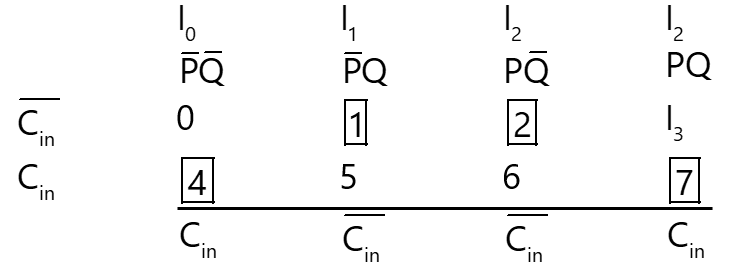

Figure shows a 4 to 1 MUX to be used to implement the sum S of a 1-bit full adder with input bits P and Q and the carry input. Which of the following combinations of inputs to and of the MUX will realize the sum S?

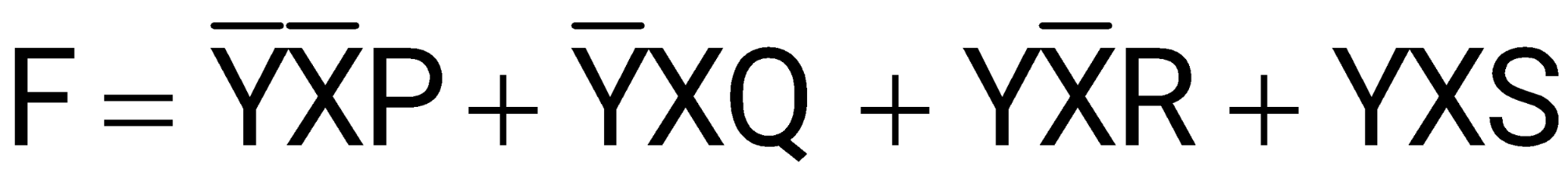

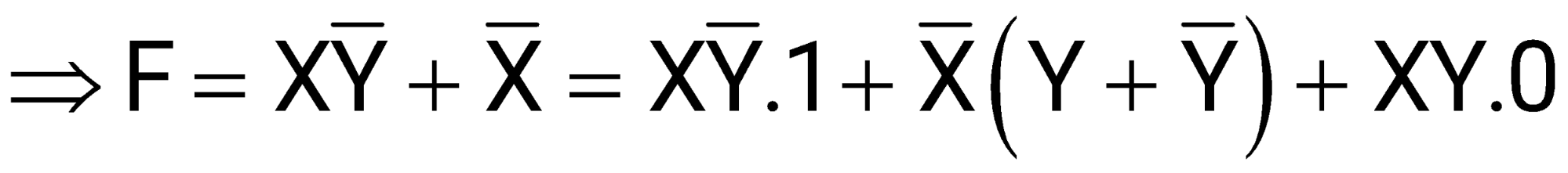

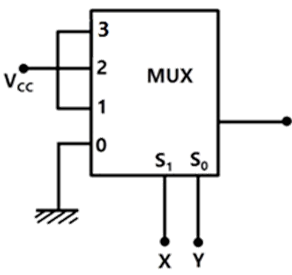

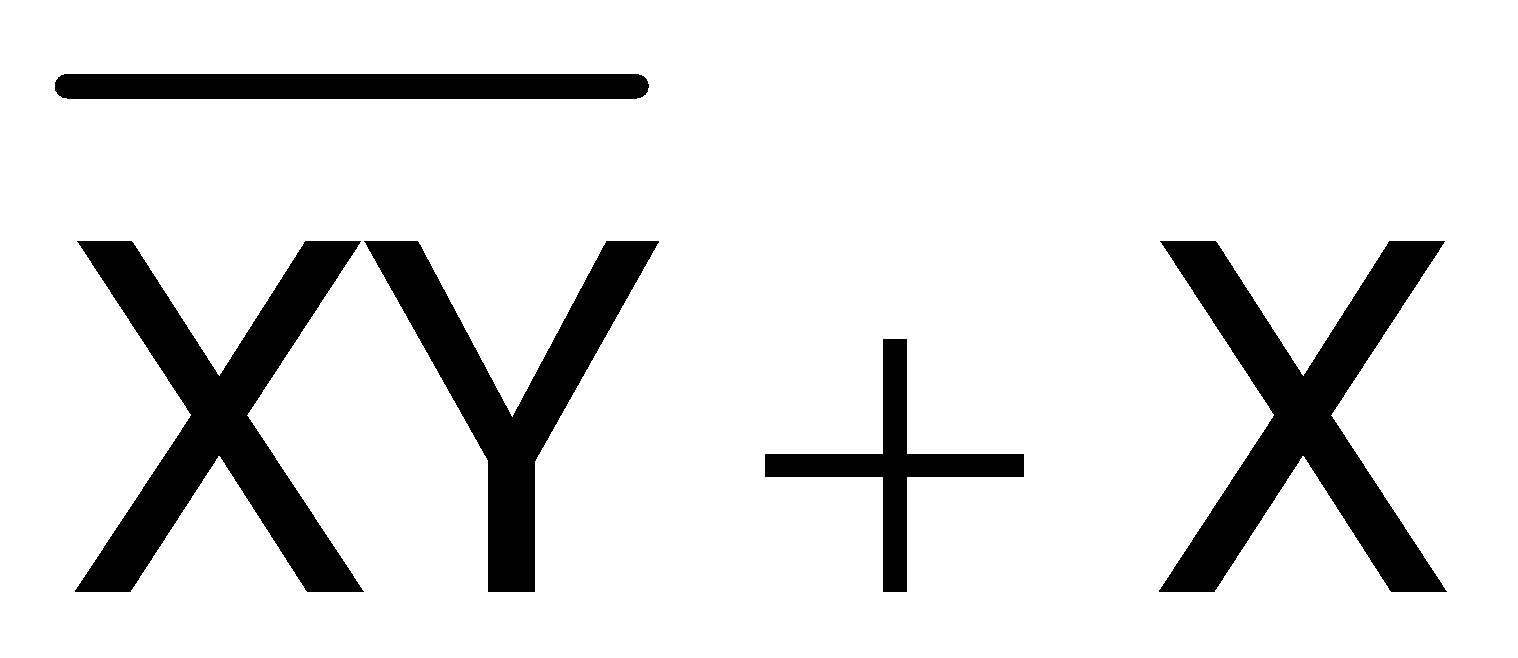

The output of the 4-to-1 MUX shown in figure is

For a 4:1 mux

Output

Apply Distribution theorem

OR

Method-2

Truth table:

X | Y | F |

0 | 0 | 0 |

0 | 1 | 1 |

1 | 0 | 1 |

1 | 1 | 1 |

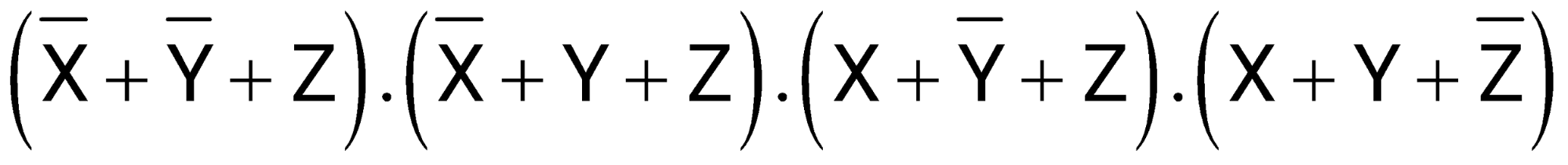

The minimal product of sums function described by the K-map

K-map for product of sum

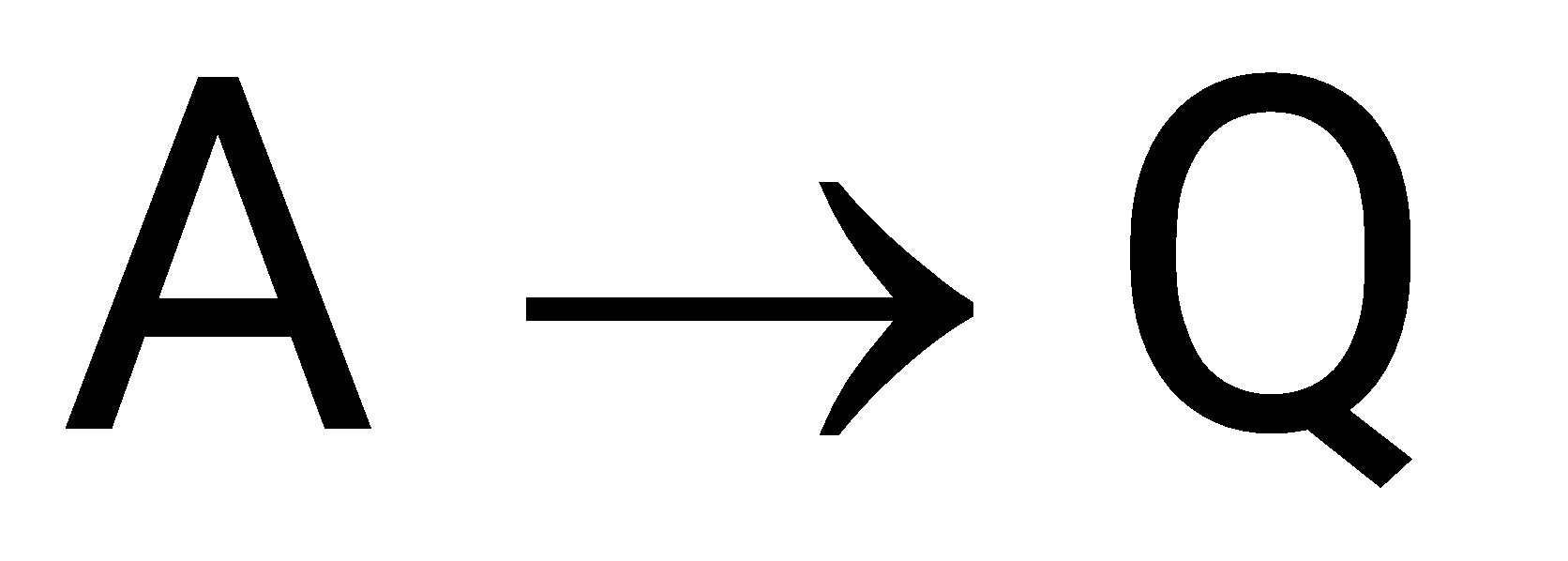

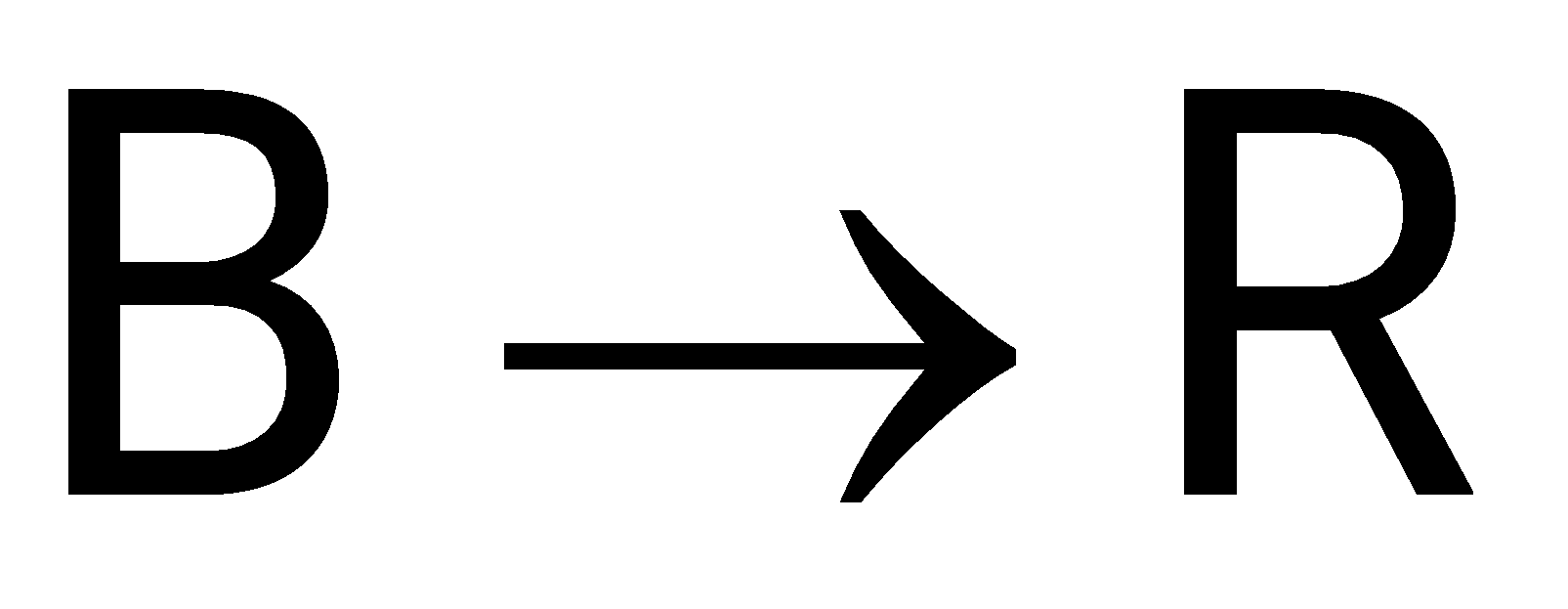

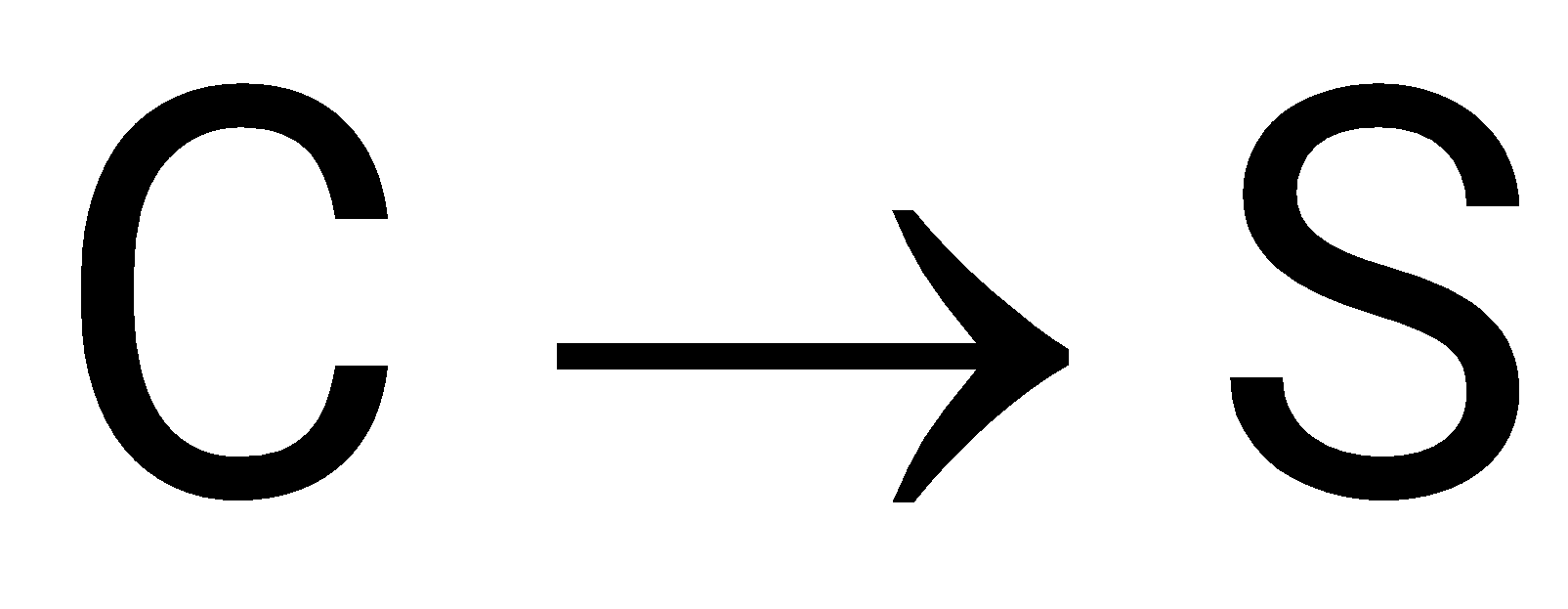

Match the following

Logic Function

(A) (P) Sum

(B) (Q) NAND

(C) (R) Carry

(S) NOR

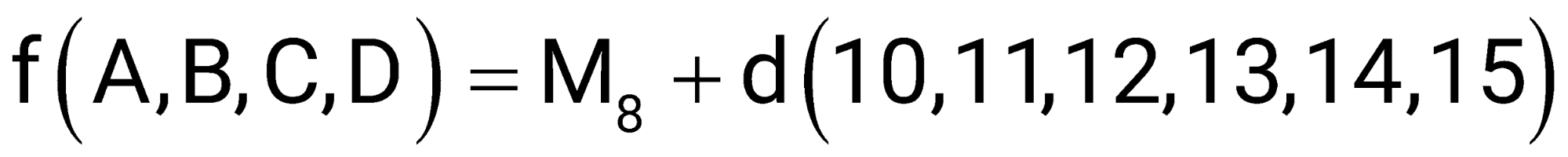

In a digital combinational circuit with 4 inputs (A, B, C, D), it is required to obtain an output of logical 1 only for the input combination (A=1; B=C=D=0). It is known that the following combinations of input are forbidden:

ABCD= 1010, 1011, 1100, 1101, 1110, 1111

Evaluate the logical expression for the output and realize the same with two input NAND gates. Assume that complements of inputs are not available.

Output is 1 for input combination (A=1; B=C=D=0) i.e. 1000 and 1110, but 1110 is forbidden so only for input combination 1000 output is 1.

Realization of output using NAND Gates

A 3-input 2-output priority encoder has the following truth table where X’s indicate don’t care conditions. Realize the logic using NAND gates and inverters

|

|

|

| |

0 | 0 | 0 | 0 | 0 |

0 | 0 | 1 | 0 | 0 |

0 | 1 | X | 1 | 0 |

1 | X | X | 1 | 1 |

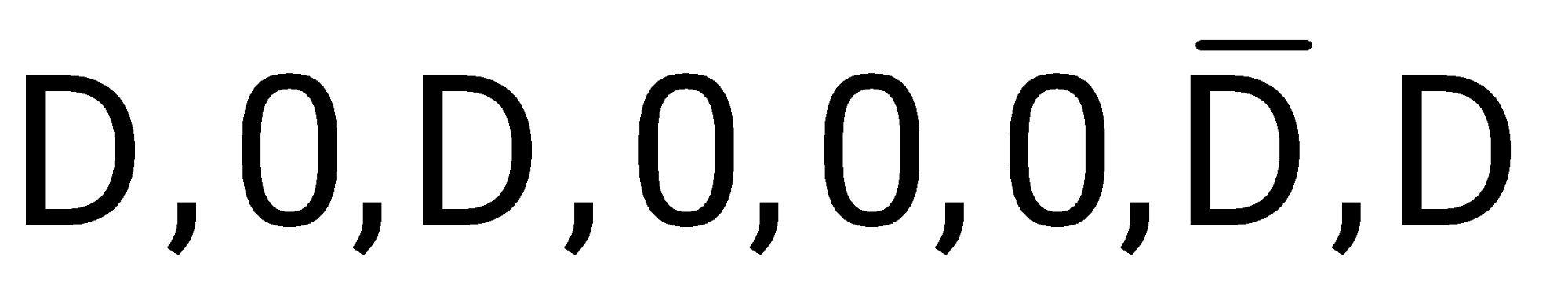

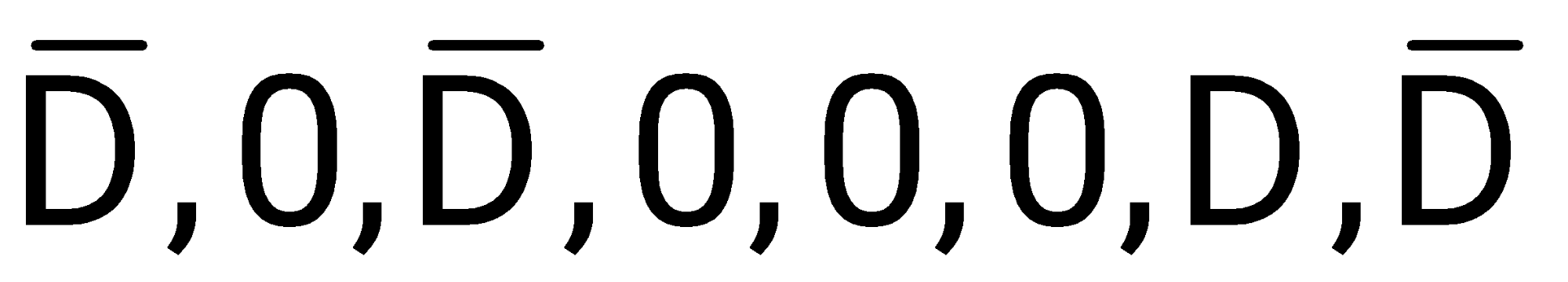

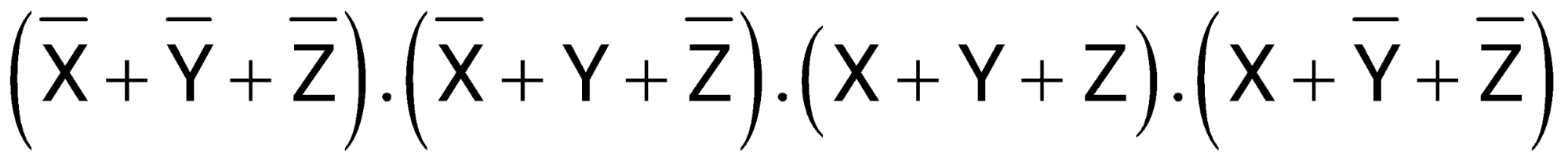

K-Map for

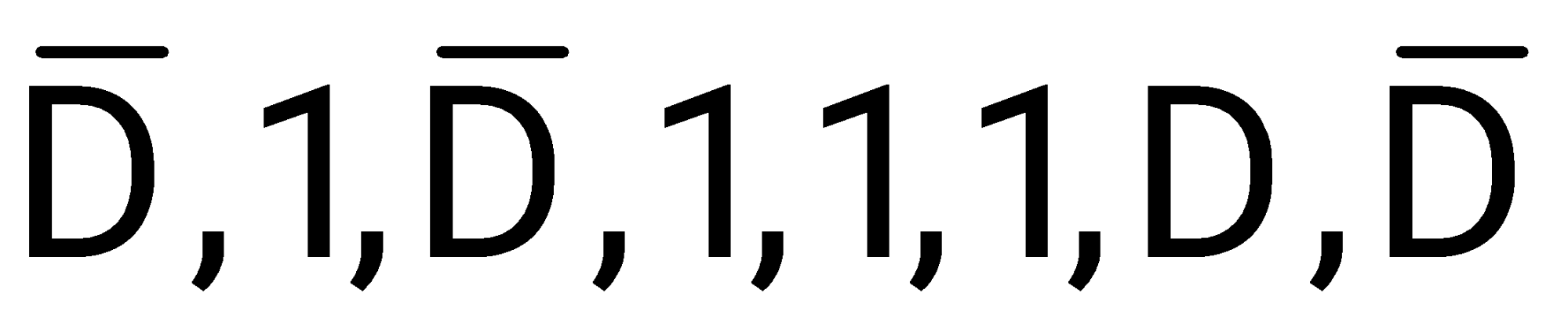

K-Map for

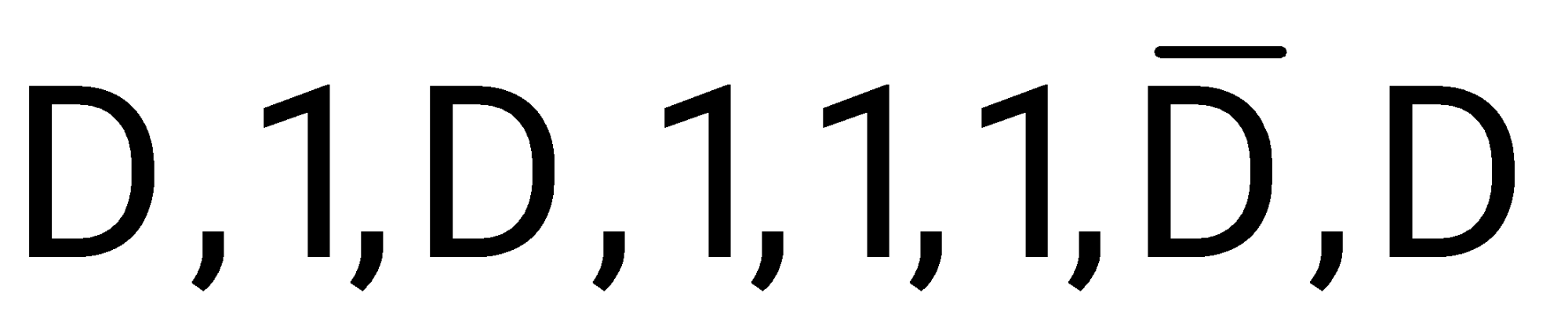

Realization of logic

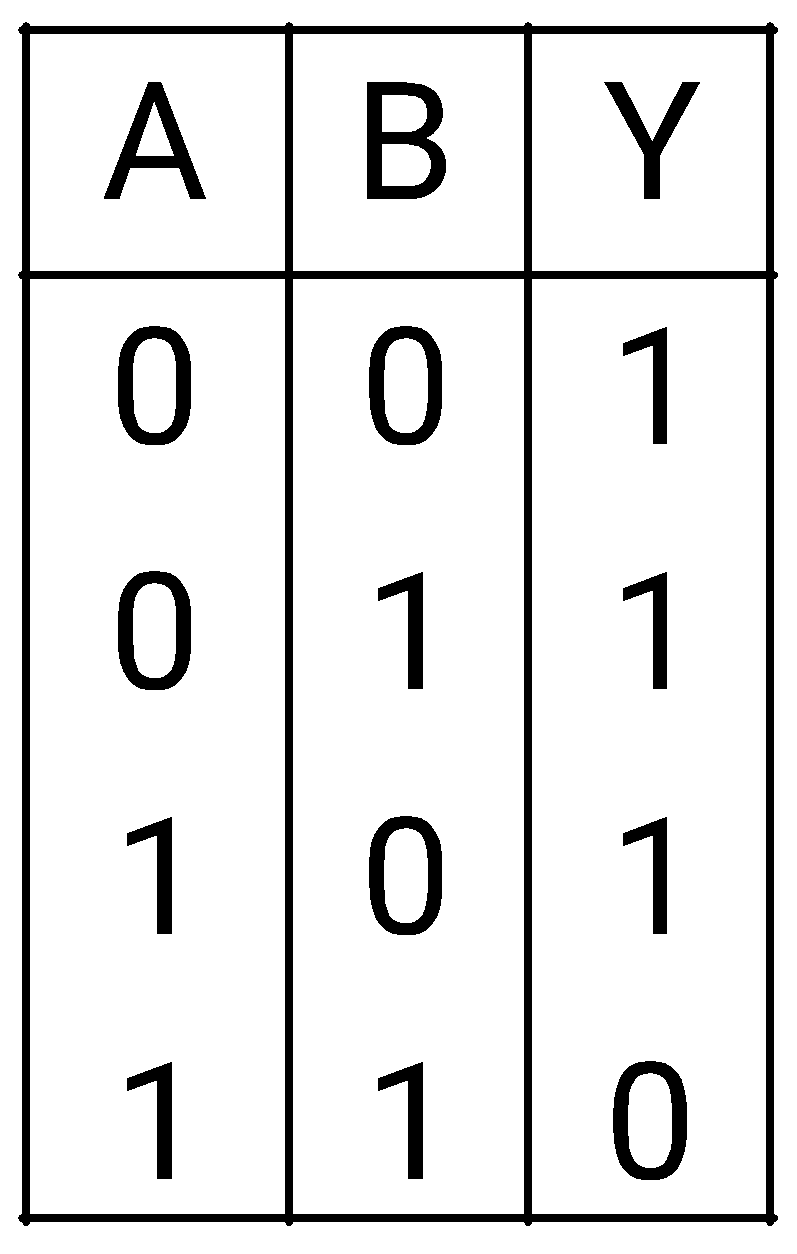

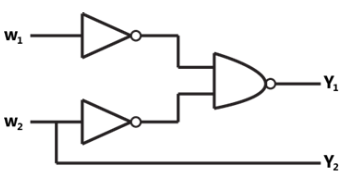

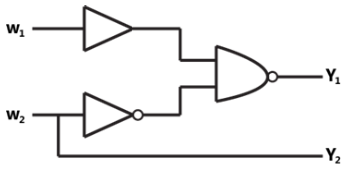

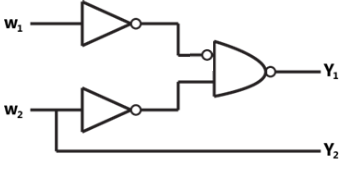

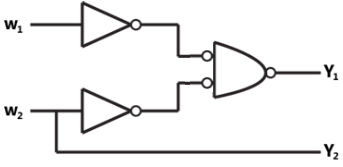

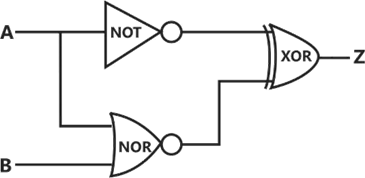

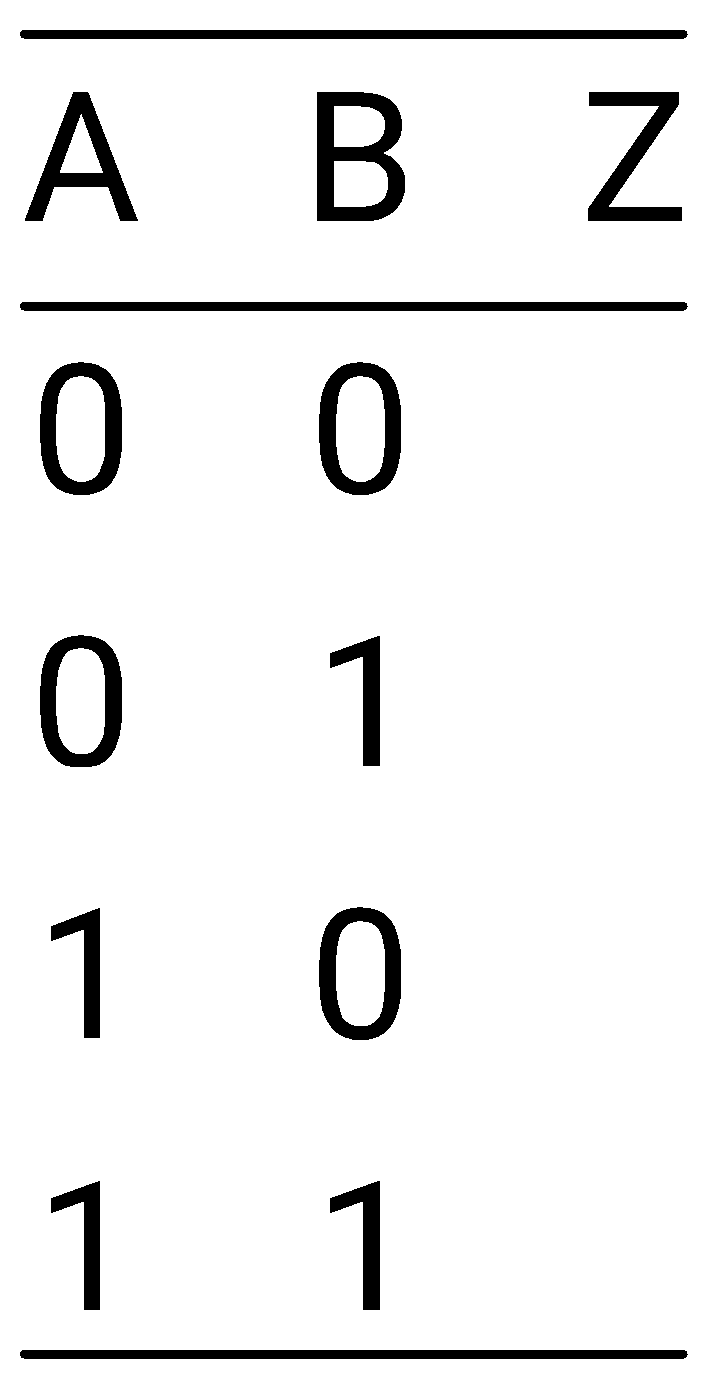

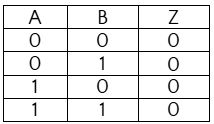

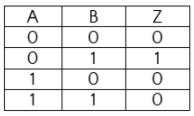

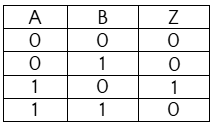

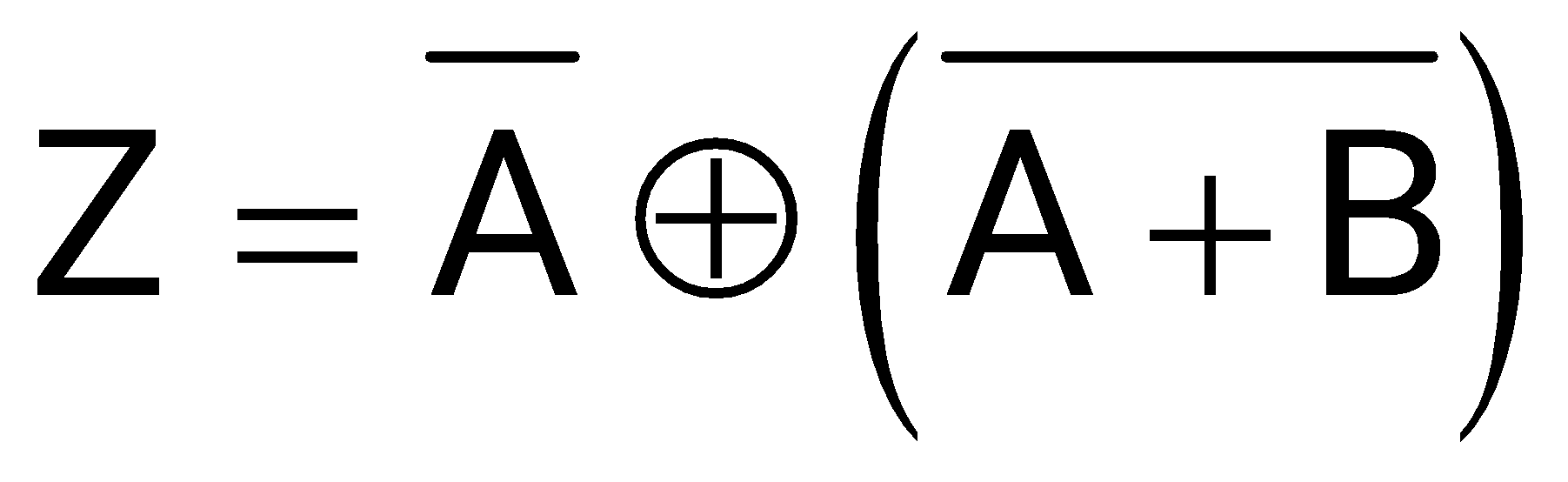

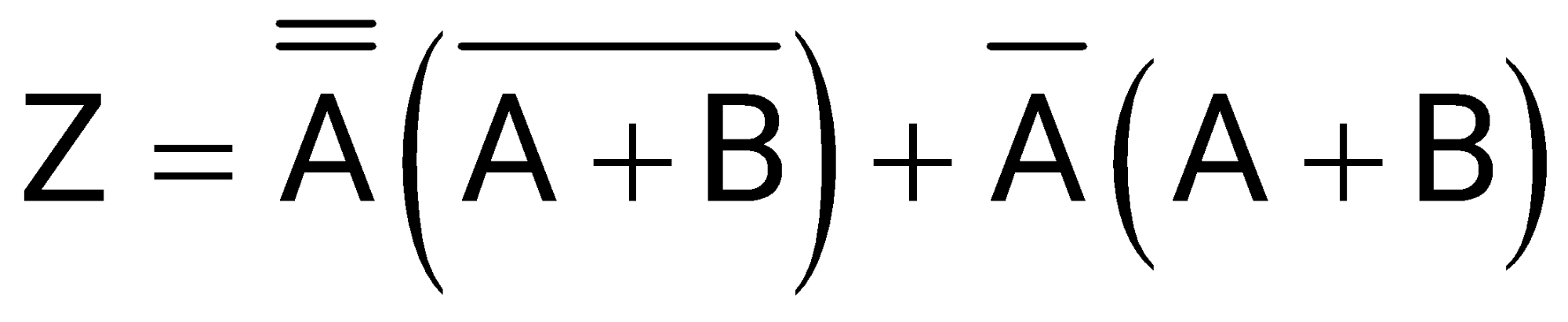

Complete the truth table for the combinational circuit shown in figure.

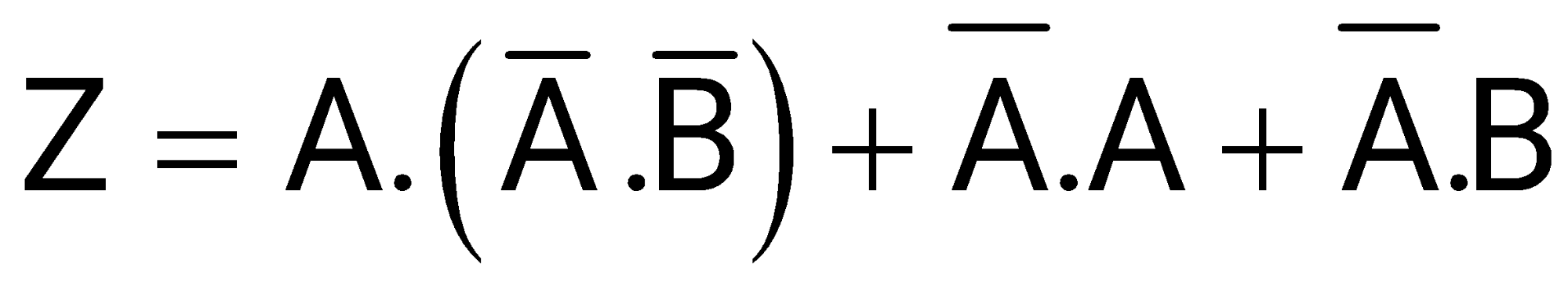

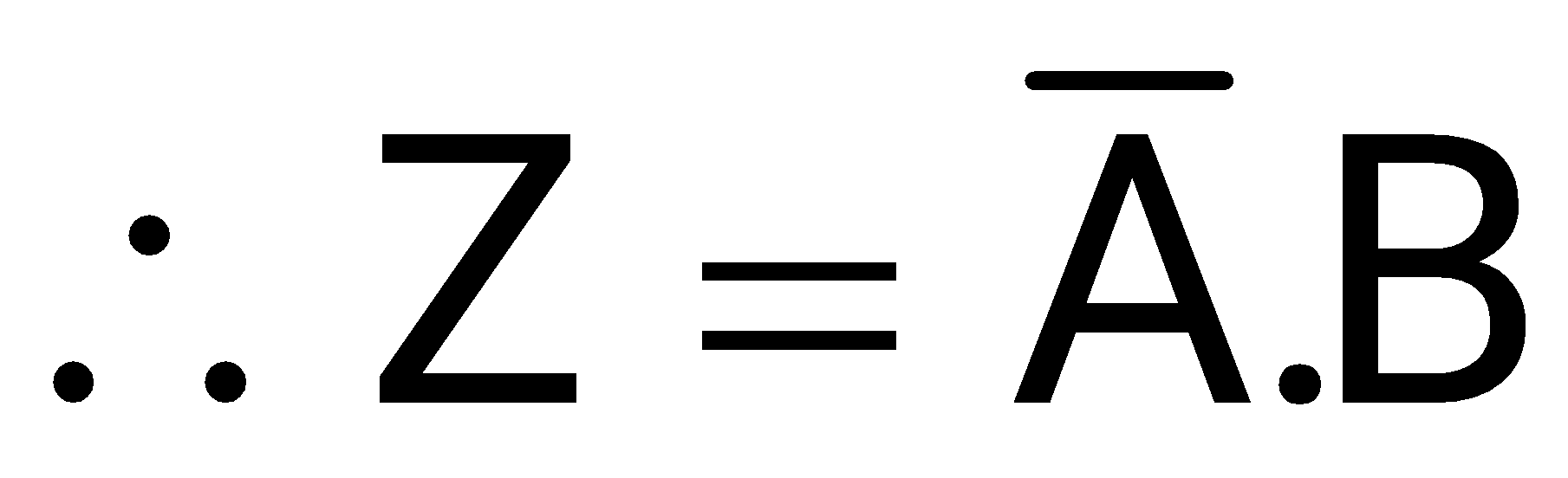

Boolean expression for Z,

Apply Demorgan’s theorem

So truth table is

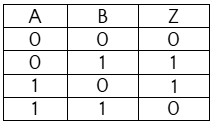

A | B | Z |

0 | 0 | 0 |

0 | 1 | 1 |

1 | 0 | 0 |

1 | 1 | 0 |