Digital Electronics

Logic Family

Practice questions from Logic Family.

9

Total0

Attempted0

Correct0

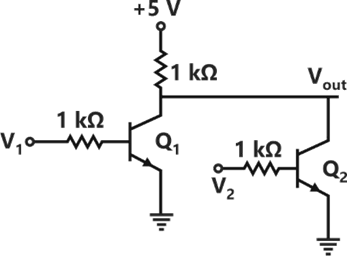

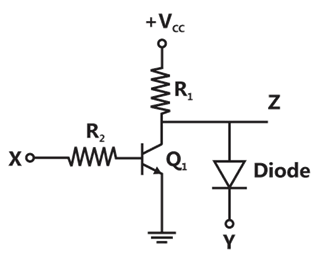

IncorrectThe logical gate implemented using the circuit shown below where, V1 and V2 are inputs (with 0 V as digital 0 and 5 V as digital 1) and VOUT is the output, is

If either or is logic 1; the transistor turns ON &

If both, the output is large 1

Hence, the logic implements a NOR gate

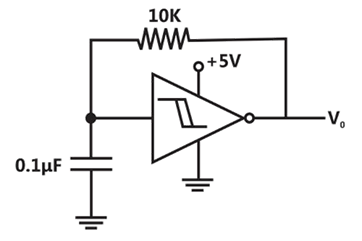

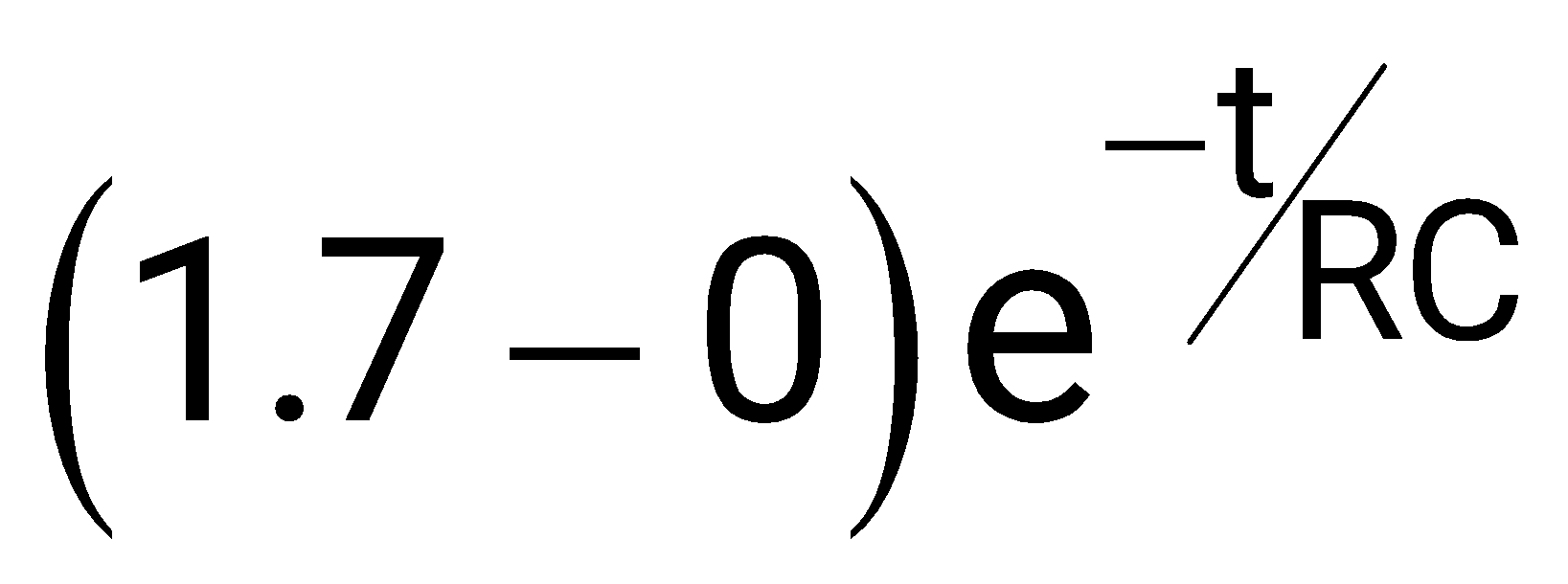

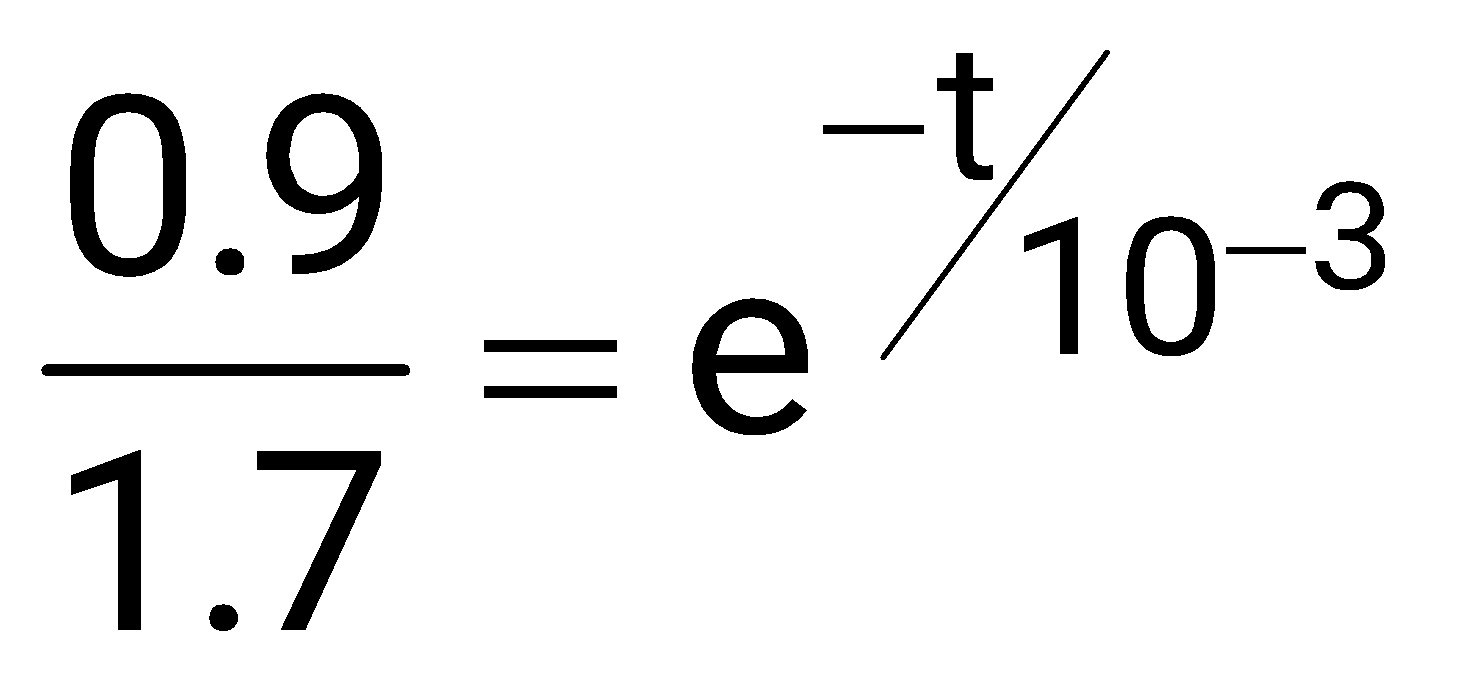

A hysteresis type TTL inverter is used to realize an oscillator in the circuit shown in the figure.

If the lower and upper trigger level voltages are 0.9V and 1.7V, the period (in ms), for which output is LOW, is ______________.

The voltage across capacitor is

When output is low,

The output triggers when input falls below = 0.9V

0.9 = 0 +

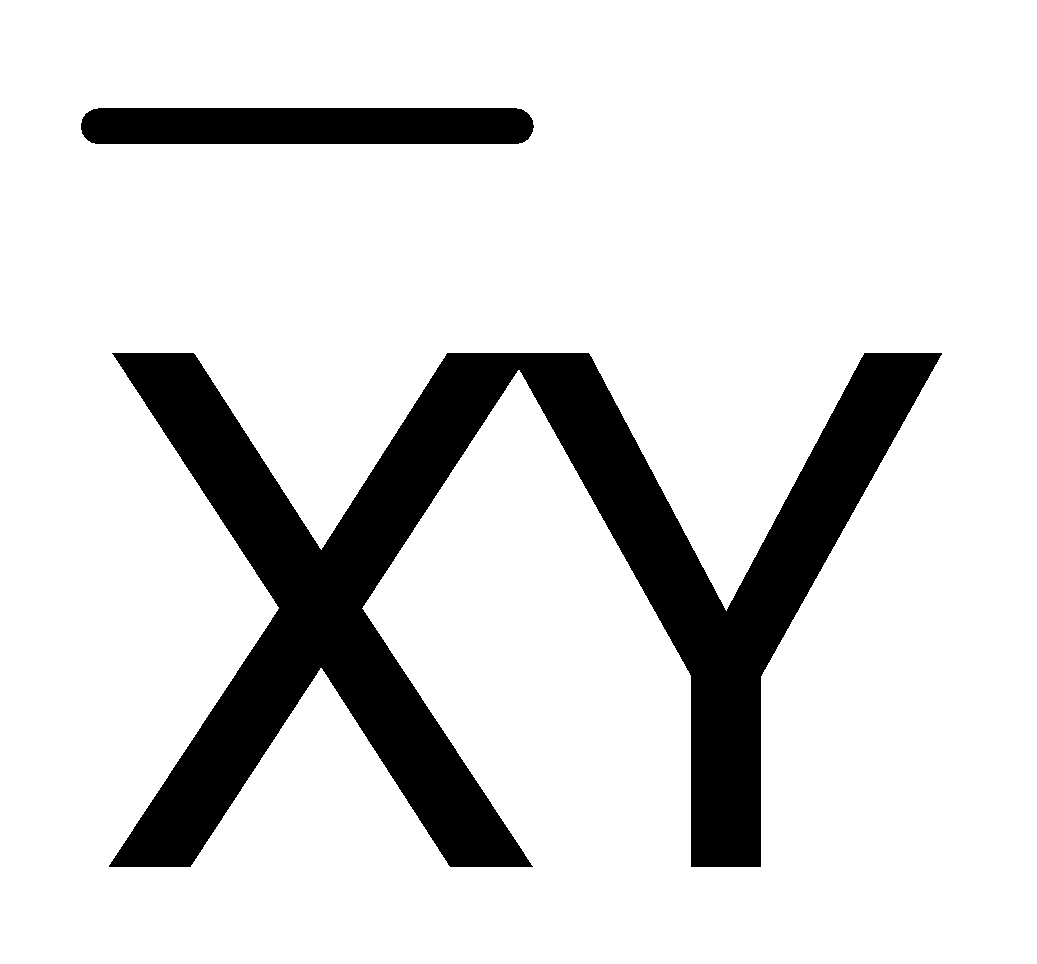

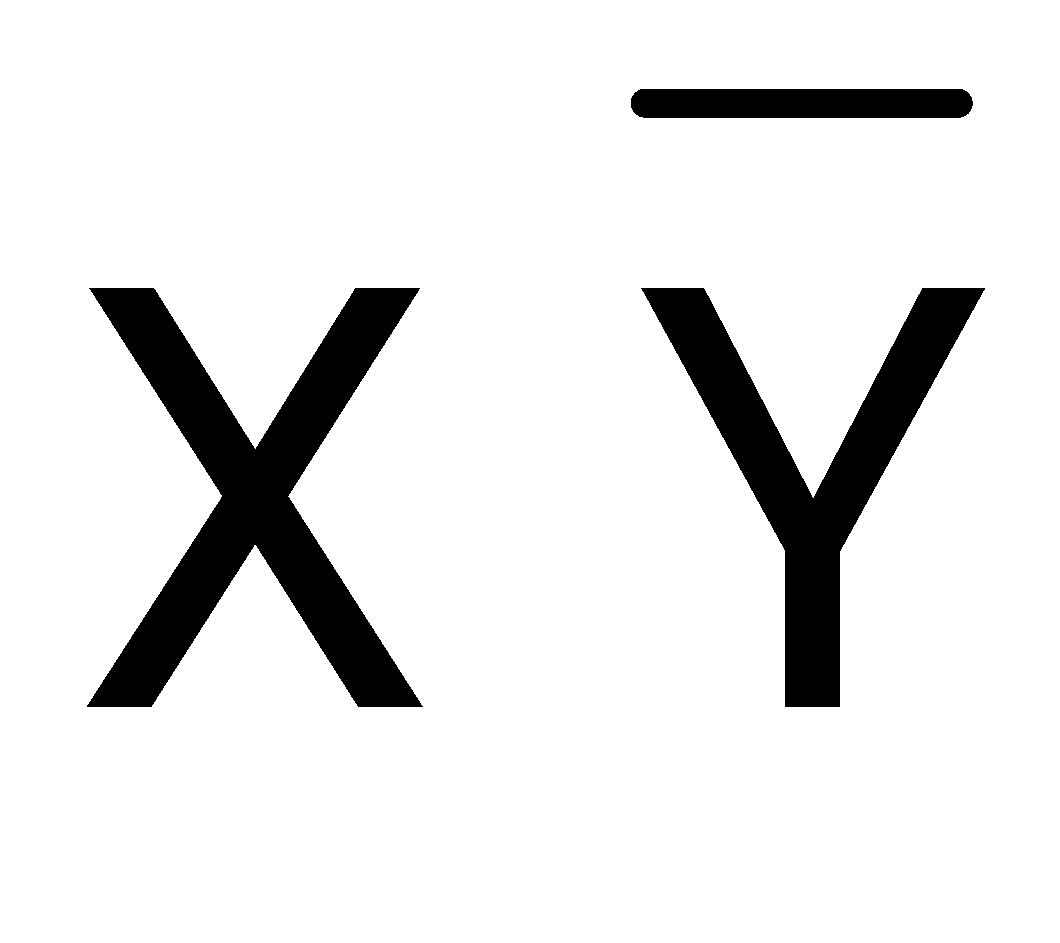

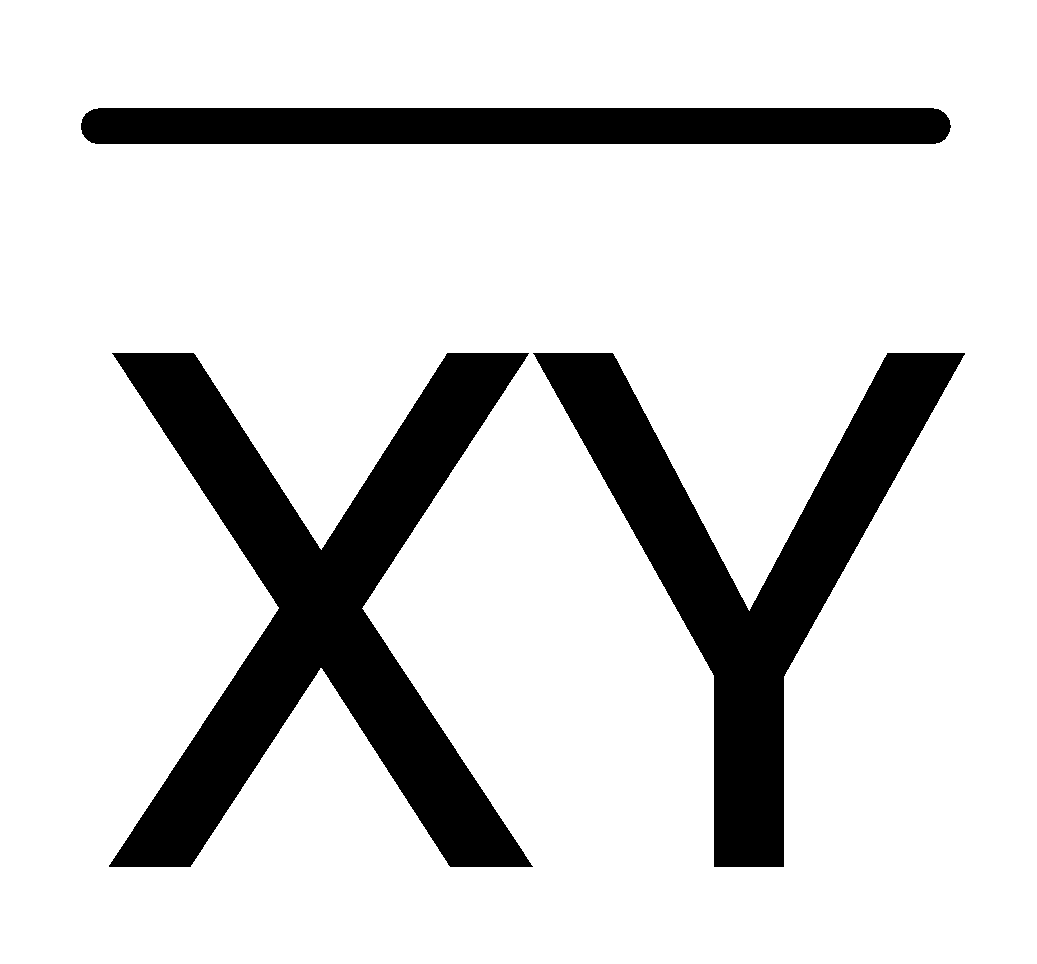

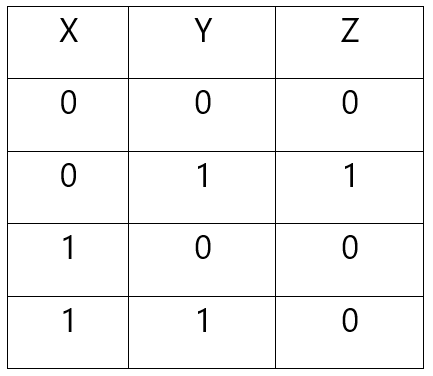

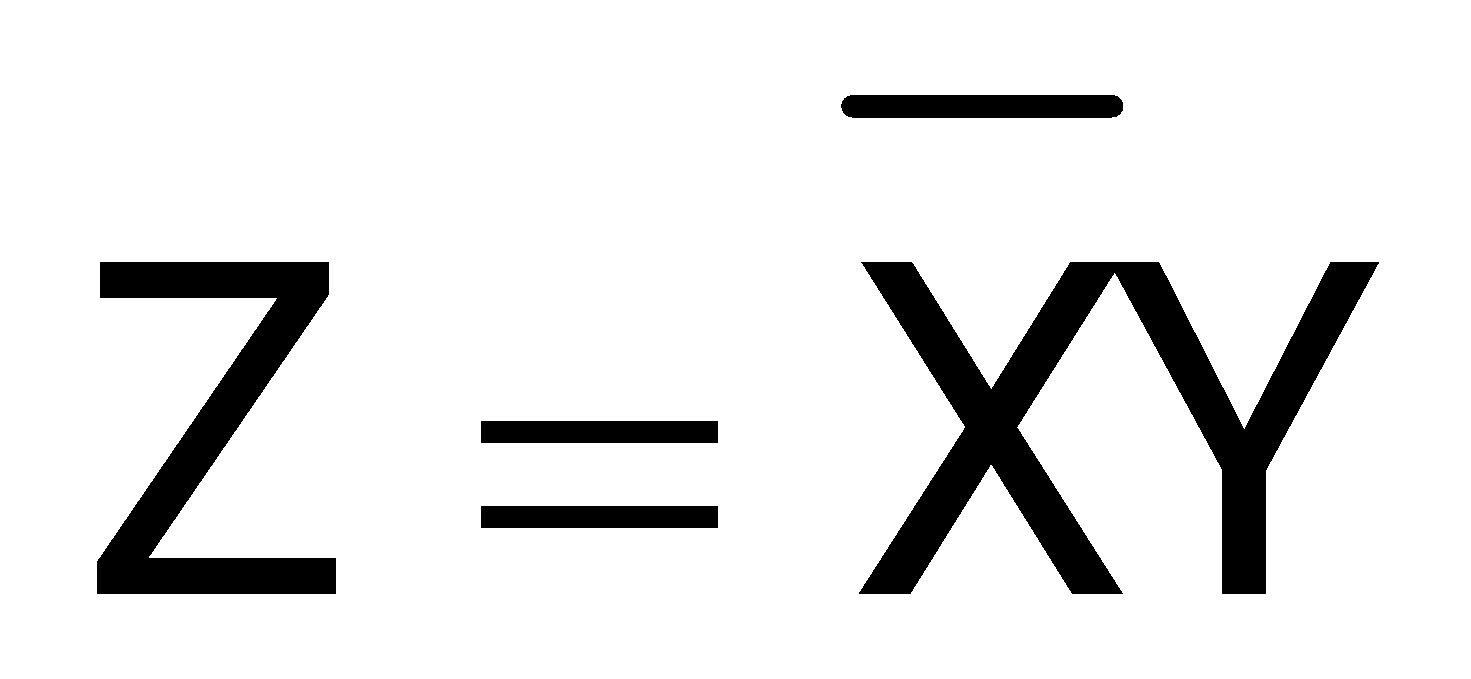

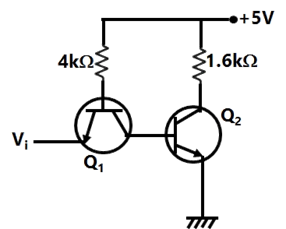

In the circuit shown below, Q1 has negligible collector-to-emitter saturation voltage and the diode drops negligible voltage across it under forward bias. If Vcc. is +5 V, X and Y are digital signals with 0 V as logic 0 and Vcc. as logic 1, then the Boolean expression for Z is

X and Y are digital signals with 0 V as logic 0 and Vcc. as logic 1

When Y=0, diode is forward biased and output Z=0

When Y=1, diode is reverse biased then for X=1, BJT turns ON and connects the output Z to ground. But for X=0, BJT is OFF and output Z is connected to Vcc.

The increasing order of speed of data access for the following devices is

(i) Cache Memory

(ii) CDROM

(iii) Dynamic RAM

(iv) Processor Registers

(v) Magnetic Tape

The increasing order of speed of data access is as follows,

Magnetic Tape<CD ROM < Dynamic RAM < Cache Memory < Processor registers.

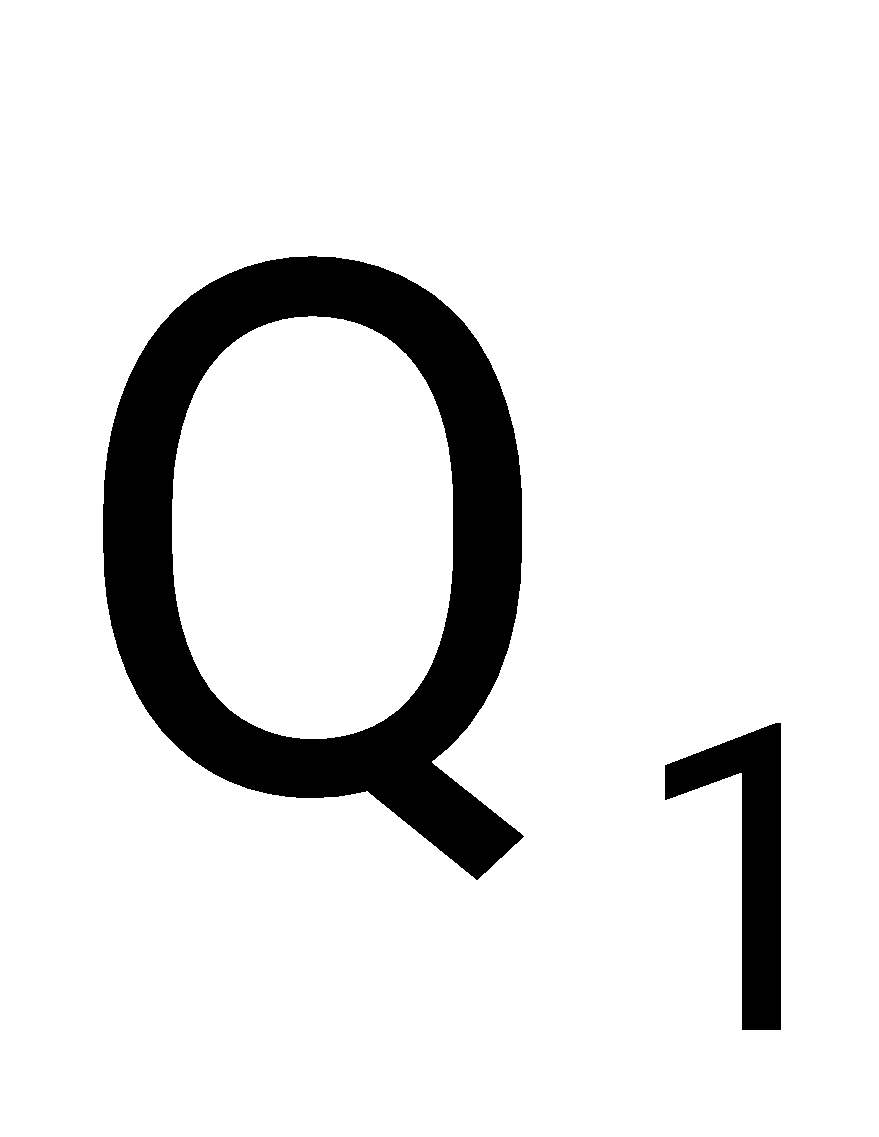

A TTL NOT gate circuit is shown in figure. Assuming VBE = 0.7V of both the transistors, if Vi = 3.0 V, then the states of the two transistors will be

In TTL Logic, if the input is high then the Transistor Q1 is in Reverse Active Mode and when input is low then the Transistor is in Forward Active Mode. In reverse active mode, the current flows from emitter to collector and turns ON the transistor Q2.

Q1 reverse ON and Q2 is ON.

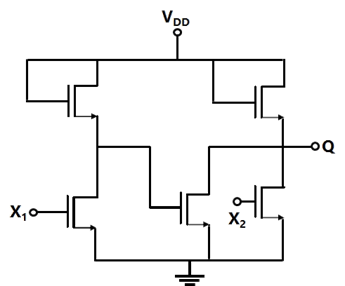

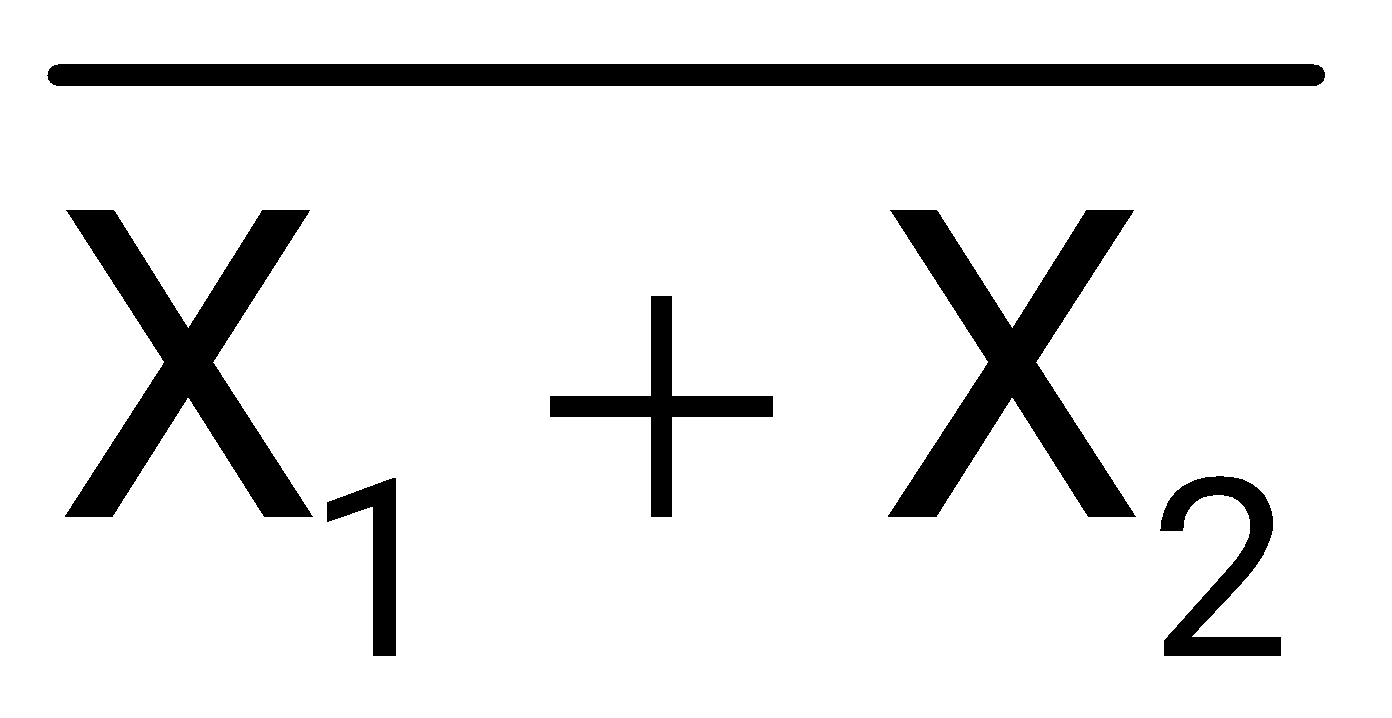

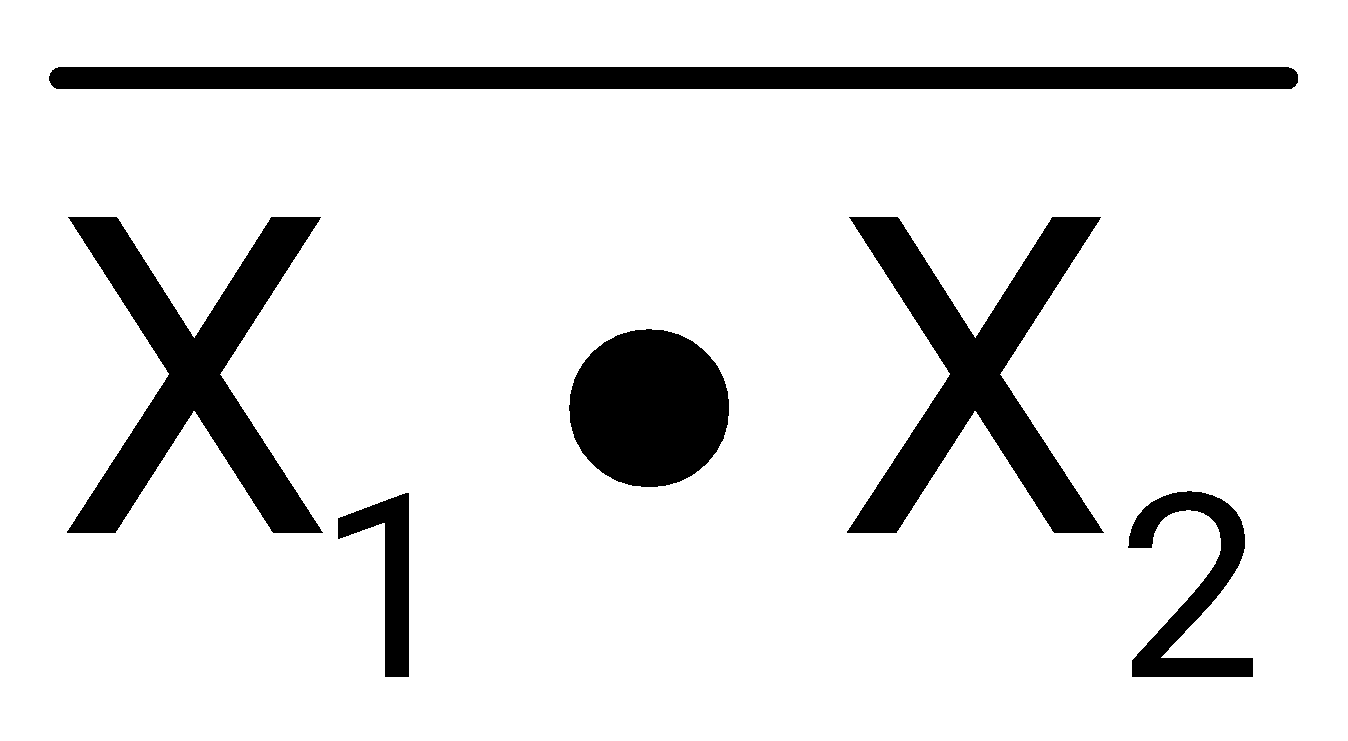

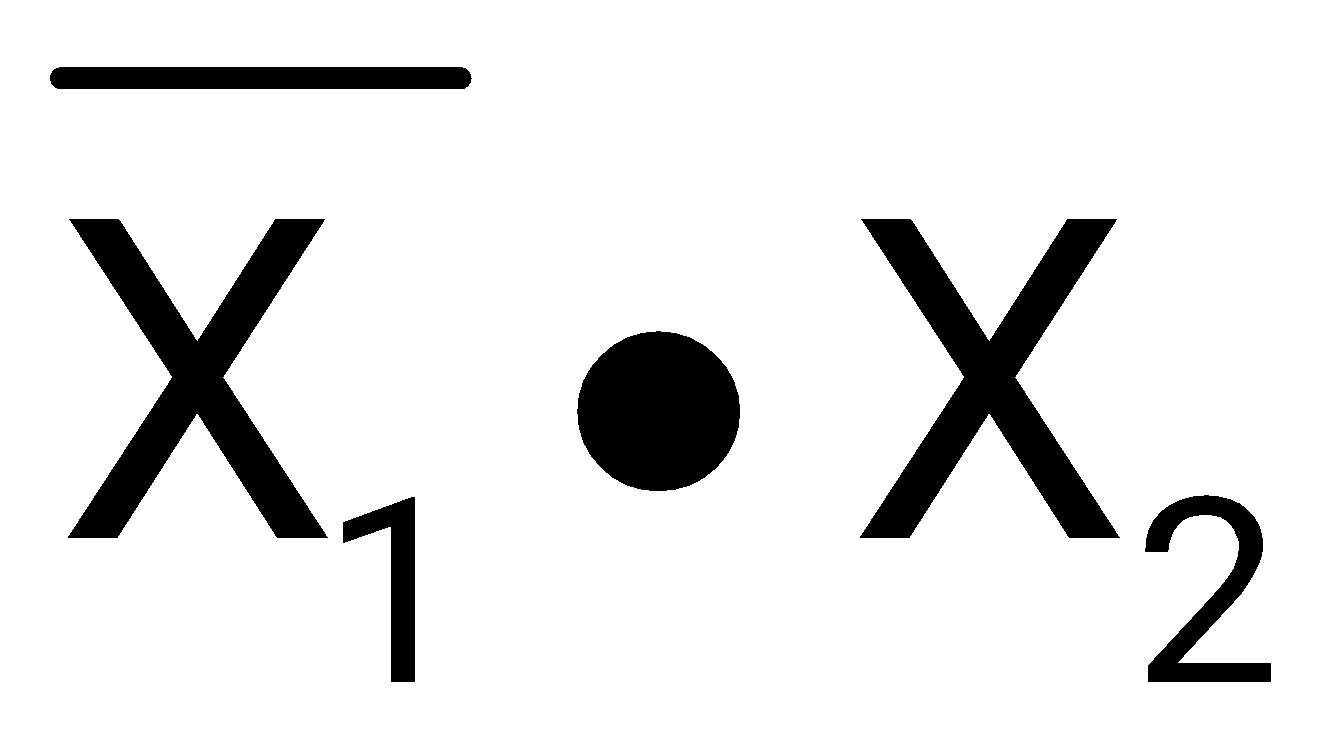

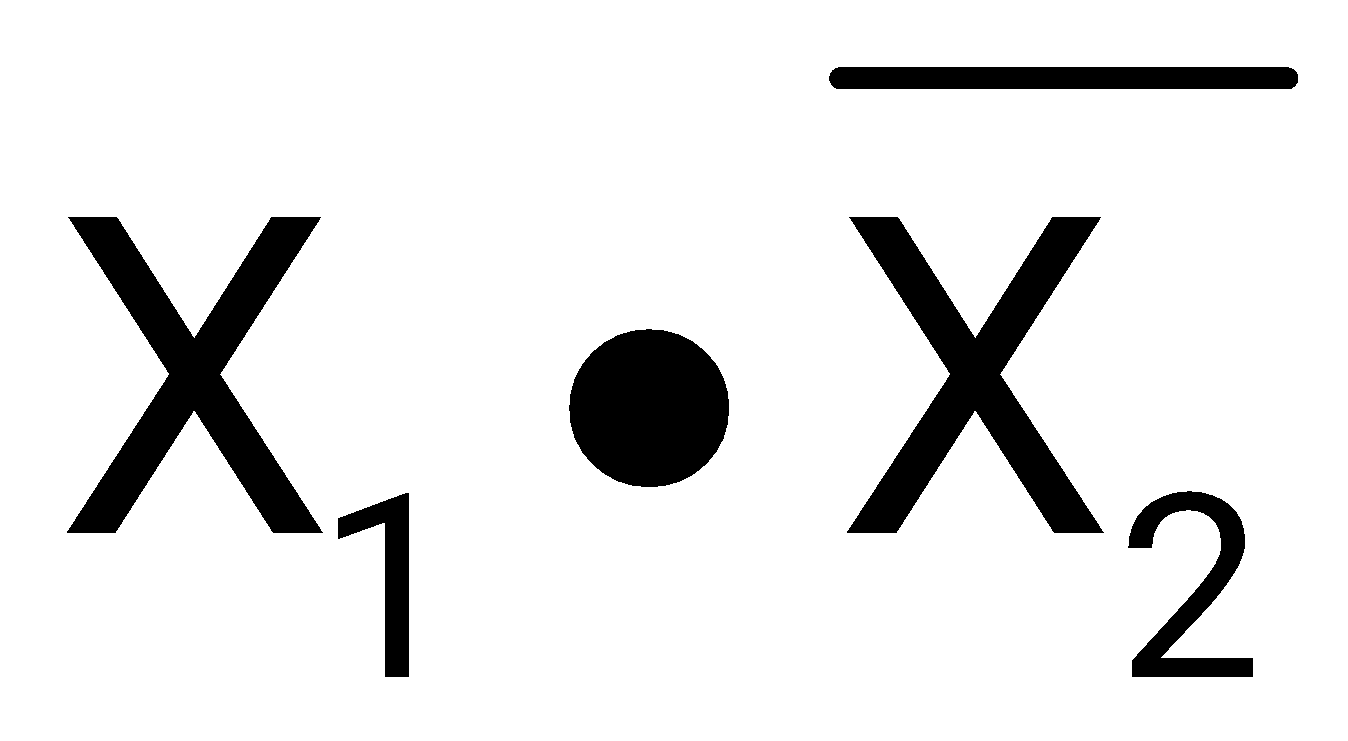

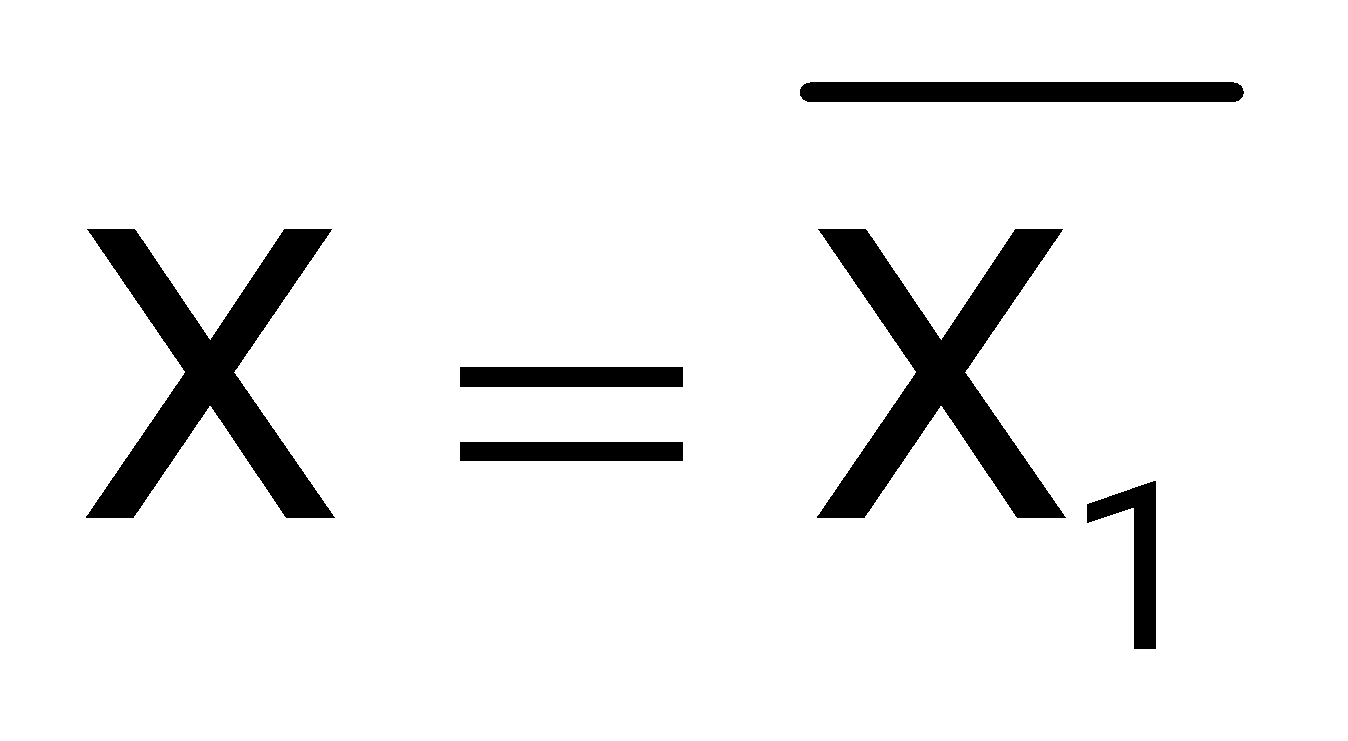

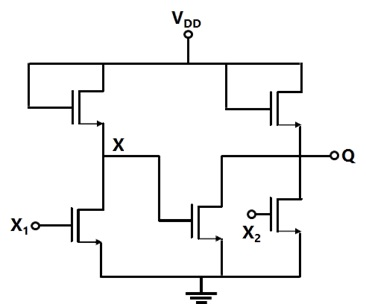

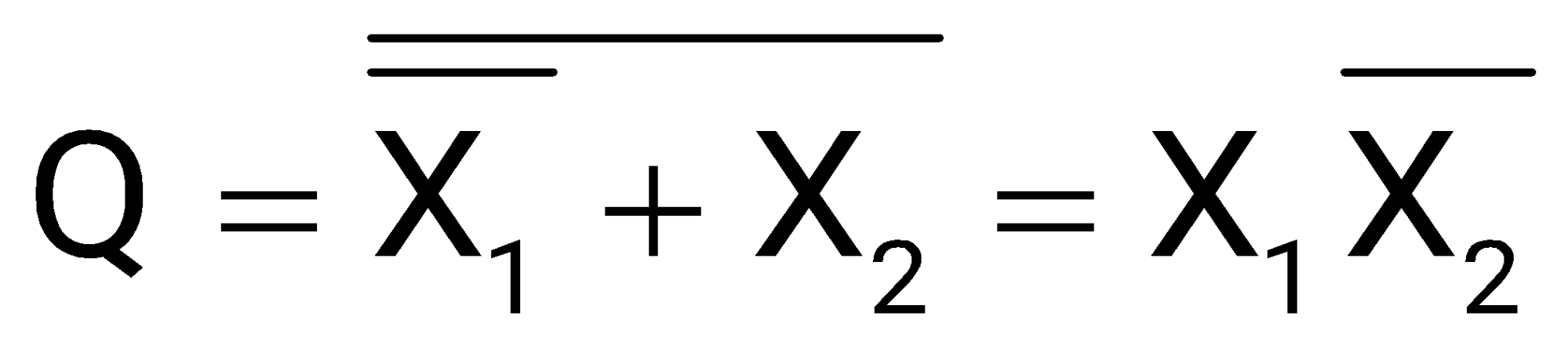

If X1 and X2 are the inputs to the circuit shown in figure, the output Q is:

This is a digital logic implemented using NMOS Transistors.

When X1 is high the output X is connected to ground

so, X = 0 and when X1 is low then the PMOS transistor

pulls the output X to 1. So, the first logic acts as Inverter.

In the second logic gate when either X or X2 is high then the output is pulled low to logic 0. So, the second logic gate is NOR gate.

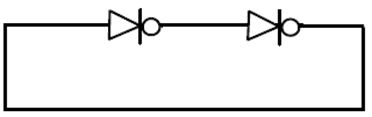

The digital circuit using two inverters shown in figure will act as

For both the states 0 and 1, system is stable

Hence it is a bi stable multivibrator

It is also known as bi stable element and it is used in semiconductor memories

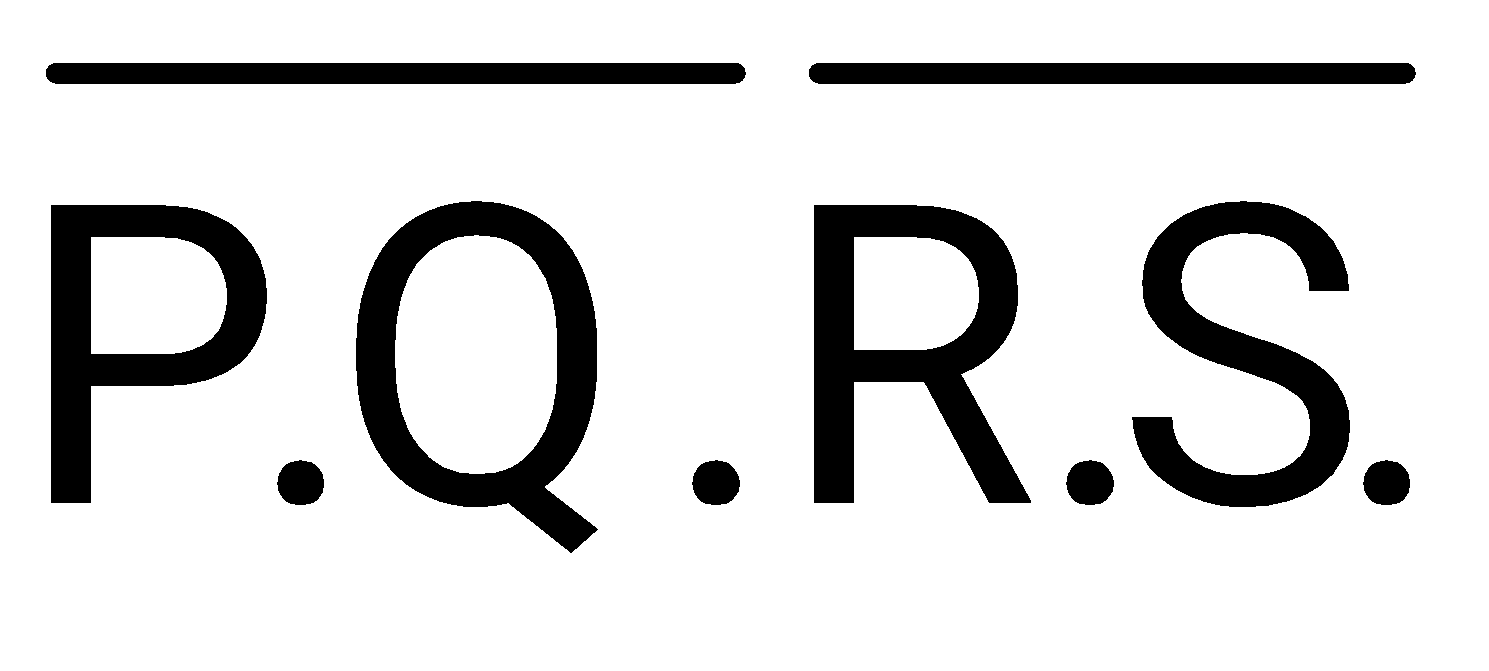

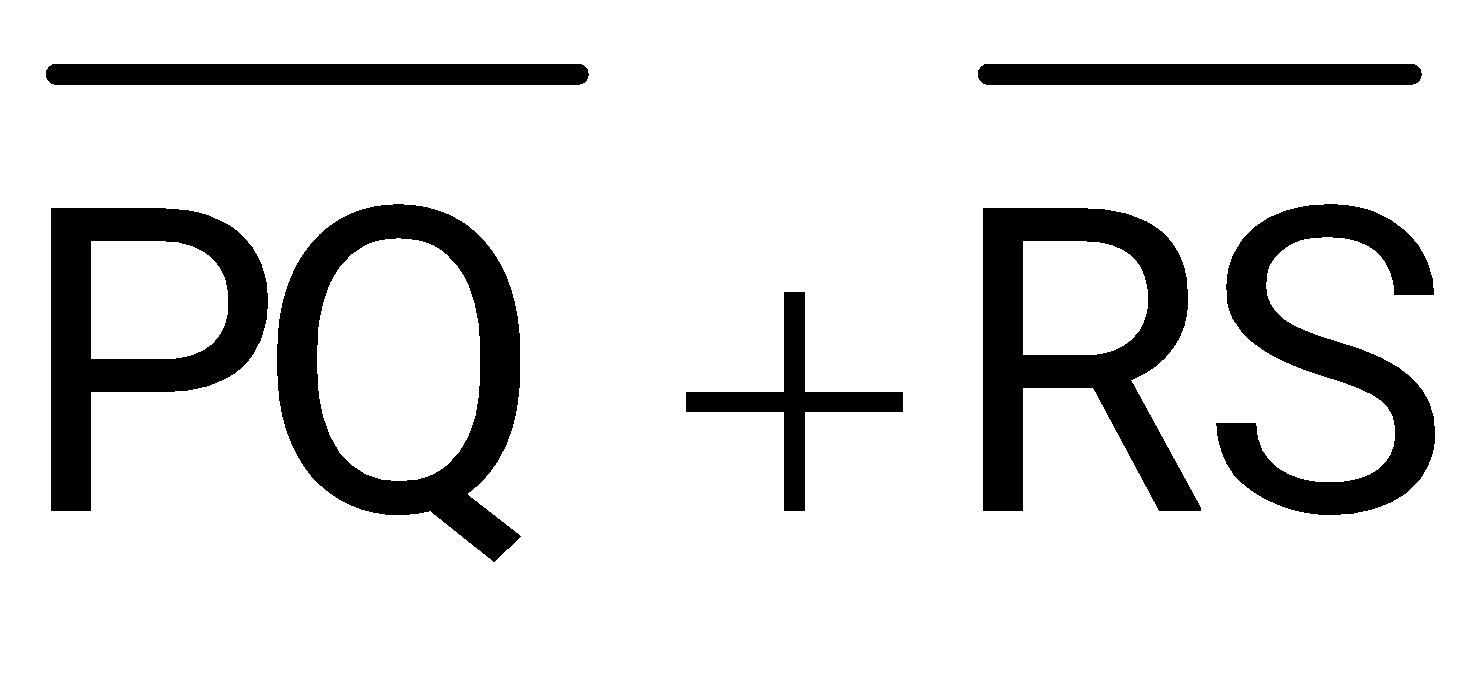

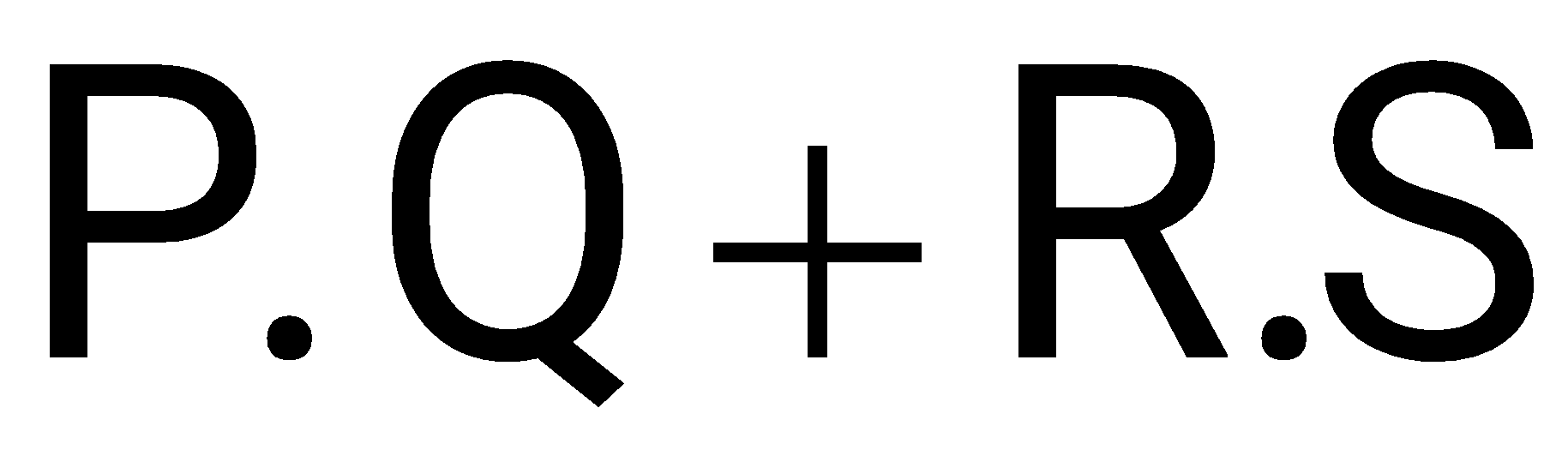

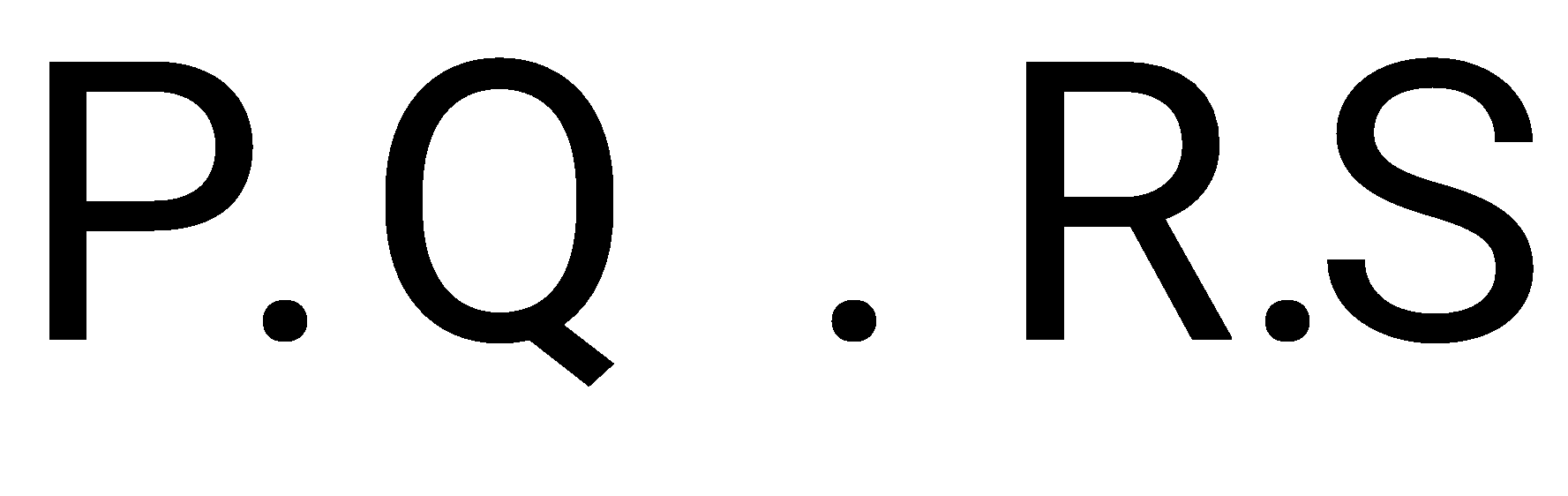

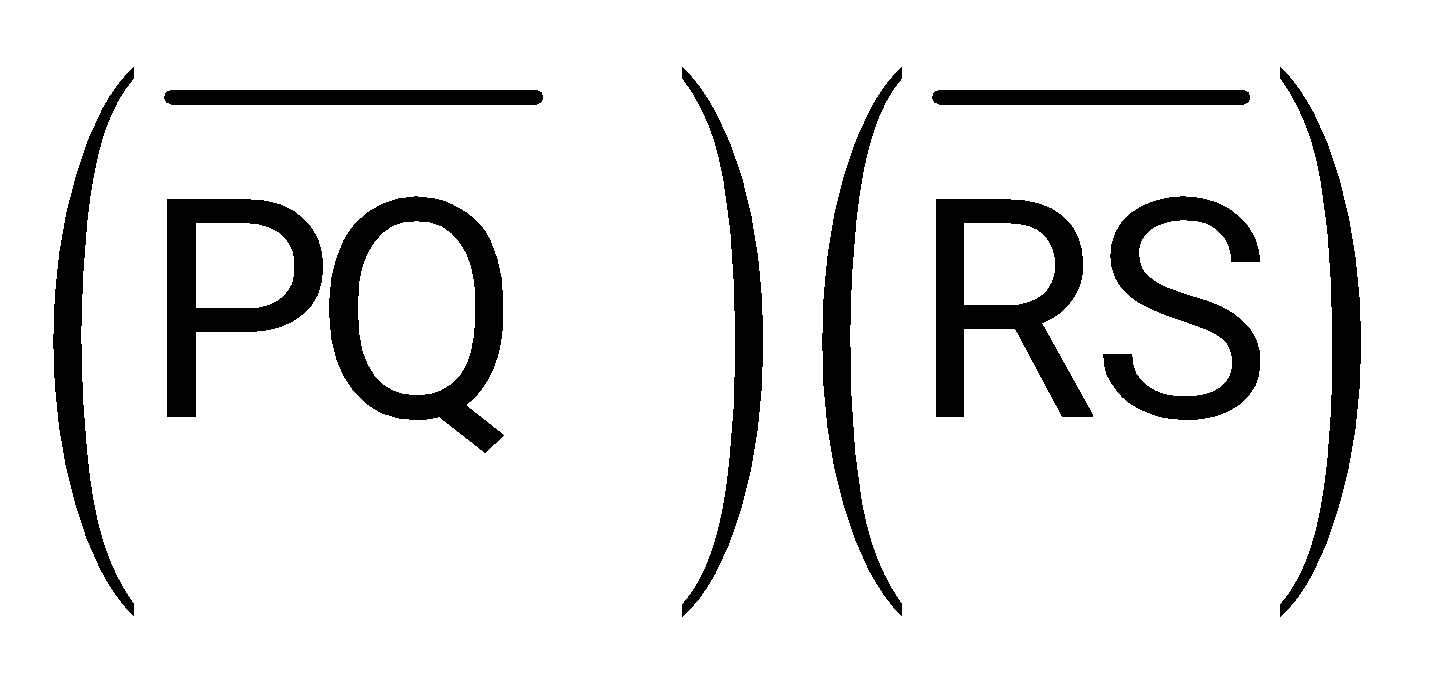

The open collector outputs of two 2-inputs NAND gates are connected to a common pull up resistor. If the input to the gates are P, Q and R, S respectively, the output is equal to

Pull up resistor works as a AND Gate.

Output =

In standard TTL gates, the totem pole output stage is primarily used to

In TTL standard logic, the totem pole configuration is primarily used to reduce the switching delay.