Digital Electronics

Microprocessor

Practice questions from Microprocessor.

30

Total0

Attempted0

Correct0

IncorrectIn a given 8-bit general purpose micro-controller there are following flags. C-Carry, A-Auxiliary Carry, O-Overflow flag, P-Parity (0 for even, 1 for odd) and are the two general purpose registers of the micro-controller. After execution of the following instructions, the decimal equivalent of the binary sequence of the flag pattern [CAOP] will be

MOV RO,

MOV R1, +0x46

ADD R0, R1

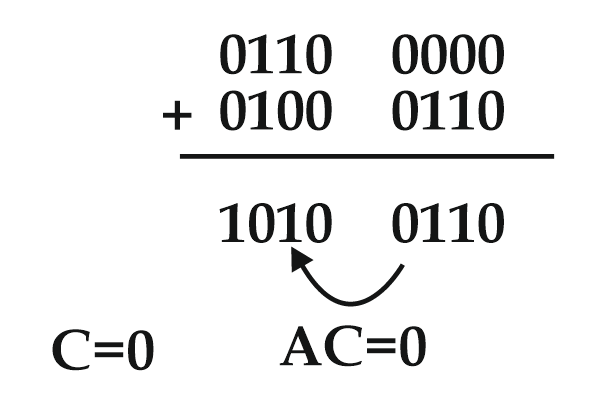

MOV R0, 0 × 60 ← (60)H is stored in R0

MOV R1, 0 × 46 ← (46)H is stored in R1

ADD R0, R1

Both values get added

Number of 1’s in result = 4 = even ∴ P =0

Overflow bit is 1 because both numbers have MSB = 0 i.e. positive numbers but result has MSB = 1 i.e. negative number.

CAOP = 0010; decimal value = 2

An 8085 microprocessor accesses two memory locations (2001H) and (2002H), that contain 8-bit numbers 98H and B1H, respectively. The following program is executed:

LXI H,2001H

MVI A, 21H

INXH

ADD M

INXH

MOV M, A

HLT

At the end of this program, the memory location 2003H contains the number in decimal (base 10) form.

LX1 H, 2001 H HL = (2001)H

MVI A, 21 H A = (21)H

INXH HL = (2002)H

ADD M A = A + M = 21 + B1 = (D2)H

INXH HL = (2003)H

MOV M, A (2003)H ← (D2)H = (210)10

HLT

A portion of the main program to call a subroutine SUB in an 8085 environment is given below.

:

:

LXI D, DISP

LP. CALL SUB

:

:

It is desired that control be returned to LP + DISP + 3 when the RET instruction is executed in thee subroutine. The set of instructions that precede the RET instruction in the subroutine are

When CALL instruction is executed the address of LP is pushed to the top of stack and then the PC is fed with new address. To return the execution to LP + DISP + 3.

The address of LP must be extracted in HL register pair by means of POP instruction and then DISP is added to it by the use of DAD instruction so that HL = LP +DISP

Then HL register pair is incremented thrice to obtain HL = LP +DISP + 3

Then this is pushed back to the top of stack to be fed to Program Counter upon execution of RET instruction.

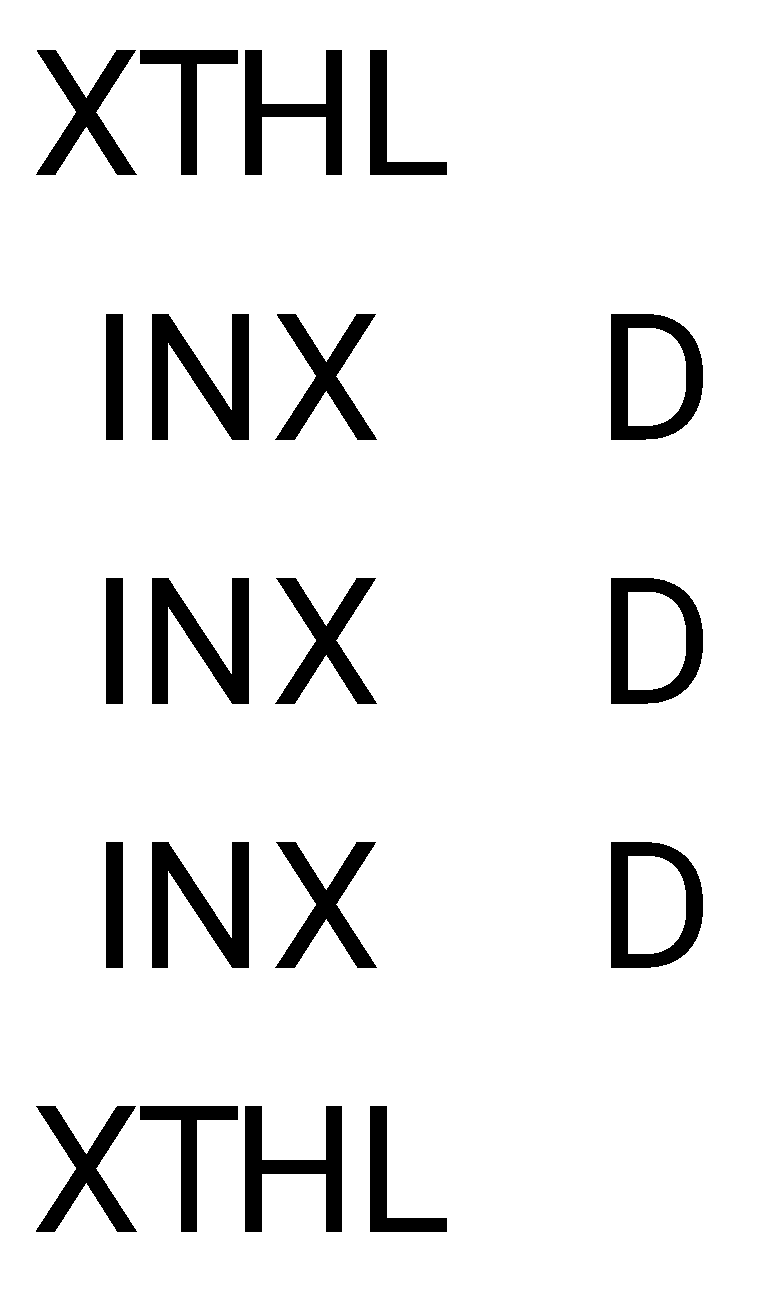

When a “CALL” Addr” instruction is executed. The CPU carries out the following sequential operations internally:

Note:

(R) means content of register R

((R)) means content of memory location pointed to by R

PC means program counter

SP means stack pointer

Whenever a CALL instruction is executed then the address of next instruction i.e. the contents of Program Counter are pushed to the Stack.

Then the Stack Pointer is incremented to point to the next memory location but in actual Stack Pointer is decremented.

Then the new address is stored in Program Counter to shift the program execution to anew location.

In an 8085 microprocessor, the contents of the Accumulator, after the following instructions are executed will become

XRA A

MVI B F0H

SUB B

XRA A: clear the contents of Accumulator. A = 00H

MVI B F0H; B = F0H

SUB B; A =A – B

A = 0000 0000

B = 1111 0000

A –B = 0001 0000 = (10)H and CY will be 1 as carry acts as borrow in case of subtraction.

An input device is interfaced with Intel 8085A microprocessor as memory mapped I/O. The address of the device is 2500H. In order to input data from the device to accumulator, the sequence of instructions will be

Memory Mapped I/O are accessed as memory location and to access a memory location, its address must be stored in HL register pair so, the first instruction should be

LXI H, 2500H

Now, the data from this address can be directly moved to accumulator by using the instruction,

MOV A, M

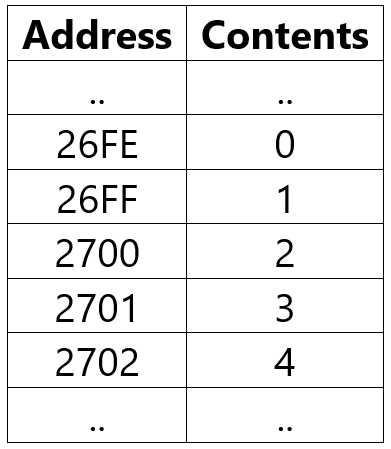

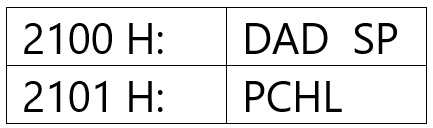

The contents (in Hexadecimal) or some of the memory locations in an 8085A based system are given below:

The contents of stack pointer (SP), program counter (PC) and (HL) are 2700H, 2100H and 0000H respectively. When the following sequence of instructions are executed,

The contents of (SP) and (PC) at the end of execution will be

DAD SP : Add the contents of SP register to the HL register pair and store the result in HL register pair.

HL = HL + SP = 2700H

PCHL: Load the Program Counter with the contents of HL register pair.

PC = HL = 2700H

Hence, after execution of these instructions the contents of both SP and PC is 2700H.

Which one of the following statements regarding the INT (interrupt) and the BRQ (bus request) pins in a CPU is true?

The INT pin is sampled after every machine cycle that is its value is sampled even in between execution of an instruction.

The BRQ or Bus Request Pin is sampled after every instruction cycle i.e. on completion of execution of an instruction.

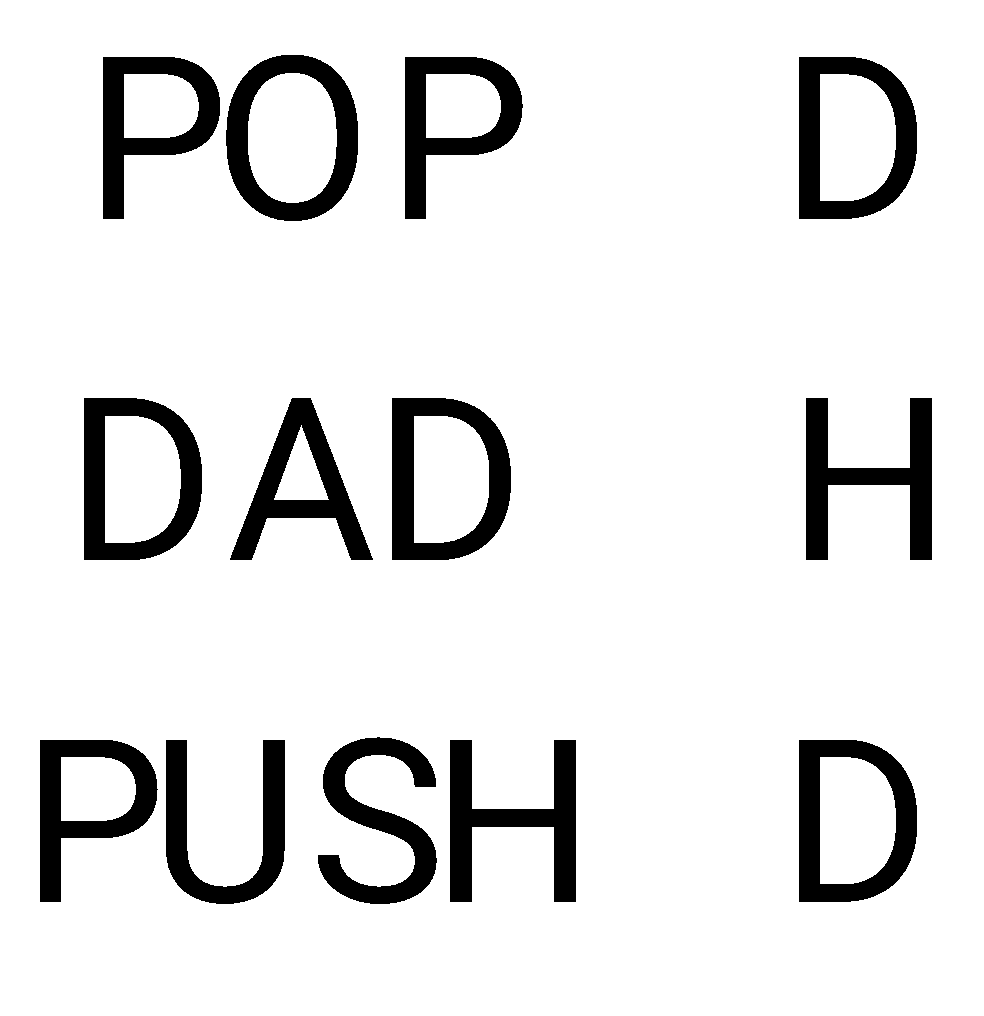

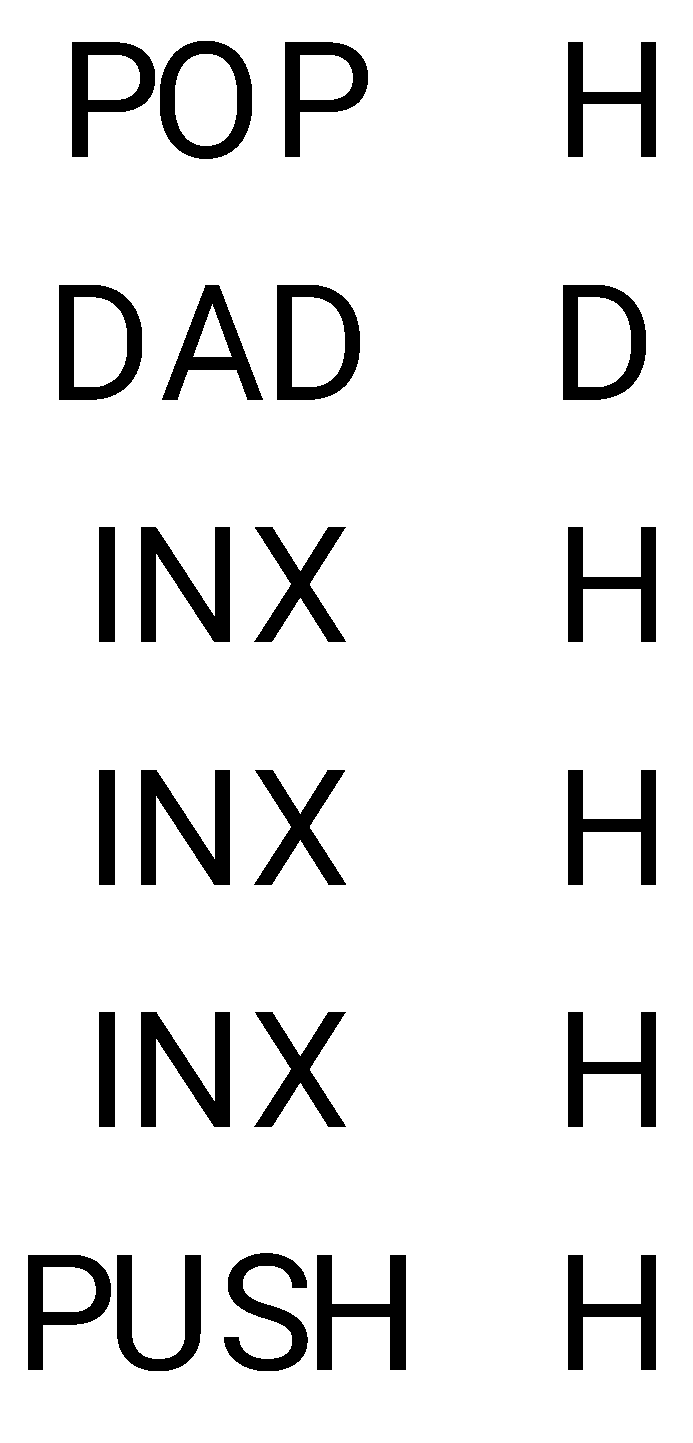

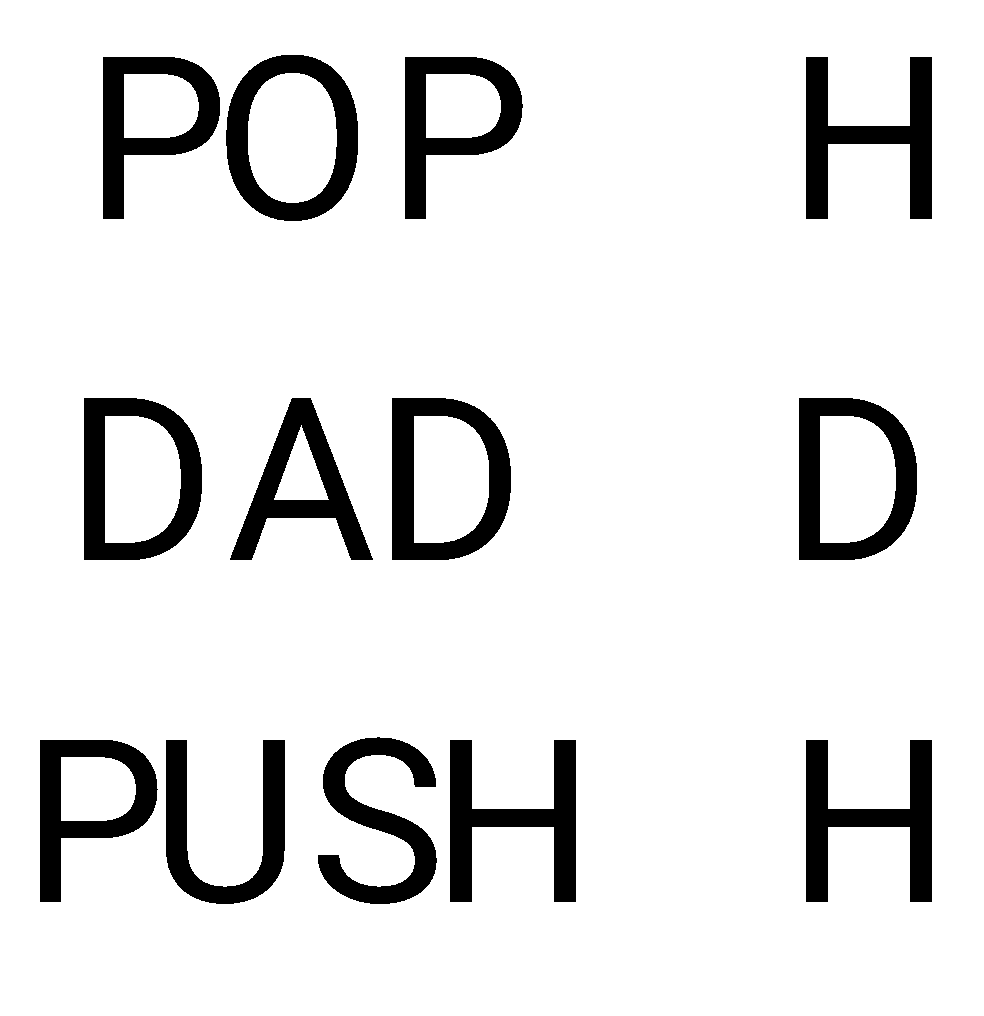

The associated figure shows the two types of rotate right instructions R1, R2 available in a microprocessor where Reg is a 8-bit register and C is the carry bit. The rotate left instructions L1 and L2 are similar except that C now links the most significant bit of Reg instead of the least significant one.

Suppose Reg contains the 2's complement number 11010110. If this number is divided by 2 the answer should be

The given number is (11010110)2 = (214)10

Since, it is in 2’s complement form, the actual number is 28 - 214 = (42)10

When this number is divided by 2 the result is (21)10

This number can be expressed in 2’s complement form as, 28 - 21 = (235)10

(235)10 = (11101011)2

The associated figure shows the two types of rotate right instructions R1, R2 available in a microprocessor where Reg is a 8-bit register and C is the carry bit. The rotate left instructions L1 and L2 are similar except that C now links the most significant bit of Reg instead of the least significant one.

Such a division can be correctly performed by the following set of operations

The objective of instruction sequence is to convert (11010110)2 to (11101011)2 by the use of Shift Instructions.

L2 : 11010110 -> 10101101, CY = 1

R2: 10101101 -> 11010110, CY = 1

R1: 11010110 -> 11101011, CY = 0

Note: Here, we must verify the options in order to know the correct sequence.

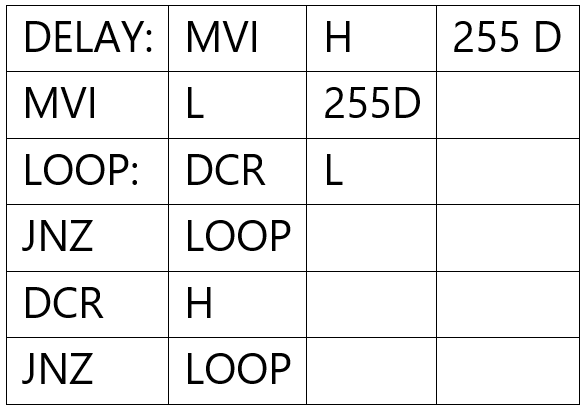

A software delay subroutine is written as given below:

How many times DCR L instruction will be executed?

In the first iteration, the value of register L is decremented from 25510 to 010. So, DCR L is executed 255 times.

In rest of 254 iterations the value of register L is decremented from 00H to 00H i.e. the value is decremented 256 times.

Hence, DCR L instruction is executed = 255 + 254 x 256 = 65,279 times

In an 8085 microprocessor based system, it is desired to increment the contents of memory location whose address is available in (D, E) register pair and store the result in same location. The sequence of instructions is

First XCHG instruction must be executed to transfer the memory address from DE register pair to HL register pair.

Then we can use INR M instruction to increase the content of memory location pointed to by HL register pair.

The 8085 assembly language instruction that stores the contents of H and L registers into the memory locations 2050H and 2051H, respectively, is:

SPHL Instruction copies the content of HL register pair into the Stack Pointer register.

STAX copies the content of accumulator into the memory location whose address is specified by the operand register pair.

SHLD is used to copy the contents of HL register pair in the memory location specified.

SHLD 2050H copies contents of H in the memory location 2050H and L into 2051H.

If the following program is executed in a microprocessor, the number of instruction cycles it will take from START TO HALT is

START MVI A, 14 H : Move 14 H to register A

SHIFT RLC : Rotate left without carry

JNZ SHIFT : Jump on non-zero to

SHIFT

HALT

Both MVI and RLC instruction do not affect the zero flag so it will remain as it is. Hence, we can safely assume that all instructions will be executed once.

Since, there are a total of 4 instruction so it requires 4 instruction cycles to operate.

When a program is being executed in an 8085 microprocessor, its Program Counter contains

Program Counter contains the address of next instruction to be executed.

A memory system has a total of 8 memory chips, each with 12 address lines and 4 data lines. The total size of the memory system is

Since, there are 4 data lines in each memory chip, it means that each memory register is 4 bits wide.

Number of Address Lines = 12

Total number of memory location in each chip =

Number of bits that can be stored =

Total bits in 8 memory chips =

8 bits = 1 byte

Total Size =

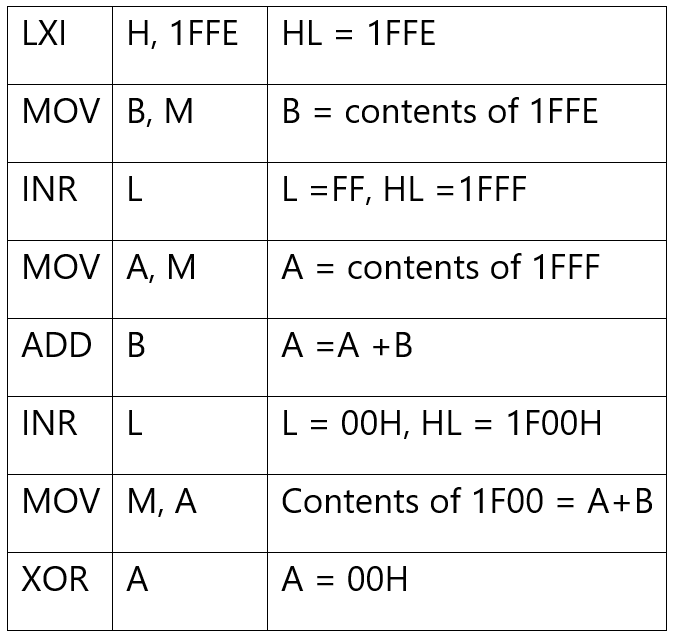

The following program is written for an 8085 microprocessor to add two bytes located at memory addresses 1FFE and 1FFF

LXI H, 1FFE

MOV B, M

INR L

MOV A, M

ADD B

INR L

MOV M, A

XOR A

On completion of the execution of the program, the result of addition is

So, the result is stored at 1F00H.

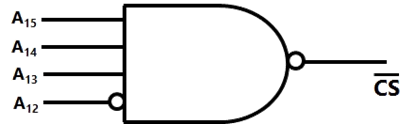

The logic circuit used to generate the active low chip selects (CS) by an 8085 microprocessor to address a peripheral is shown in Figure. The peripheral will respond to addresses in the range.

Since, the CS signals is an active low signal so the output of NAND Gate must be 0 to assert the Chip Select signal. Hence, all inputs must be asserted to make the output zero.

Since, A12 is associated with an inverter, it must be LOW to be asserted.

A15 = 1, A14 = 1, A13 = 1, A12 = 0.

Minimum Address = 1110 0000 0000 0000 (E000 H)

Maximum Address = 1110 1111 1111 1111 (EFFF H)

An intel 8085 processor is executing the program given below.

MVI A, 10H

MVI B, 10H

BACK: NOP

ADD B

RLC

JNC BACK

HLT

The number of times that the operation NOP will be executed is equal to

The instruction NOP will be executed as many number of times as the loop is executed. Upon execution once,

A = A + B = 20H (0010 0000)

RLC; A = 40H (0100 0000), CY = 0

Second execution,

A = A + B = 50H (0101 0000)

RLC; A = A0H (1010 0000), CY = 0

Third execution,

A = A + B = B0H (1011 0000)

RLC; A = 61H (0110 0001), CY = 1

Since, the CY flag is now set the loop terminates and hence NOP instruction is executed thrice.

Which one of the following is not a vectored interrupt?

TRAP, RST 7.5, RST 6.5 and RST 5.5 are vectored interrupts whereas INTR is a non-vectored interrupt.

In a microprocessor, the address of the next instruction to be executed, is stored in

Program Counter stores the address of next instruction to be executed.

The computer program which converts statements written in high level language to object code is known as

Assembler converts program written in High Level Language to Machine code with one line at a time.

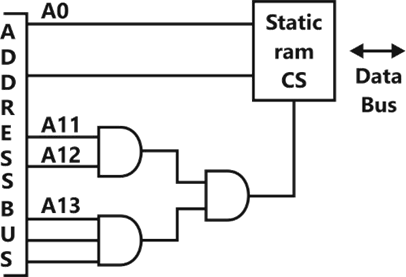

The range of address for which the memory chip shown in figure, will be selected is_________ to_________

For CS to be selected all the address lines connected to AND Gate should be asserted so

(A11 – 1, A12 – 1, A13 – 1, A14 – 1, A15 – 1).

The other address lines can vary from all 0’s and all 1’s. Hence the address range can vary between

Minimum Address: 1111 1000 0000 0000 = (F800 H)

Maximum Address: 1111 1111 1111 1111 = (FFFF H)

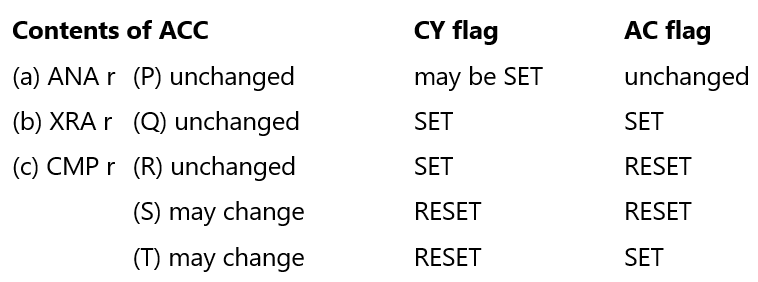

In a 8085 microprocessor, the following instructions may result in change of accumulator contents and change in status flags. Choose the correct match for each instruction.

ANA r: ANDs the content of register with accumulator which modifies the content of accumulator and resets the carry flag and sets the AC flag.

XRA r: Ex-ORs the contents of a register with the accumulator. So, the contents of accumulator are modified. It resets both CY and AC flag.

CMP r: Compares the contents of register r with accumulator but contents of both registers are preserved. Contents of CY flag will change depending on the result. AC = unchanged.

In an 8085 microprocessor, after the execution of XRA A instruction

Ex-OR of two identical values results in zero output. So, when contents of Accumulator are EX-ORed with itself then Accumulator is reset and Zero Flag is set to reflect the result.

A subroutine PROG1 written in the 8085 assembly language is given below. At entry to this program, the values of different registers in HEX are. A=05; BC=0000; DE=5472; HL=4528, All the flags are set to 1. Determine the register contents and condition of the zero and carry flags after the execution of the program. (i.e., after executing RET statement). What does the program accomplish?

PROG1 MOV A, E

ADD L

DAA

MOV L, A

MOV A, D

ADC H

DAA

MOV H, A

MVI A, 00H

RAL

RET

PROG1 MOV A, E; A = 72H, flags unchanged

ADD L; A = A + L = 9AH (1001 1010); Z = 0, CY = 0

DAA;

Since, the lower nibble of accumulator is greater than 09H then 06H is added to lower nibble which makes the result A0H. Now the higher order nibble becomes greater than 09H so 06H is added to higher order nibble. Hence, A = 00H. So Carry Flag is set and zero flag is also set.

Contents of Registers,

HL = 0000H

BC = 0000H

DE = 5472H

A = 01H

CY = 0 and Z =1

The contents of the accumulator in an 8085 microprocessor is altered after the execution of the instruction.

CMP C: Compares the content of register C with accumulator and only flags are modified but contents of accumulator are unchanged.

CPI 3A: Compares the content of Accumulator with the data byte “3A”. The contents of accumulator remains unchanged.

ANI 5C: It is bit by bit AND operation of the data byte “5C” with the accumulator and is used for masking certain bits so it changes the contents of accumulator.

ORA A: It is a bit by bit OR operation of Accumulator with itself so the contents of accumulator are unchanged.

The stack pointer of a microprocessor is at A001 At the end of execution of following instructions, the value of stack pointer is _____________

PUSH PSW

X THL

PUSH D

JMP FC70 H

PUSH Instruction decrements the content of Stack Pointer by 2.

So, value of Stack Pointer after execution of each instruction is given below,

PUSH PSW SP = 9FFF

XTHL SP = 9FFF

PUSH D SP = 9FFD

JMP FC70 SP = 9FFD

XTHL: exchanges top of stack with HL register pair but Stack Pointer remains same.

JMP shifts the program execution to a new address but Stack Pointer remains same.

Three devices A, B and C have to be connected to a 8085 microprocessor. Device A has highest priority and device C has the lowest priority. In this context which of the following is correct assignment of interrupt inputs?

The TRAP interrupt has highest priority followed by RST 7.5, 6.5, 5.5. Since, device A has highest priority so it must be connected to RST 7.5, B must be connected to RST 6.5 and C must be connected to RST 5.5.

If the HLT instruction of a 8085 microprocessor is executed,

The microprocessor will enter the HALT state and HALT the execution of program and releases the buses i.e. they enter tri-state logic.