Digital Electronics

Sequential Circuits

Practice questions from Sequential Circuits.

35

Total0

Attempted0

Correct0

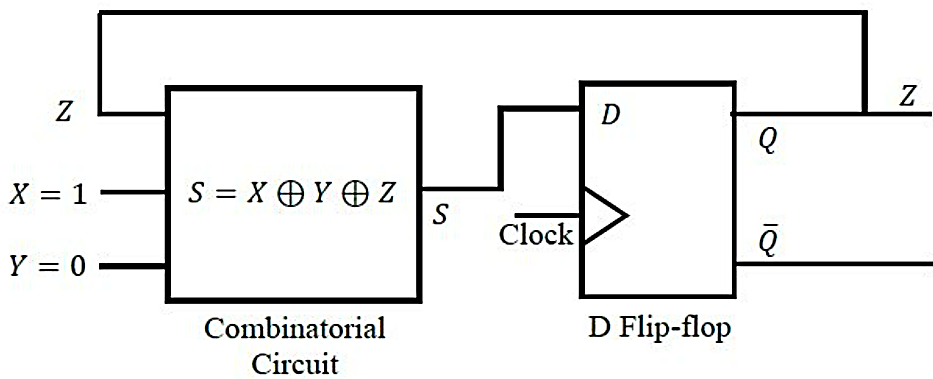

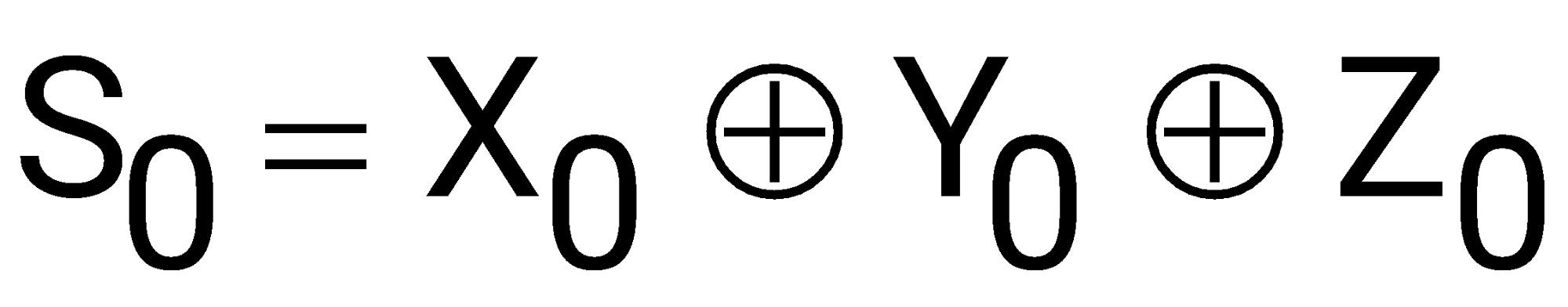

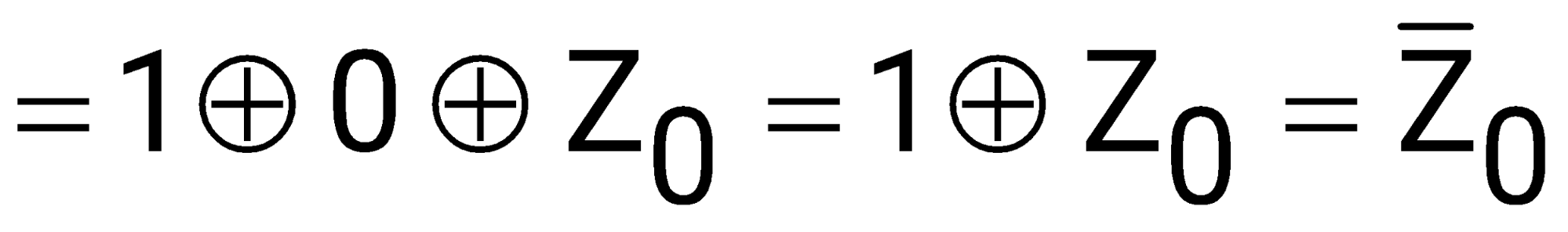

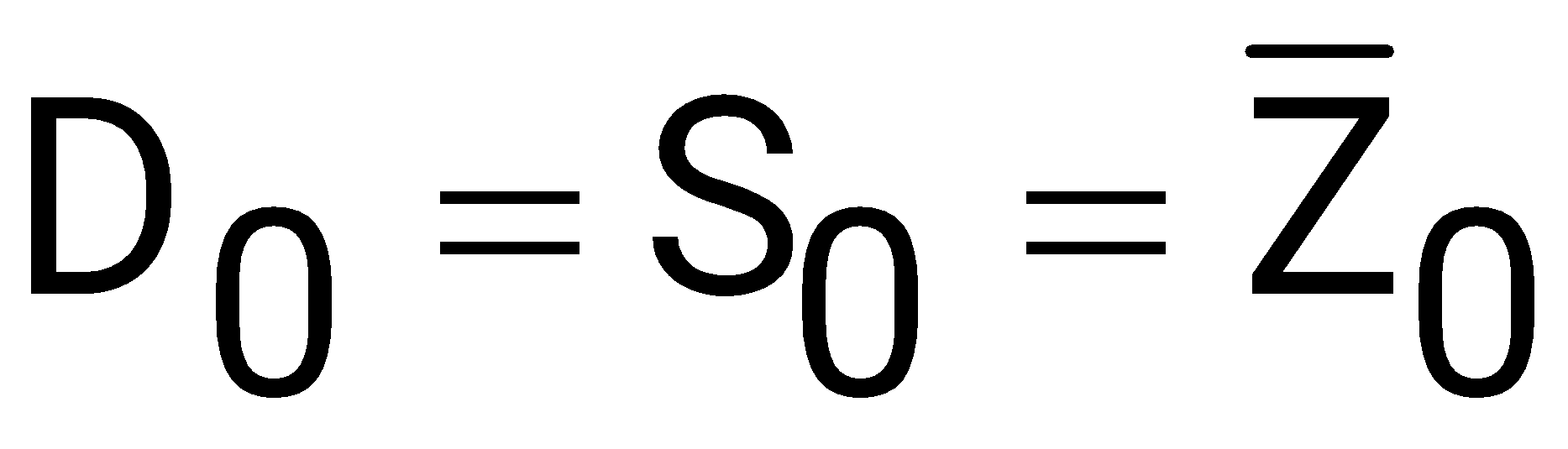

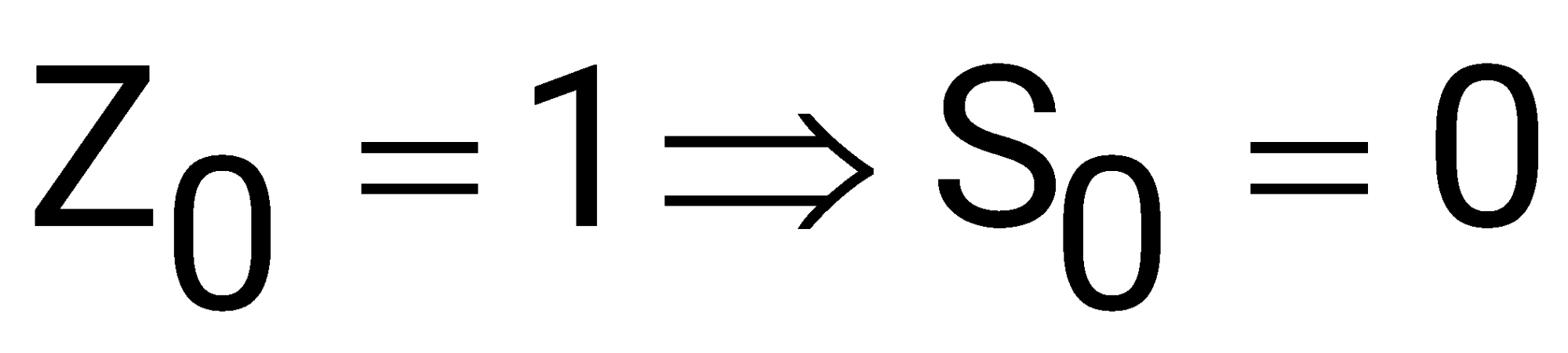

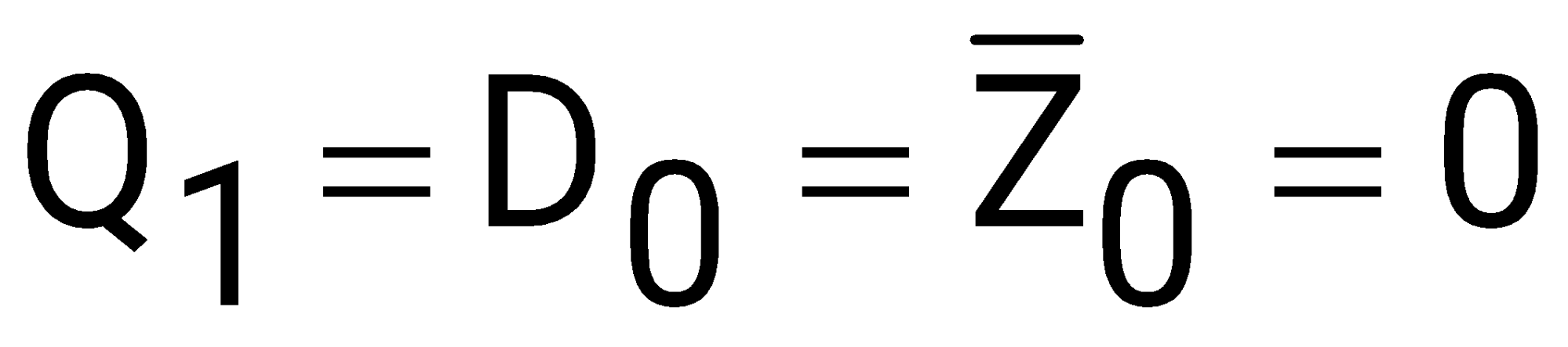

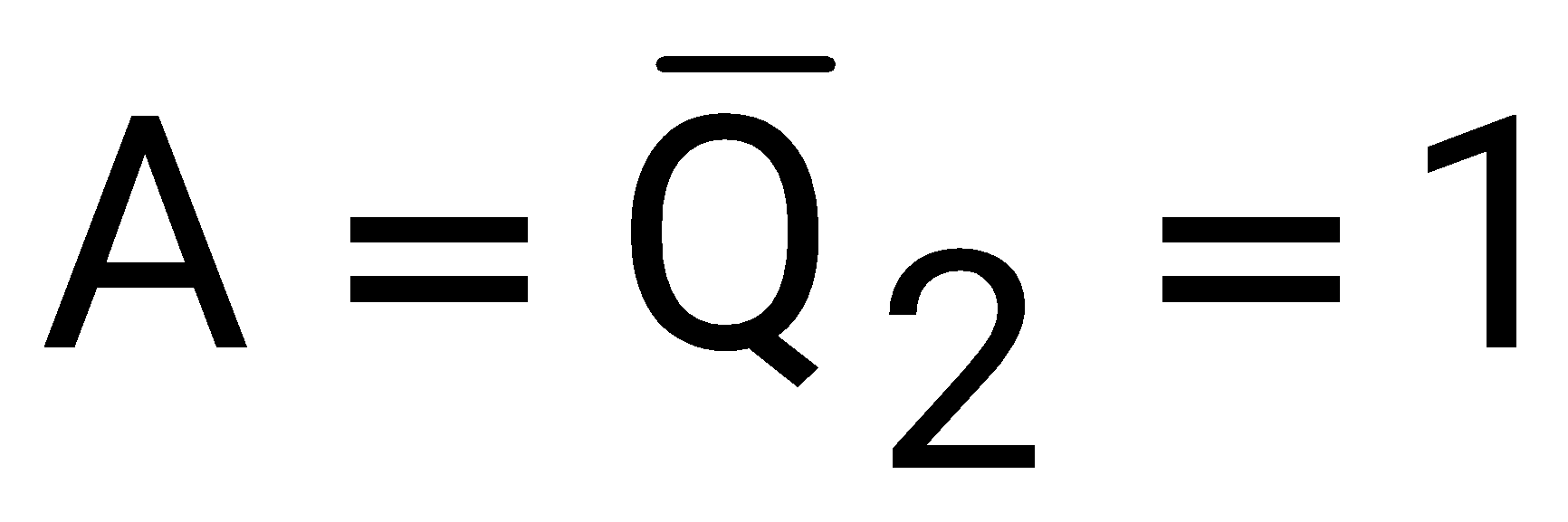

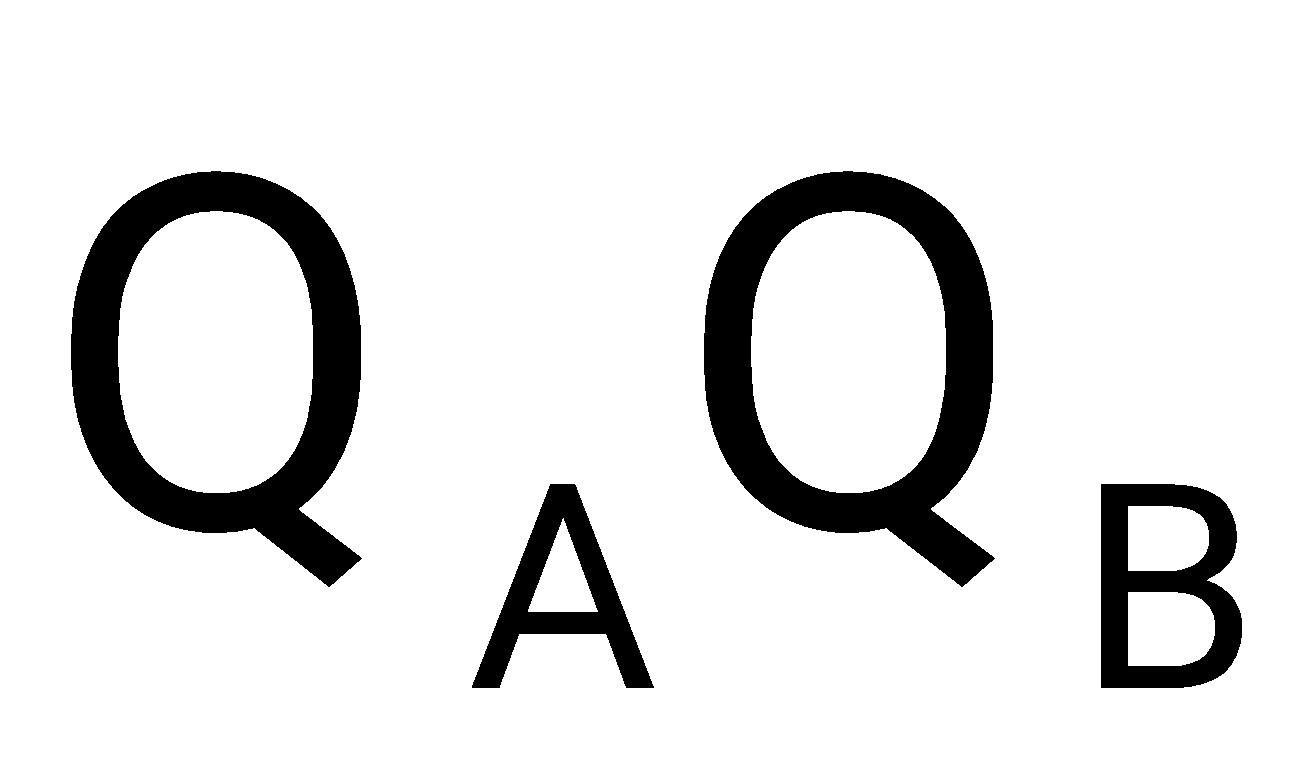

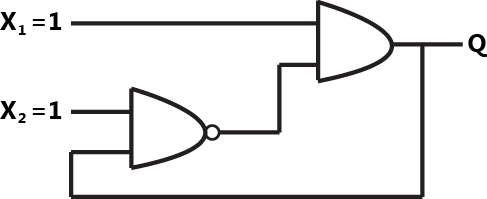

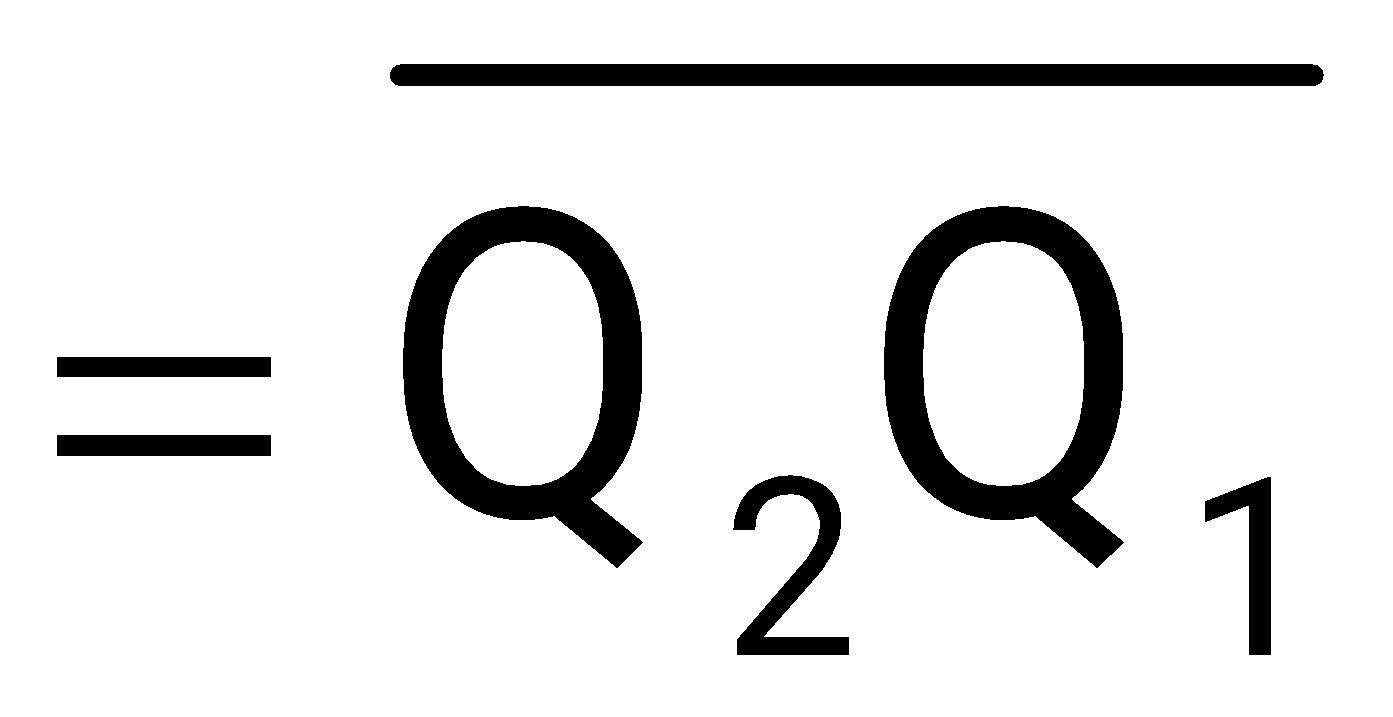

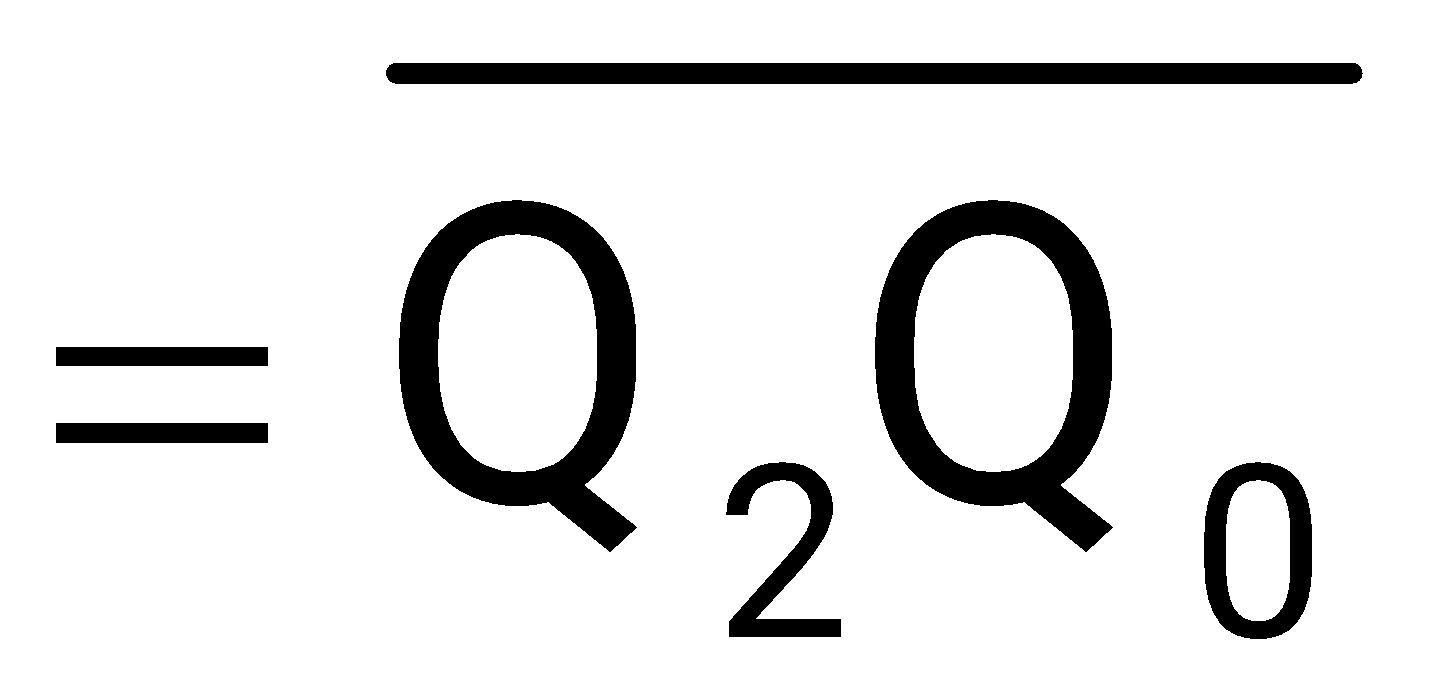

IncorrectIn the circuit, the present value of is 1. Neglecting the delay in the combinatorial circuit, the values of and , respectively, after the application of the clock will be

Since the output Q is fed back to the combinational circuit as Z

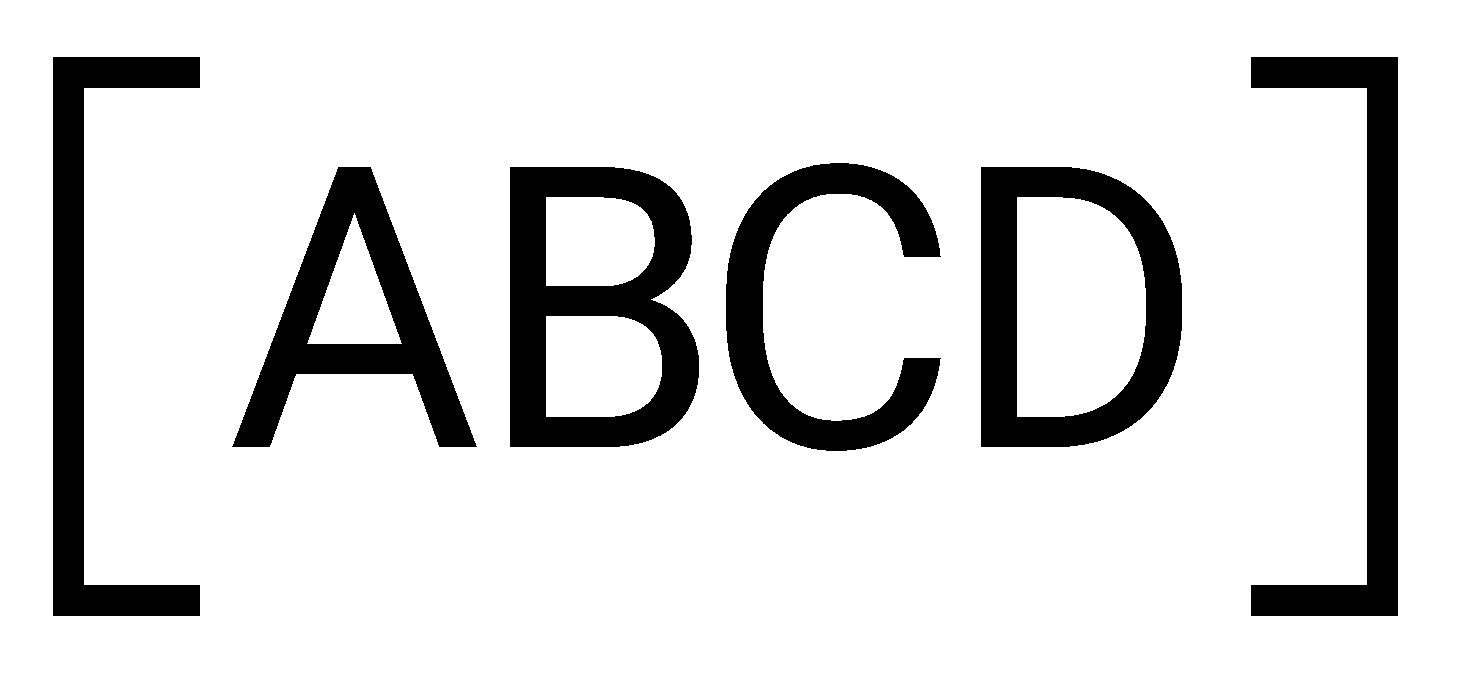

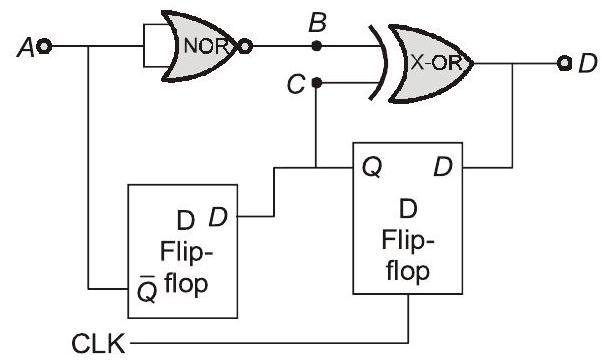

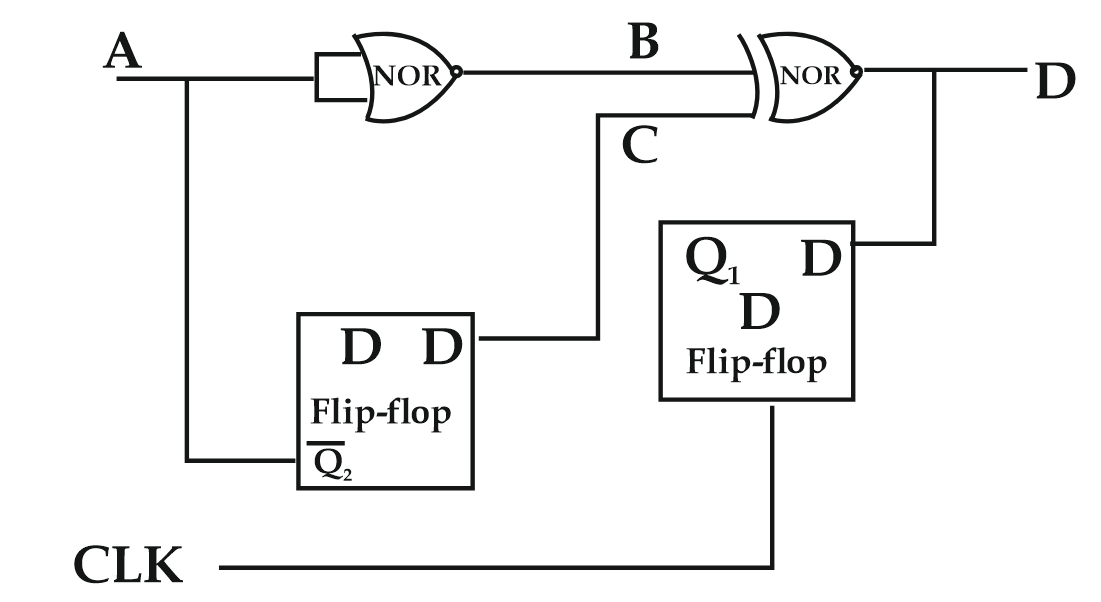

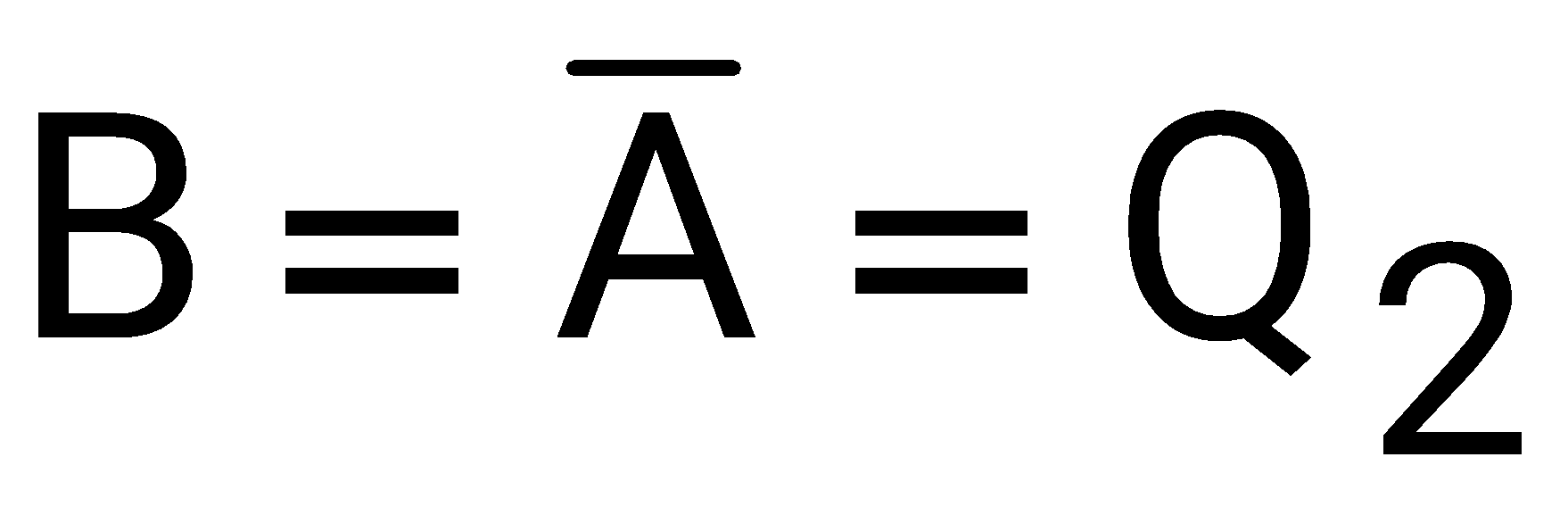

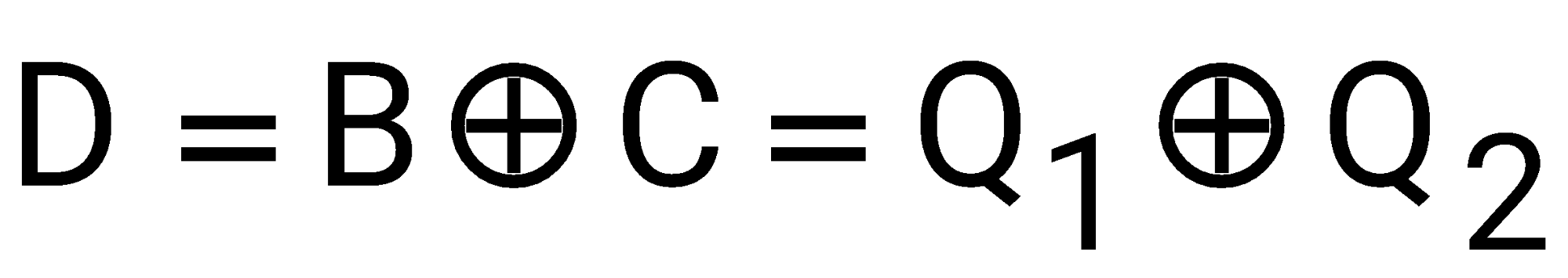

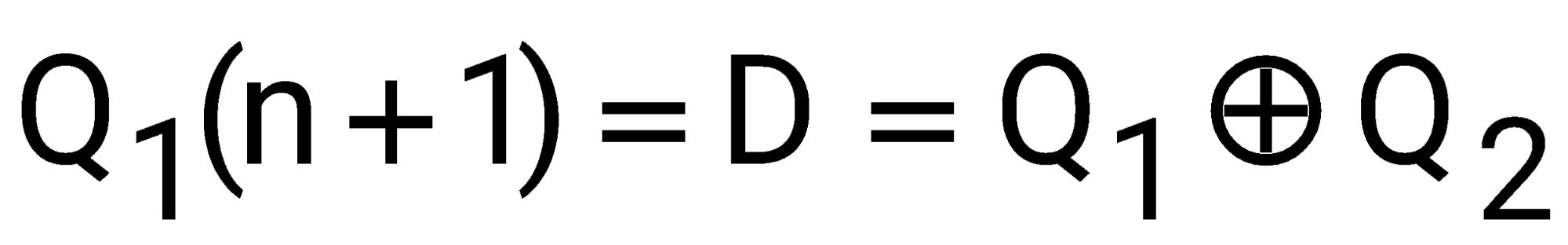

Neglecting the delays due to the logic gates in the circuit shown in figure, the decimal equivalent of the binary sequence of initial logic states, which will not change with clock, is

Assume initial state of circuit Q1 Q2 = 00

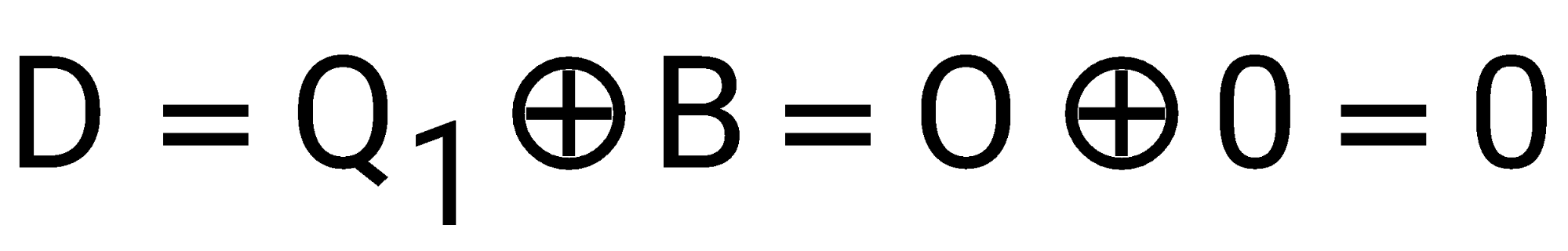

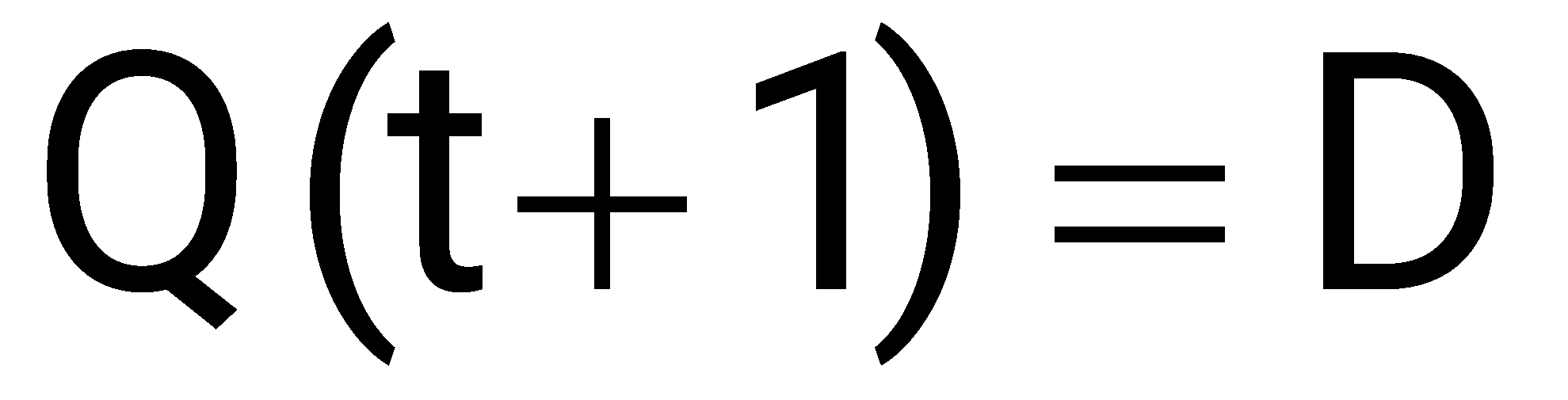

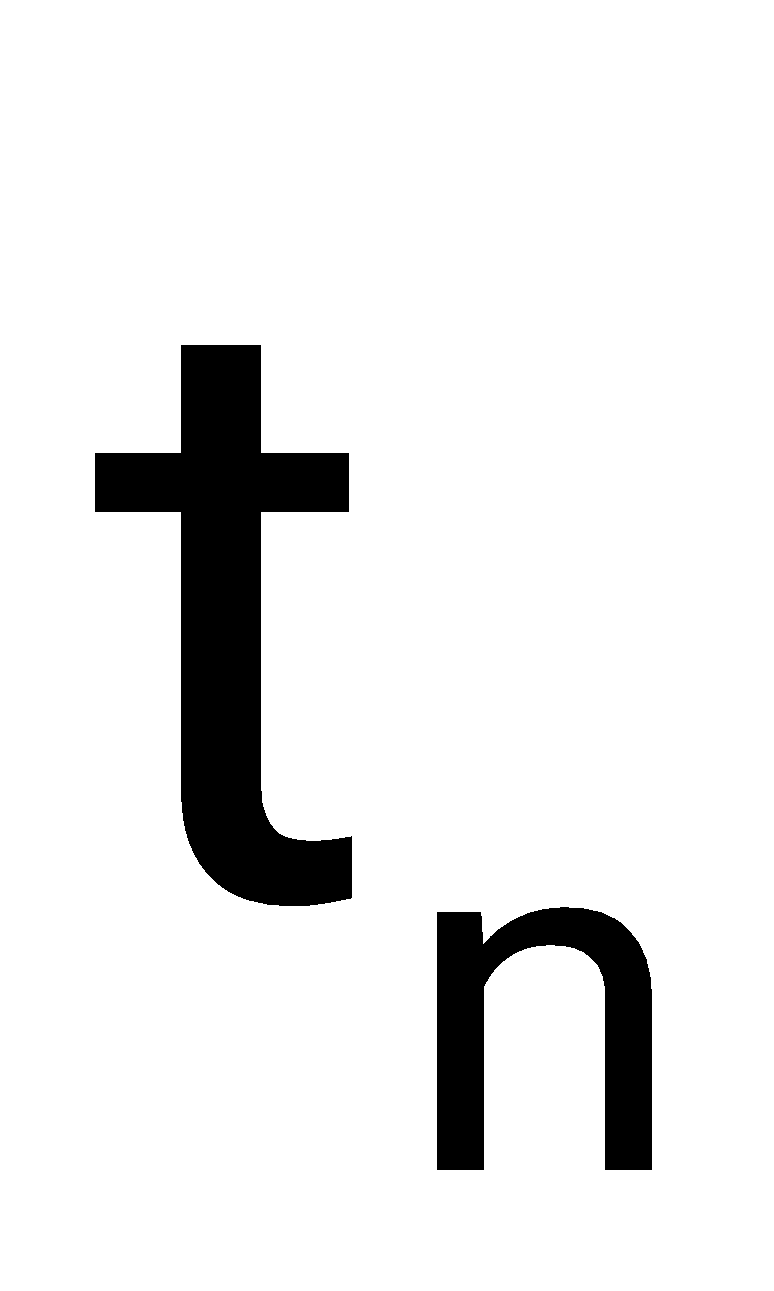

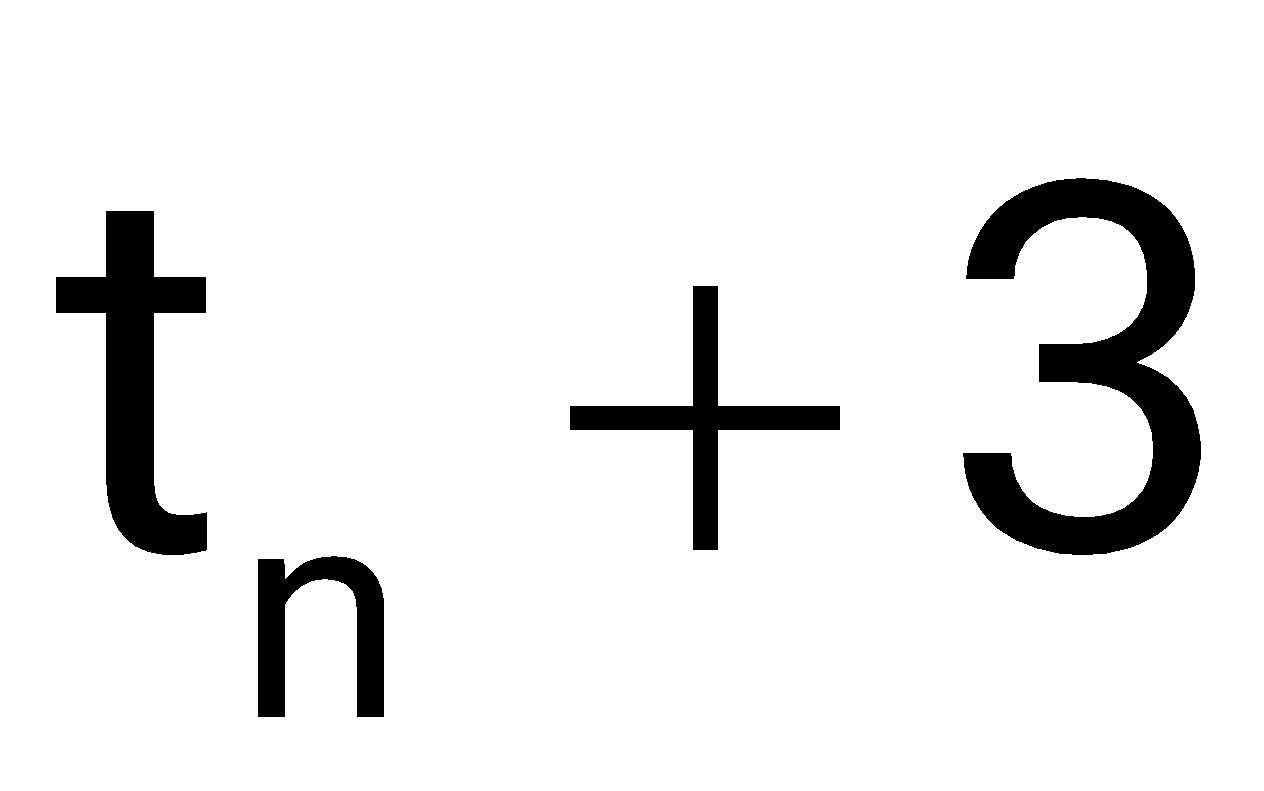

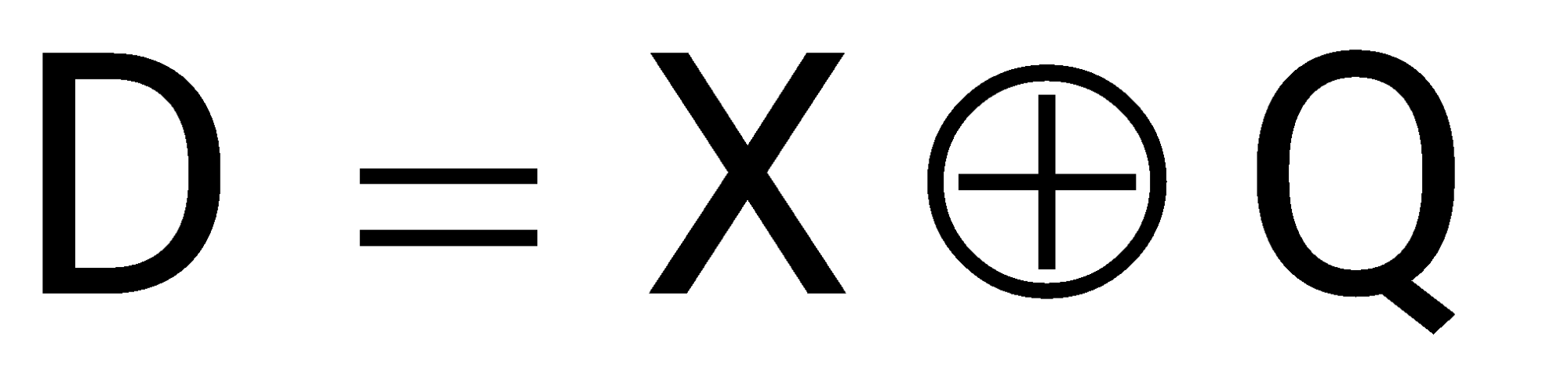

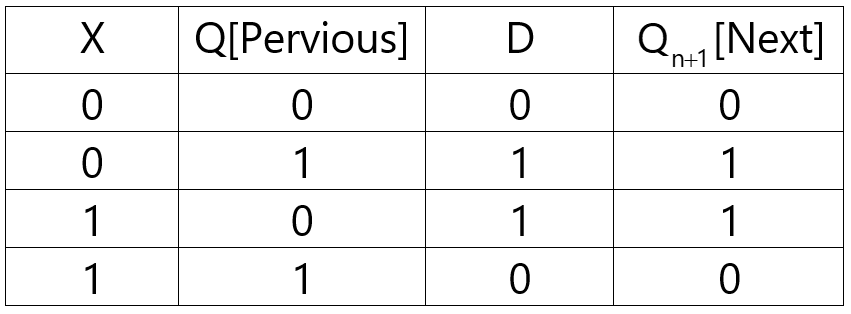

Characteristic equation of D-flip flop: Qn+1 = D

Q2(n+1) = C = Q1

For binary sequence [ABCD] to remain same, state of circuit must remain same

Q1 | Q2 | Q1(n+1) | Q2(n+1) |

0 | 0 | 0 | 0 |

0 | 1 | 1 | 0 |

1 | 0 | 1 | 1 |

1 | 1 | 0 | 1 |

∴ When Q1 Q2 = 00, next state is same as present state & hence binary sequence remains same.

C = Q1 = 0

[ABCD] = [1000]

Decimal value = 8

A MOD 2 and a MOD 5 up-counter when cascaded together results in a MOD ______ counter. (in integer)

In cascade connection, MOD of counters get multiplied

MOD = 2 × 5 = 10

The maximum clock frequency in MHz of a 4-stage ripple counter, utilizing flipflops, with each flip-flop having a propagation delay of 20 ns, is ___________. (round off to one decimal place)

Maximum propagation delay = ntpd = 4 × 20 ns = 80 ns

Clock period TCLK ≥ 80 ns

fCLK ≤ 1/80 ns

fCLK ≤ 12.5 MHz

A 16-bit synchronous binary up-counter is clocked with a frequency fCLK. The two most significant bits are OR-ed together to form an output Y. Measurements show' that Y is periodic, and the duration for which Y remains high in each period is 24 ms. The clock frequency fCLK is _________ MHz. (Round off to 2 decimal places.)

The output Y will be 1 whenever any of the two MSB is 1.

Total number of clock cycles = 216

16th bit is 0 for first 215 cycles & 1 for next 215 cycle

15th bit is 0 for first 214 cycles then 1 for next 214 cycles & so on

First 214 cycles: both 0 ; Y = 0

Next 214 cycles: MSB = 0, 15th bit = 1 ; Y = 1

Next 214 cycles: MSB = 1, 15th bit = 0 ; Y = 1

Next 214 cycles: MSB = 1, 15th bit = 1 ; Y = 1

∴ Y = 1 for 3 × 214 cycles

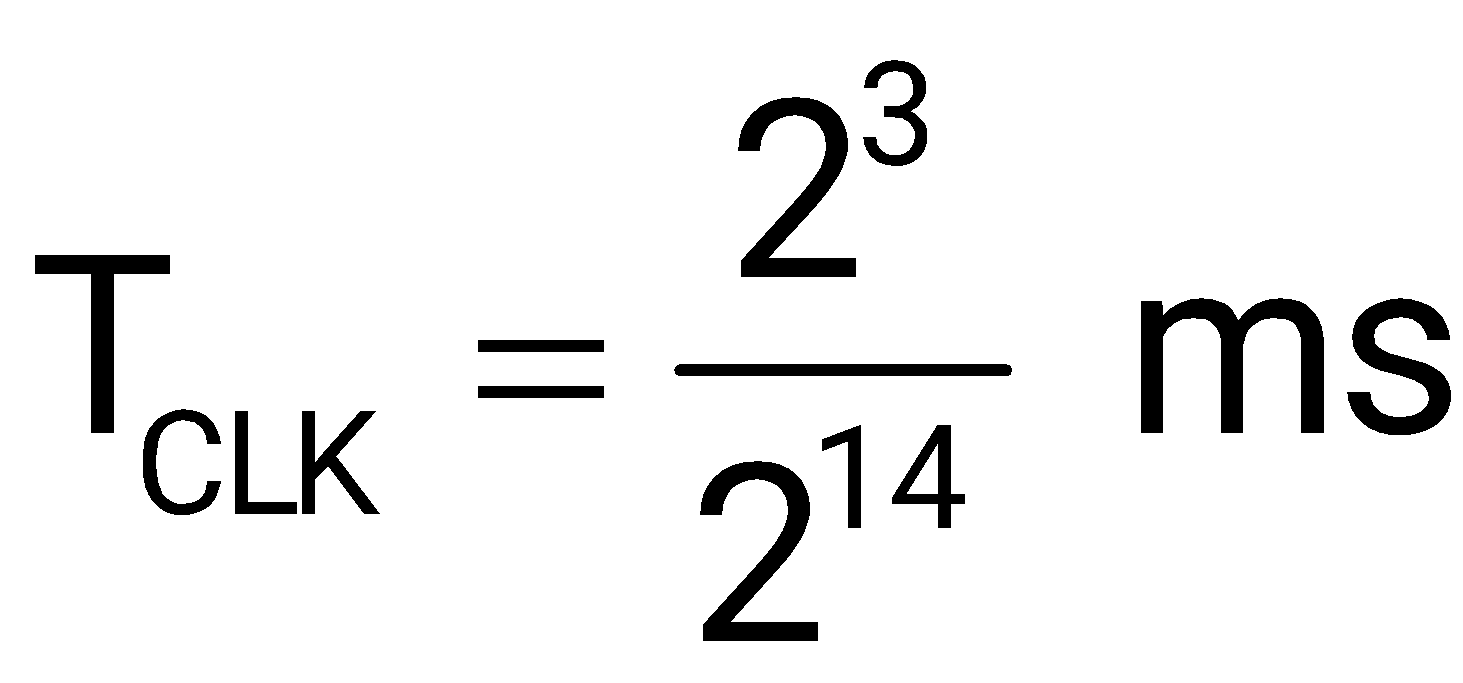

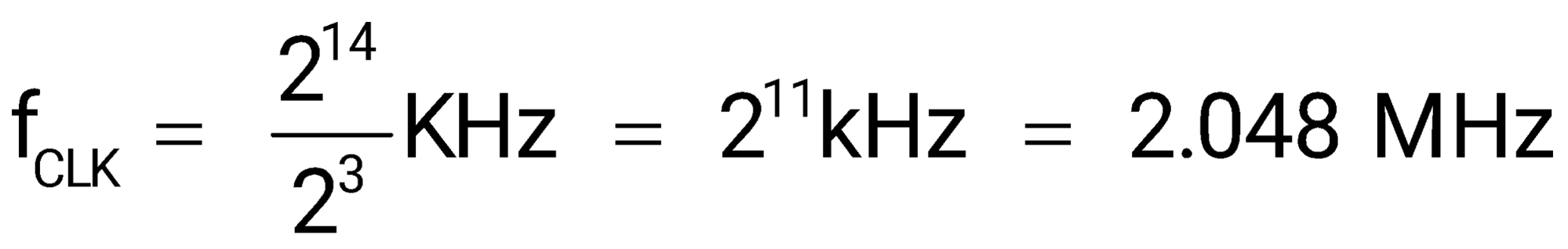

3 × 214 TCLK = 24 ms

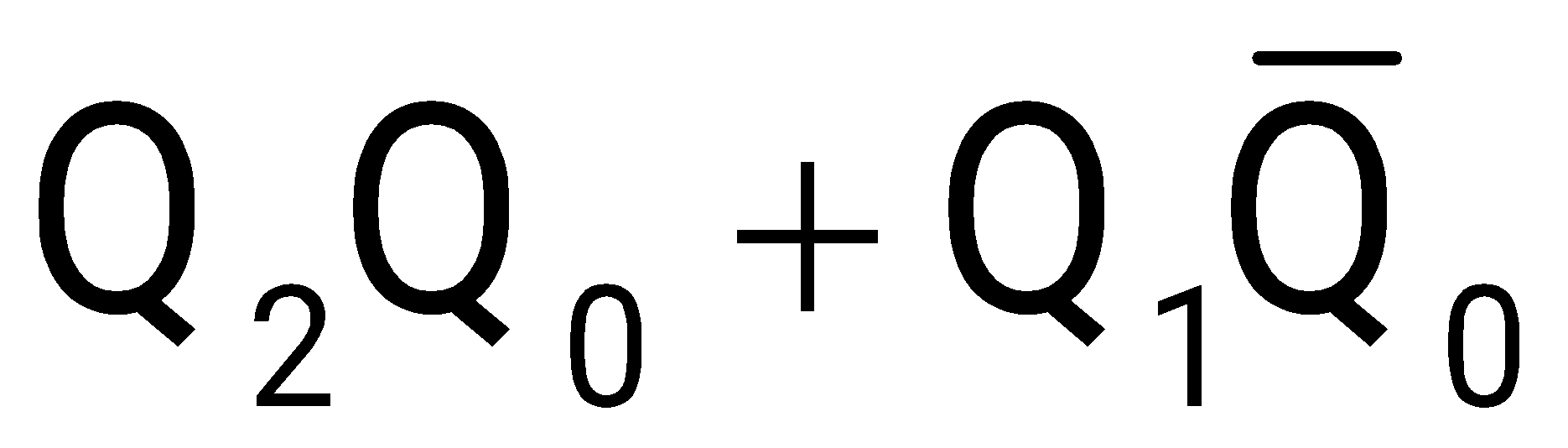

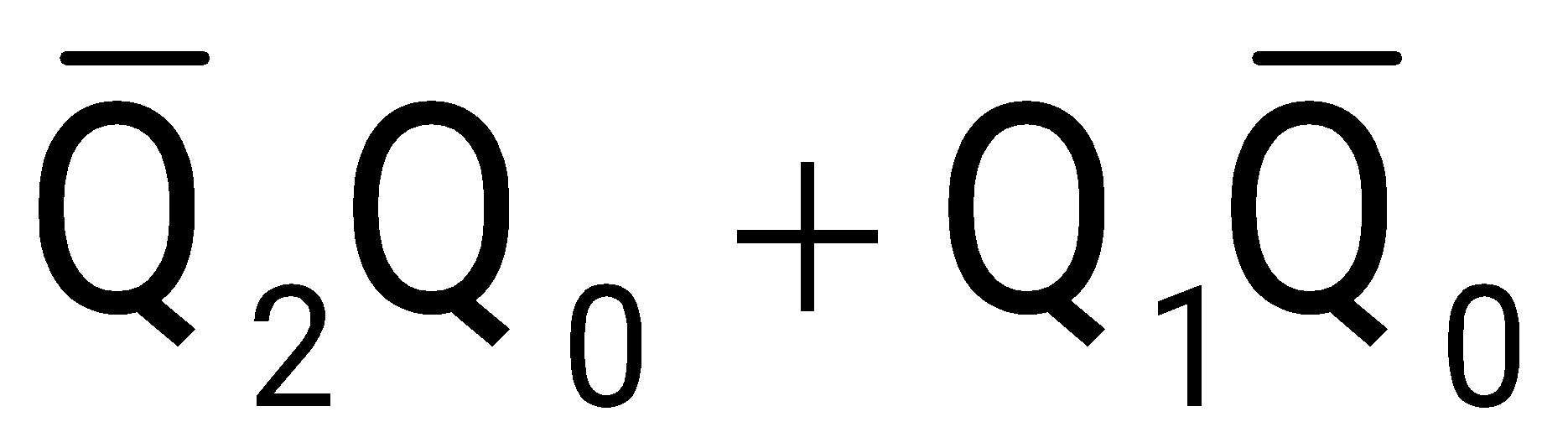

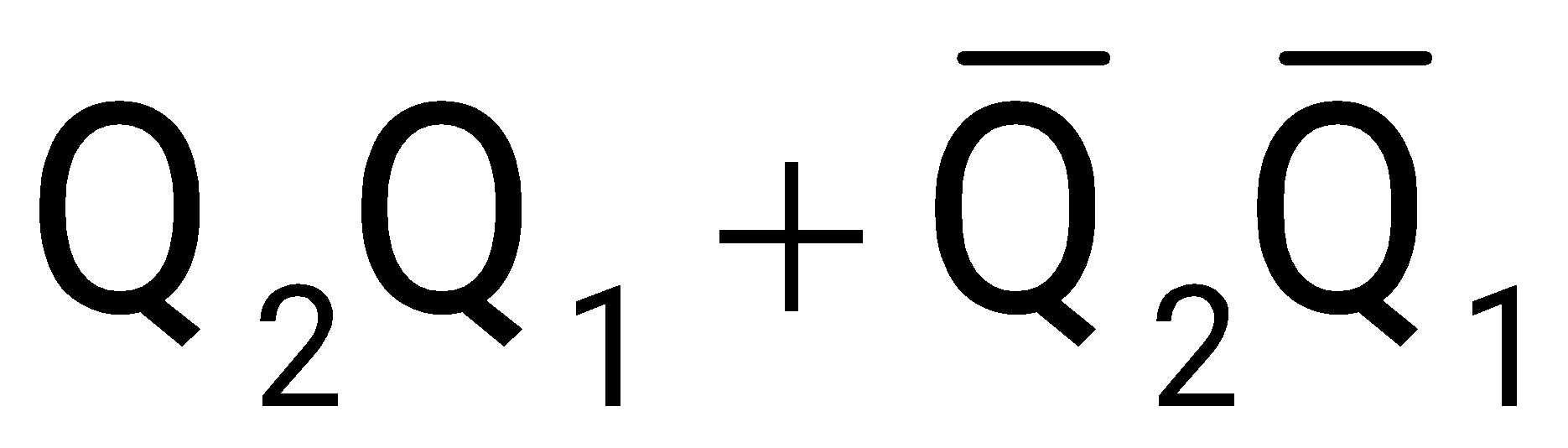

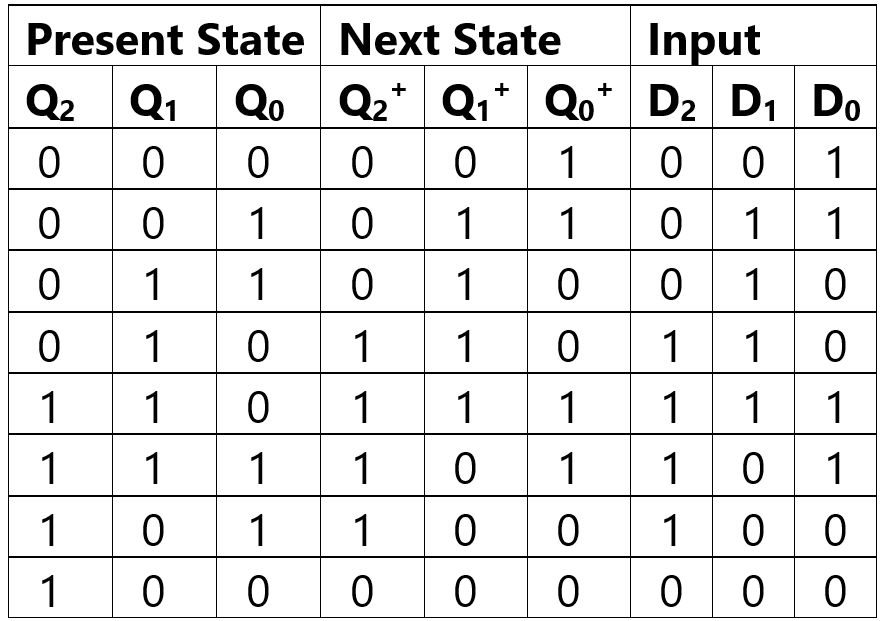

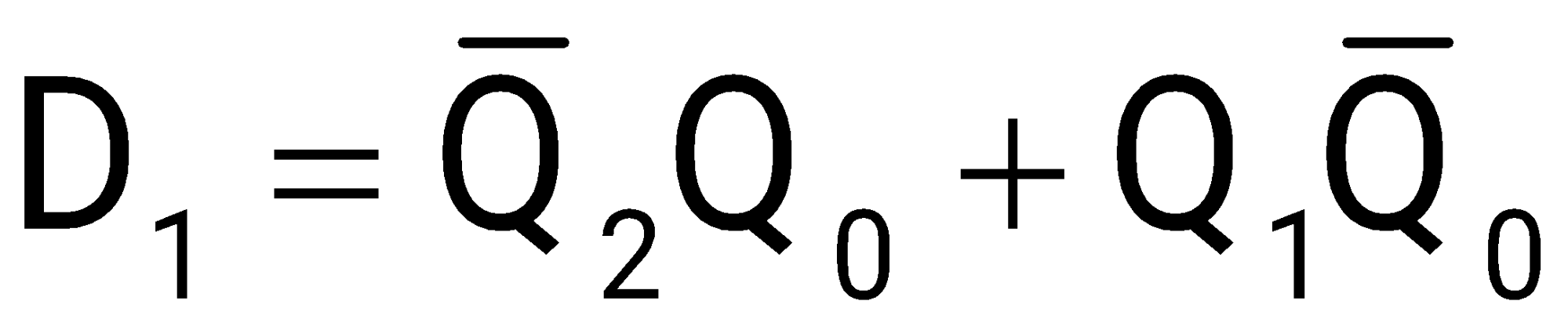

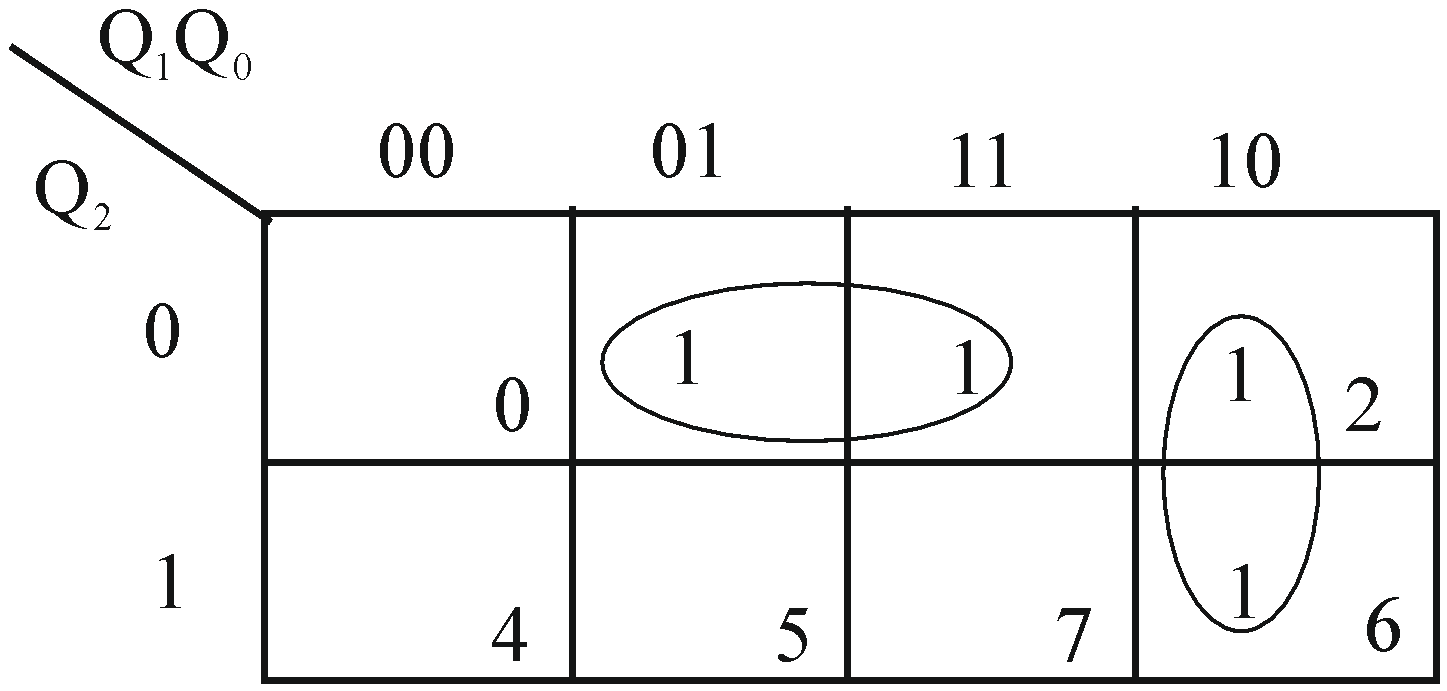

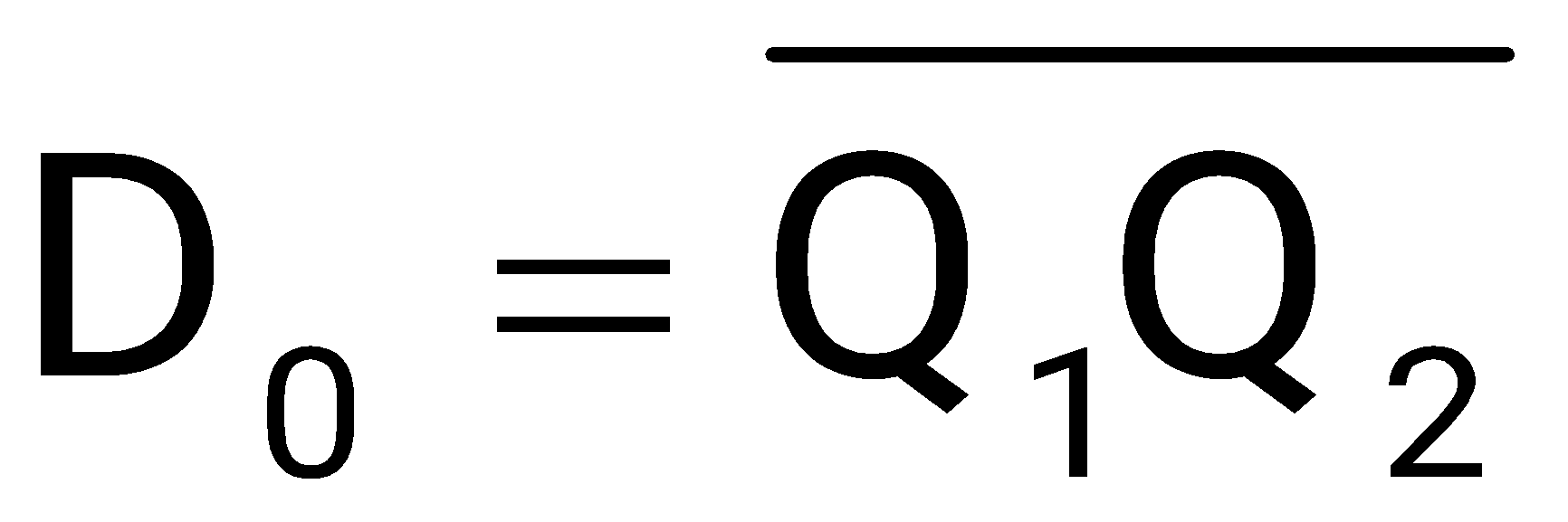

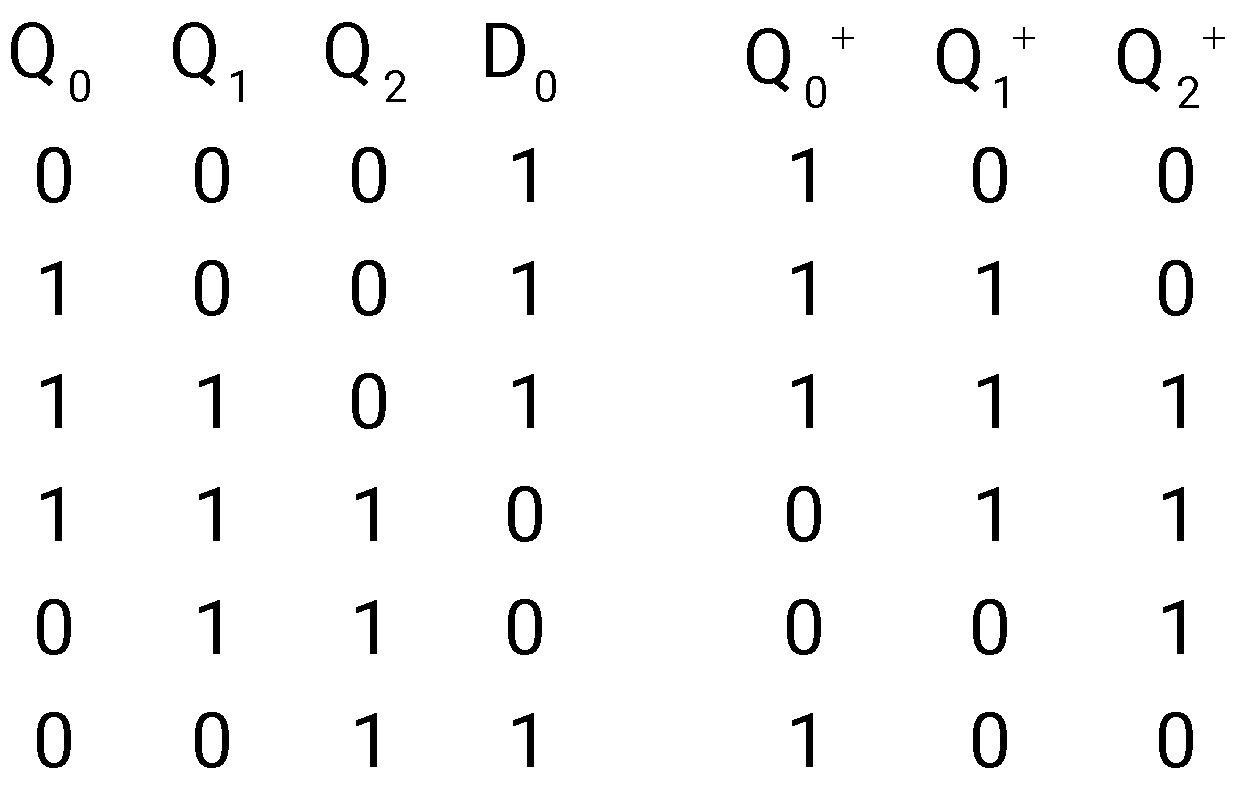

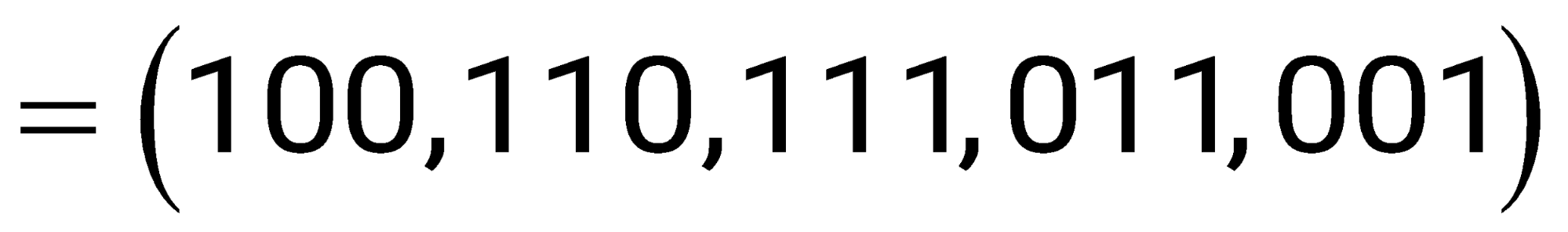

A counter is constructed with three D flip-flops. The input-output pairs are named (D0, Q0), (D1, Q1), and (D2, Q2), where the subscript 0 denotes the least significant bit. The output sequence is desired to be the Gray-code sequence 000, 001, 011, 010, 110, 111, 101, and 100, repeating periodically. Note that the bits are listed in the Q2 Q1 Q0 format. The combinational logic expression for D1 is

D1 = Σm (1, 2, 3, 6)

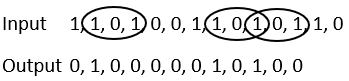

A sequence detector is designed to detect precisely 3 digital inputs, with overlapping sequences detectable. For the sequence (1,0,1) and input data (1,1,0,1,0,0,1,1,0,1,0,1,1,0), what is the output of this detector?

The sequence detector will output 1 as soon as a sequence 101 is detected & until then output remains 0.

Due to overlapping sequences, we can use digits of previous sequence to generate new sequence.

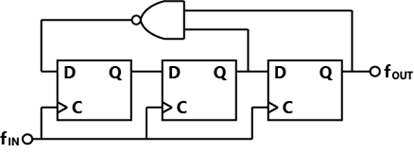

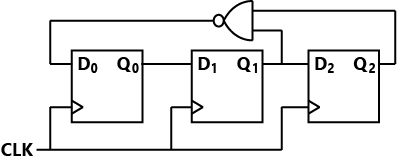

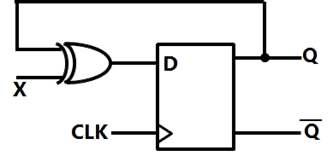

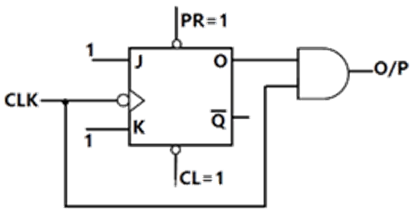

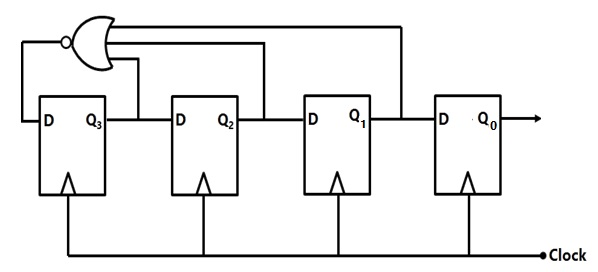

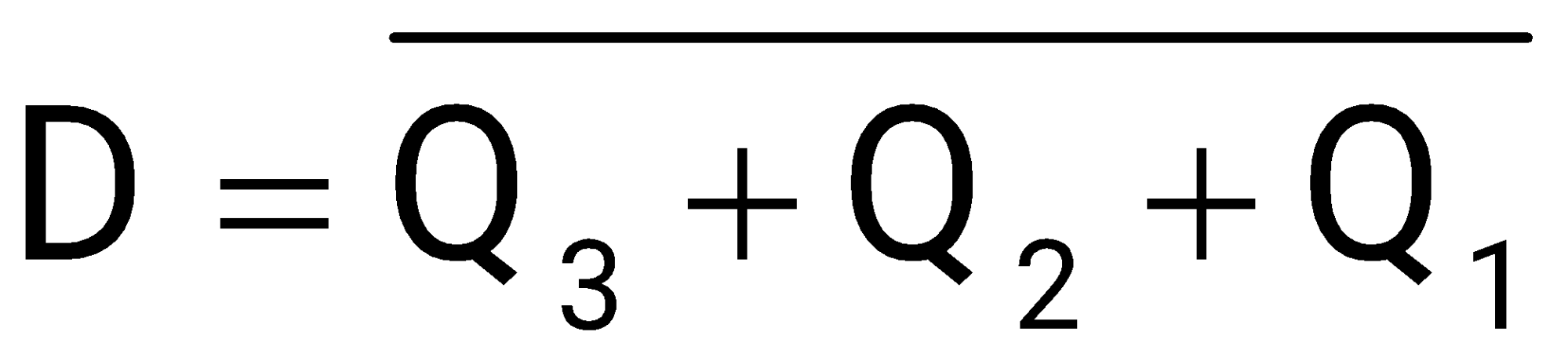

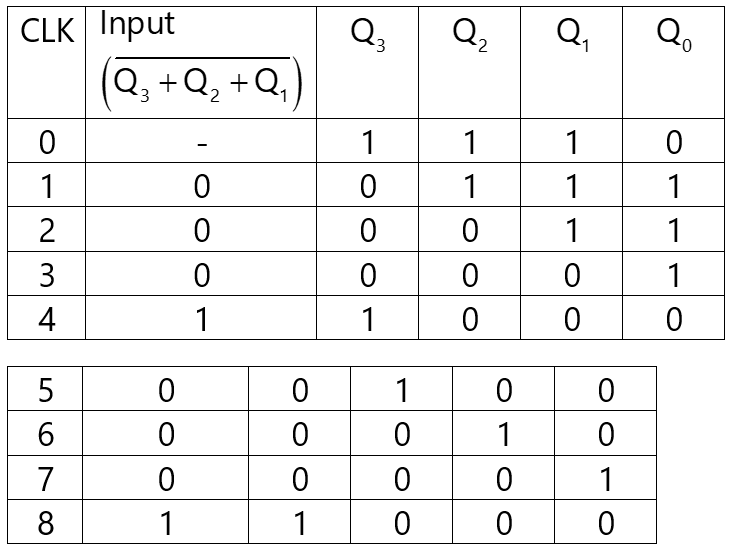

Which one of the following statements is true about the digital circuit shown in the figure?

No. of unique states

Hence, it can divide clock frequency by 5

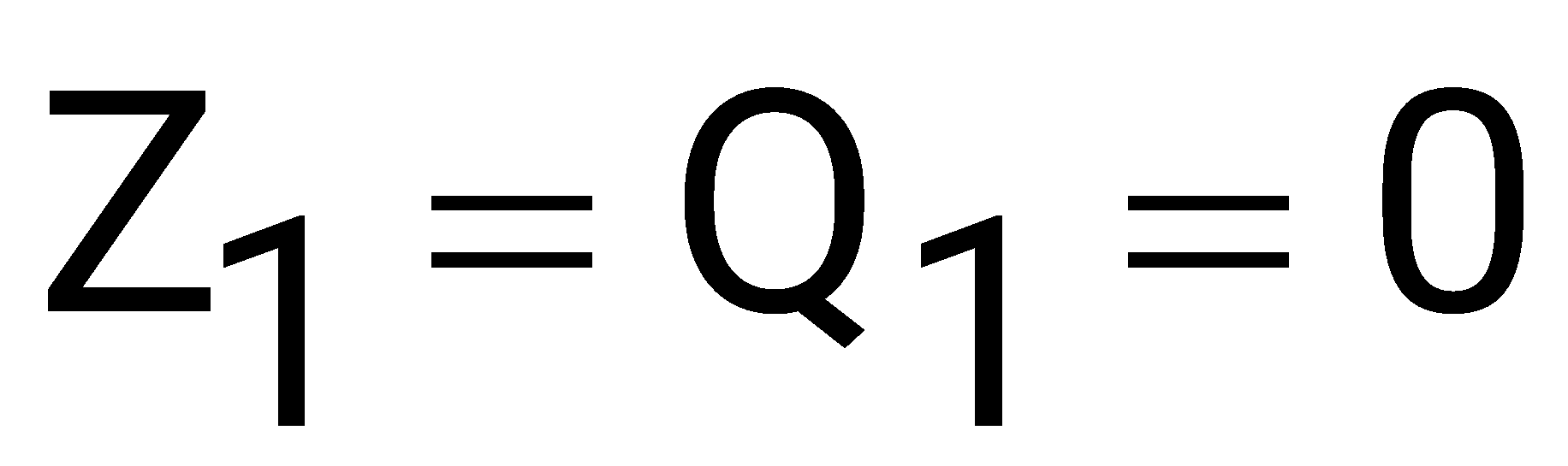

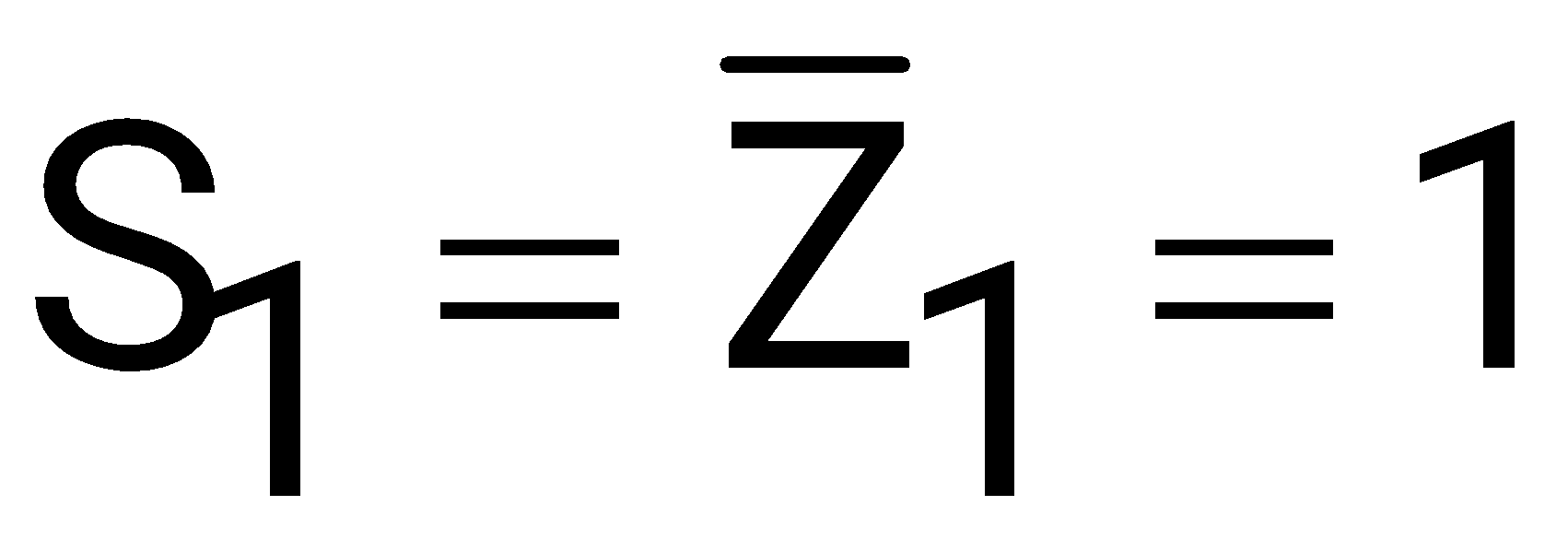

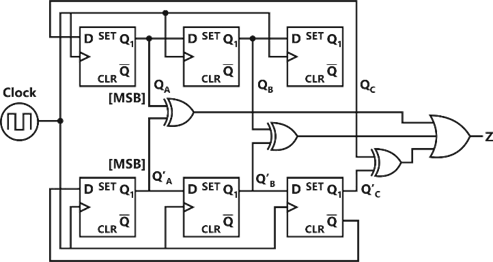

For the synchronous sequential circuit shown below, the output Z is zero for the initial conditions

The minimum number of clock cycles after which the output Z would again become zero is ___________.

The output will be 0 if all inputs are zero and this happens if

On careful observation, is a ring counter and is a Johnson counters so whenever their states are same the output is zero

Hence, after 6 cycles output is zero.

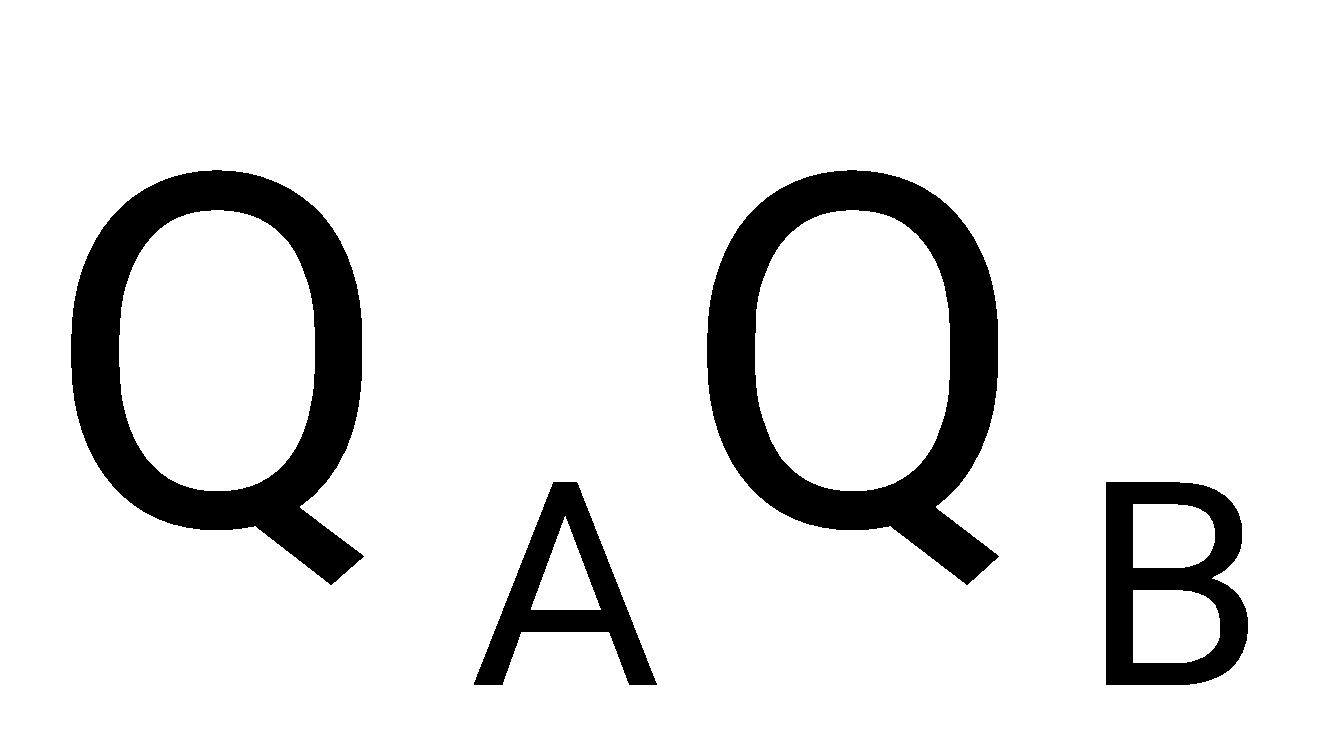

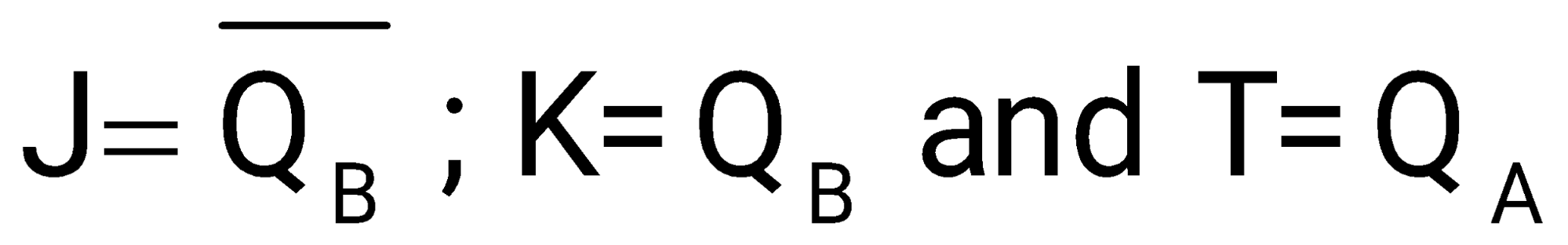

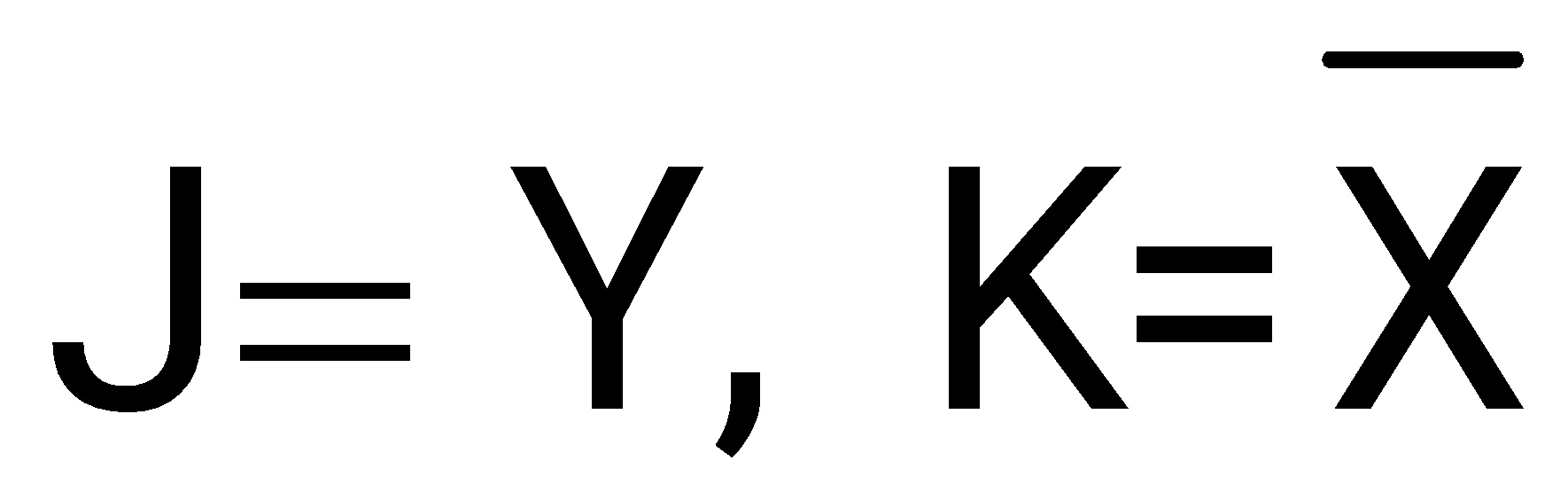

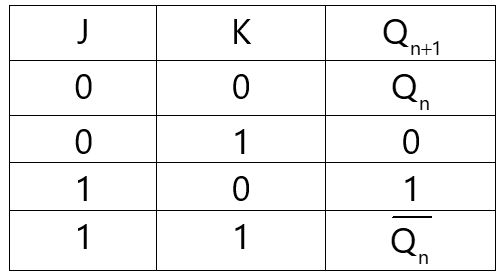

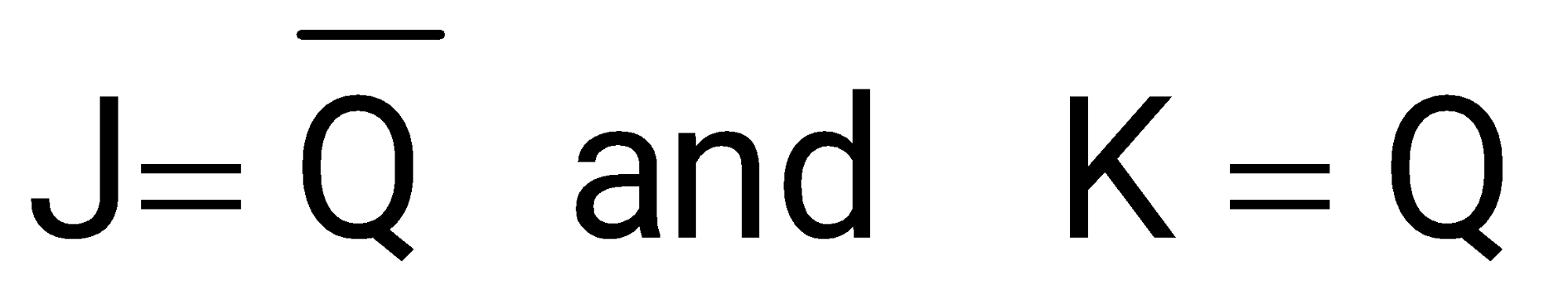

The current state of a two JK flip-flop system is 00. Assume that the clock rise-time is much smaller than the delay of the JK flip-flop. The next state of the system is

The JK inputs of the first flip flop are both pulled high and the JK inputs of the second flip flop are connected to which is initially 1.

When , it is toggle condition.

So output of both the flip-flops will be change to 1 in the next state.

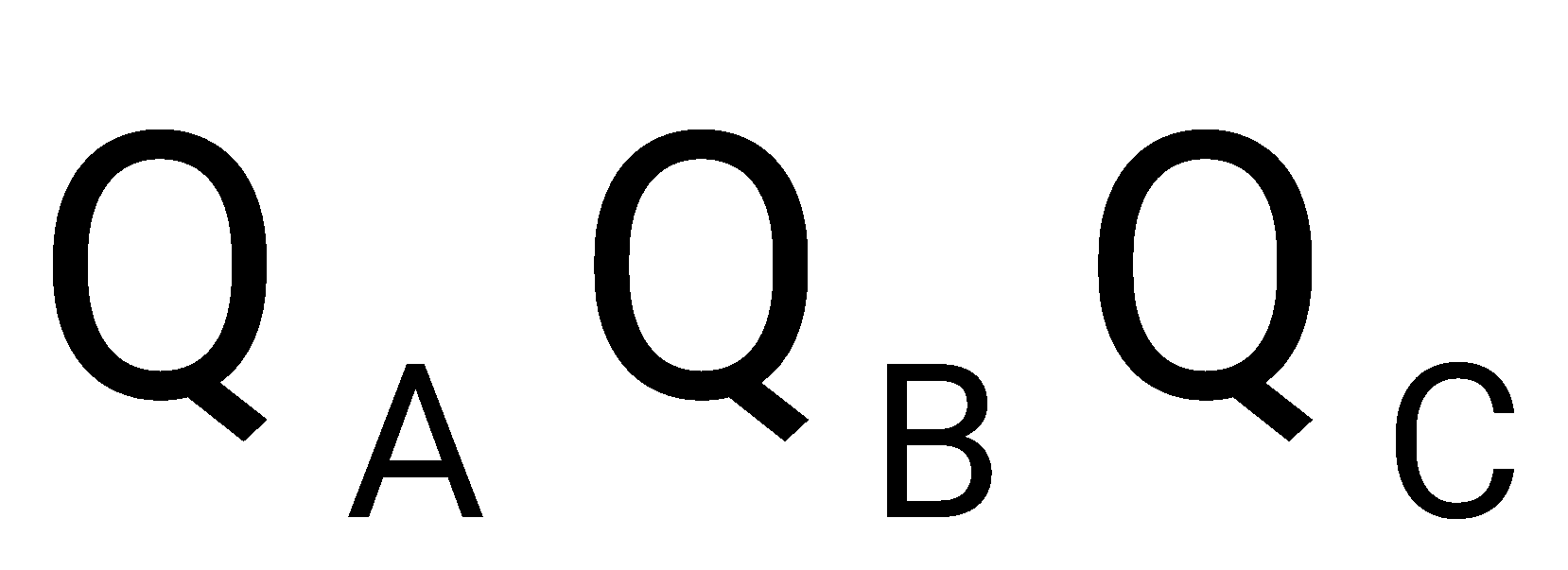

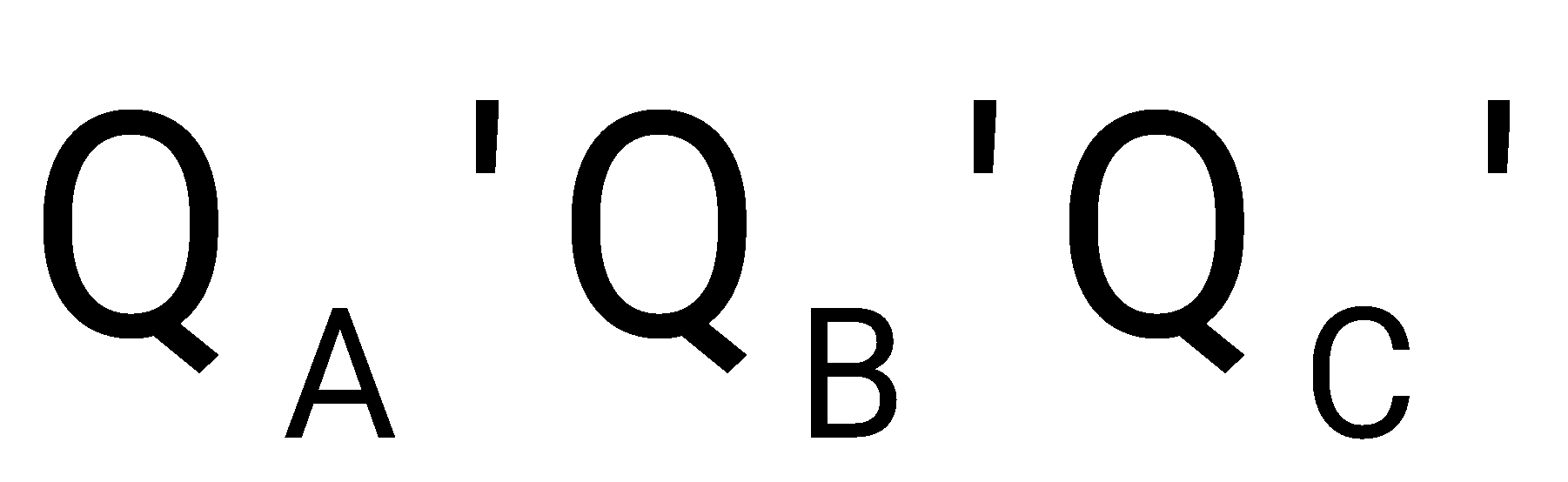

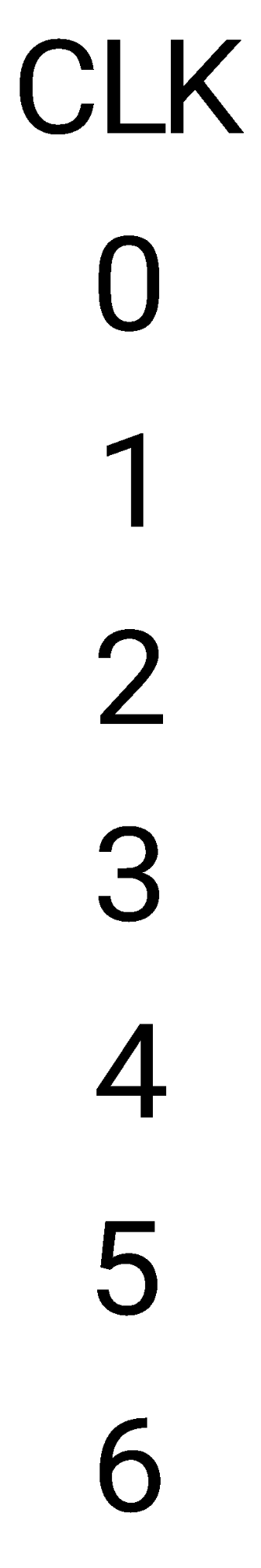

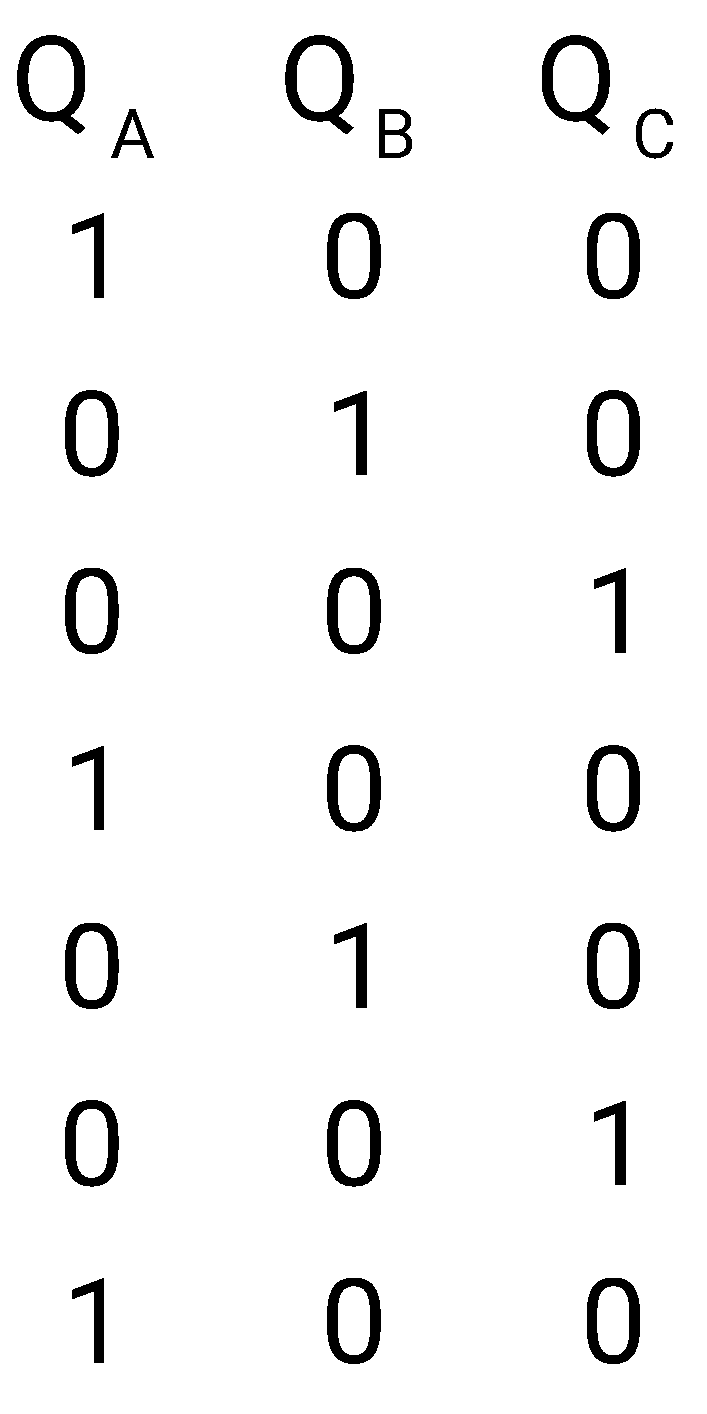

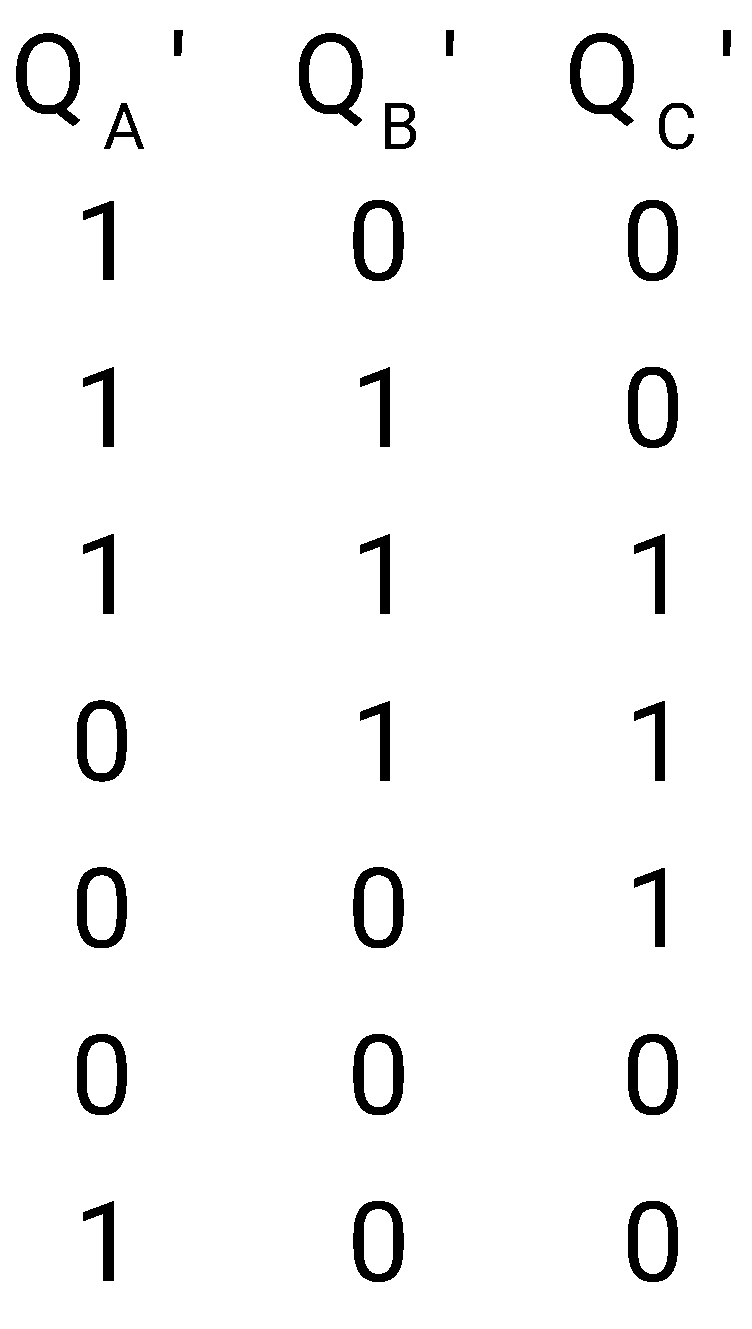

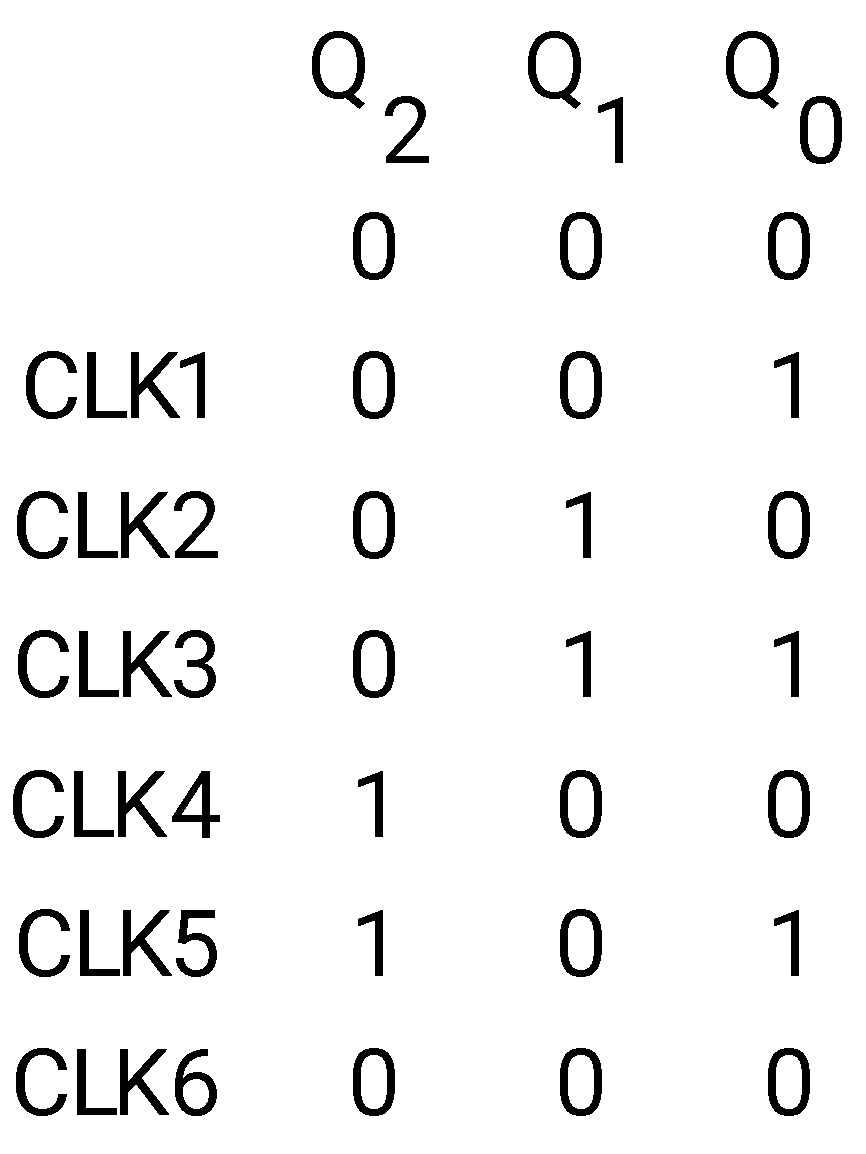

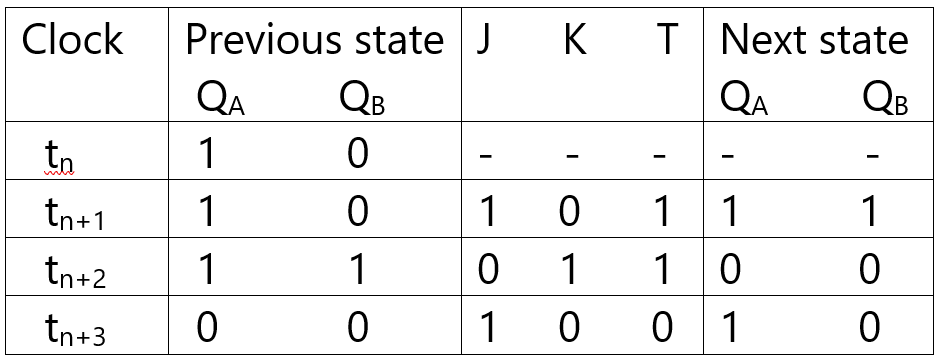

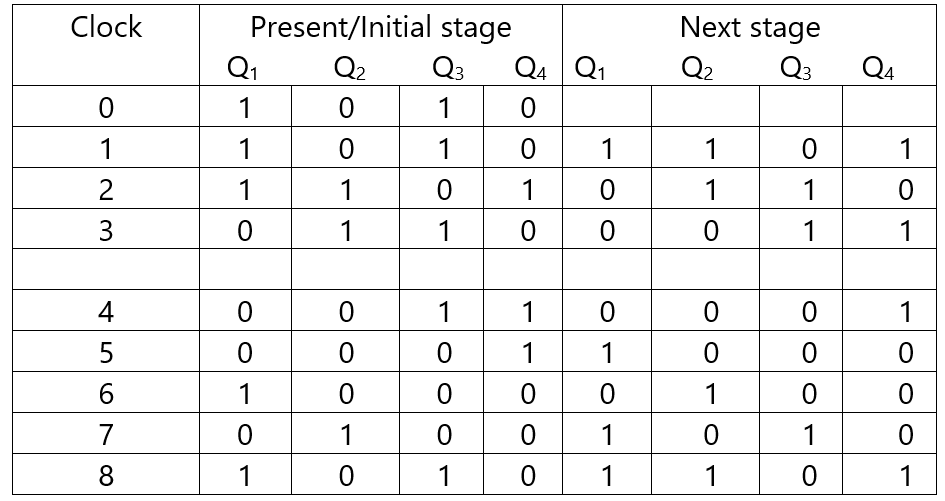

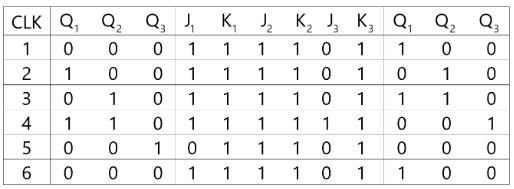

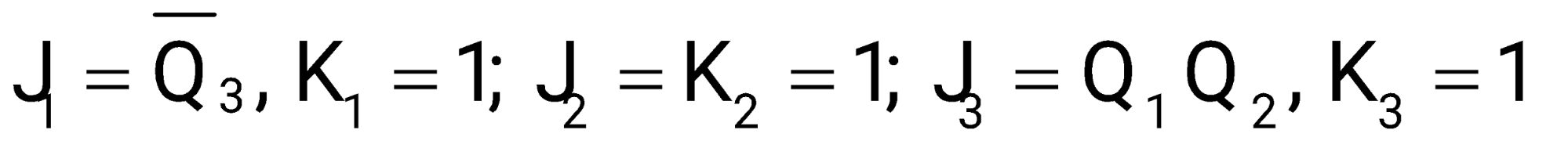

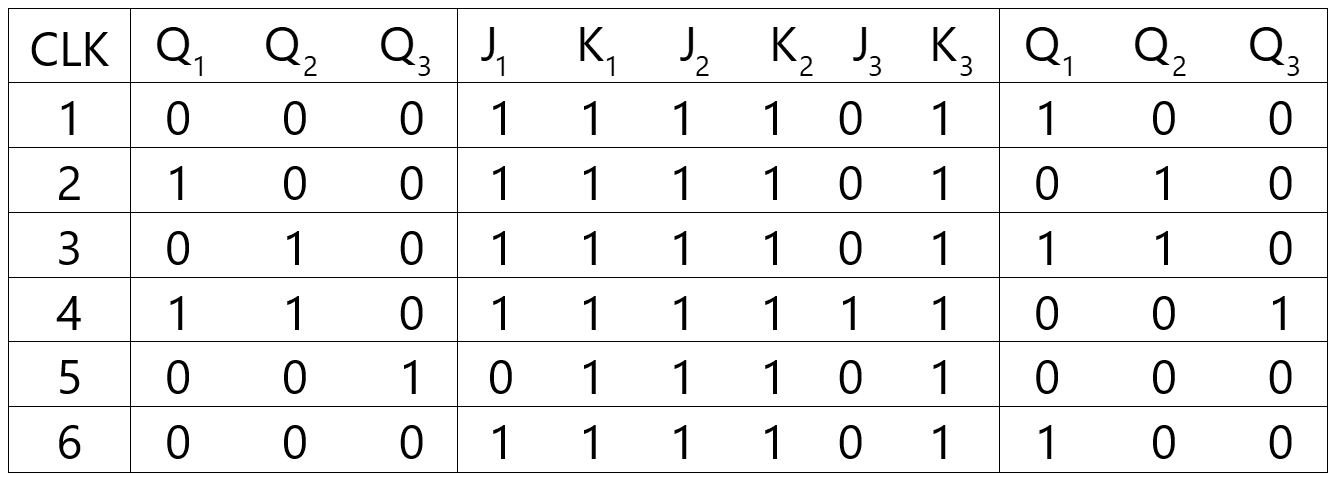

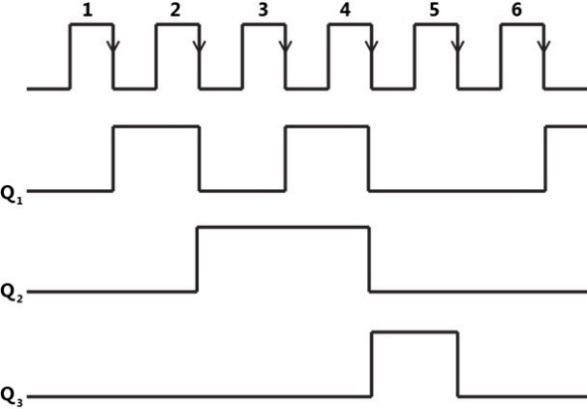

The figure shows a digital circuit constructed using negative edge triggered J – K flip flops. Assume a starting state of . This state will repeat after __________ number cycles of the clock CLK.

The state table for the system shown is given below,

So, original state is reached after 6 clock cycles.

In the following sequential circuit, the initial state (before the first clock pulse) of the circuit is . The state , immediately after the 333rd clock pulse is

CLK

0 0 0

1 0 1

2 1 1

3 1 0

4 0 0

After 332nd clock pulse, the counter will again reach initial state ( ) = (0 0)

After 333rd clock pulse, the counter will show () = (0 1)

A cascade of three identical modulo – 5 counters has an overall module of

Cascaded connection means that output of one counter acts as a clock for next counter. Hence, the modulus get multiplied. Therefore, overall modulus = 5 × 5 × 5 = 125

Which of the following is an invalid state in an 8-4-2-1 Binary coded decimal counter

The count in a BCD counter cannot go beyond the decimal value 9 and hence (1100), whose decimal equivalent is ‘12’ cannot be a BCD counter output.

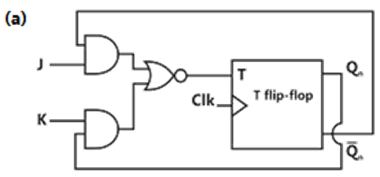

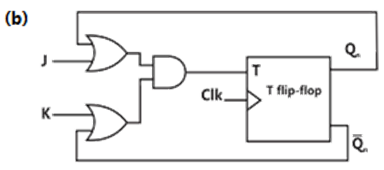

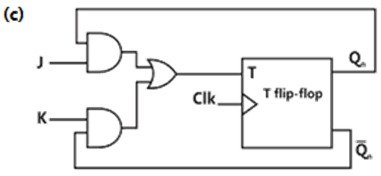

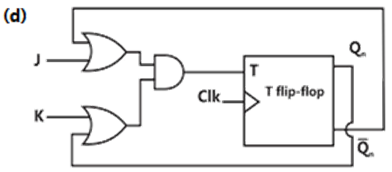

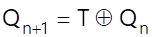

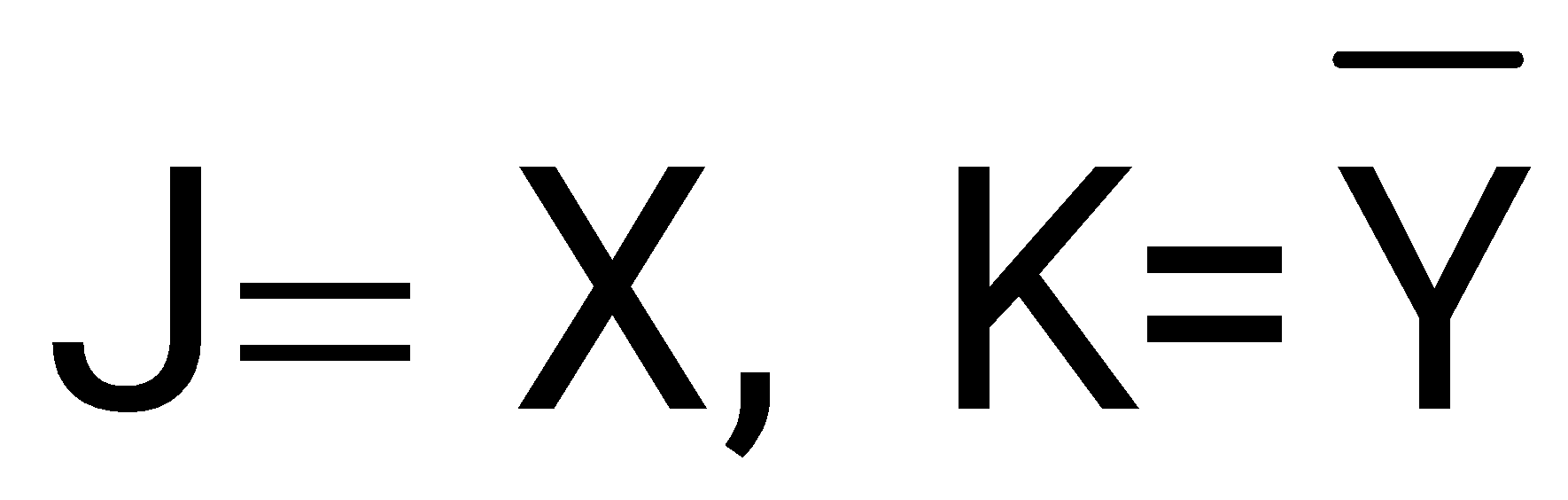

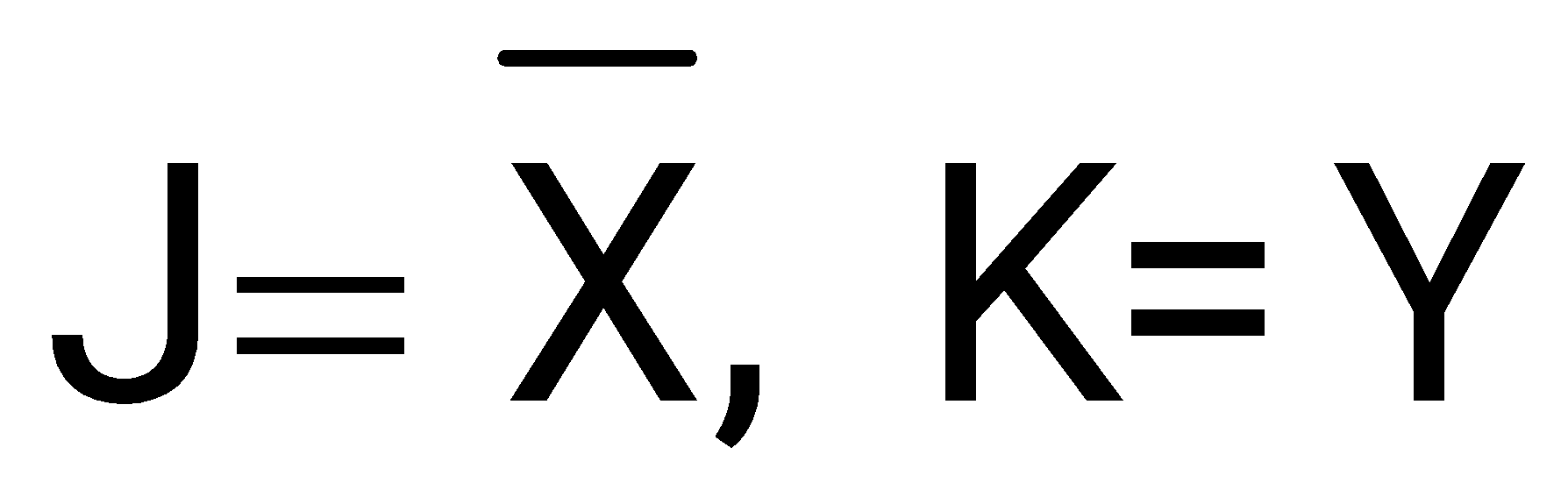

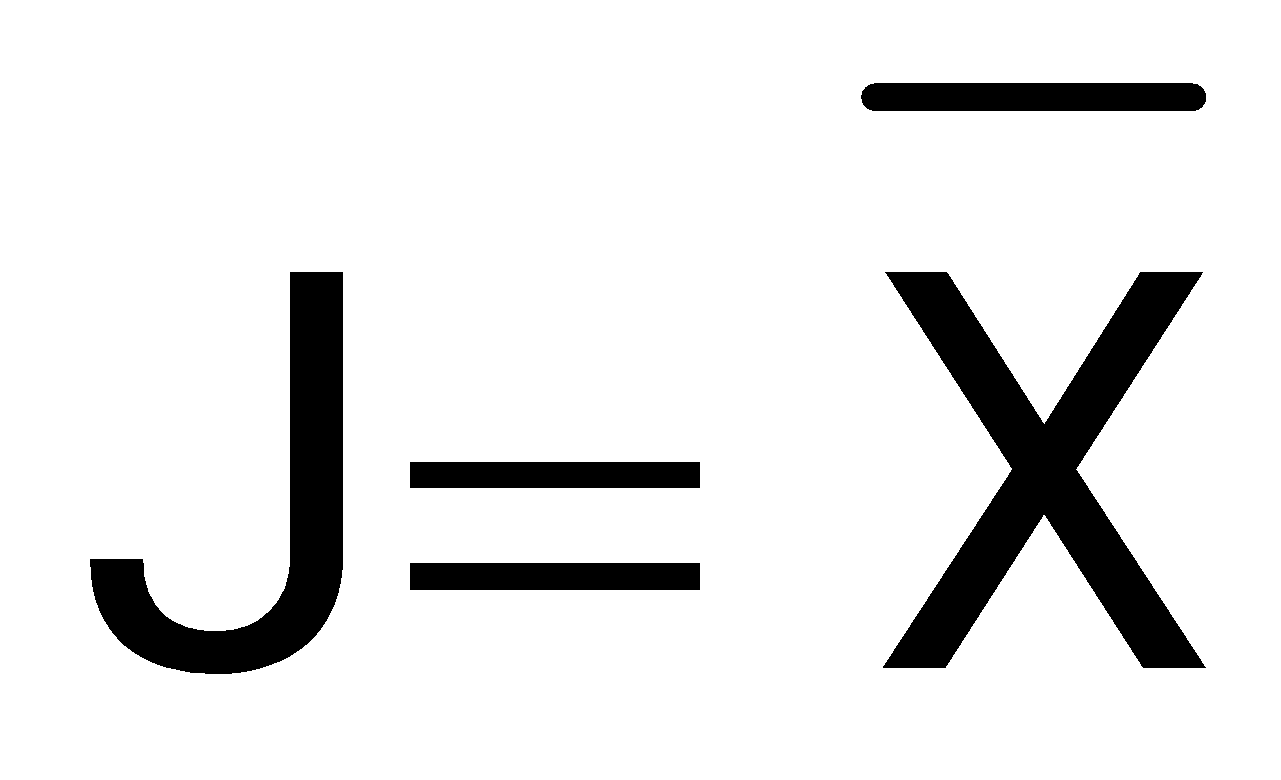

A JK flip flop can be implemented by T flip-flops. Identify the correct implementation.

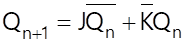

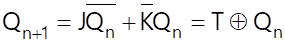

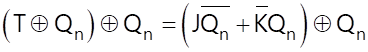

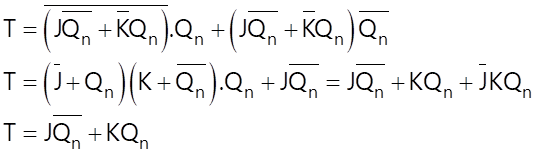

We know, characteristic equation of T flip-flop is,

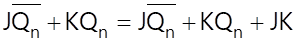

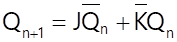

The characteristic equation required for JK Flip Flop is,

So,

To determine the Flip Flop input T, take

By Consensus Theorem,

This logic is implemented in option B.

Note: We can also derive state table for each option to determine the correct answer.

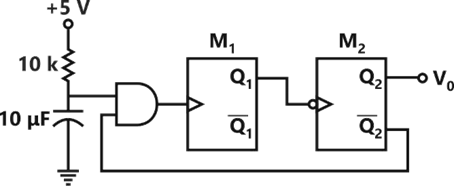

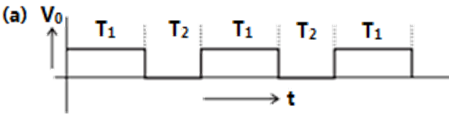

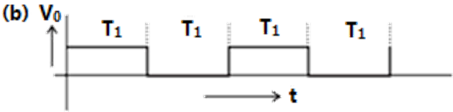

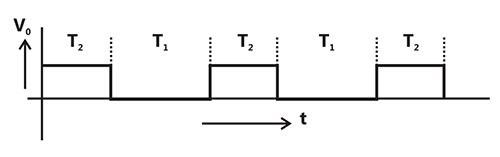

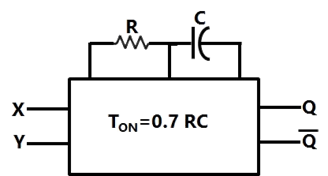

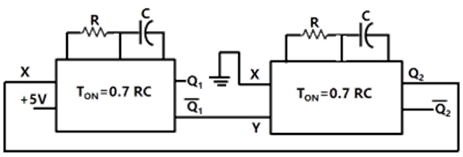

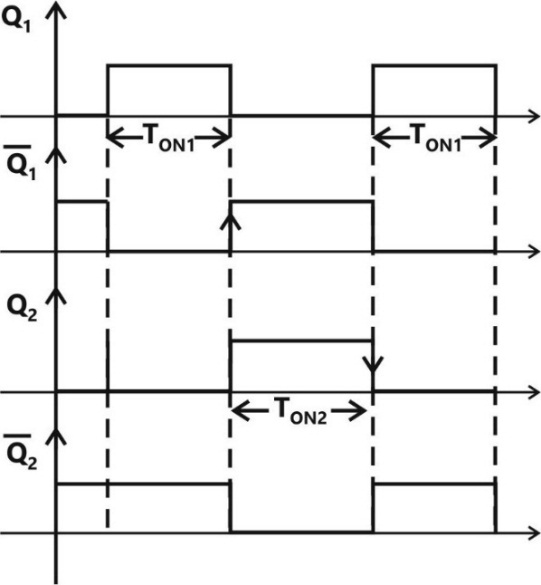

Two monoshot multivibrators, one positive edge triggered and another negative edge triggered are connected as shown in figure

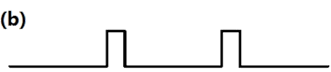

The monoshots and when triggered produce pulse of width and respectively. Where . The steady state output voltage of the circuit is

When M1 is on, it produces a pulse of width , during that time M2 is off & the output is ‘0’. As M1 output goes to zero, M2 is triggered & produces a pulse of width . When M2 turns OFF there is negative edge on Q2 and positive edge on . So, M1 is triggered again and again produces a pulse of width T1.

Output will be ON for time & OFF for time as shown below,

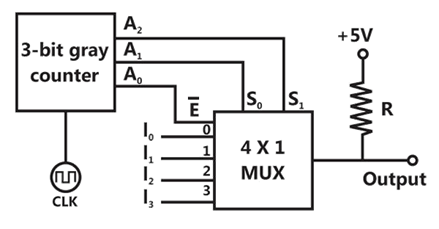

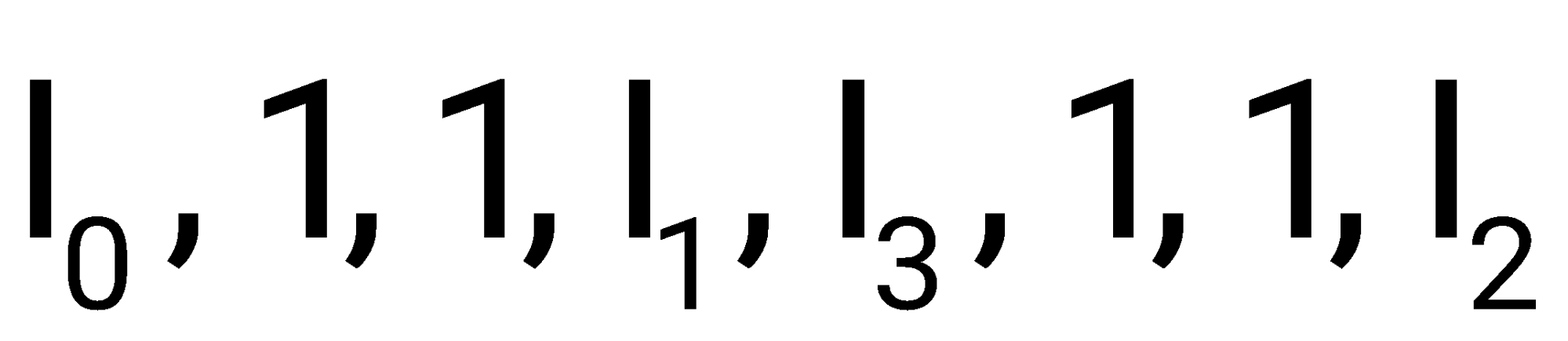

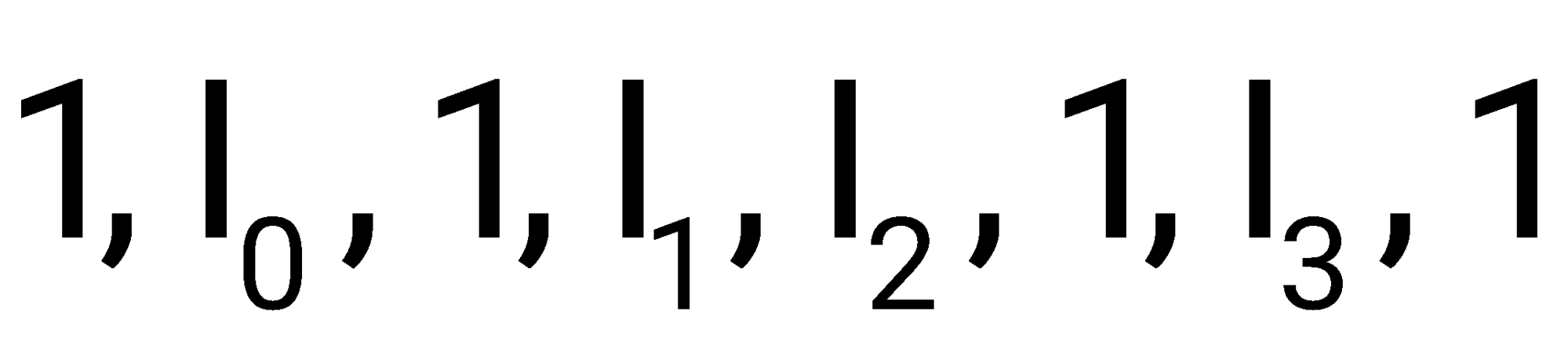

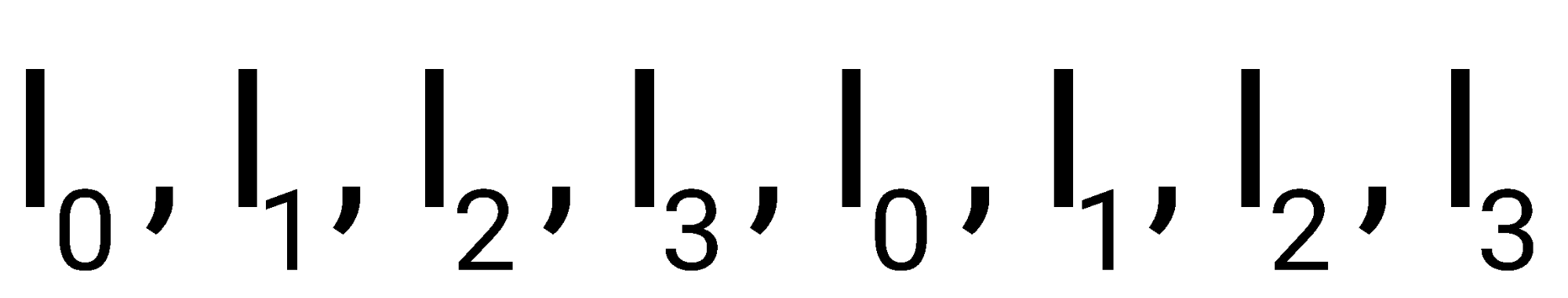

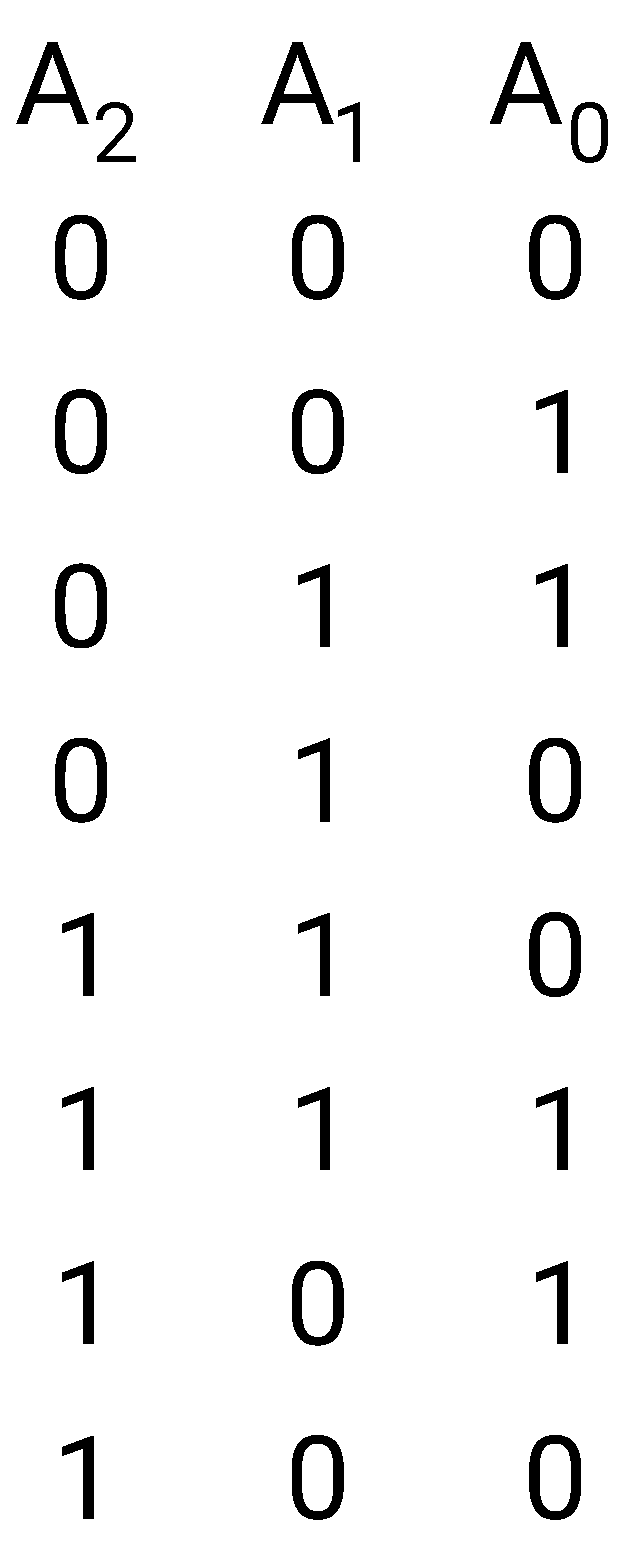

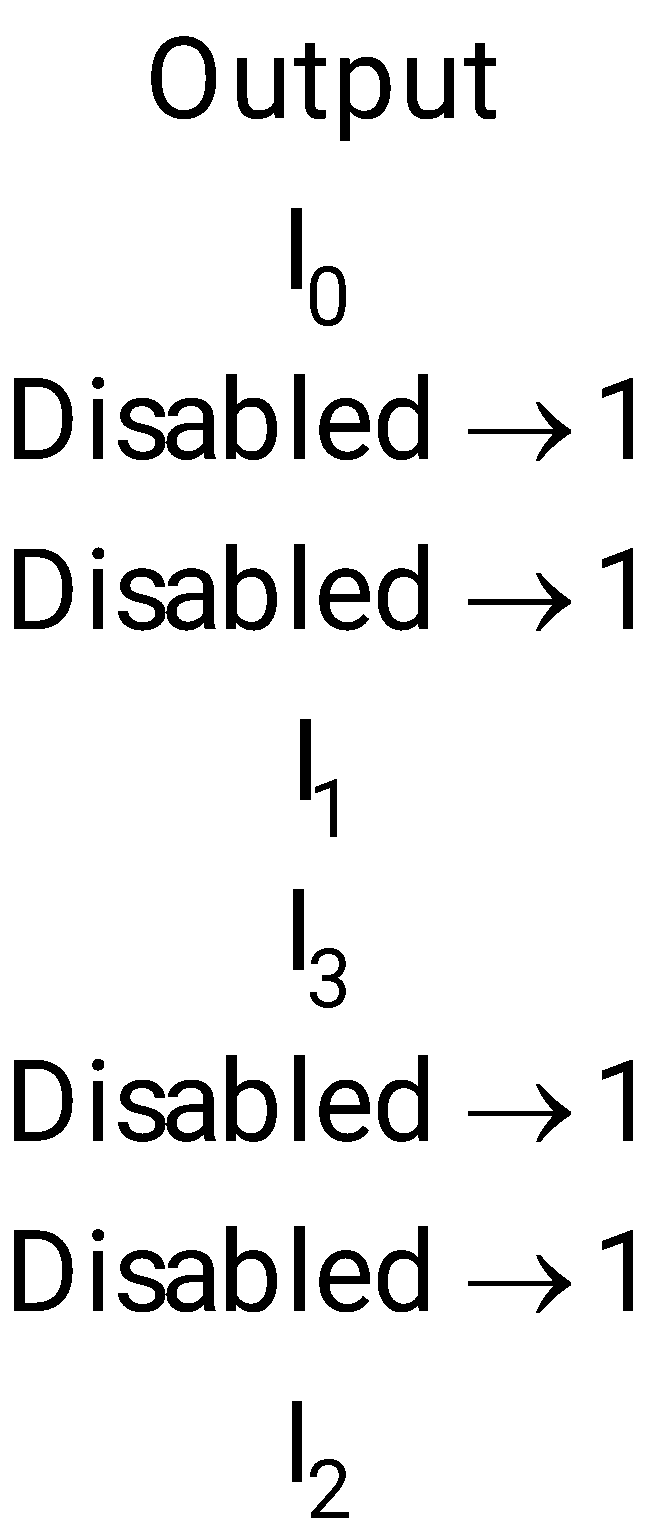

A 3-bit gray counter is used to control the output of the multiplexer as shown in the figure. The initial state of the counter is . The output is pulled high. The output of the circuit follows the sequence

The enable pin is marked as active LOW in the circuit given so whenever the input A0 is low the multiplexer will be disabled and the output will be pulled HIGH.

Counting sequence of gray code counter

Hence, the counting sequence is,

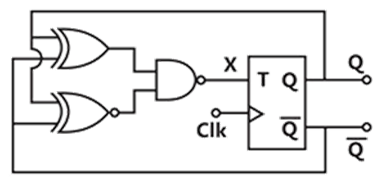

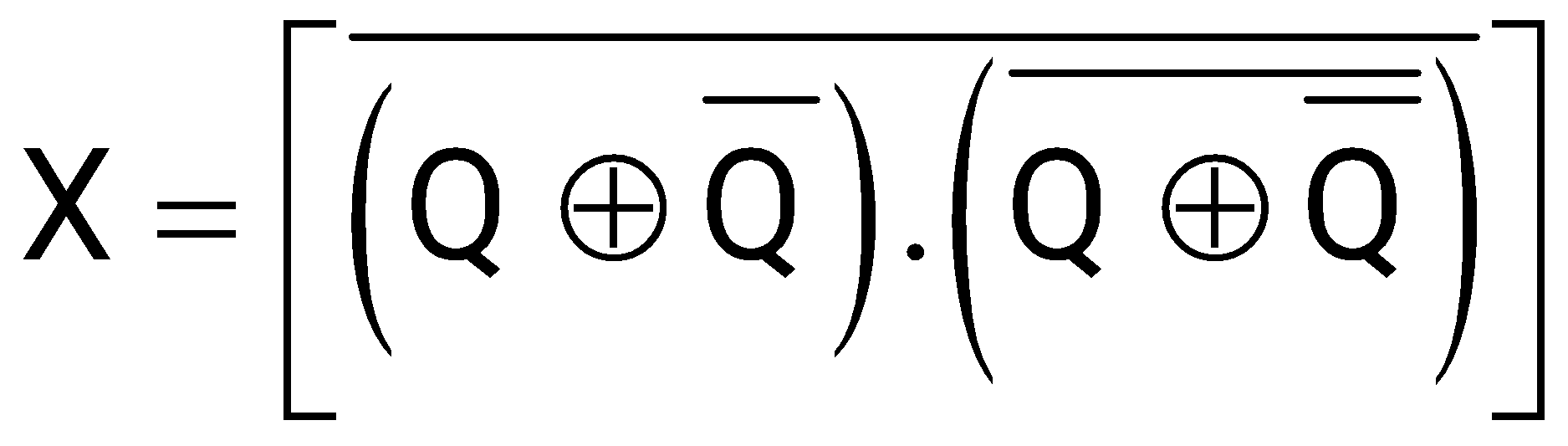

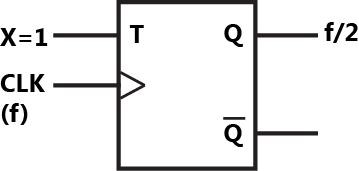

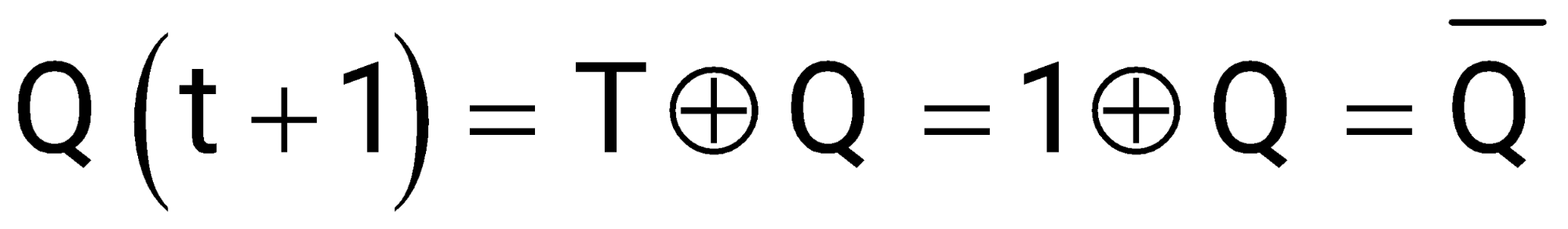

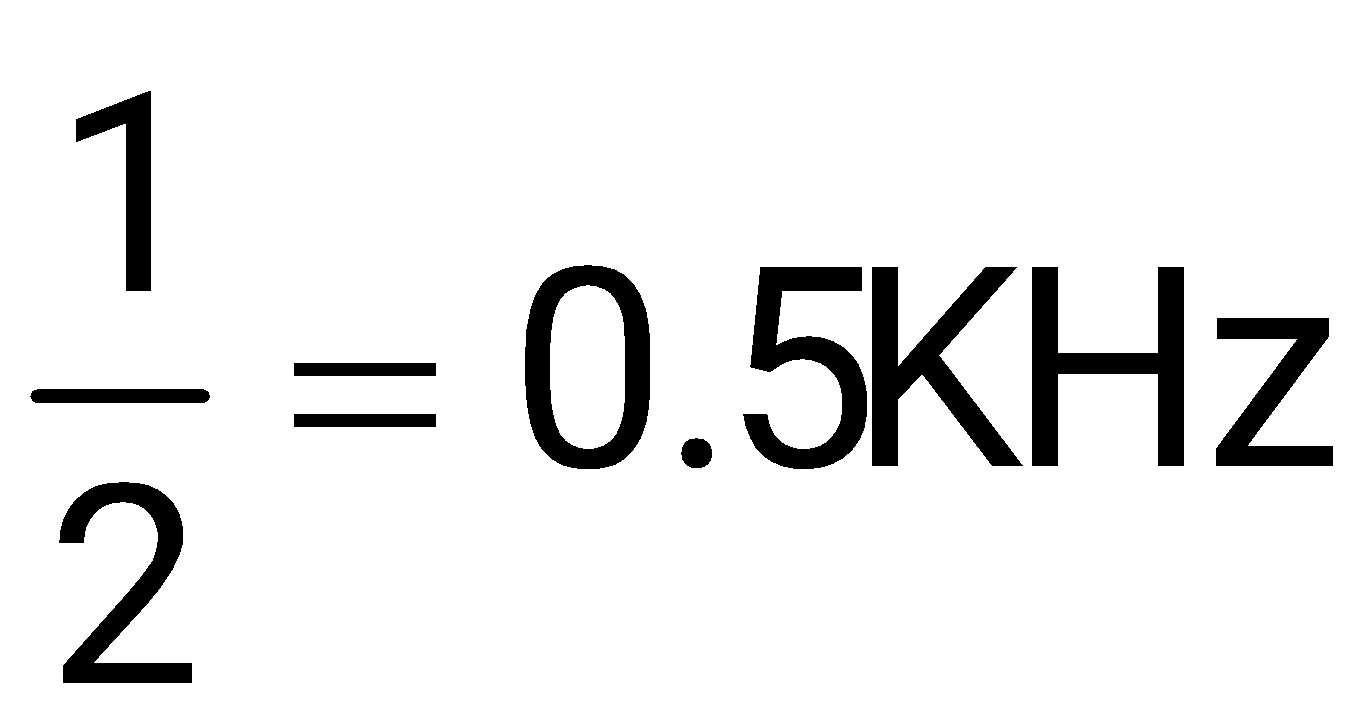

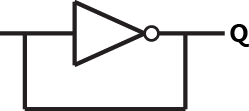

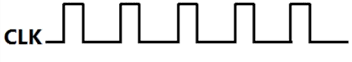

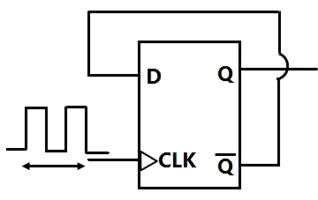

The clock frequency applied to the digital circuit shown in the figure below is 1 kHz. If the initial state of the output Q of the flip-flop is 0, then the frequency of the output waveform Q in kHz is

As we can see that

We know that

So, X=1

Now, the given sequential circuit can be reduced as

This is a toggle mode i.e.

So frequency of the output waveform Q is

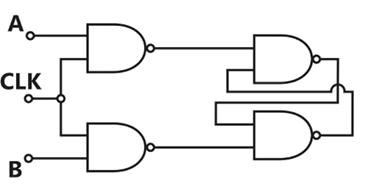

Consider the given circuit,

In this circuit, the race around

Given circuit is a S-R flip flop

Race around condition does not occur in S-R flip flop.

It occurs only in JK flip flop with J=K=1 also clock=1

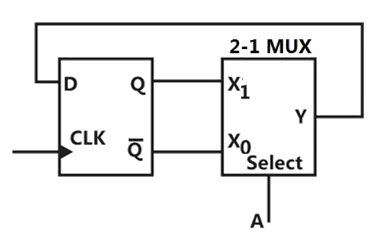

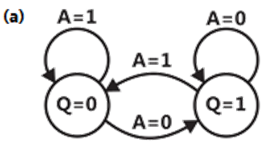

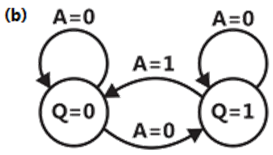

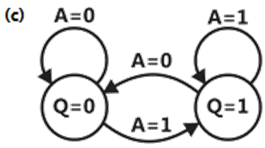

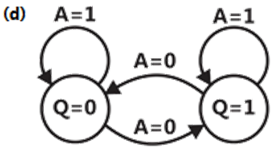

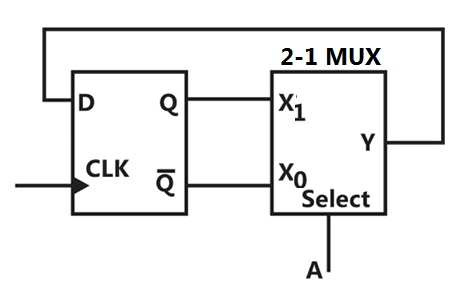

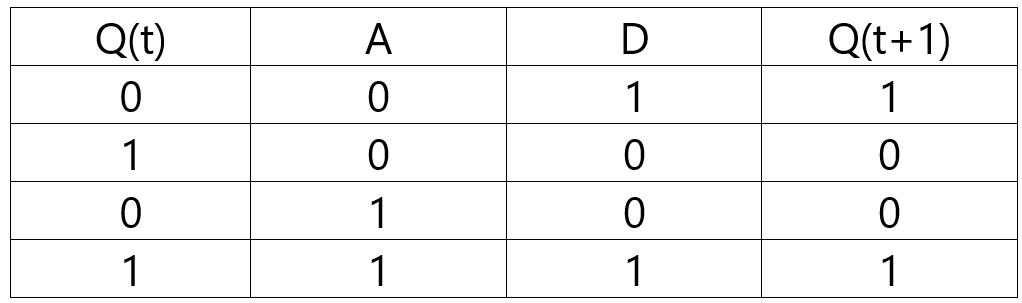

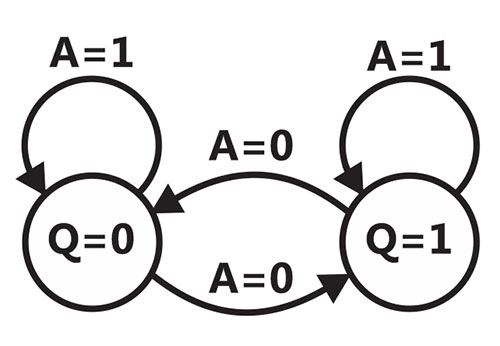

The state transition diagram for the logic circuit shown is

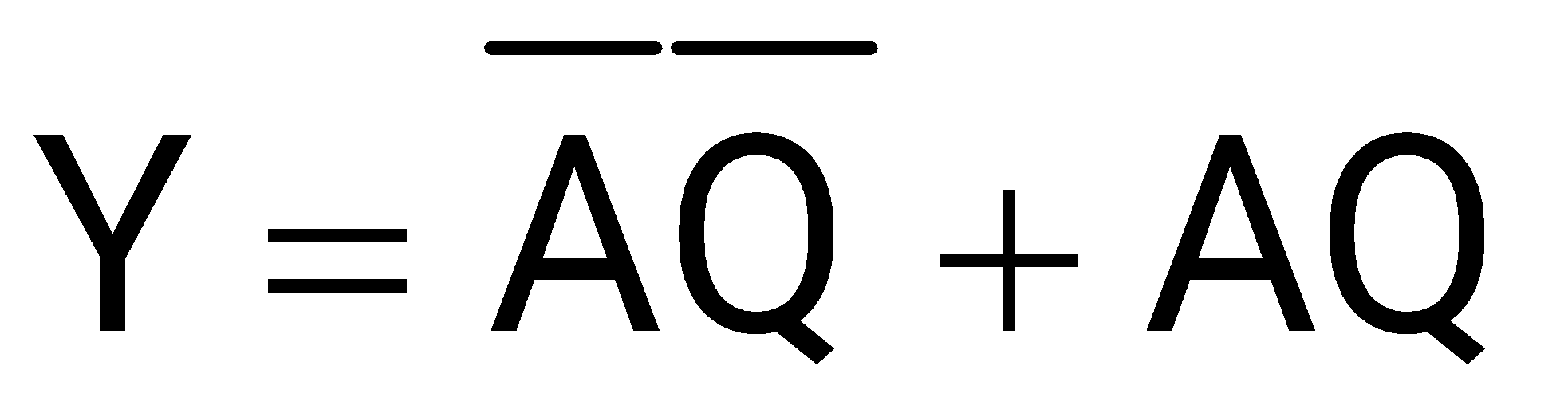

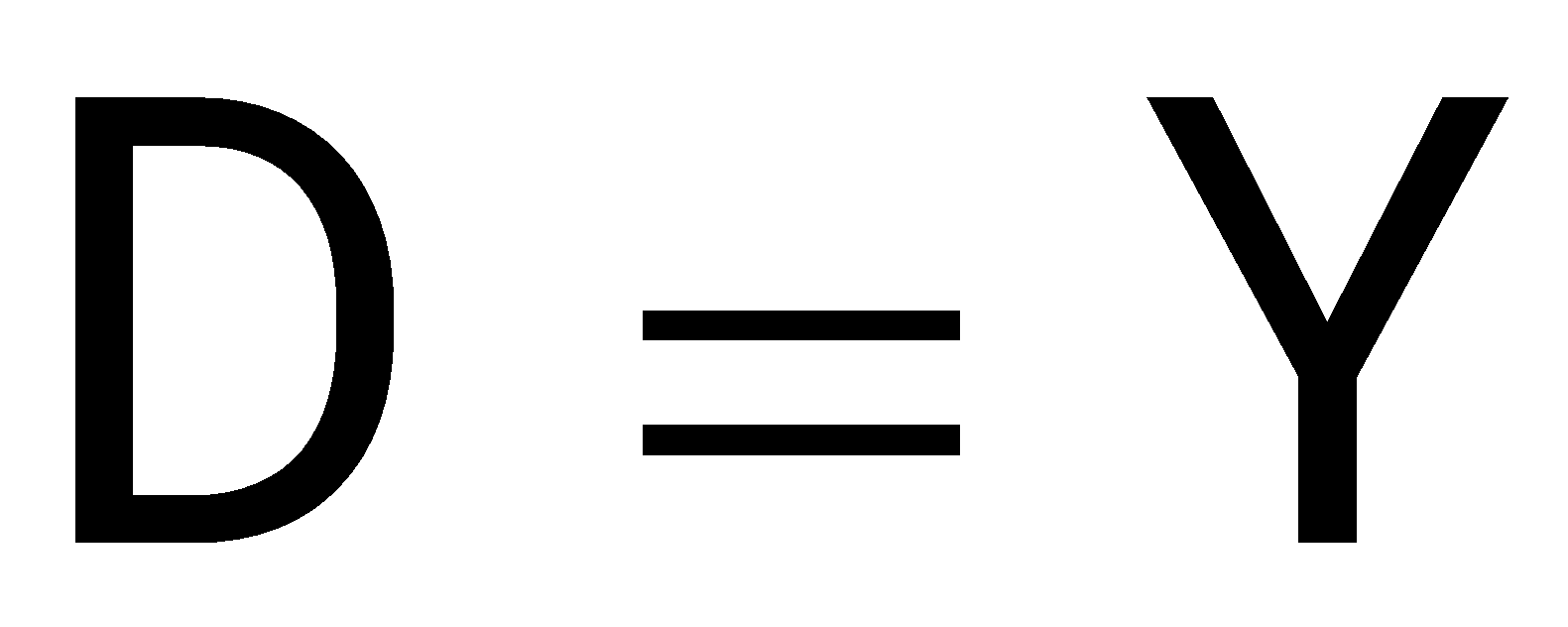

For 2-1 Mux

And

Characteristic equation for D flip flop

So, state transition diagram of given logic circuit

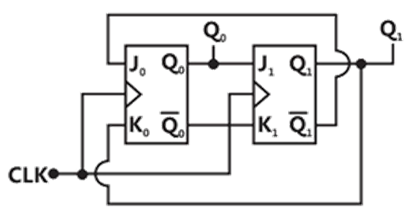

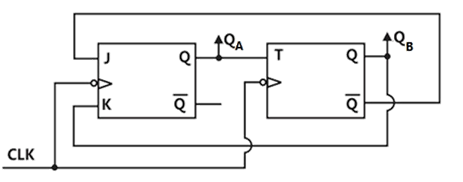

two-bit counter circuit is shown below.

If the state of the counter at the clock time is “10” then the state of the counter at (after three clock cycles) will be

Excitation Table

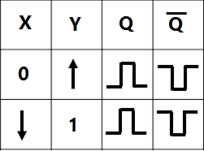

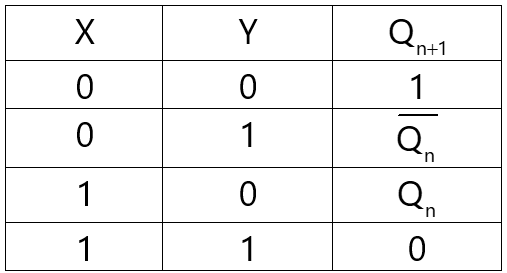

The truth table of a monoshot shown in the figure is given in the table below:

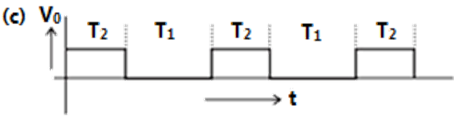

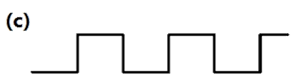

Two monoshots, one positive edge triggered and other negative edge triggered, are connected as shown in the figure. The pulse widths of the two monoshot outputs, , and , are and , respectively.

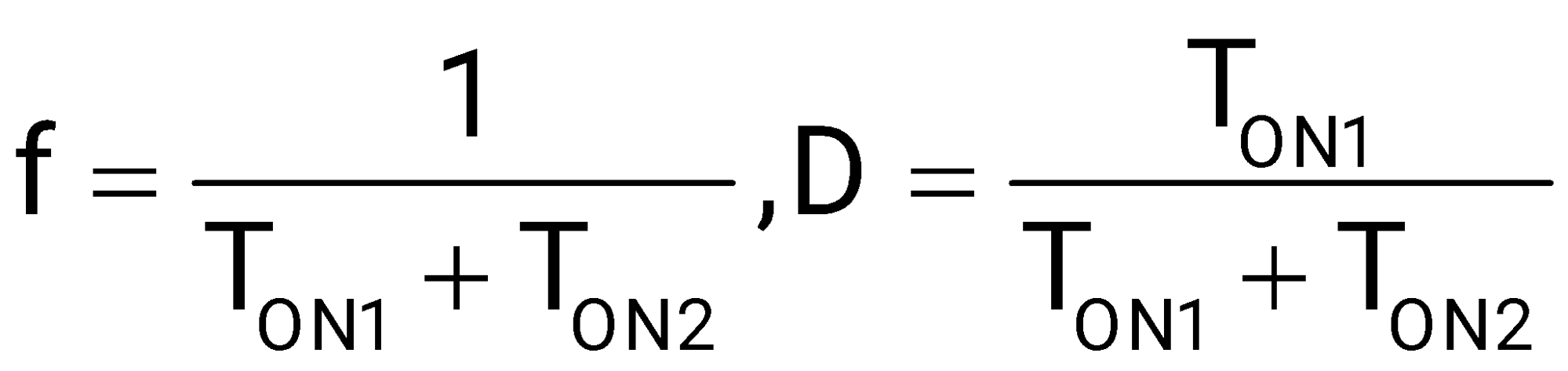

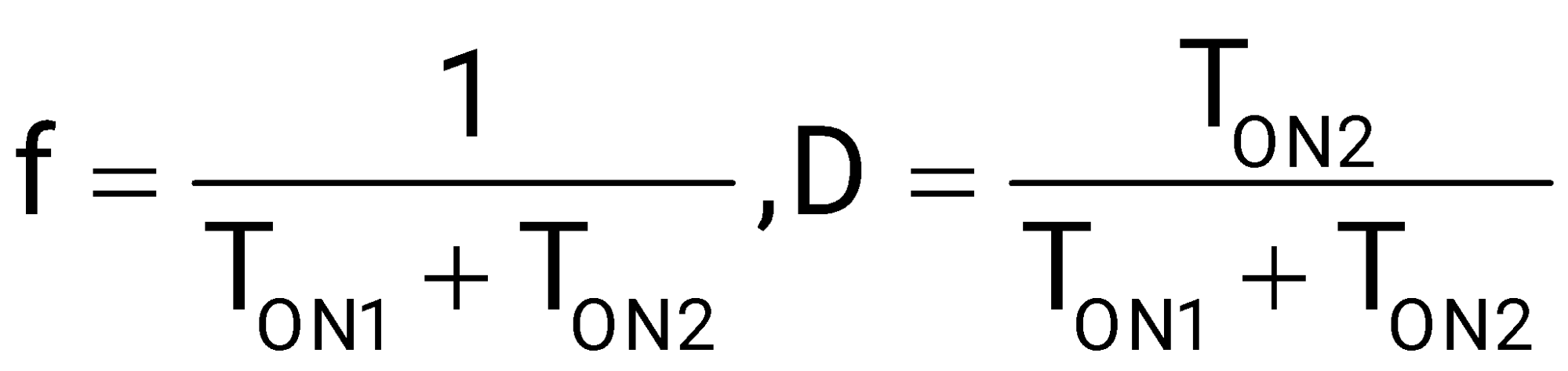

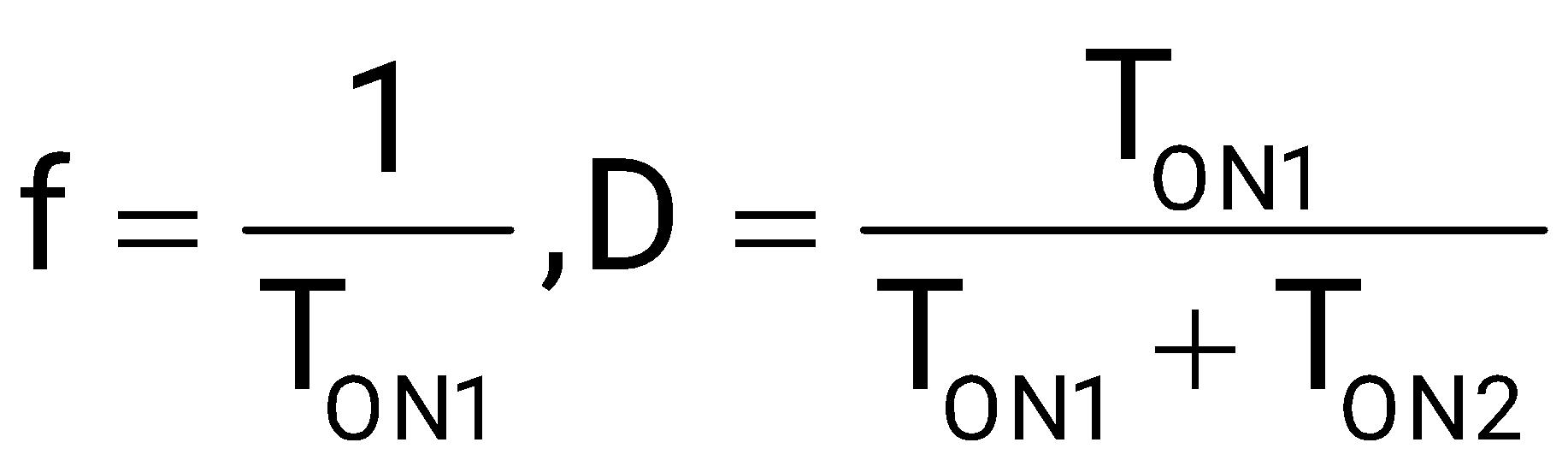

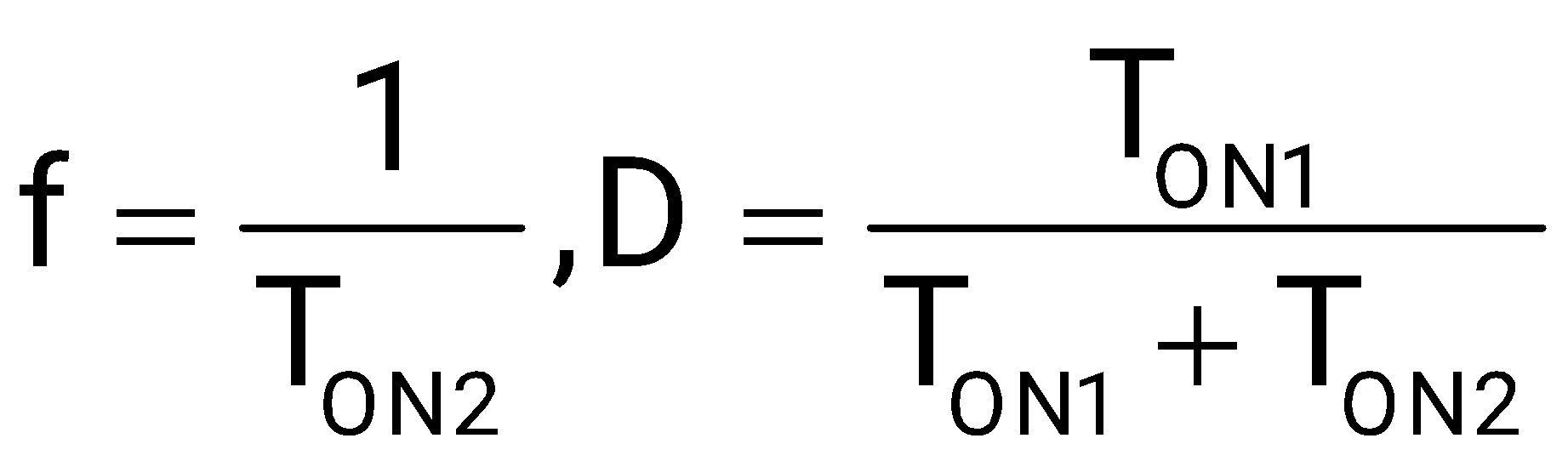

The frequency and the duty cycle of the signal at Q1 will respectively be

In the first monoshot,

Y = 1, so it will be triggered at negative edge of X = Q2

In second monoshot,

X = 0, so it will be triggered at positive edge of Y =

The waveforms for the outputs of two monoshots are shown below,

From the waveform, time period of Q1,

T = TON1 + TON2, f =

Duty cycle, D =

The digital circuit shown in figure works as a

Characteristic equation

Excitation Table

Hence the circuit works as T Flip flop

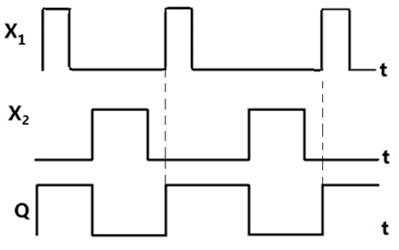

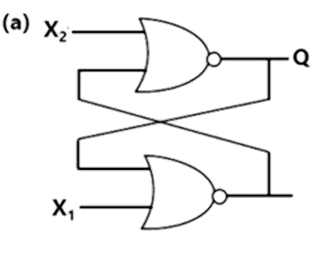

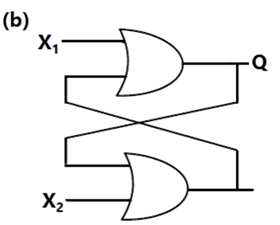

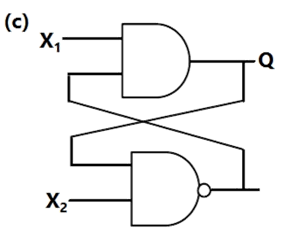

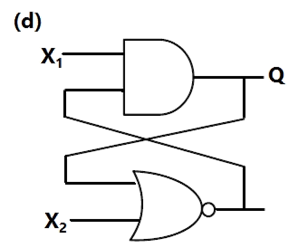

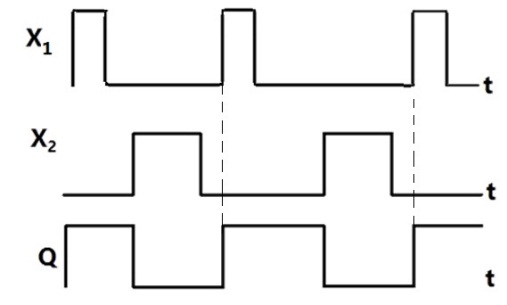

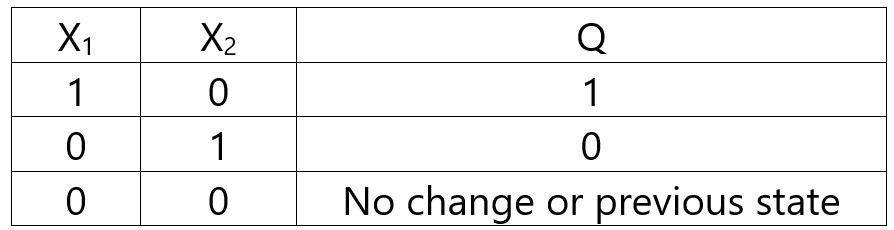

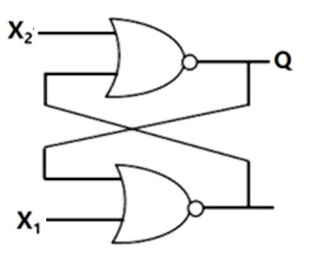

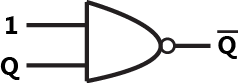

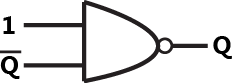

Select the circuit, which will produce the given output Q for the input signals X1 and X2 given in Figure.

Truth Table

It is similar to SR latch using NOR gate

In figure, as long as and , the output Q remains

This circuit behaves like

So, Q is unstable

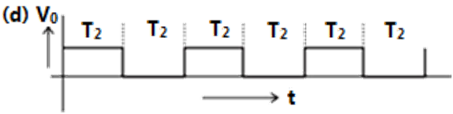

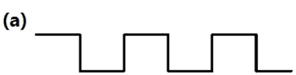

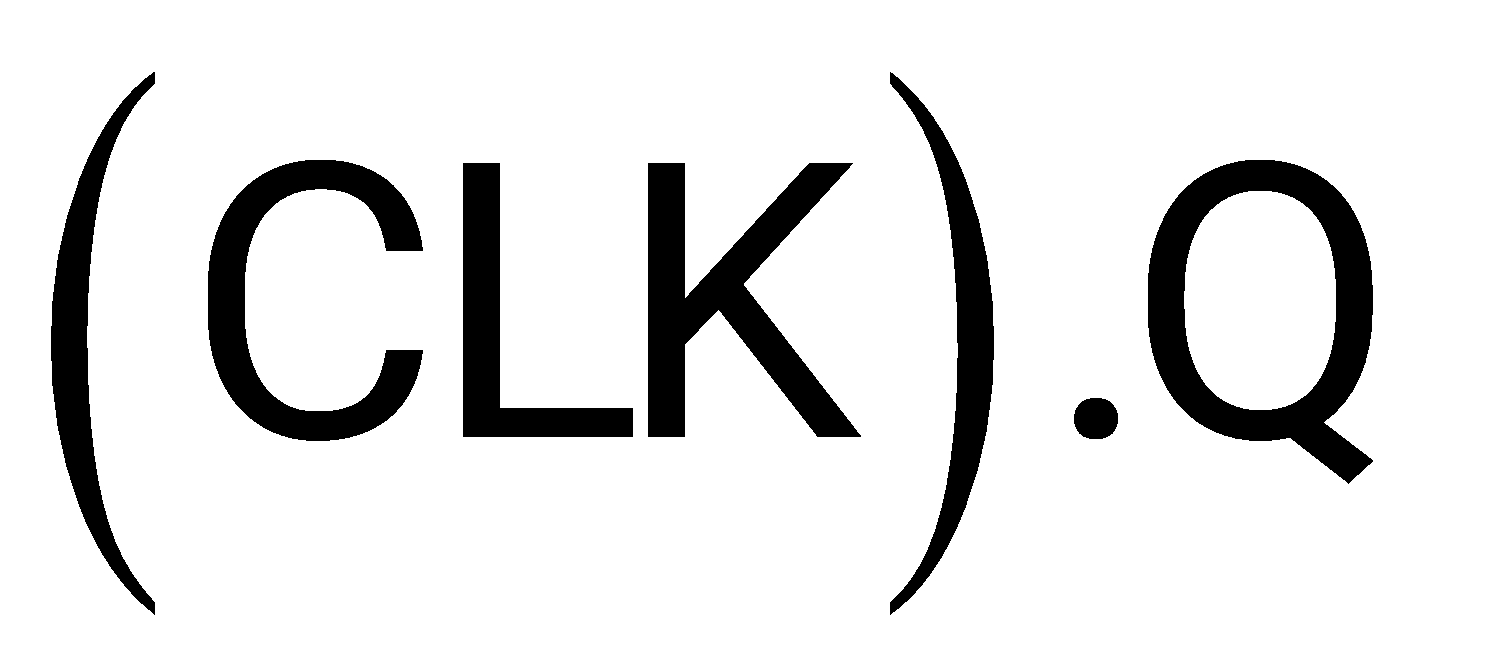

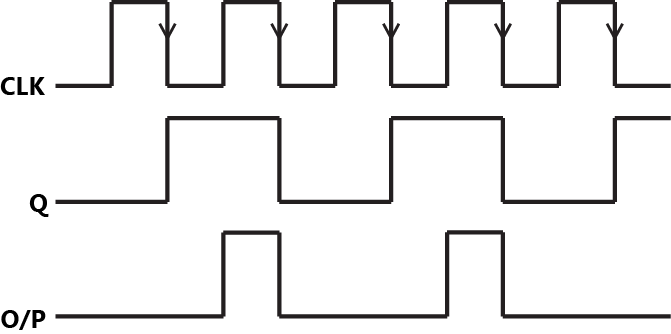

The digital circuit shown in figure generates a modified clock pulse at the output. Choose the correct output waveform form the options given below.

The J-K flip flop is in toggle mode & it is negative edge triggered

So output changes at negative edge.

Output =

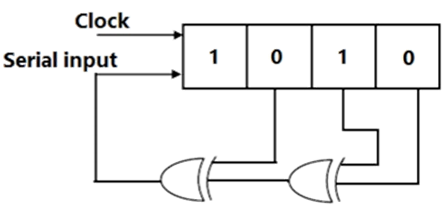

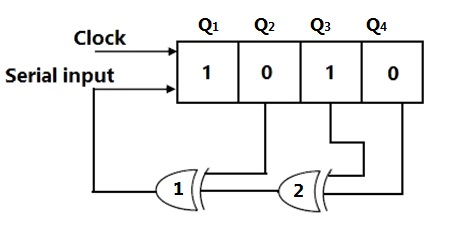

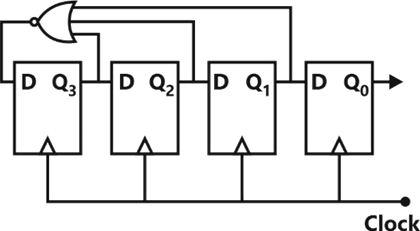

The shift register shown in Figure is initially loaded with the bit pattern 1010. Subsequently the shift register is clocked, and with each clock pulse the pattern gets shifted by one bit position to the right. With each shift, the bit at the serial input is pushed to the left most position (MSB). After how many clock pulses will the content of the shift register become 1010 again?

Output of Gate 2=

Output of Gate 1=

Truth Table

Total number of clock pulse=7

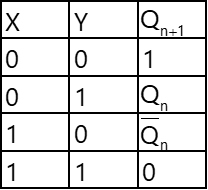

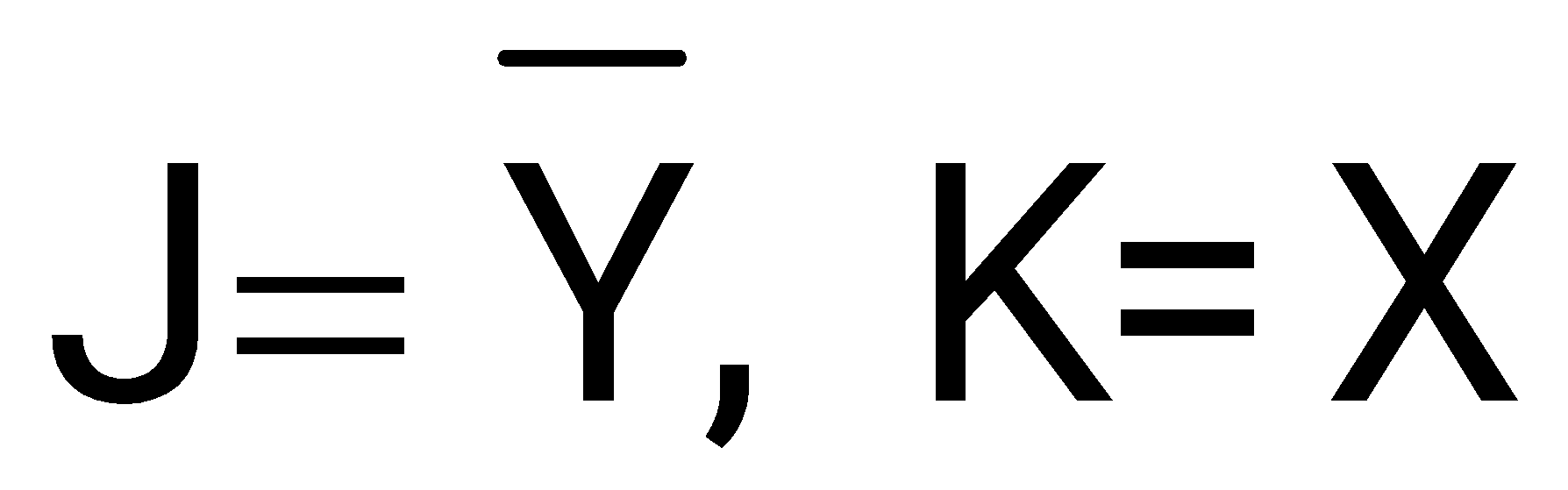

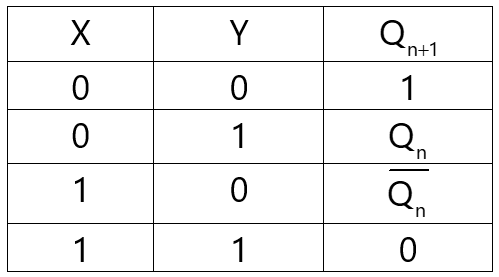

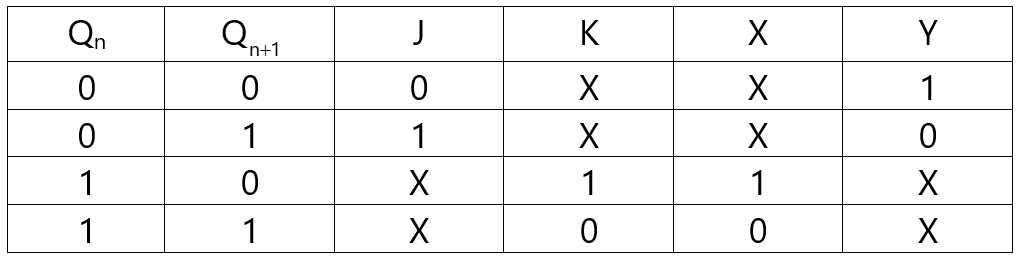

An X-Y flip flop, whose Characteristic Table is given below is to be implemented using a J-K flip flop

This can be done by making

J-K flip flop Truth table:

Given Truth table

Excitation Table

Similarly we can get ;

The frequency of the clock signal applied to the rising edge triggered D flip-flop shown in figure is 10 kHz. The frequency of the signal available at Q is

Characteristic equation

The given D Flip flop is in toggle mode

So, output frequency

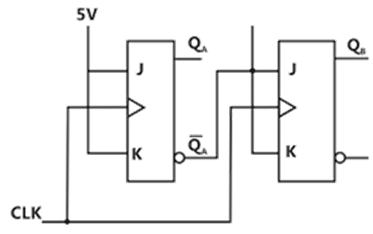

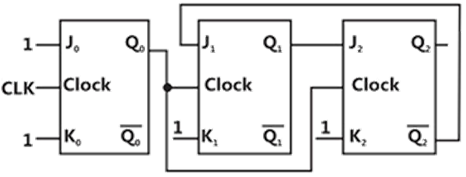

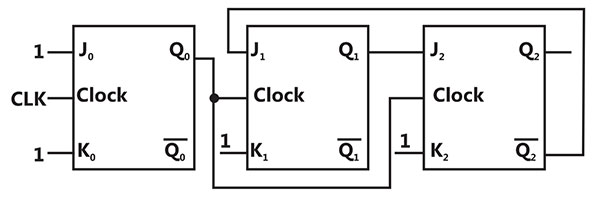

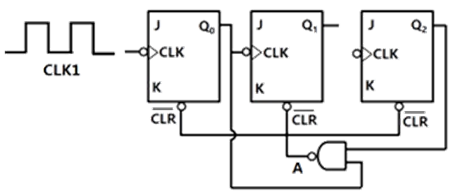

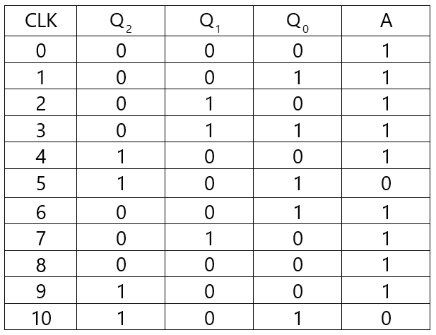

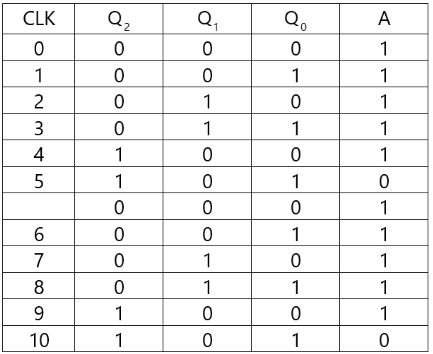

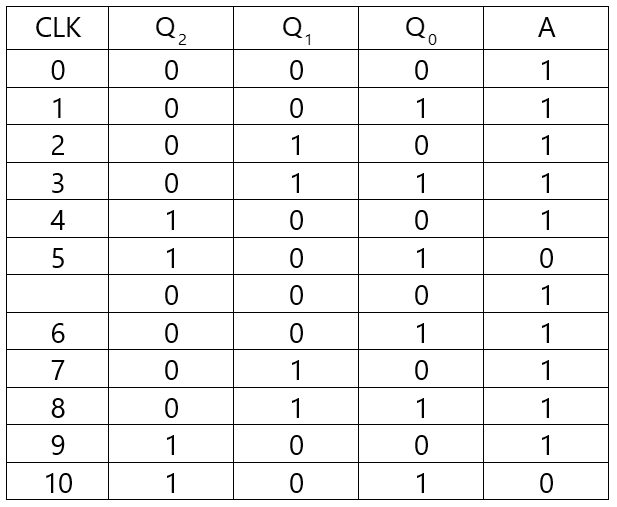

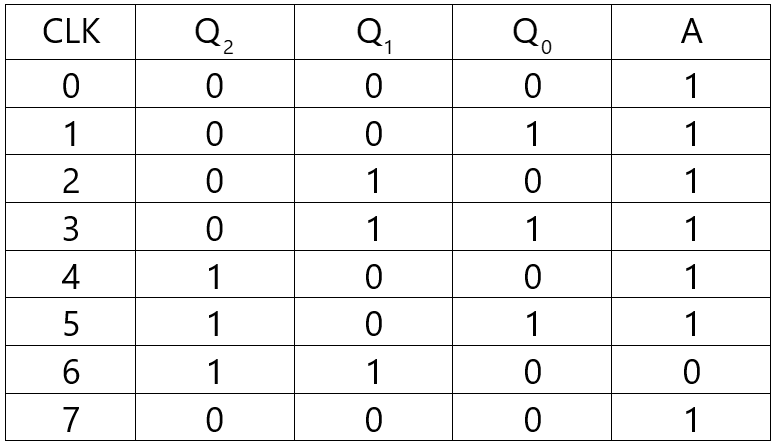

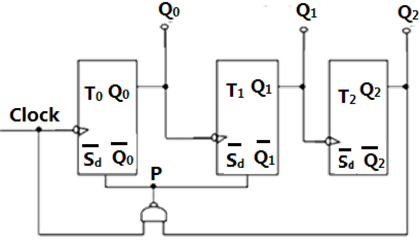

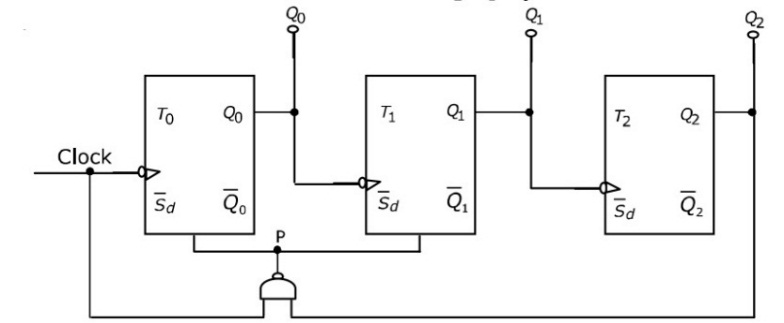

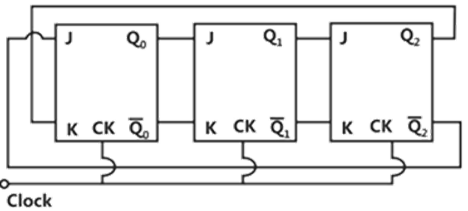

The ripple counter shown in figure is made up negative edge triggered J-K flips flops. The signal levels at J and K inputs of all the flip-flops are maintained at logic 1. Assume that all outputs are cleared just prior to applying the clock signal.

(a) Create a table of Q0, Q1, Q2 and A in the format given below for 10 successive input cycles of the clock CLK1.

(b) Determine the module number of the counter.

(c) Modify the circuit of given figure to create a module-6 counter using the same components used in the figure.

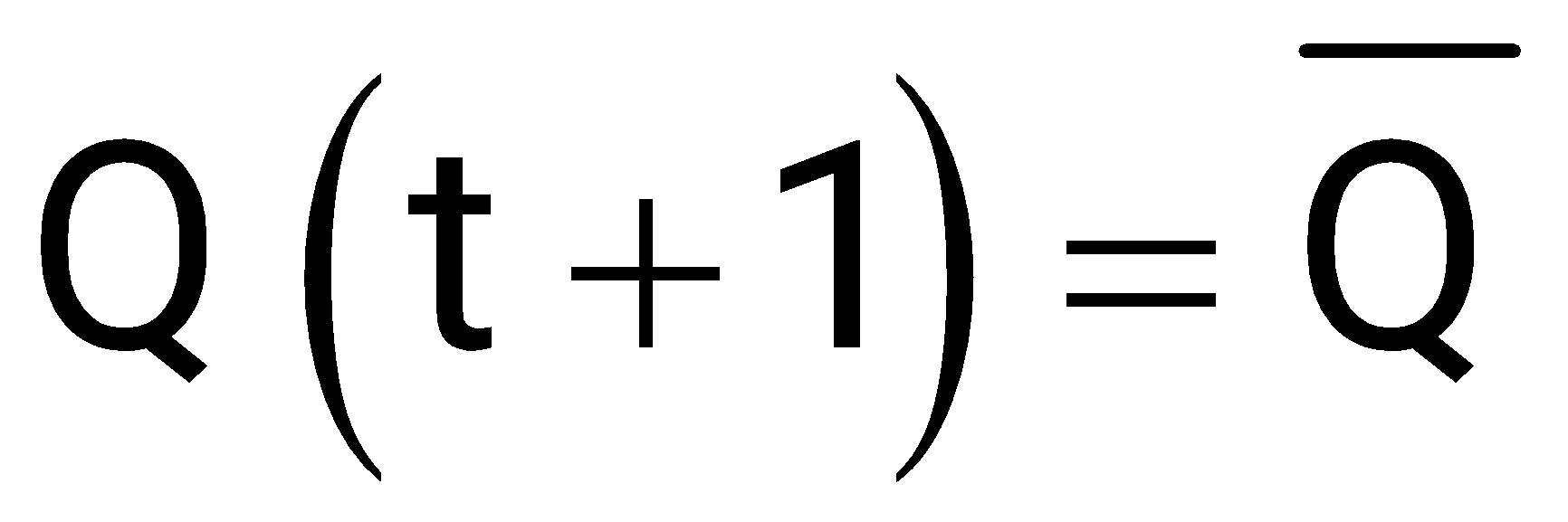

Given all the flip flops are negative edge triggered and in toggle mode. [J=1, K=1 Q (n+1)=

Q1 Toggles whenever Q0 changes from 1 to 0 and similarly Q2 Toggles whenever Q1 changes

from 1 to 0.

Output of the NAND gate A

When both Q2 and Q0 are logic 1 then only all the three J-K flip flops will be clear i.e. Q=0

Truth Table:

(b) The given circuit is a Mod-5 counter

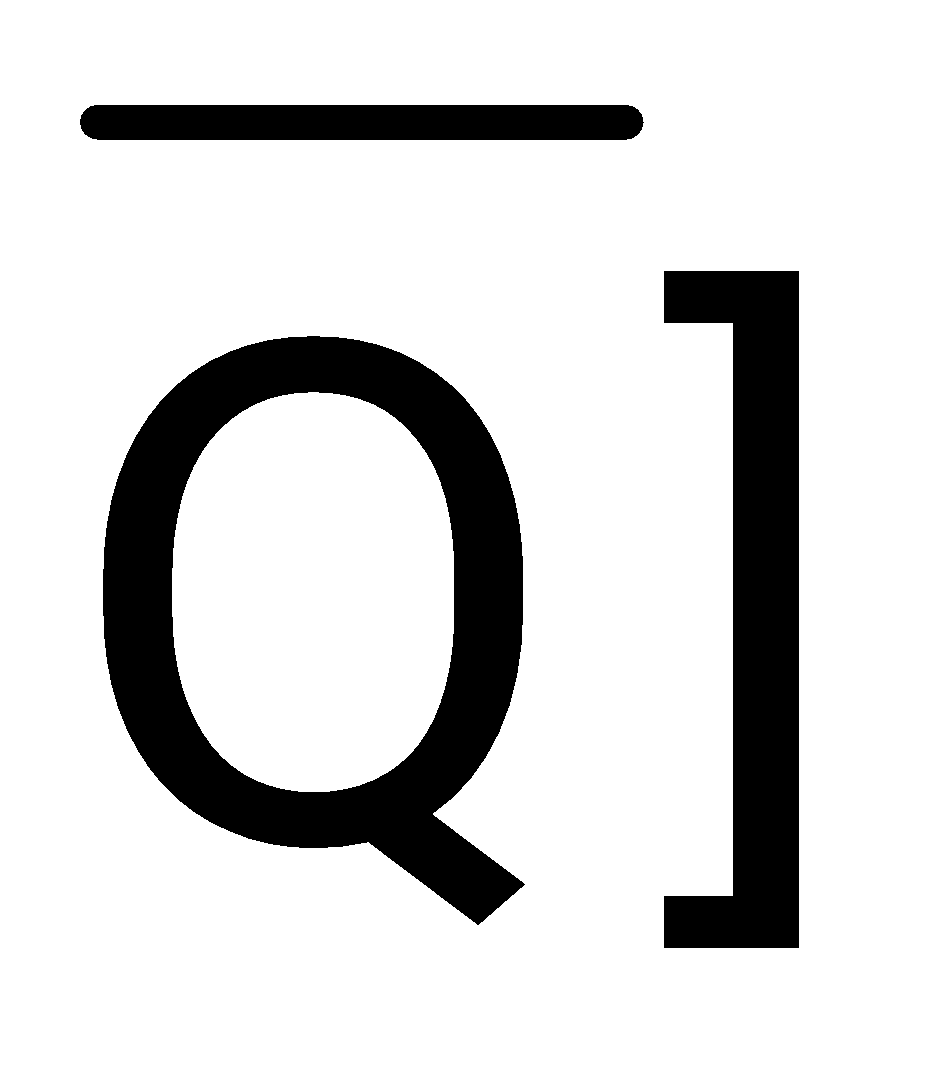

(c) The NAND gate input should be changed to instead of .

i.e. A

Truth Table:

Now it is a MOD 6 counter

For the ring counter shown in figure, find the steady state sequence if the initial state of the counters is 1110 (i.e., Q3, Q2, Q1, Q0 = 1110). Determine the MOD number of the counter.

Characteristic equation

Truth Table

So the given ring counter is a Mod-4 counter

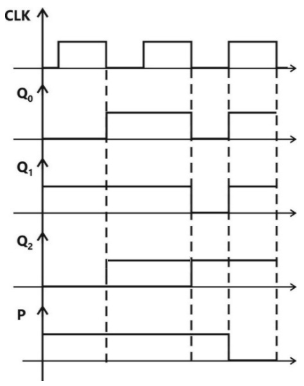

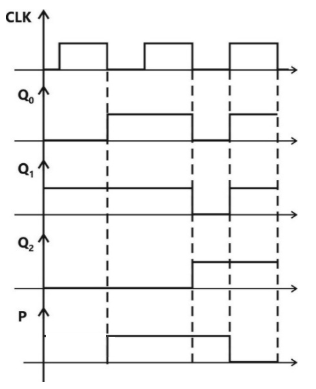

The counter shown in the figure, is initially in state . With reference to the CLK input, draw waveforms for and P for the next three CLK cycles.

The preset input to Q0 & Q1 flip flop is such that flip flop will be set when clock & Q2 will be high or logic ‘1’.

The waveforms for the output are shown below assuming that all the Toggle inputs are high.

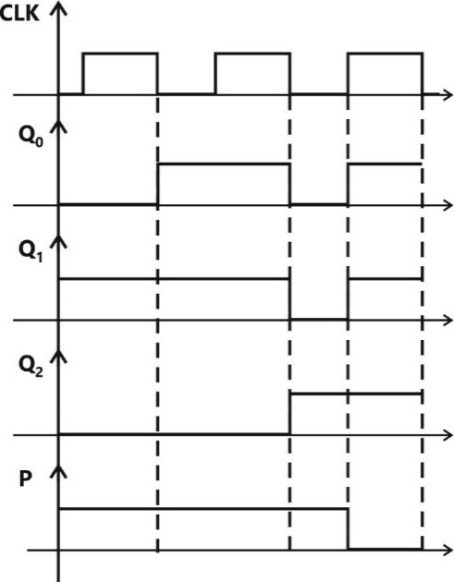

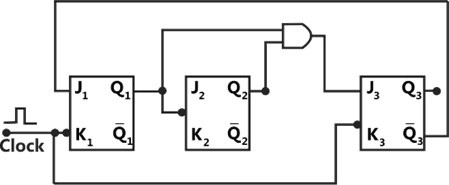

(a) Construct the truth table for the circuit given. are outputs and the clock pulses are the inputs. Unused J, K inputs are assumed to be at logic 1. All flip-flops are rest at power ON.

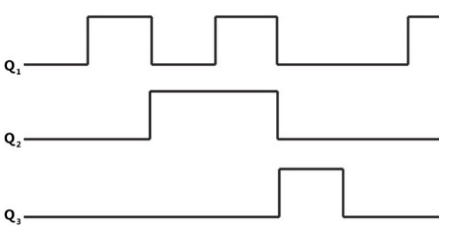

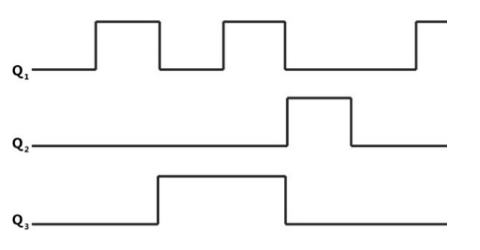

(b) Sketch the output waveforms at

(c) What function does this circuit perform?

(a)

Flip flop 1 and 3 are in synchronous mode, Flip flop 2 is in Asynchronous mode, Q2 Toggles whenever Q1 changes from 1 to 0. Assuming negative edge triggering.

Truth table:

(b)

(c) It is a MOD-5 counter.

For a J-K flip-flop its J input is tied to its own output and its K input is connected to its own Q output. If the flip-flop is fed with a clock of frequency 1MHz, its Q output frequency will be _________________

Characteristic equation for this configuration

Given

Hence J-K flip-flop in the given configuration keeps toggling for every rising edge of the clock pulse.

So output frequency is=

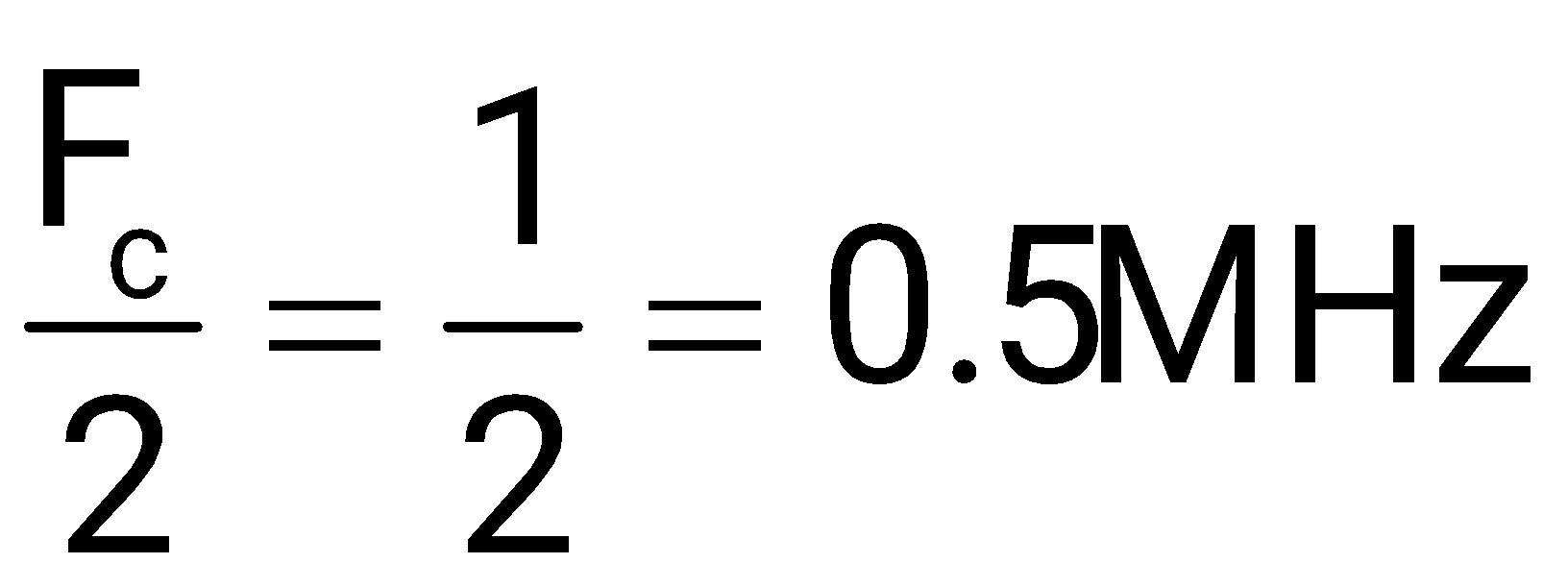

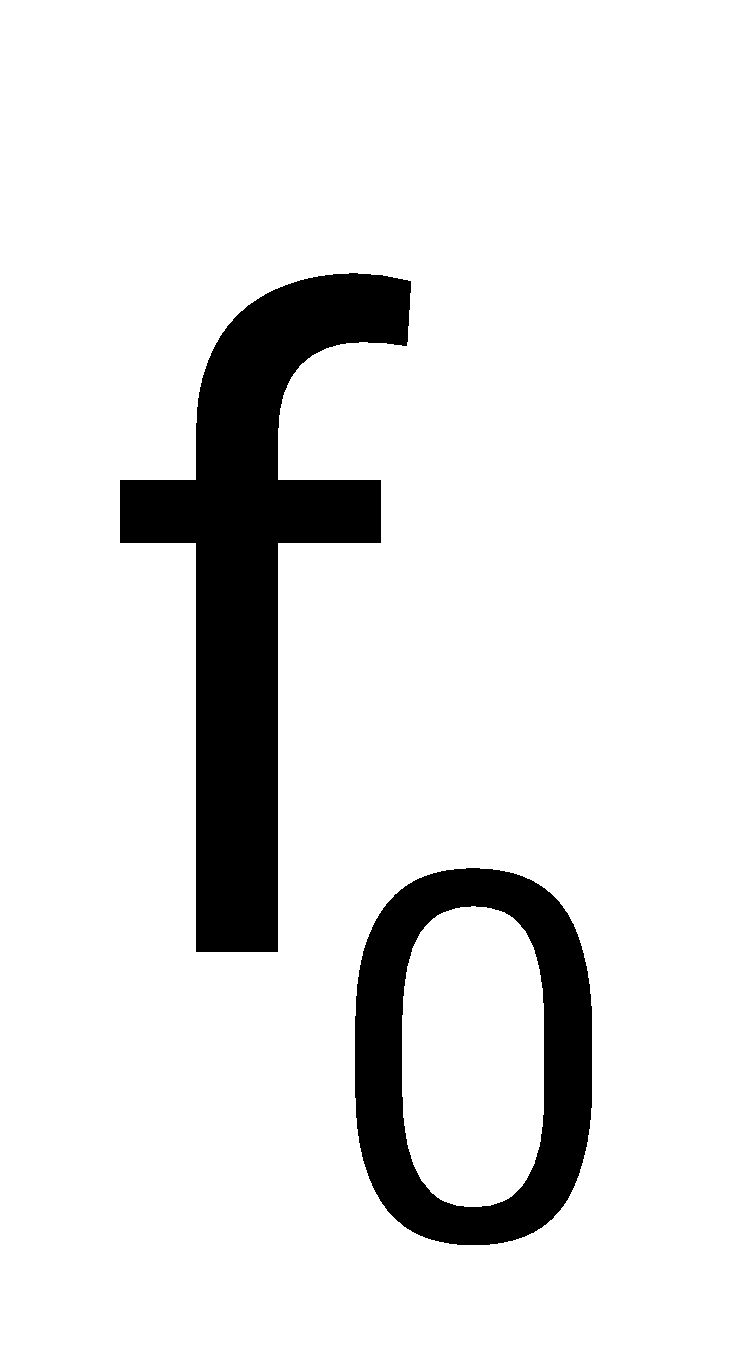

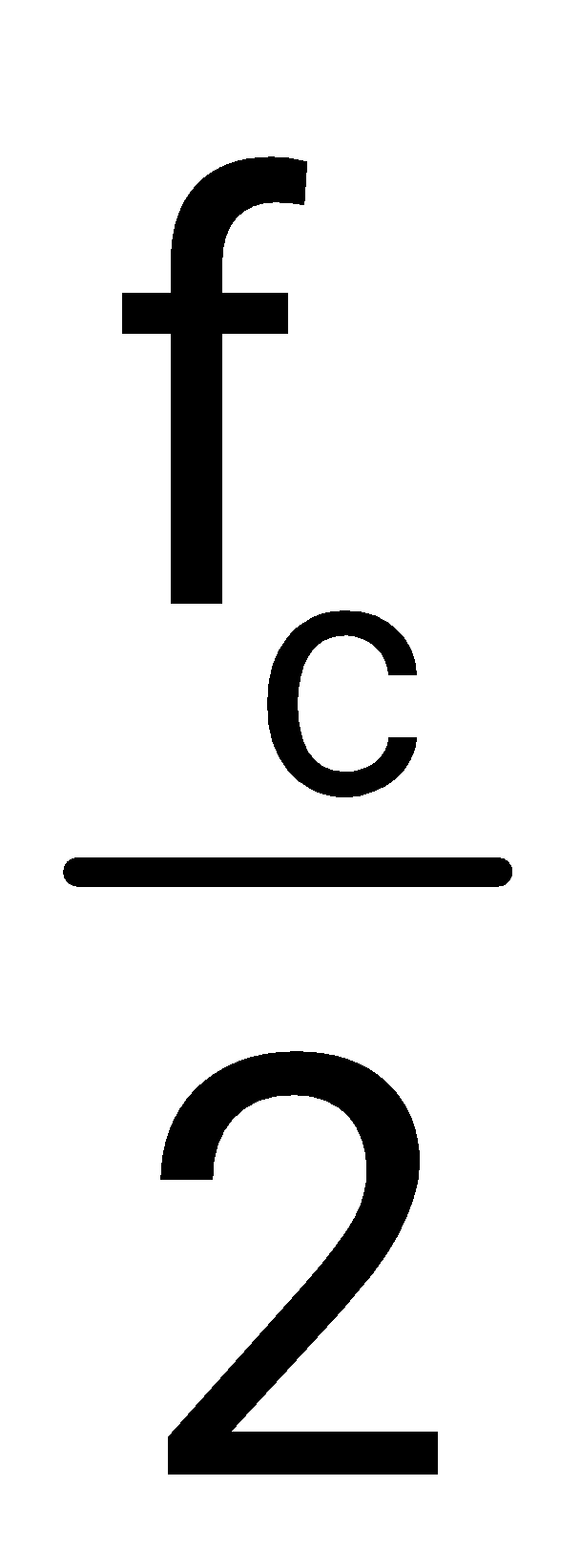

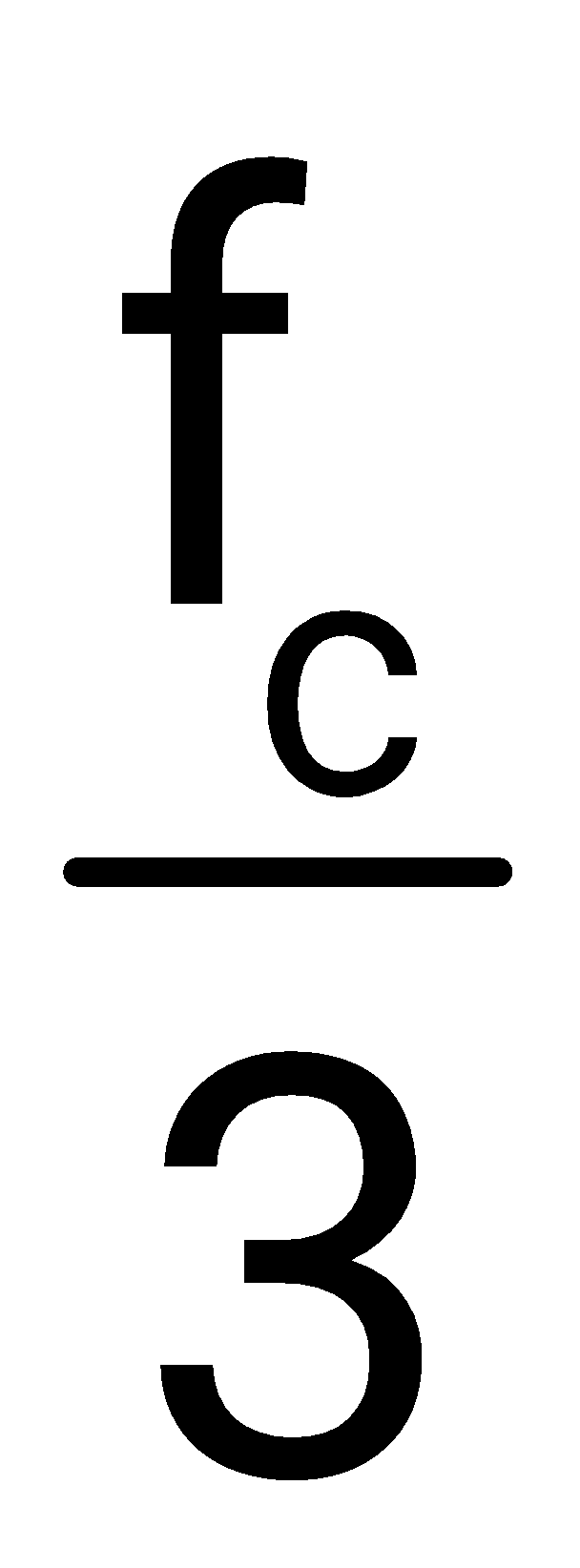

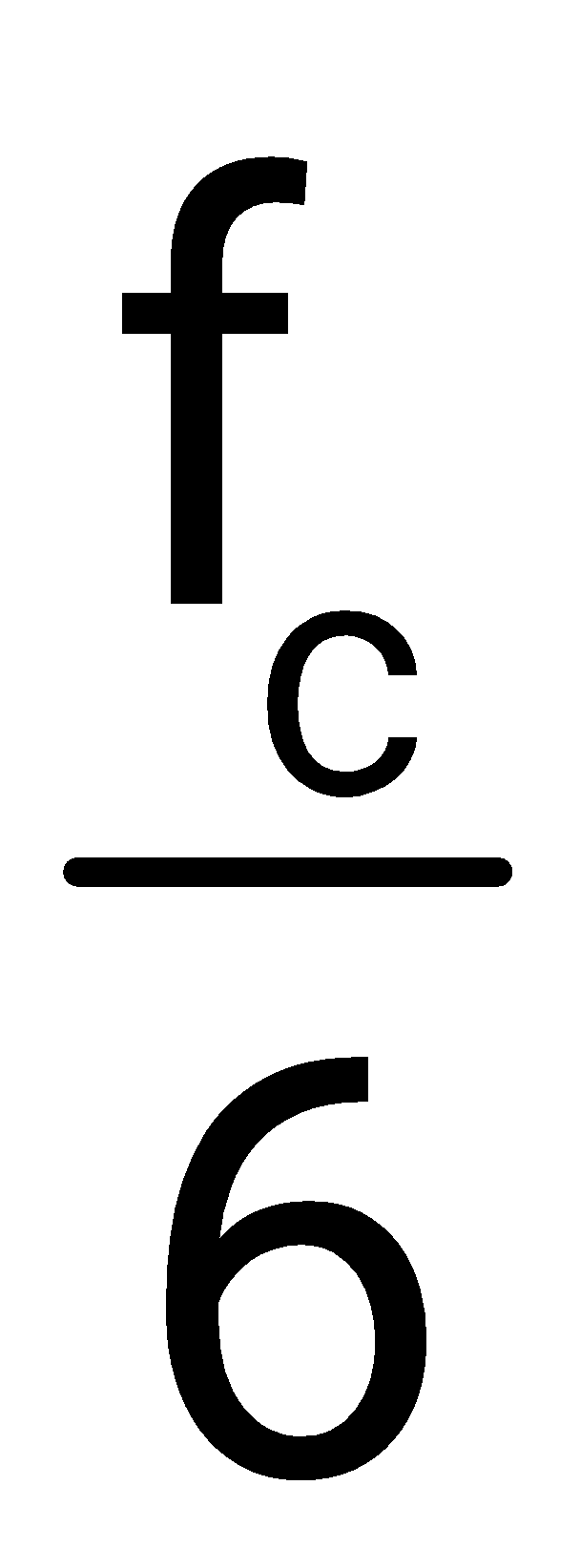

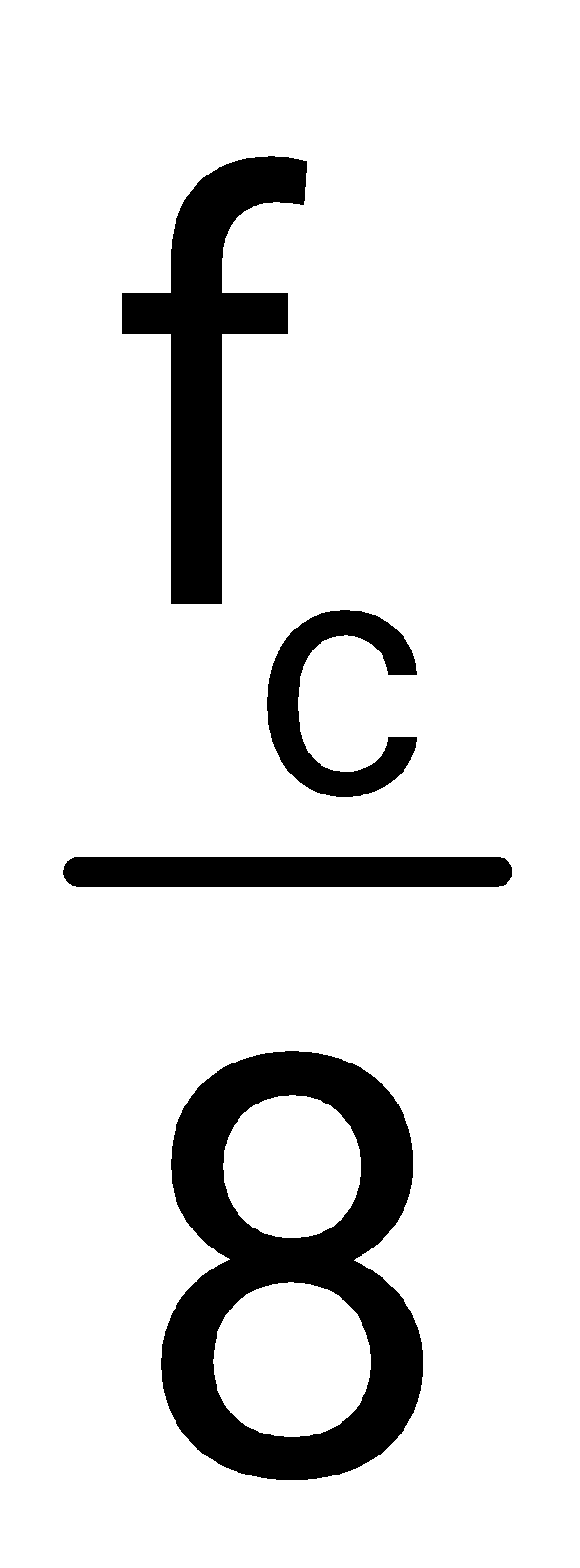

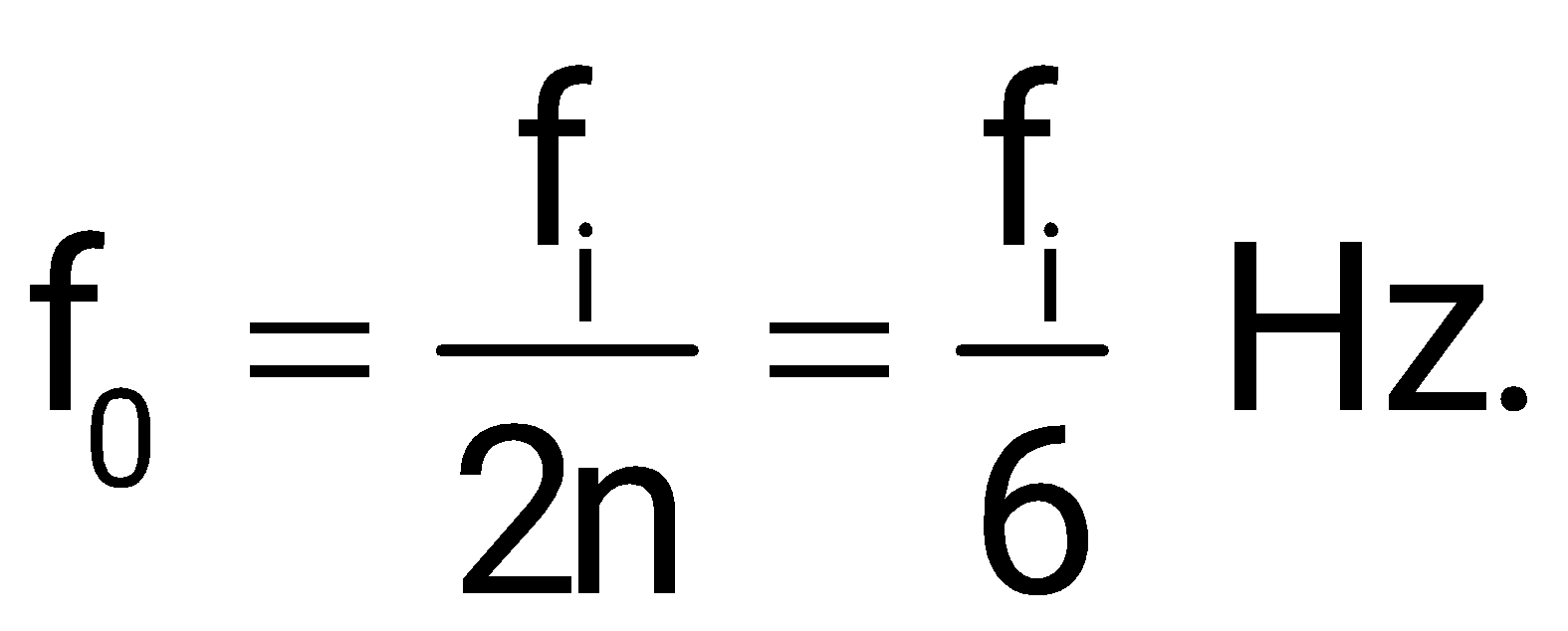

The three stage Johnson ring counter shown in figure is clock at a constant frequency of from the starting stage of . The frequency of outputs will be

Each output of a n stage Johnson ring counter has same output frequency given by,

Where n is the number of Flip-flops.