Network Analysis

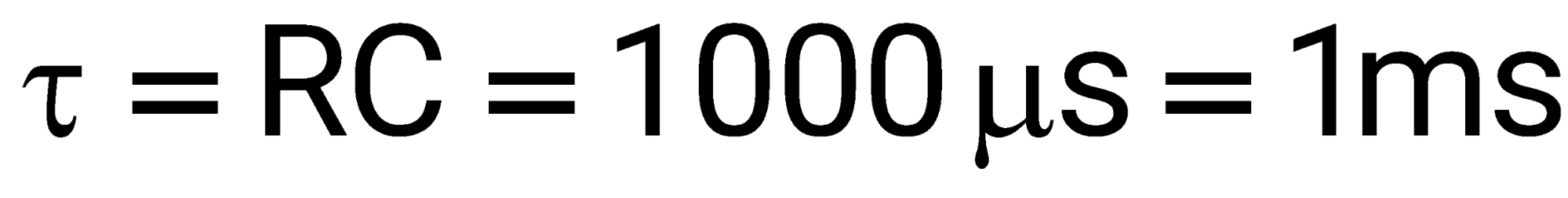

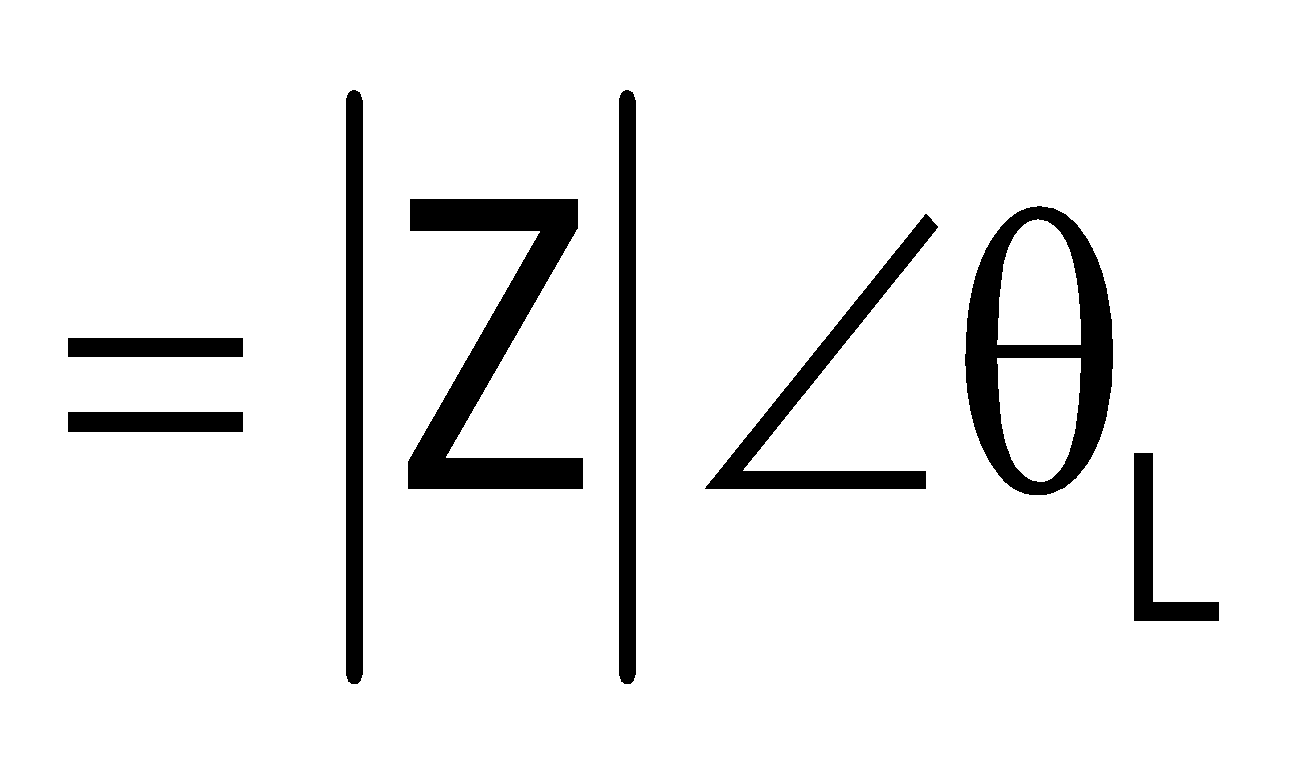

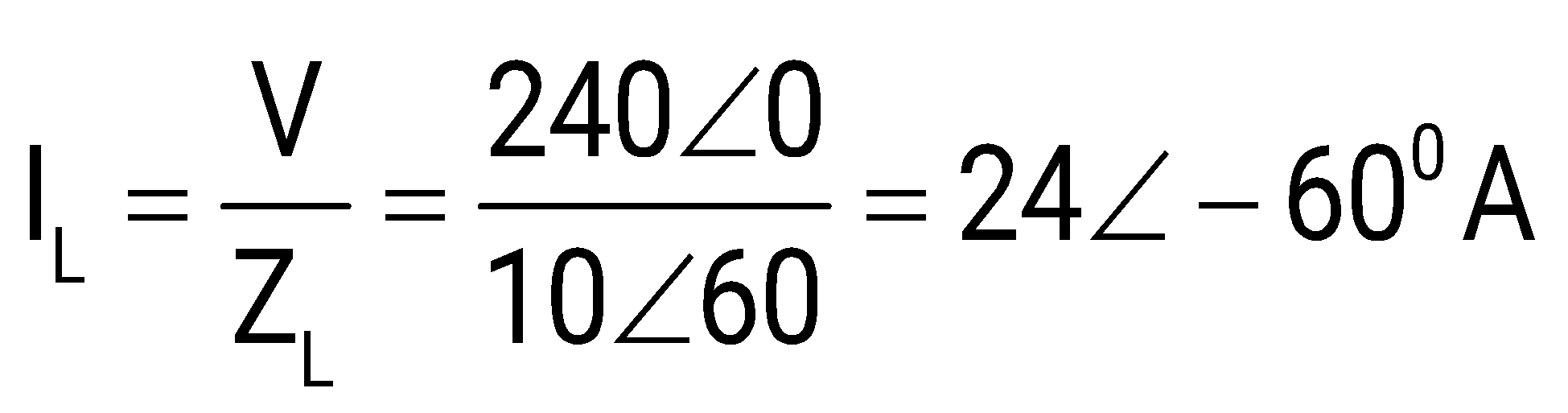

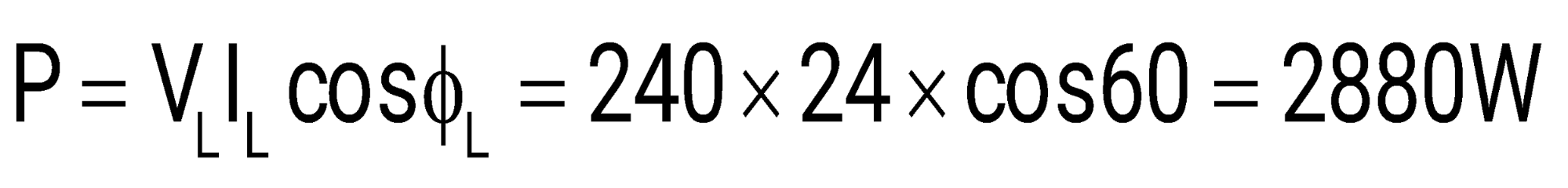

Sinusoidal Steady State Analysis

Practice questions from Sinusoidal Steady State Analysis.

79

Total0

Attempted0

Correct0

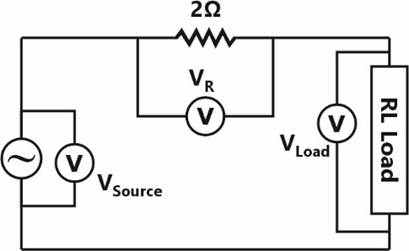

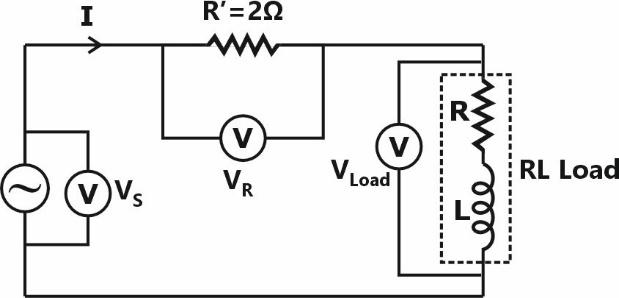

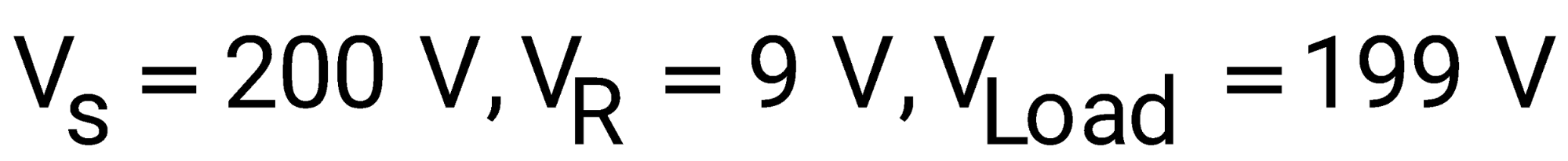

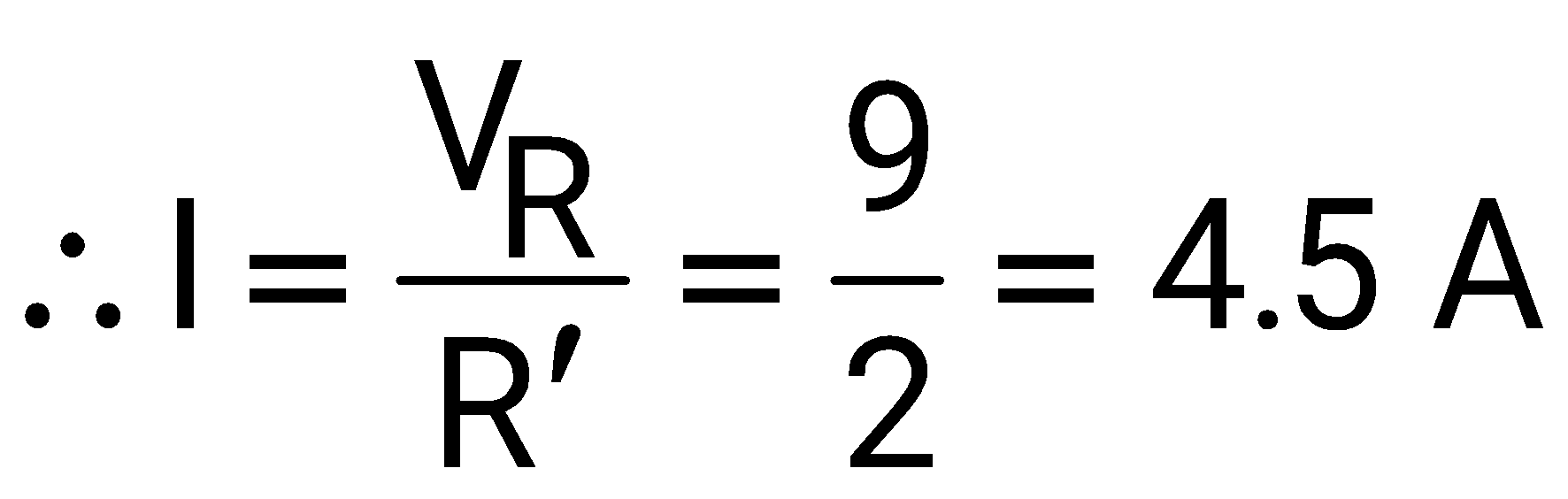

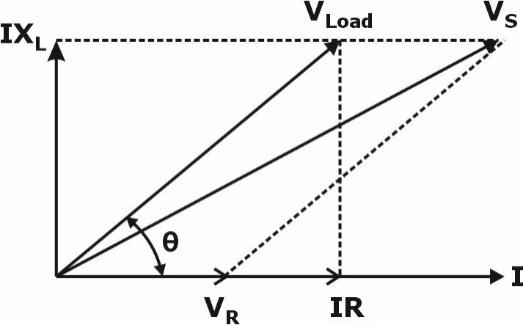

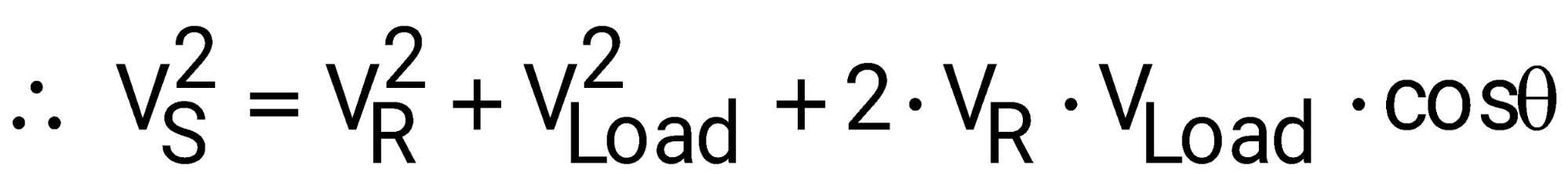

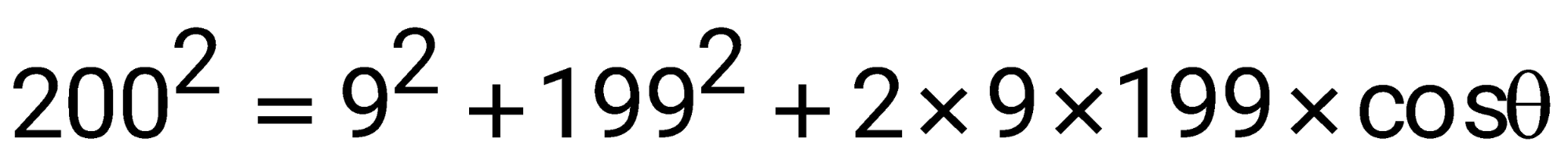

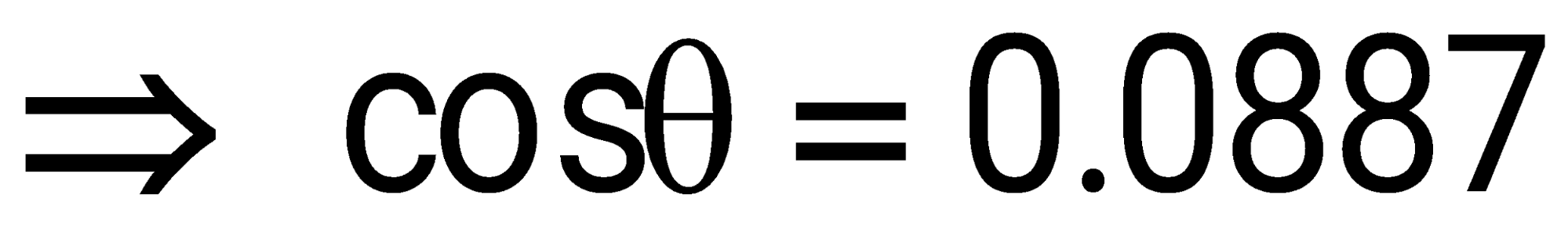

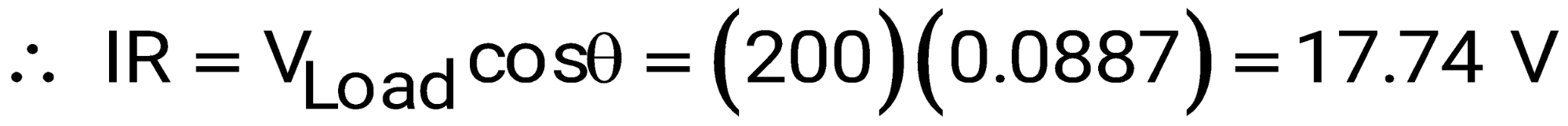

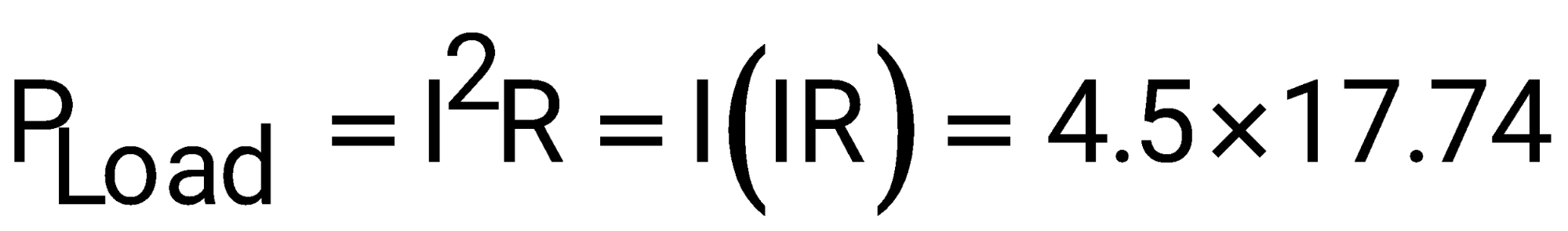

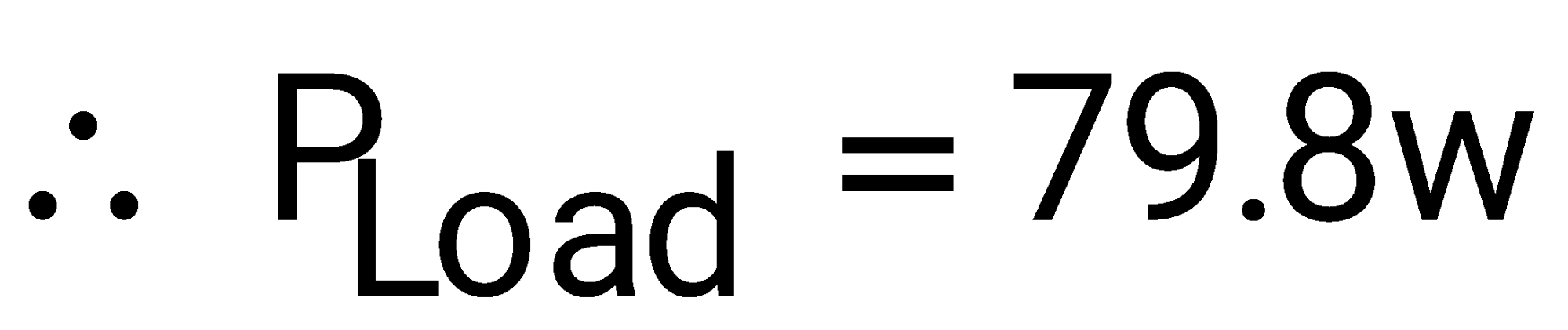

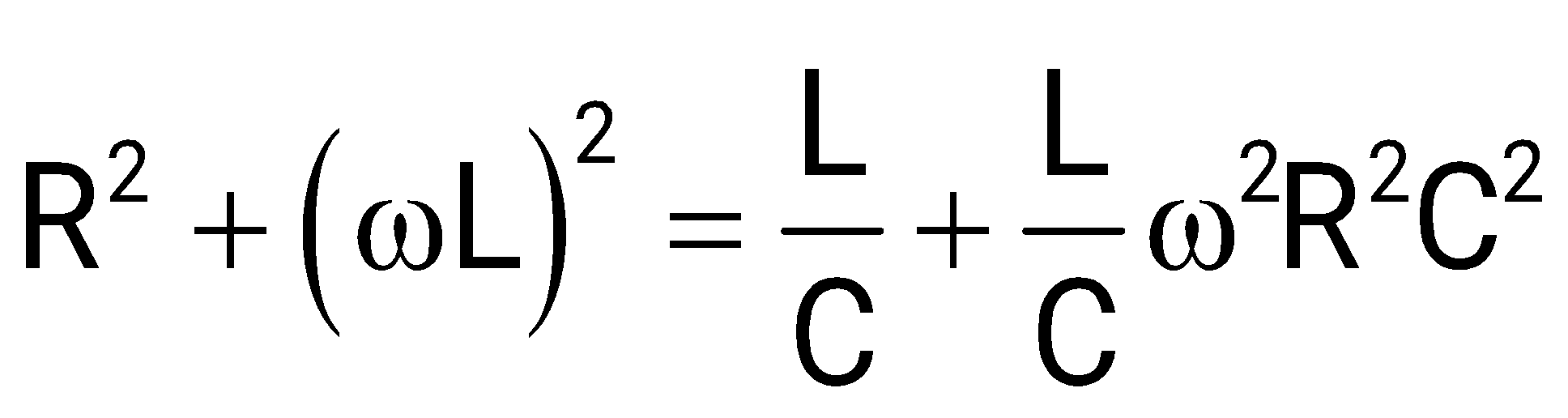

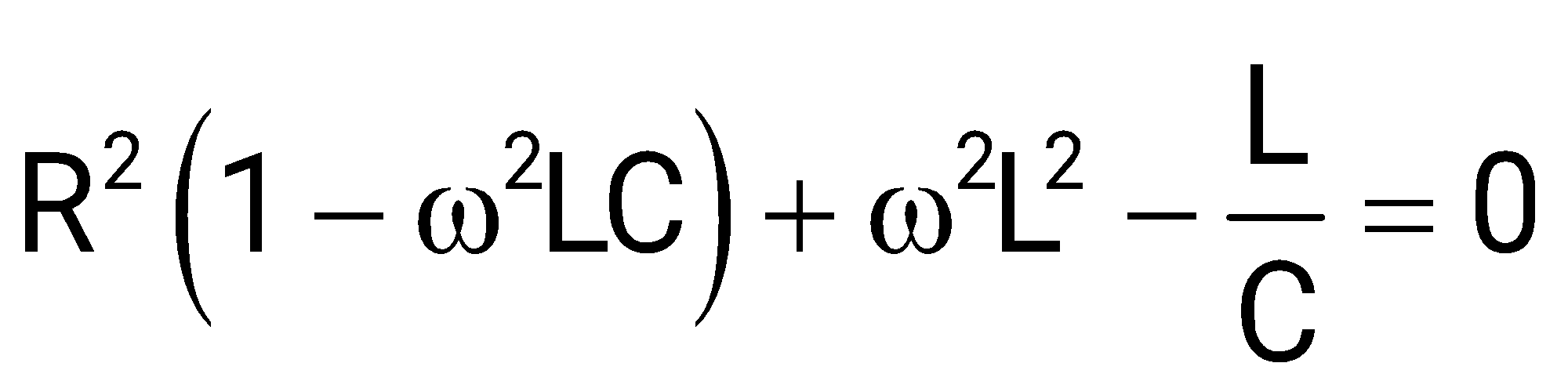

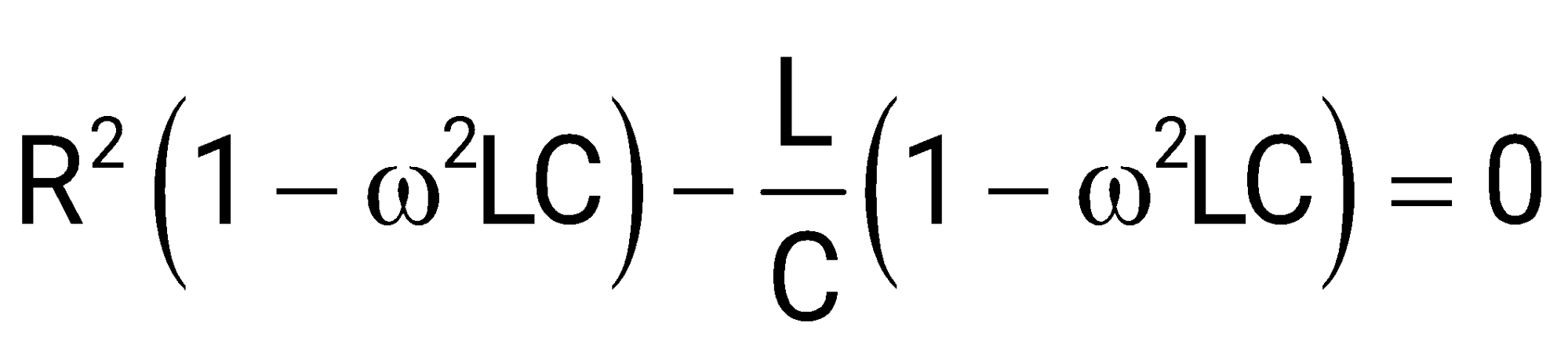

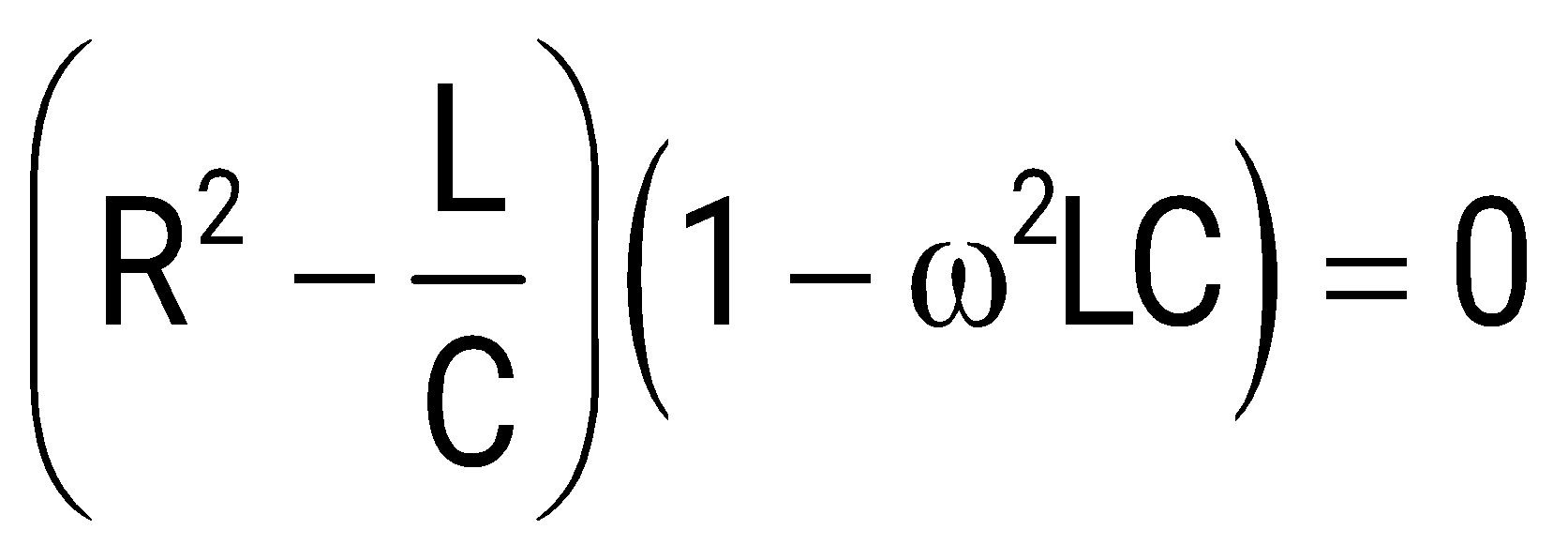

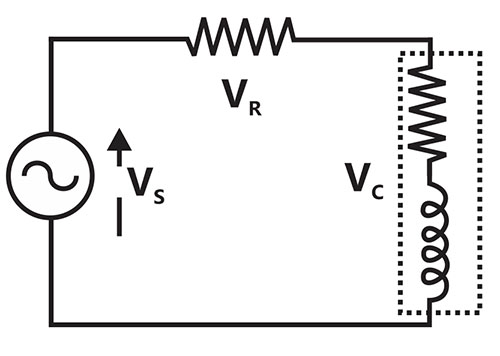

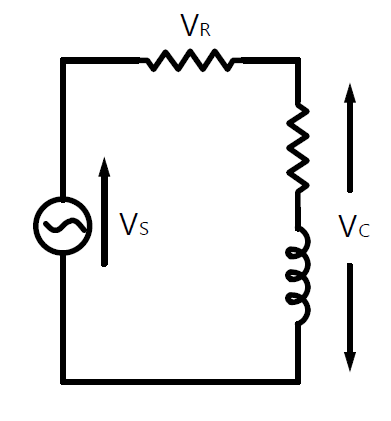

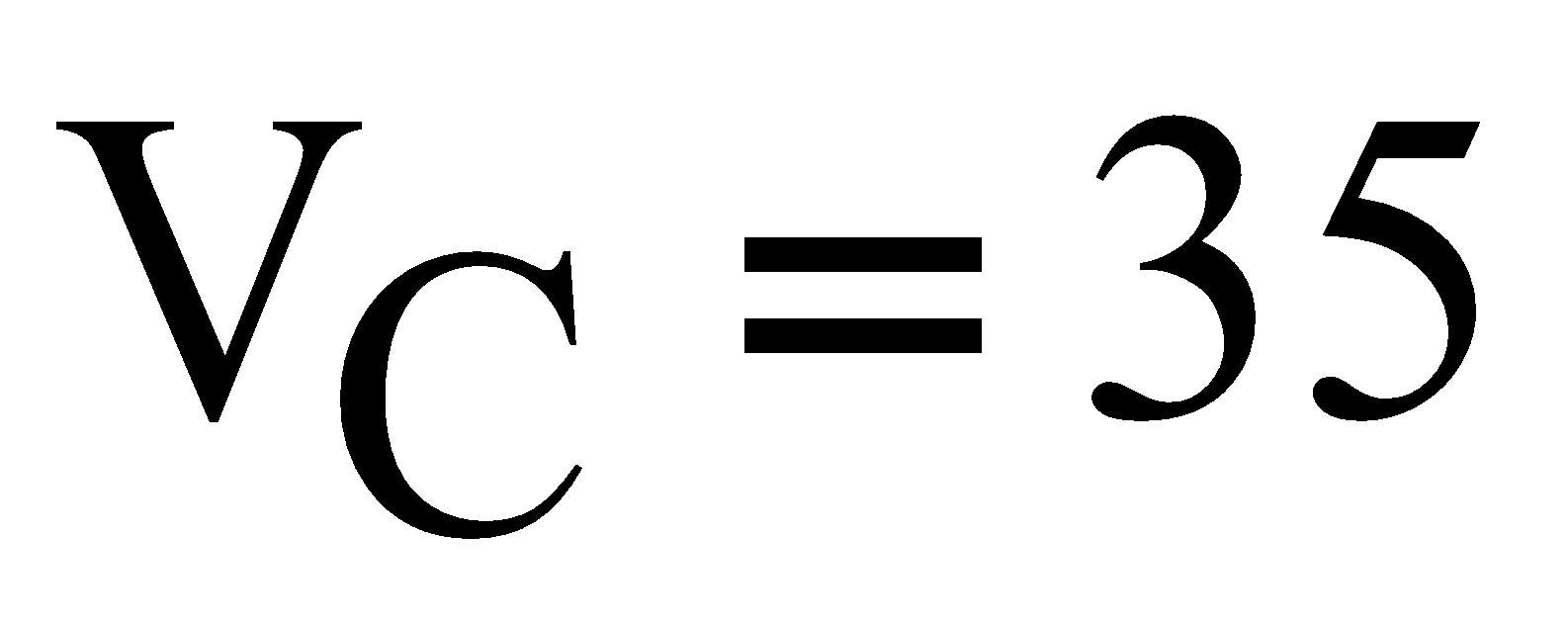

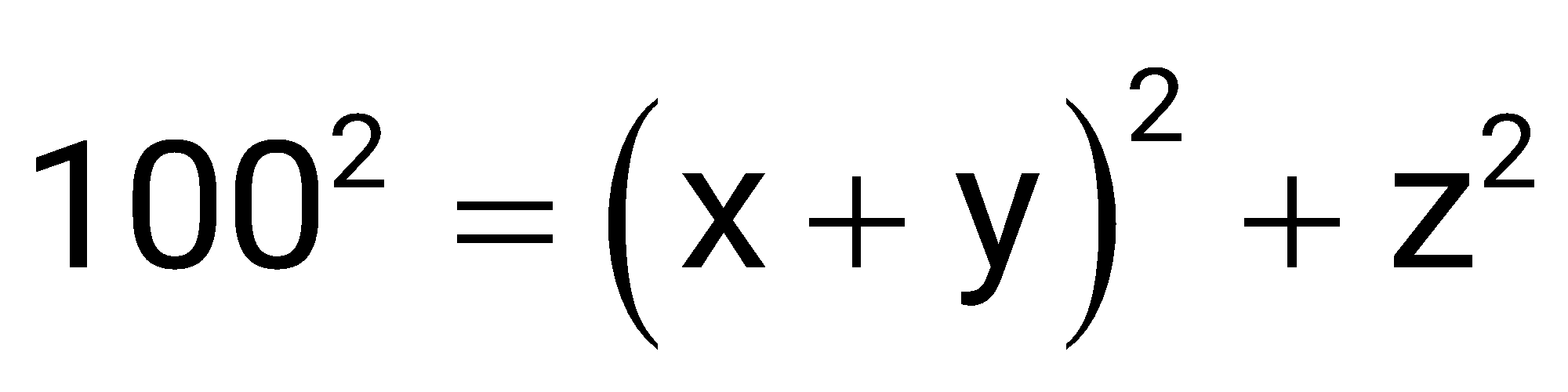

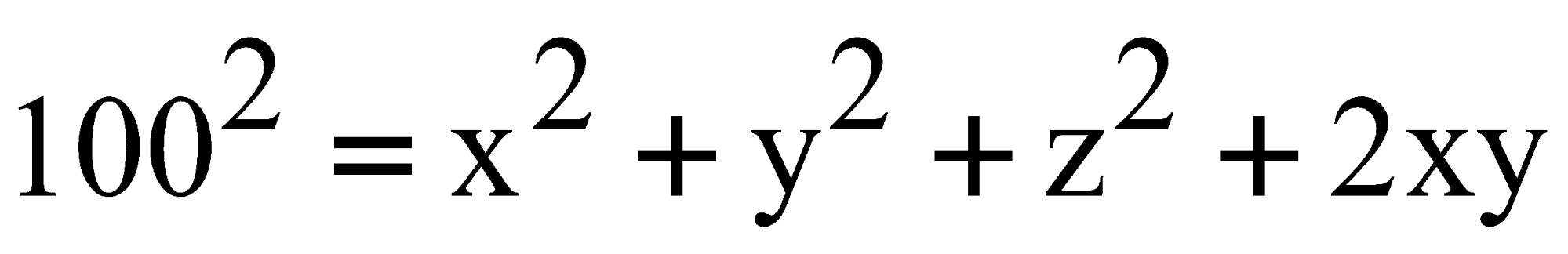

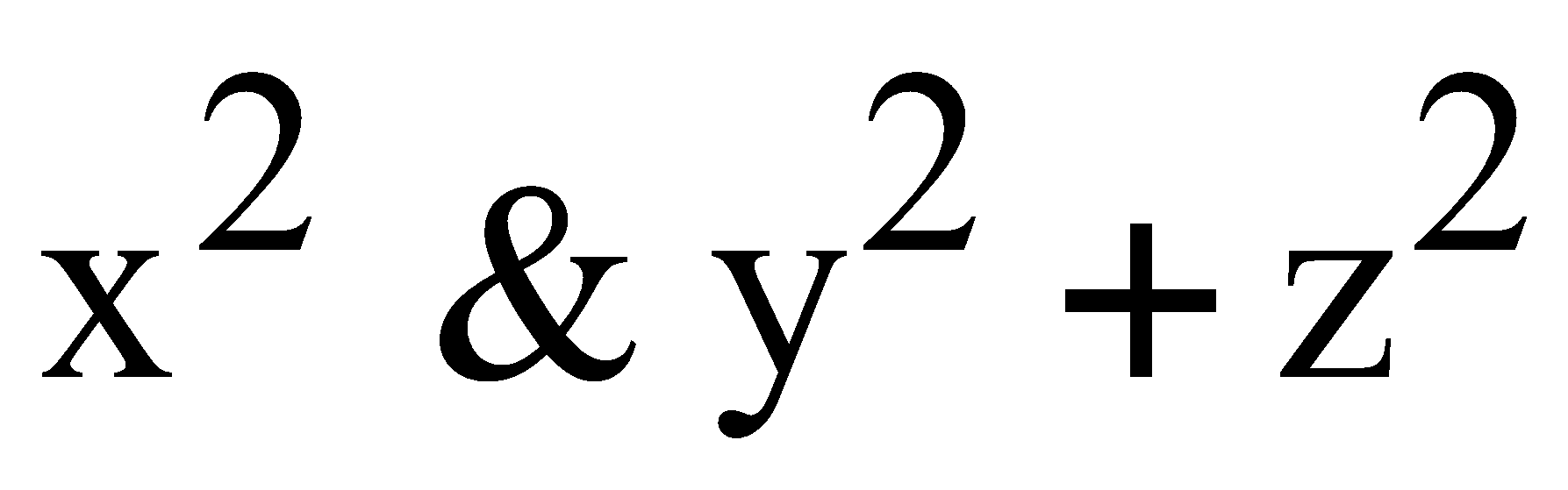

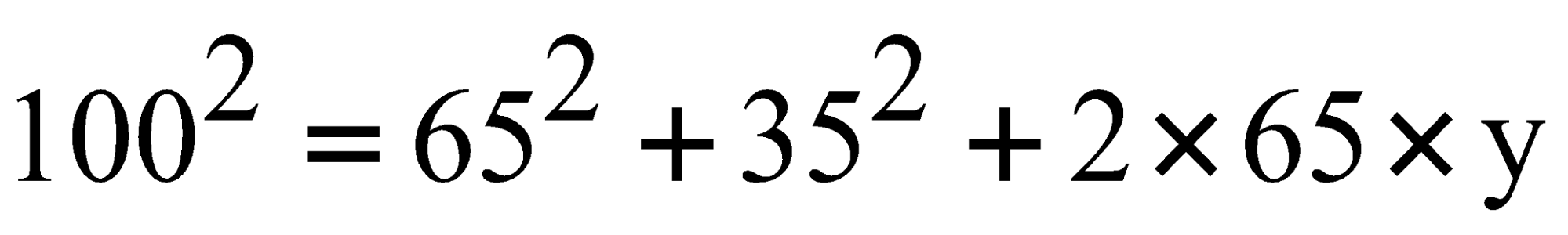

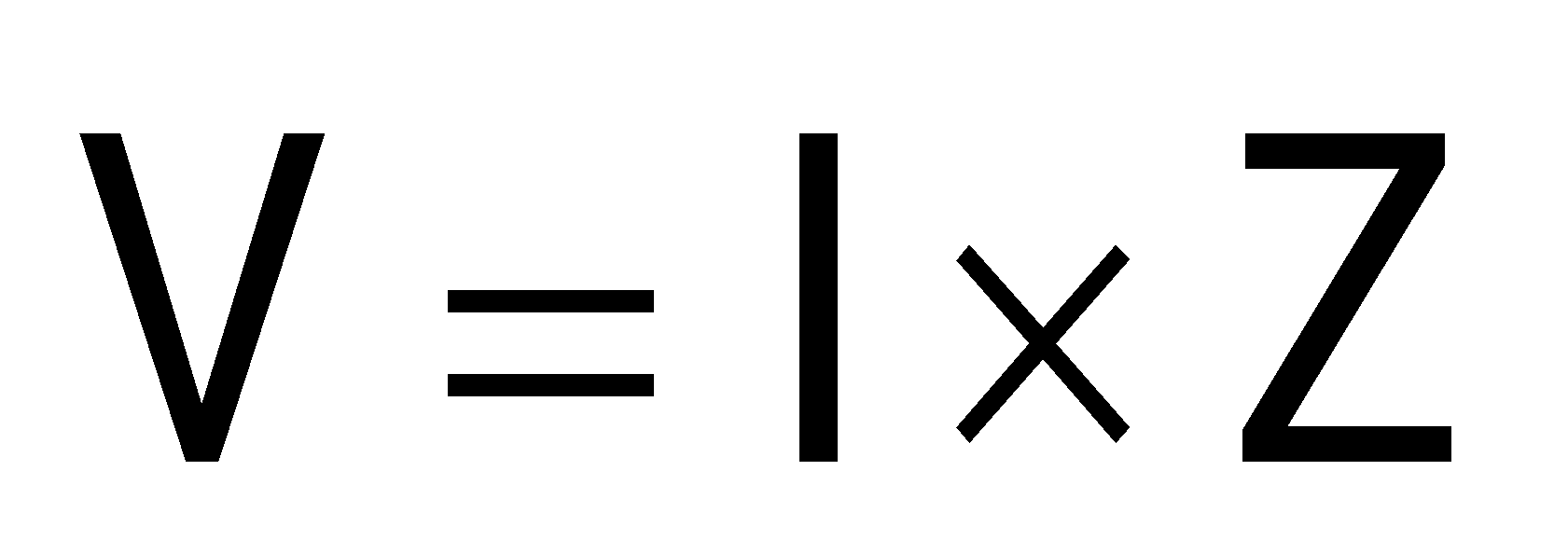

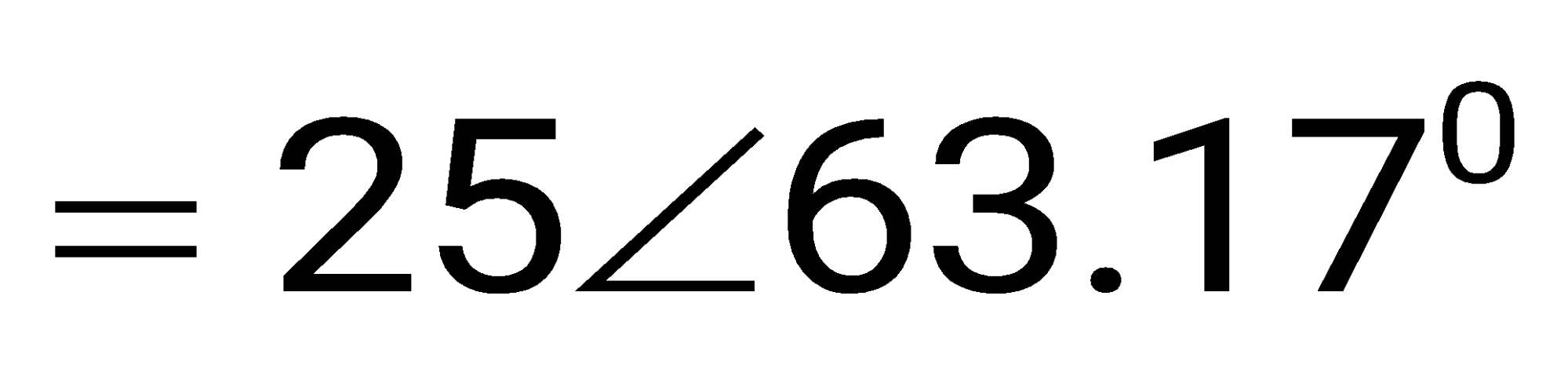

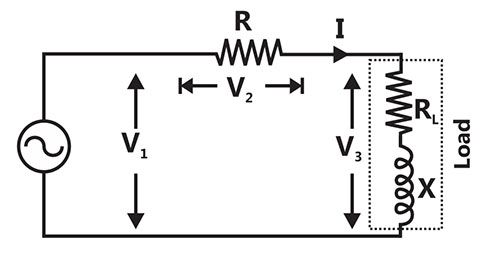

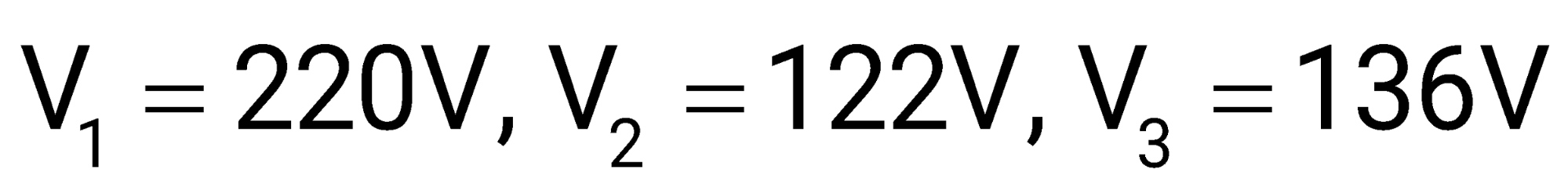

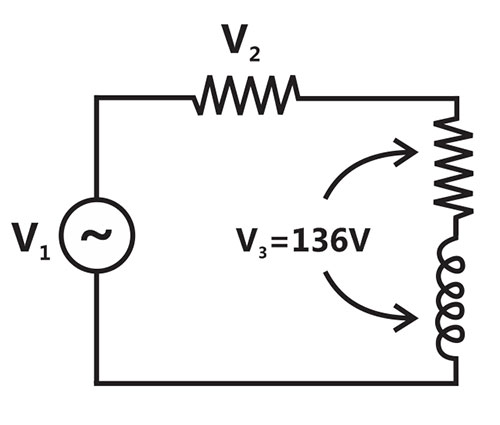

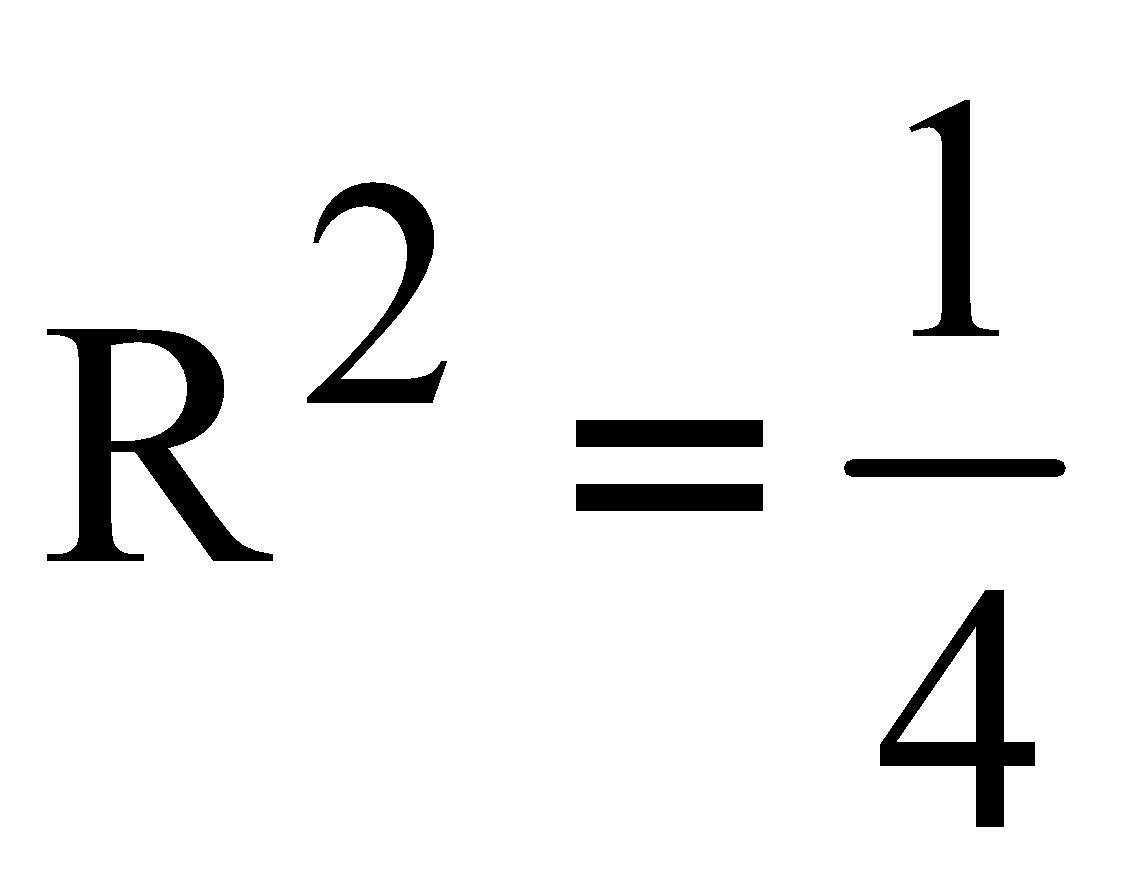

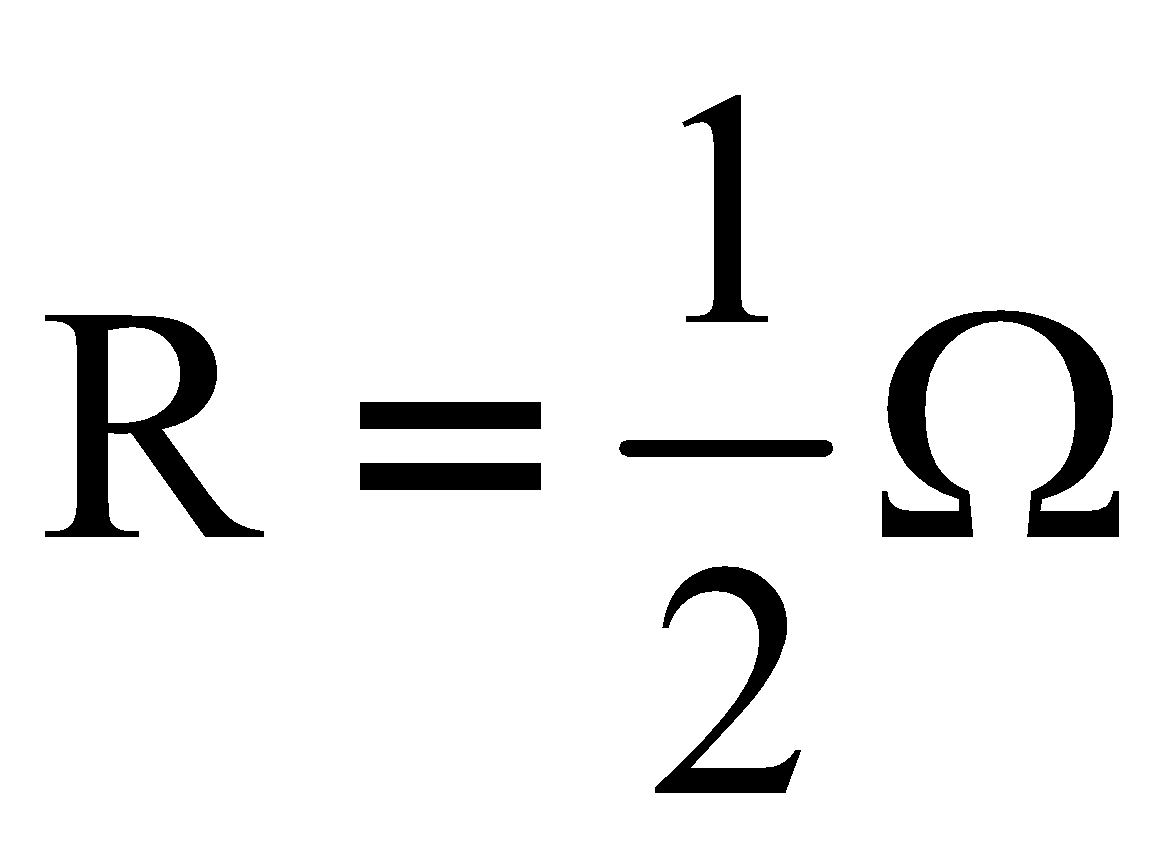

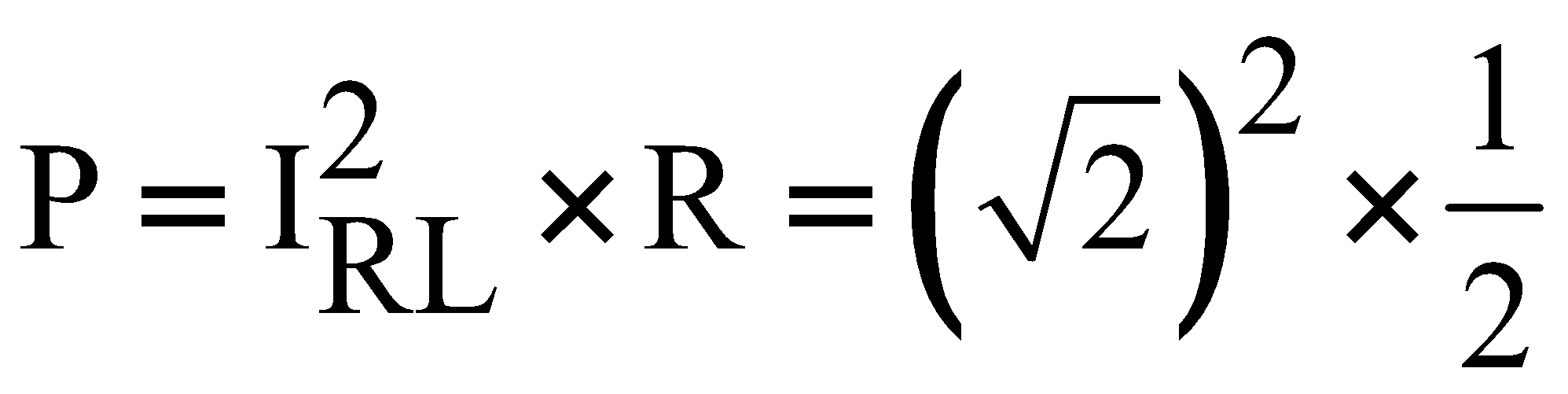

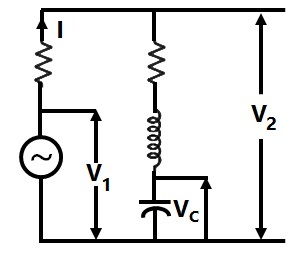

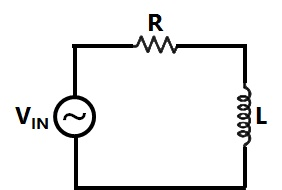

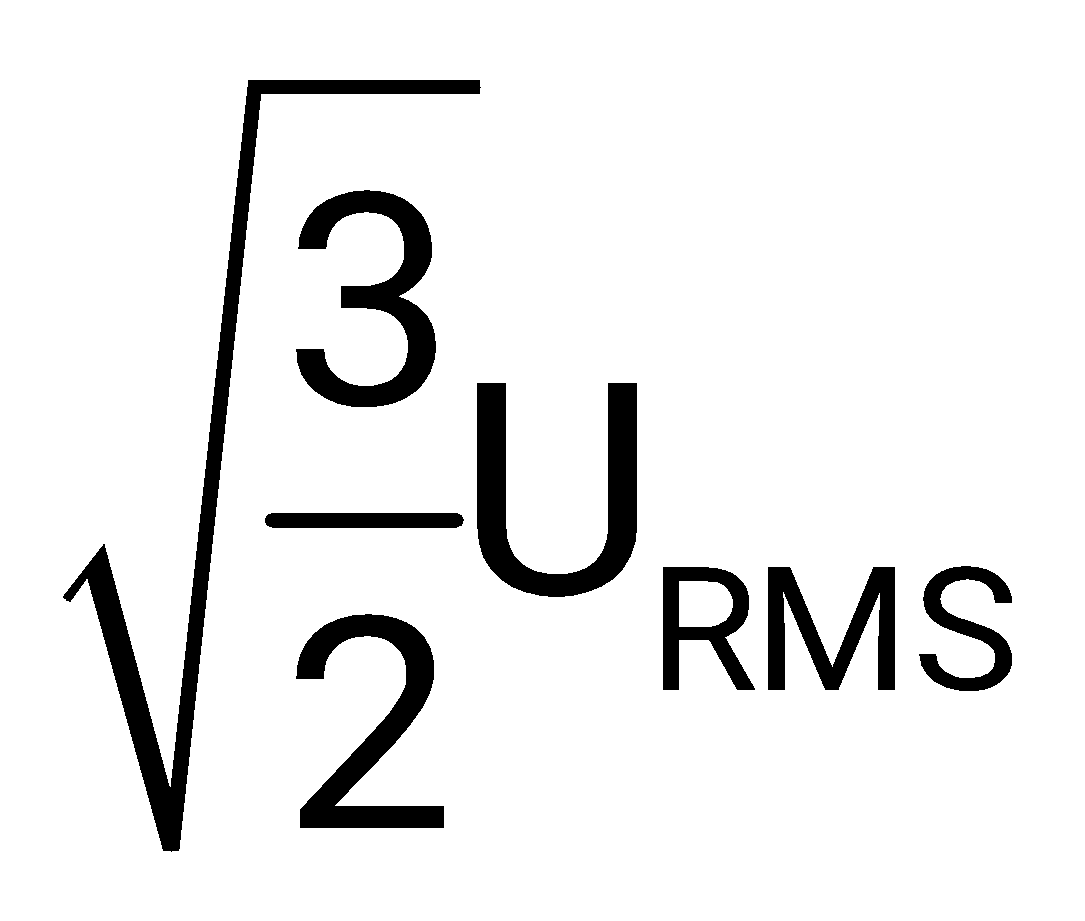

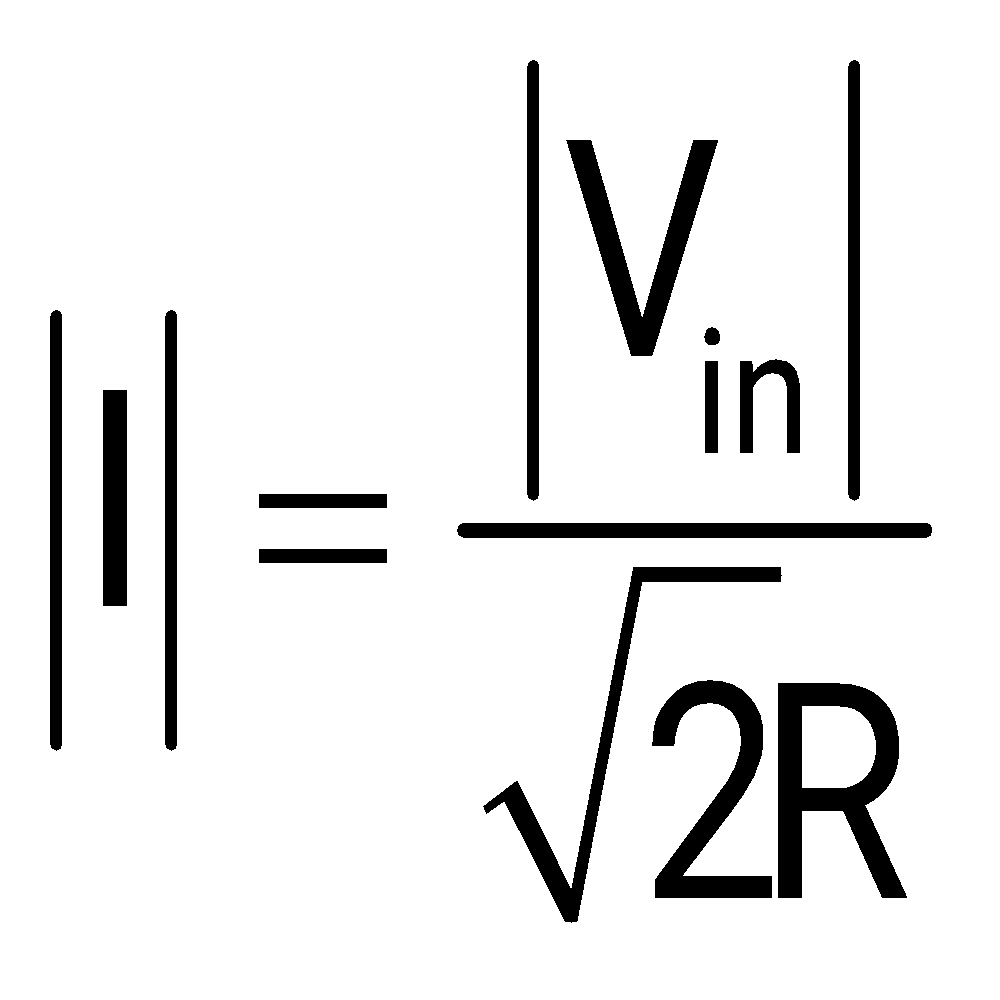

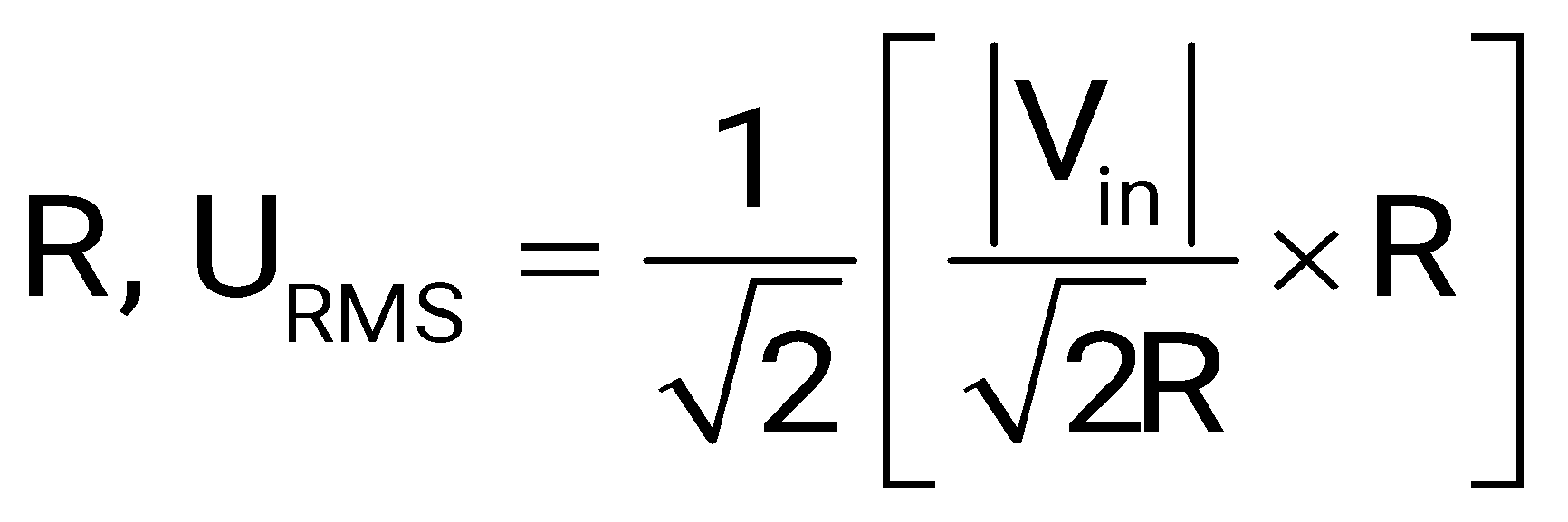

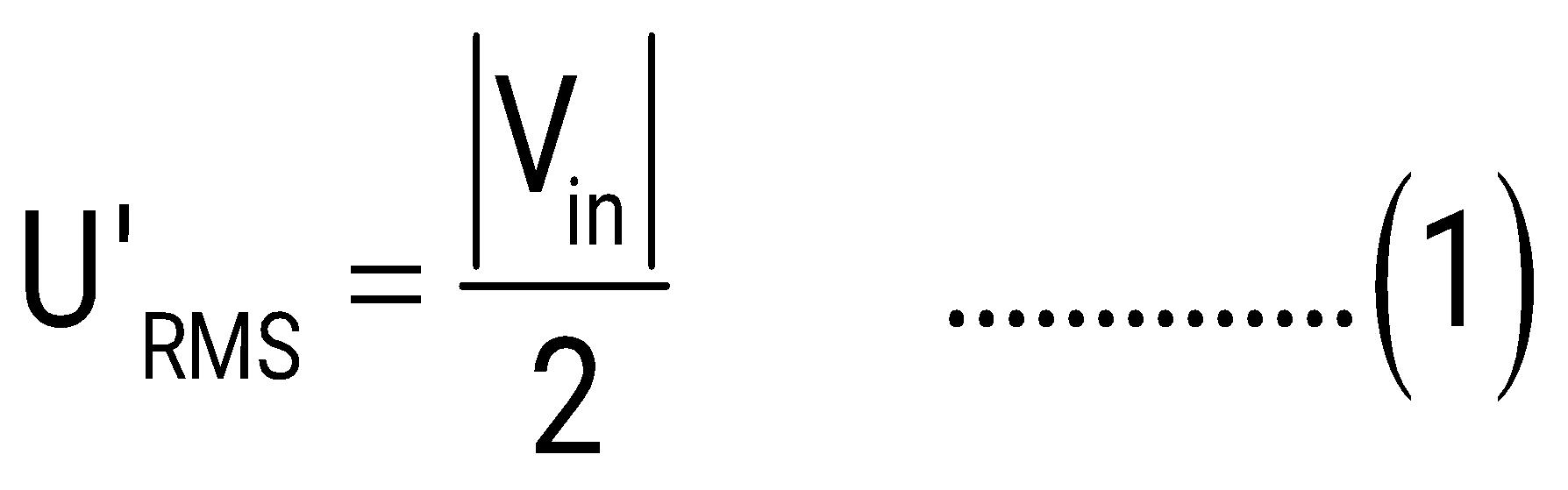

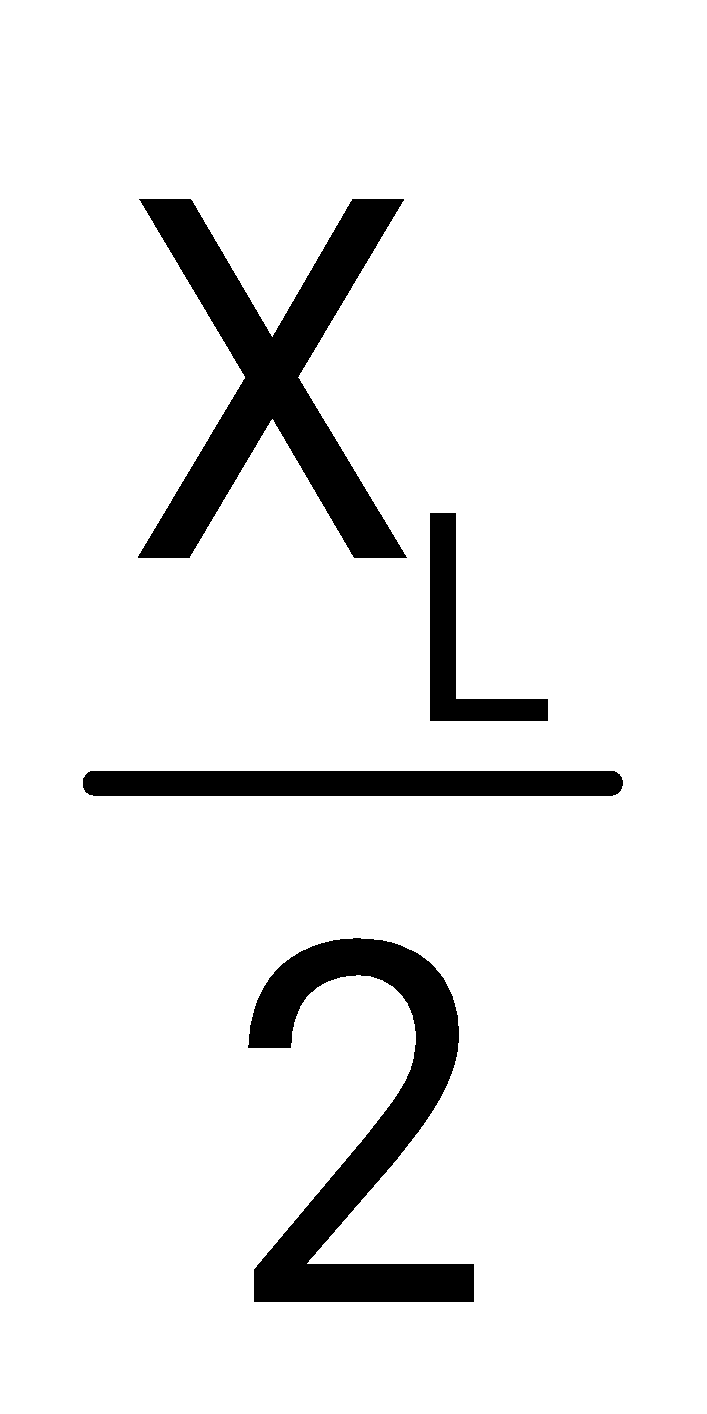

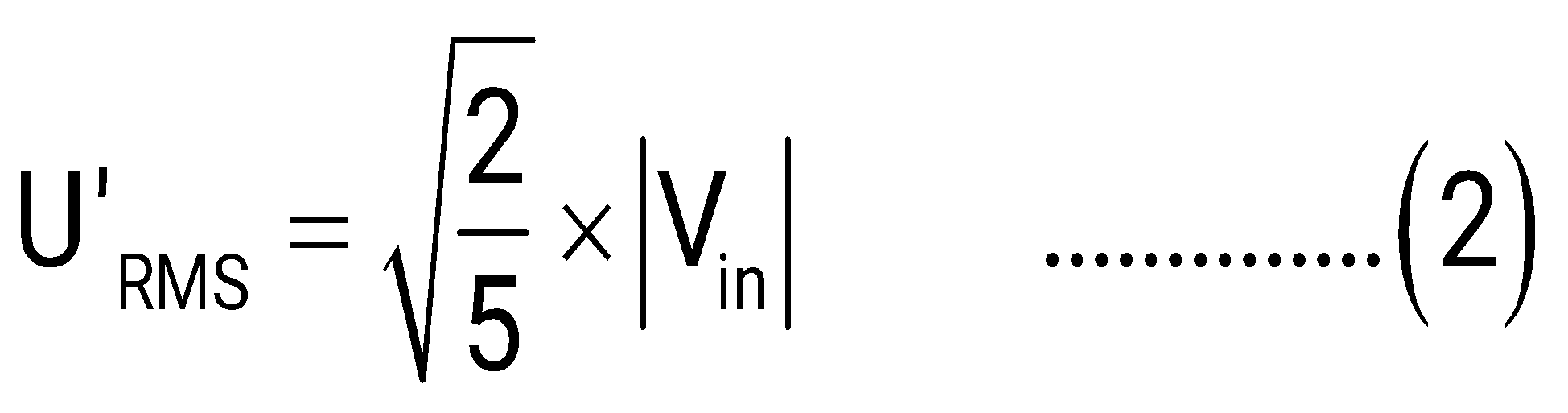

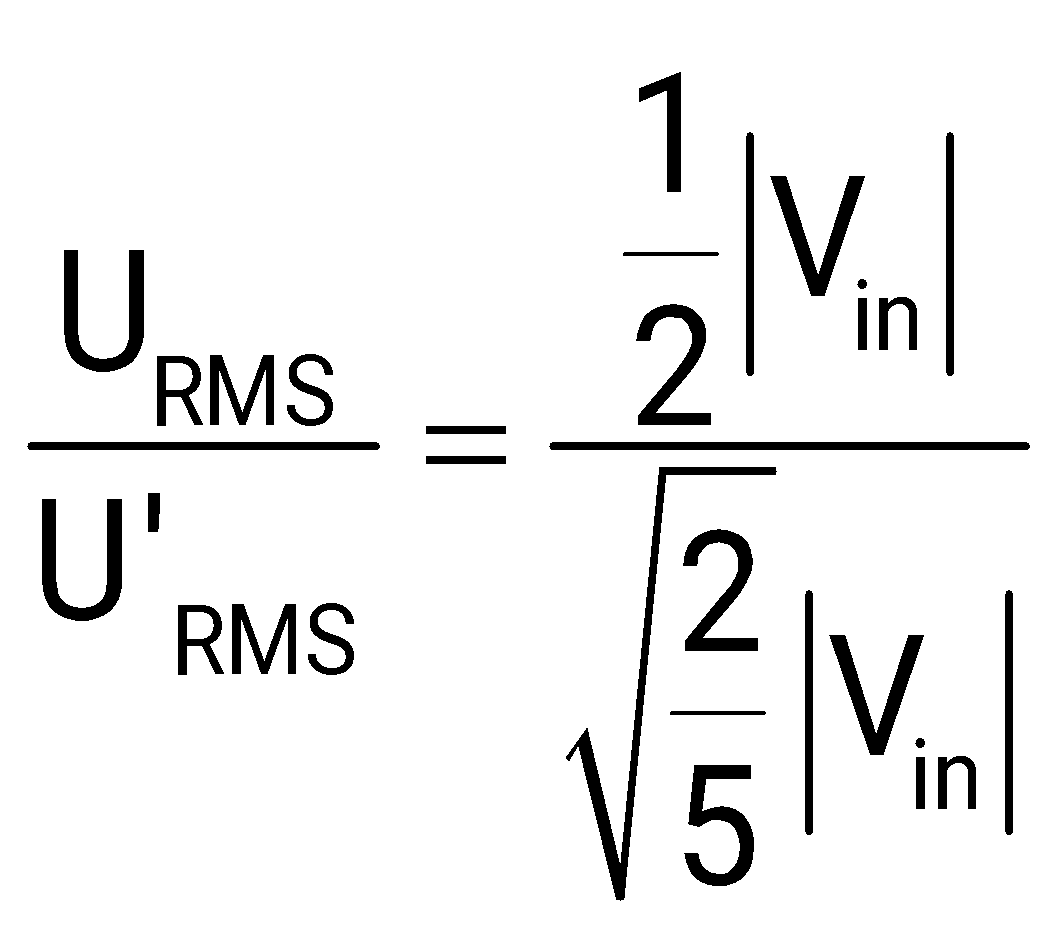

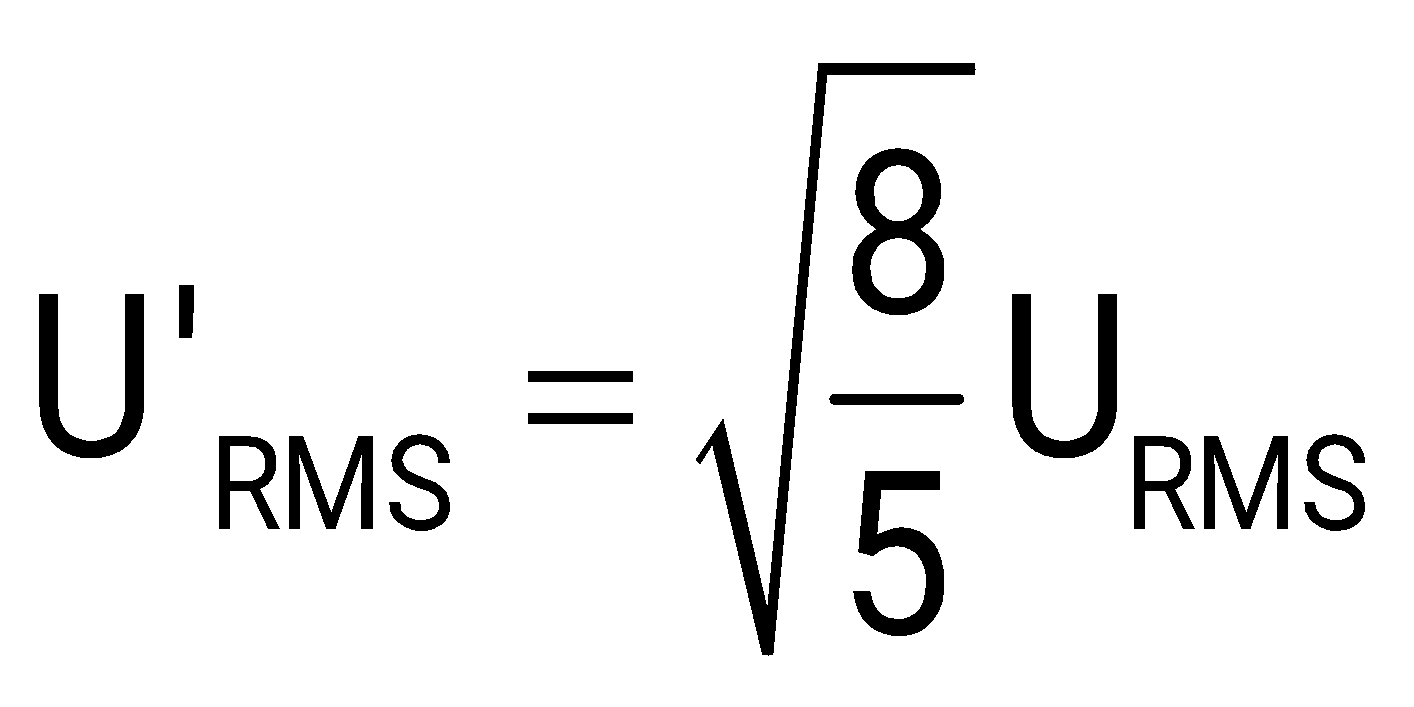

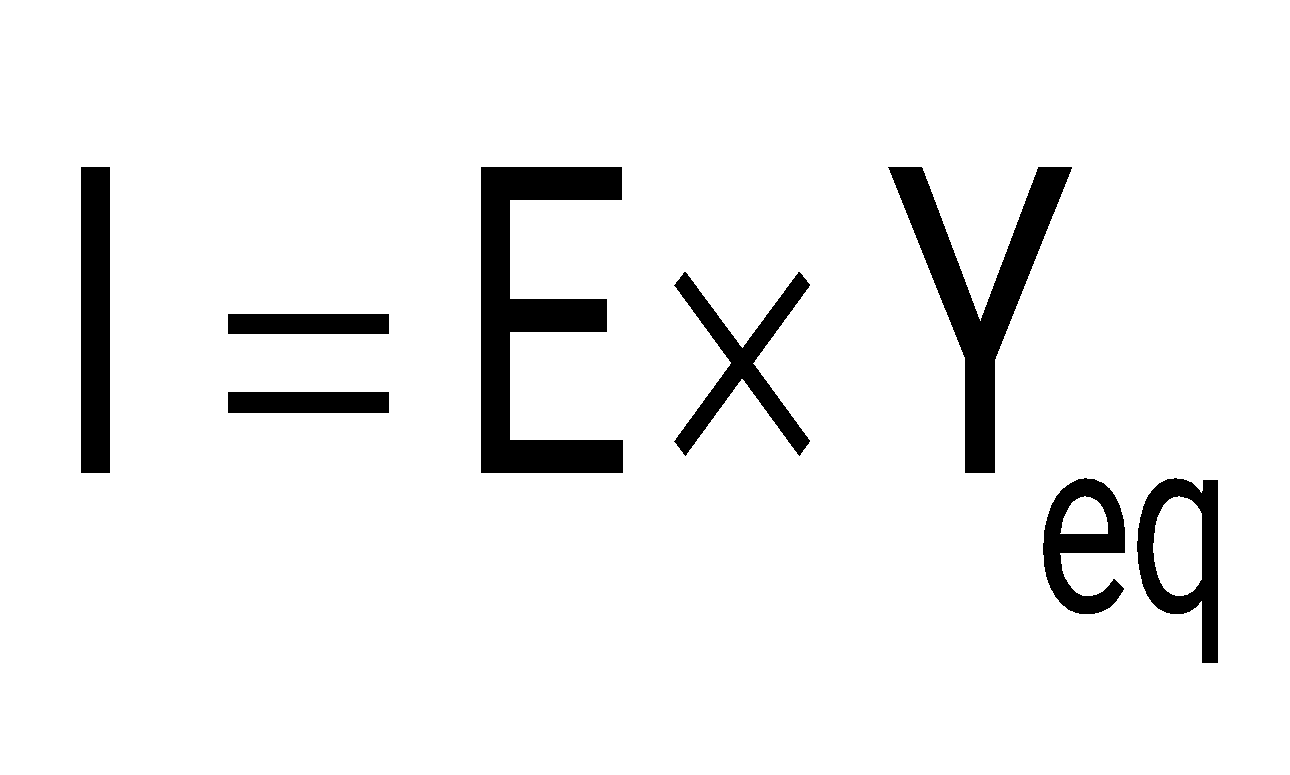

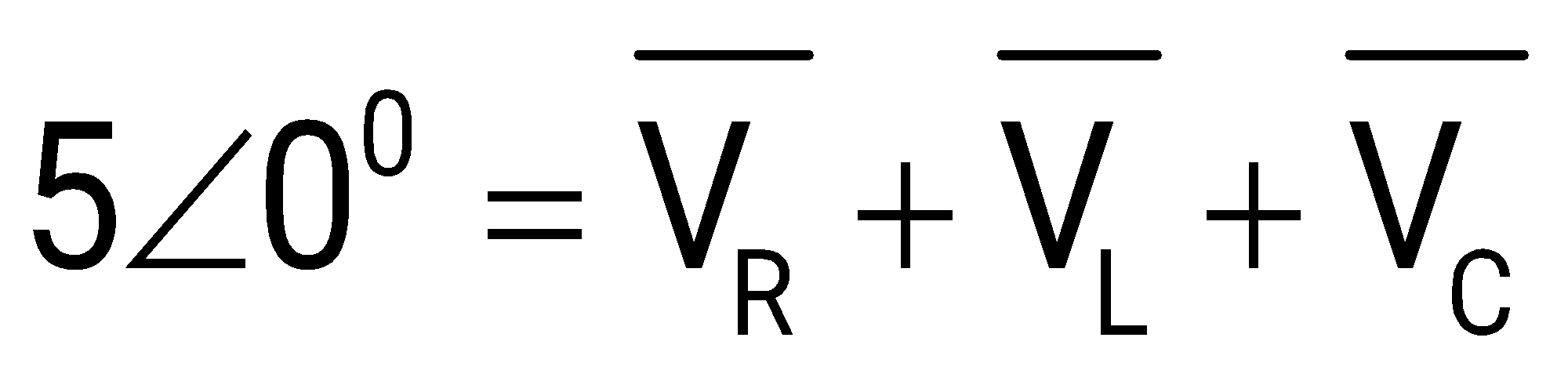

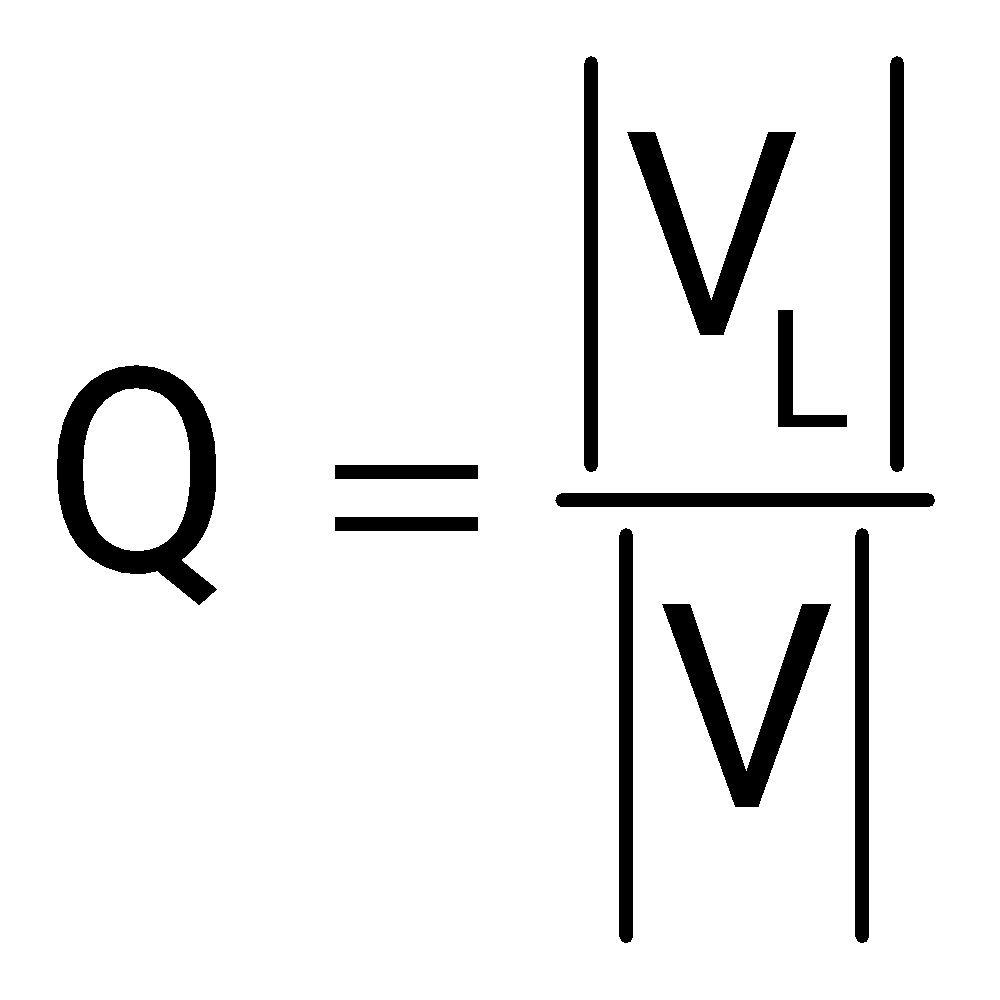

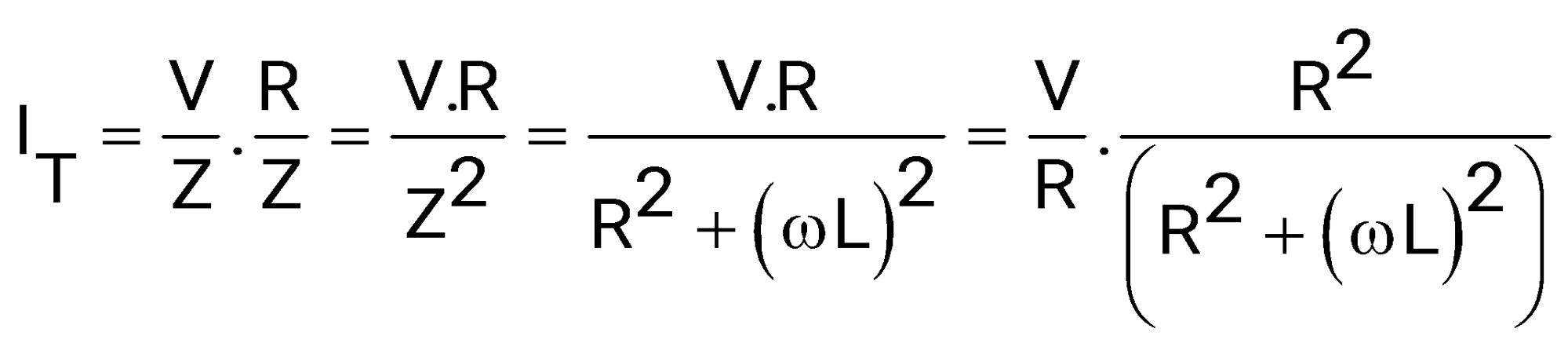

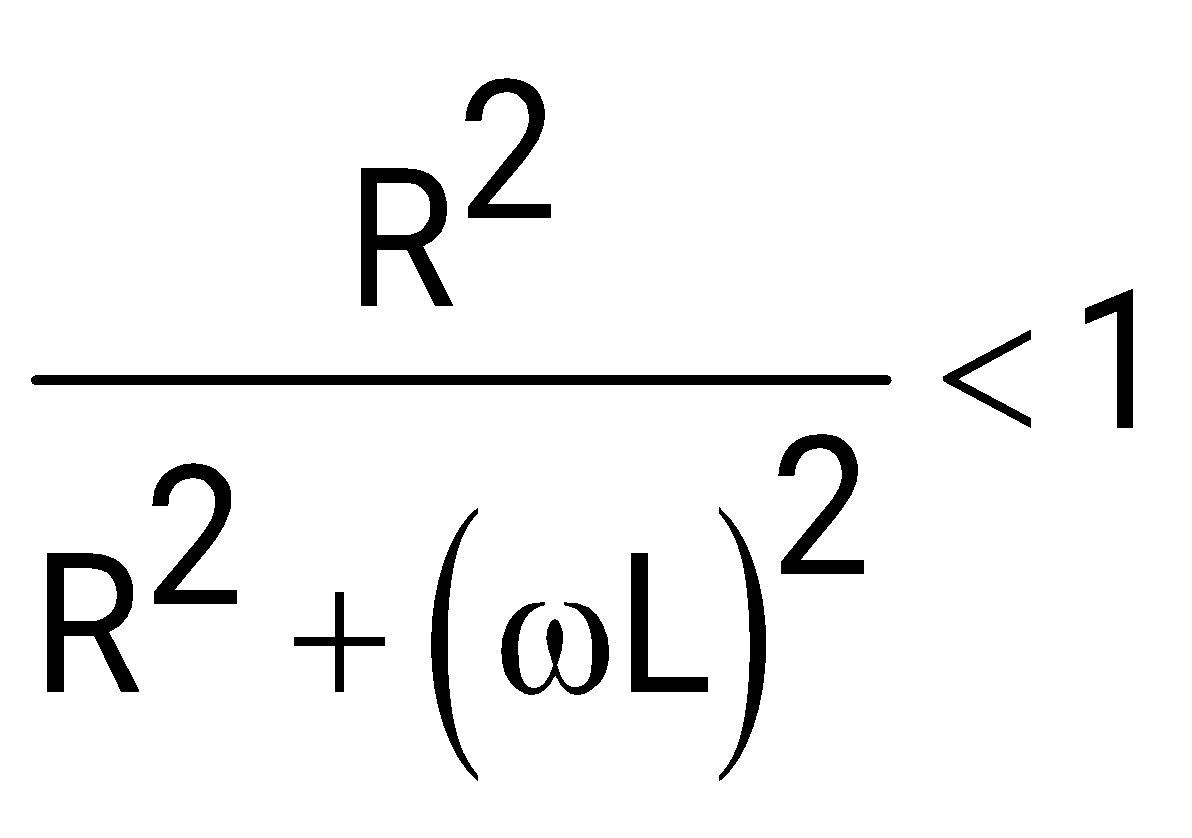

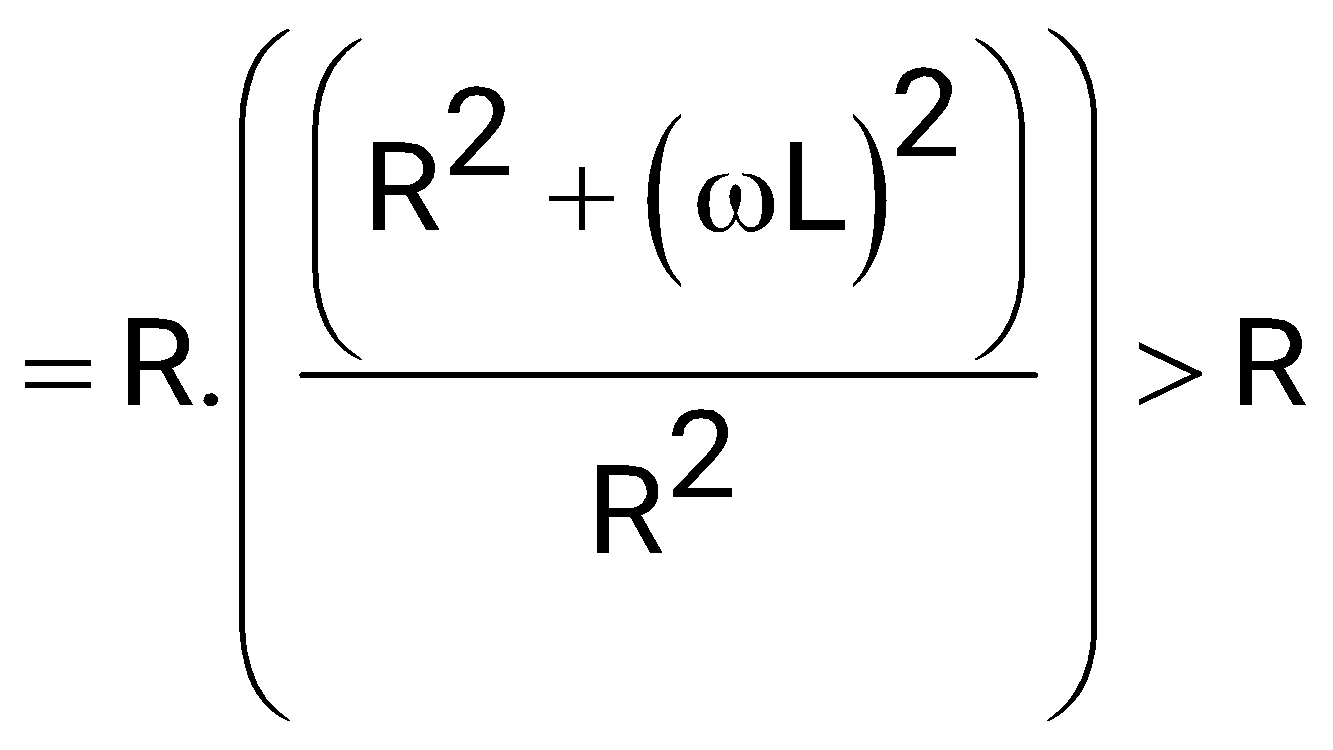

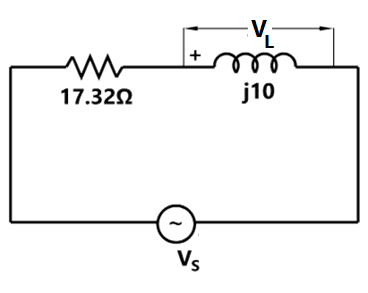

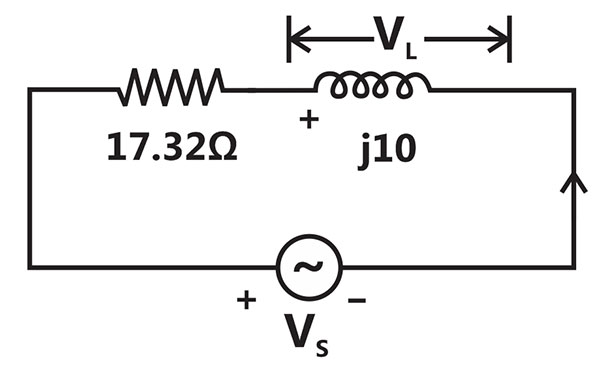

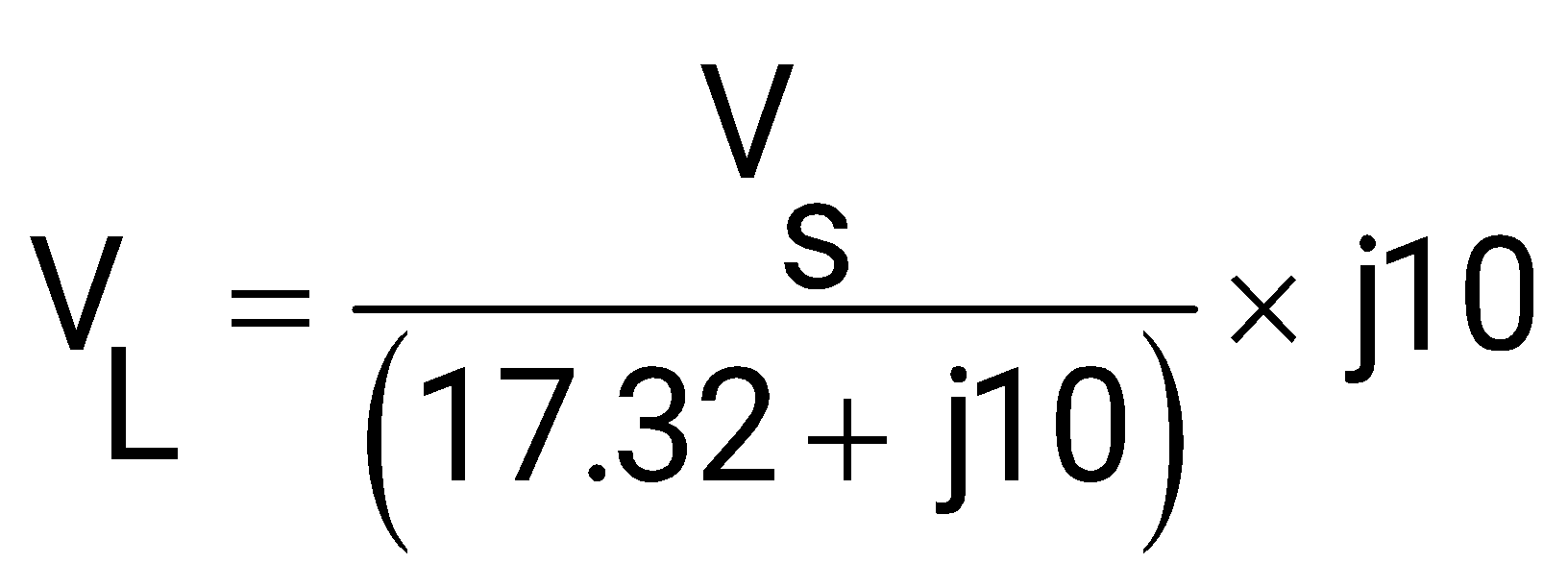

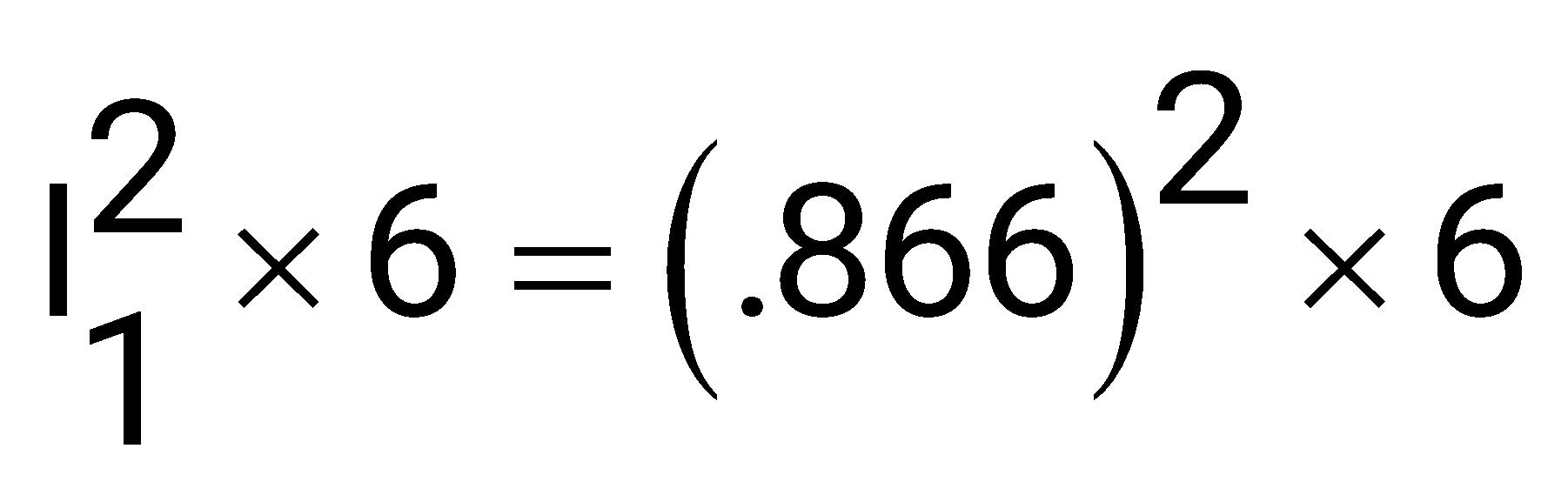

IncorrectIn an experiment to measure the active power drawn by a single-phase RL Load connected to an AC source through a resistor, three voltmeters are connected as shown in the figure below. The voltmeter readings are as follows: . Assuming perfect resistors and ideal voltmeters, the Load-active power measured in this experiment, in W, is __________ (round off to one decimal place).

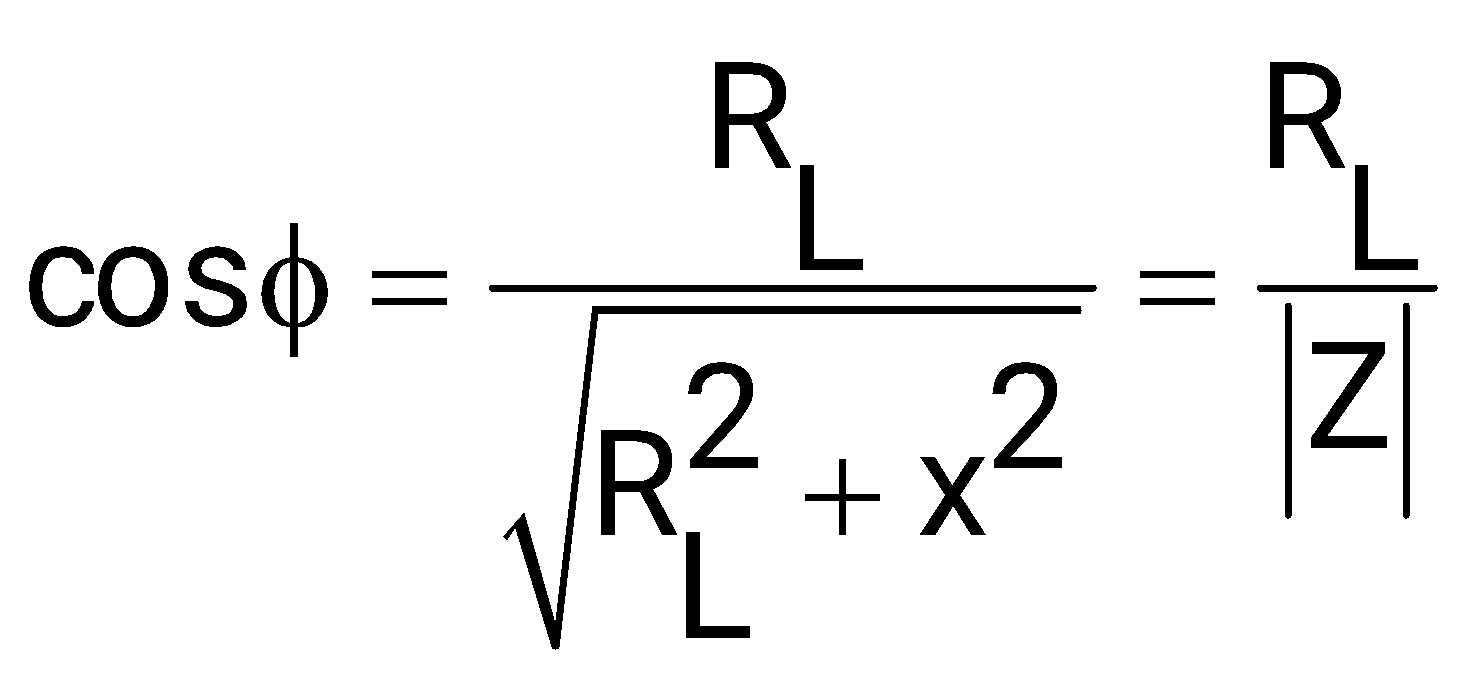

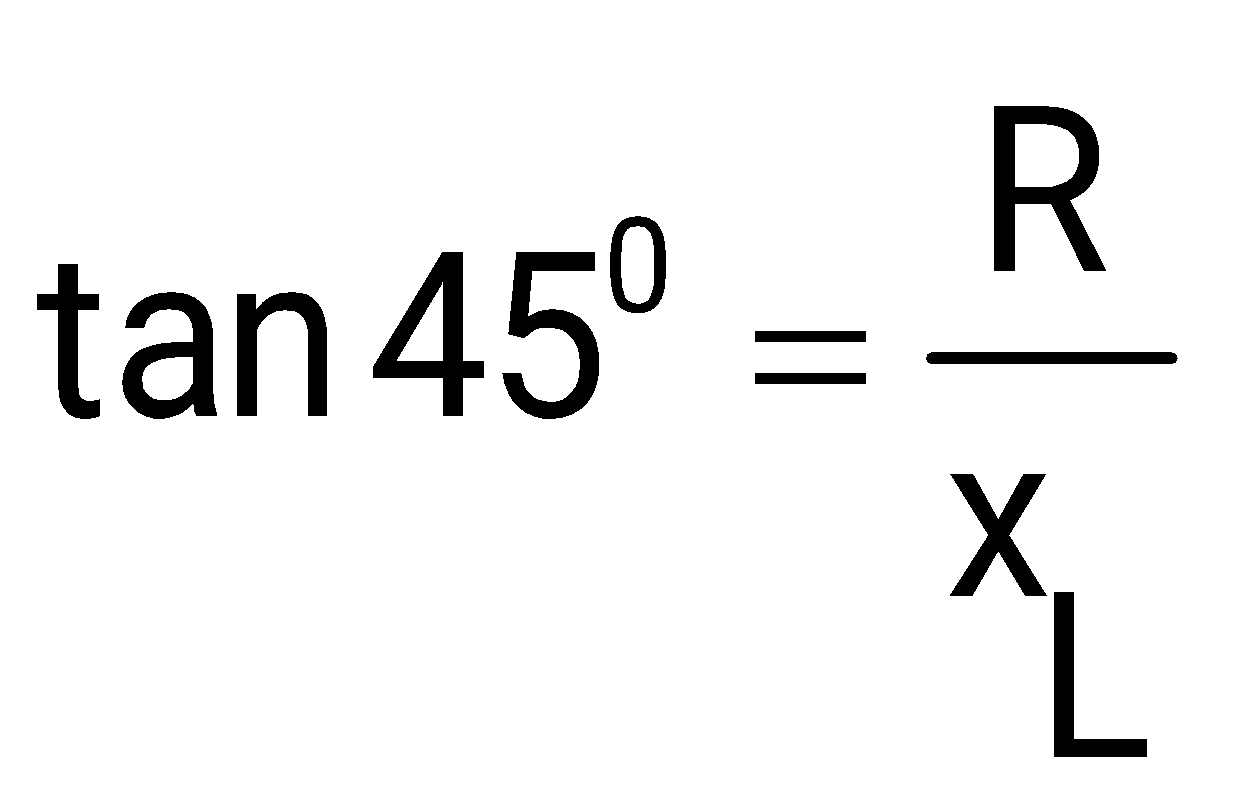

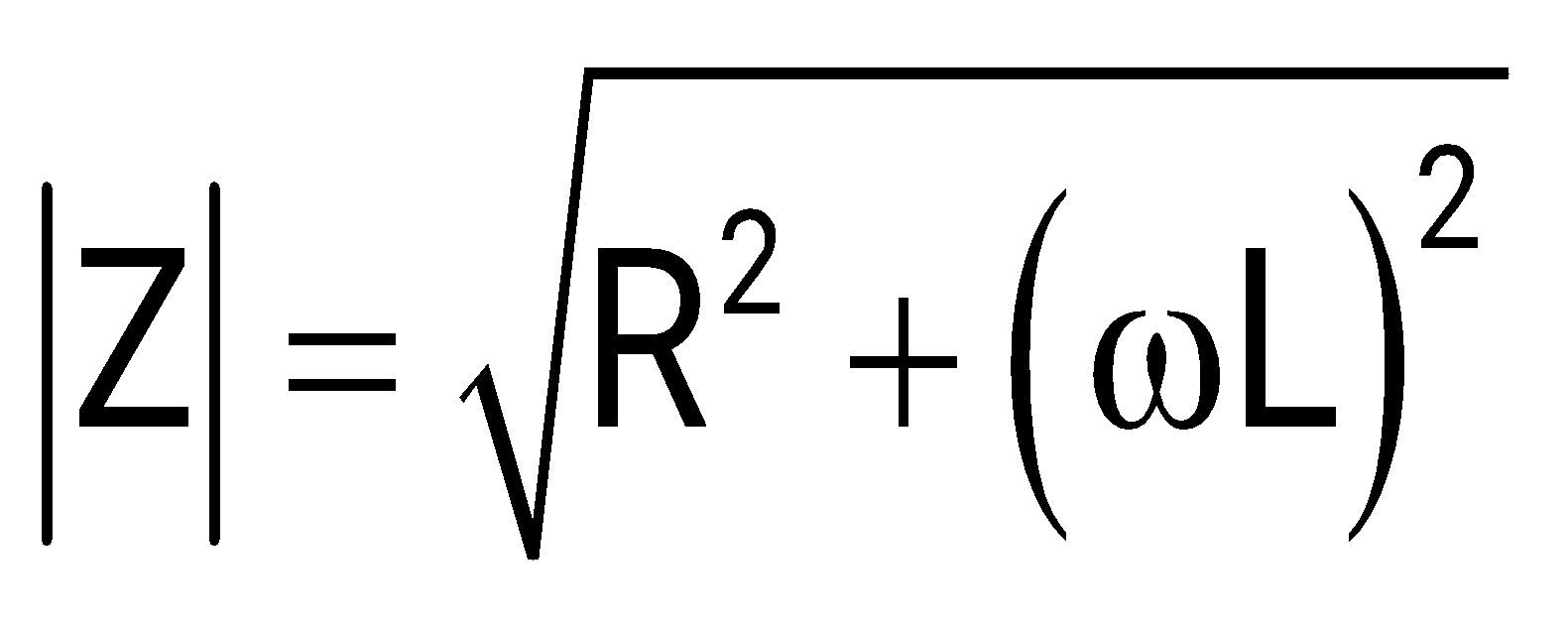

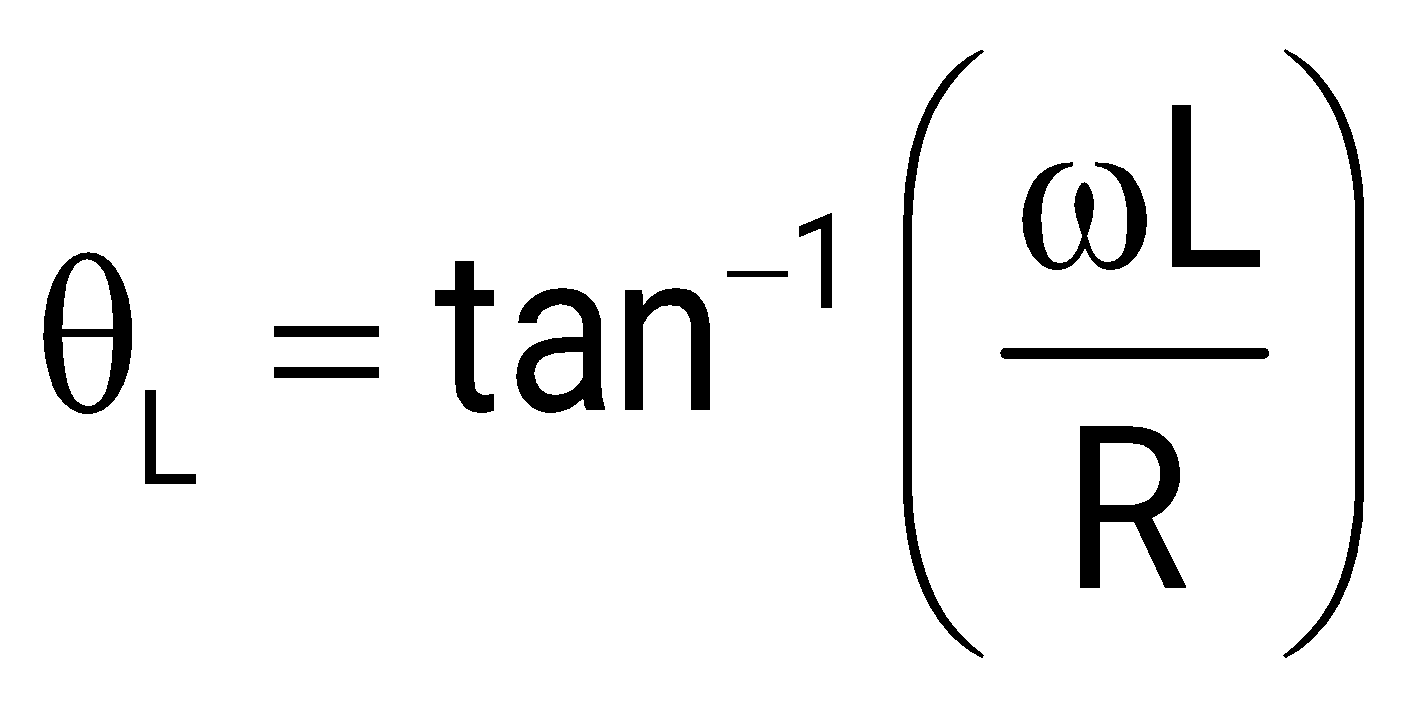

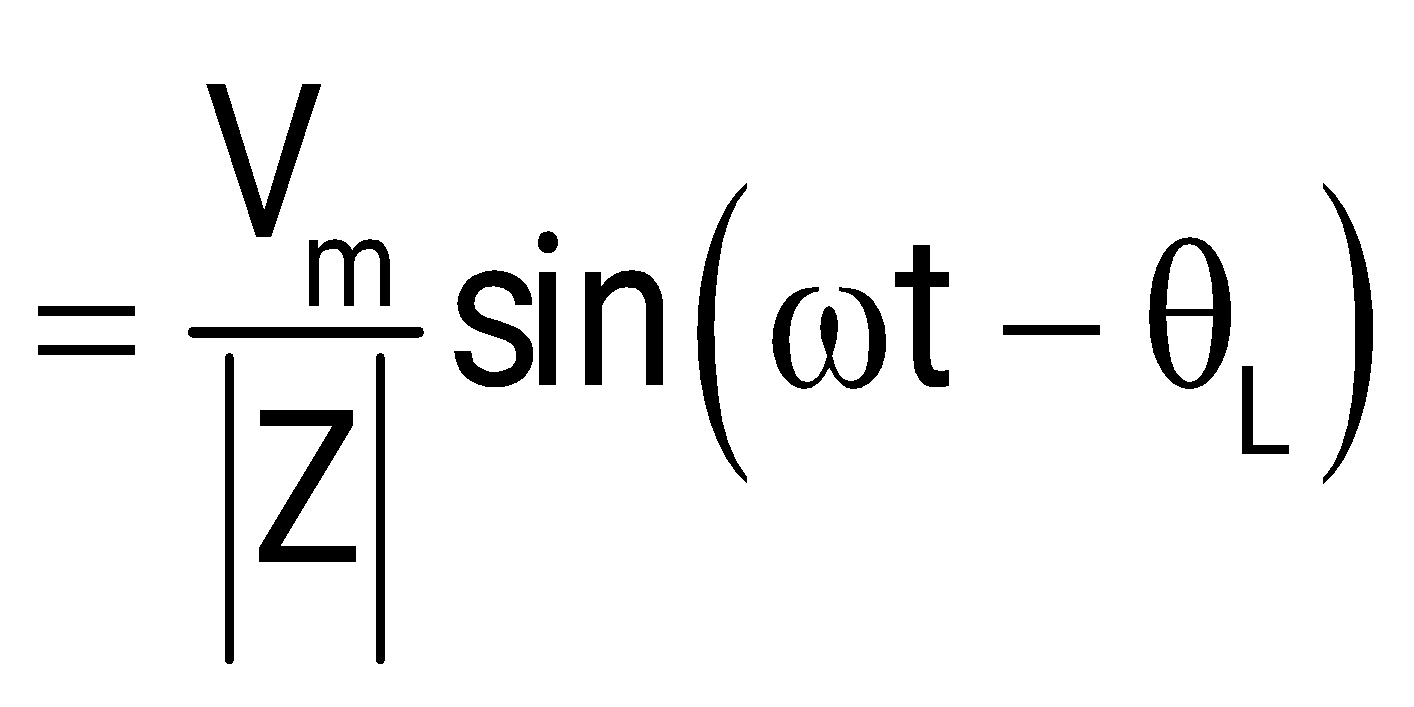

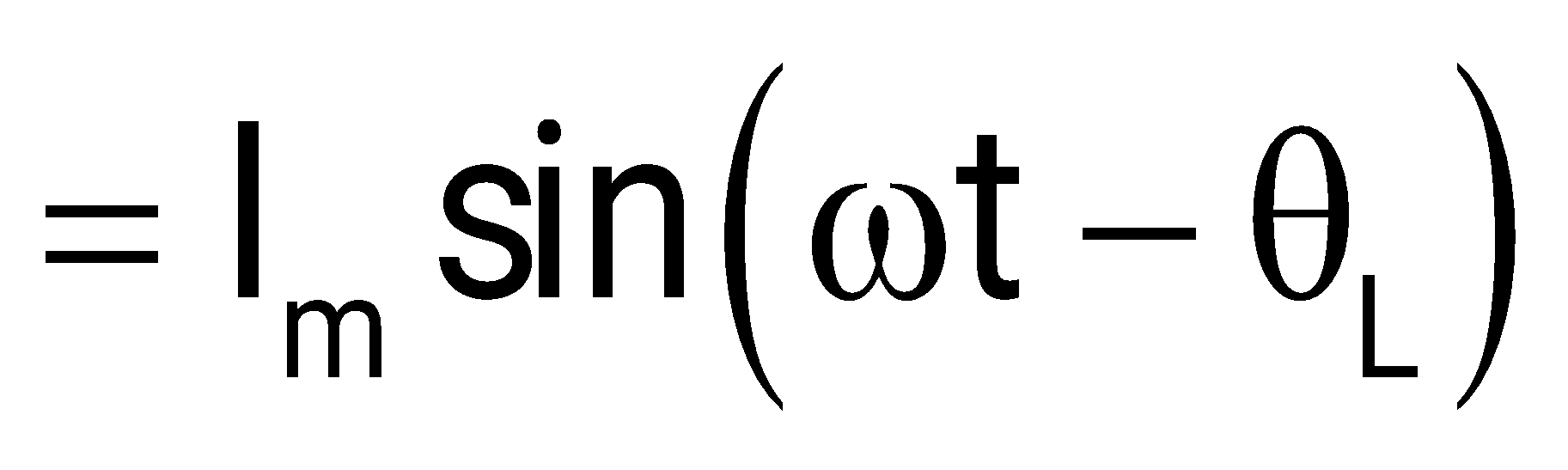

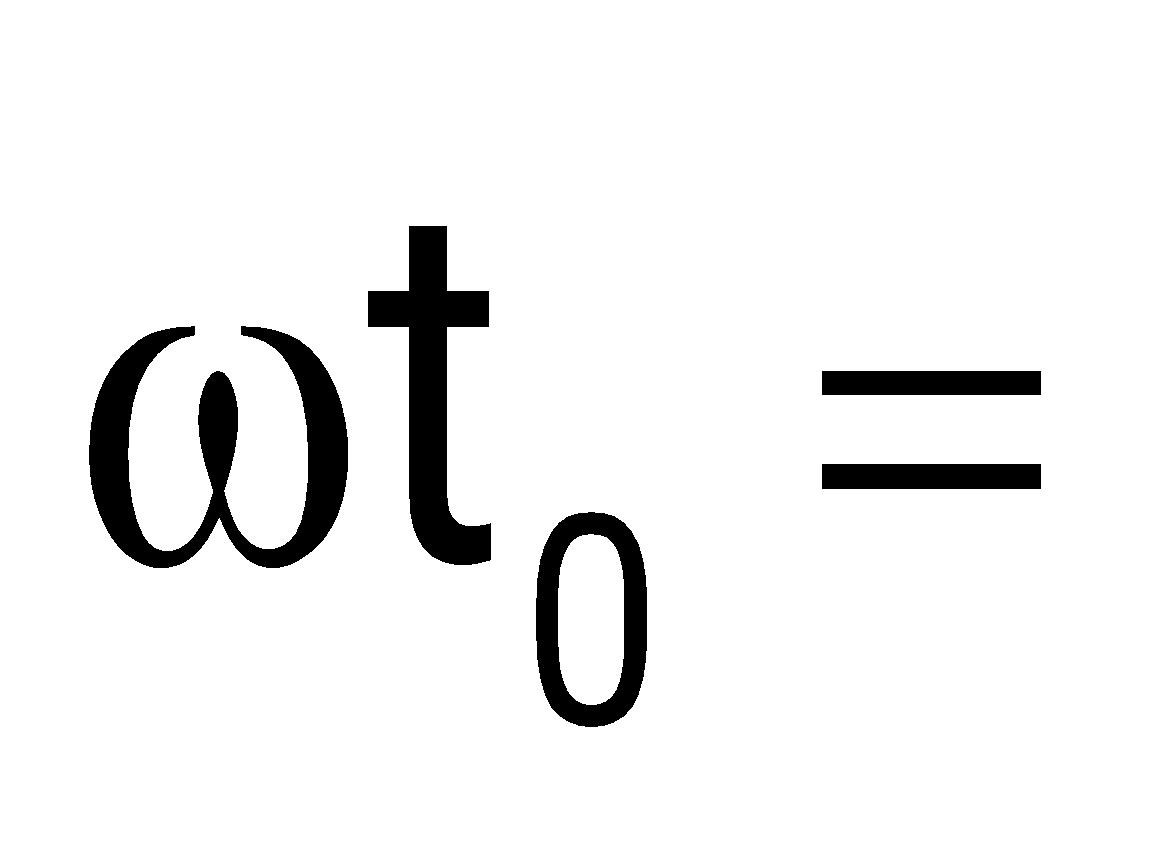

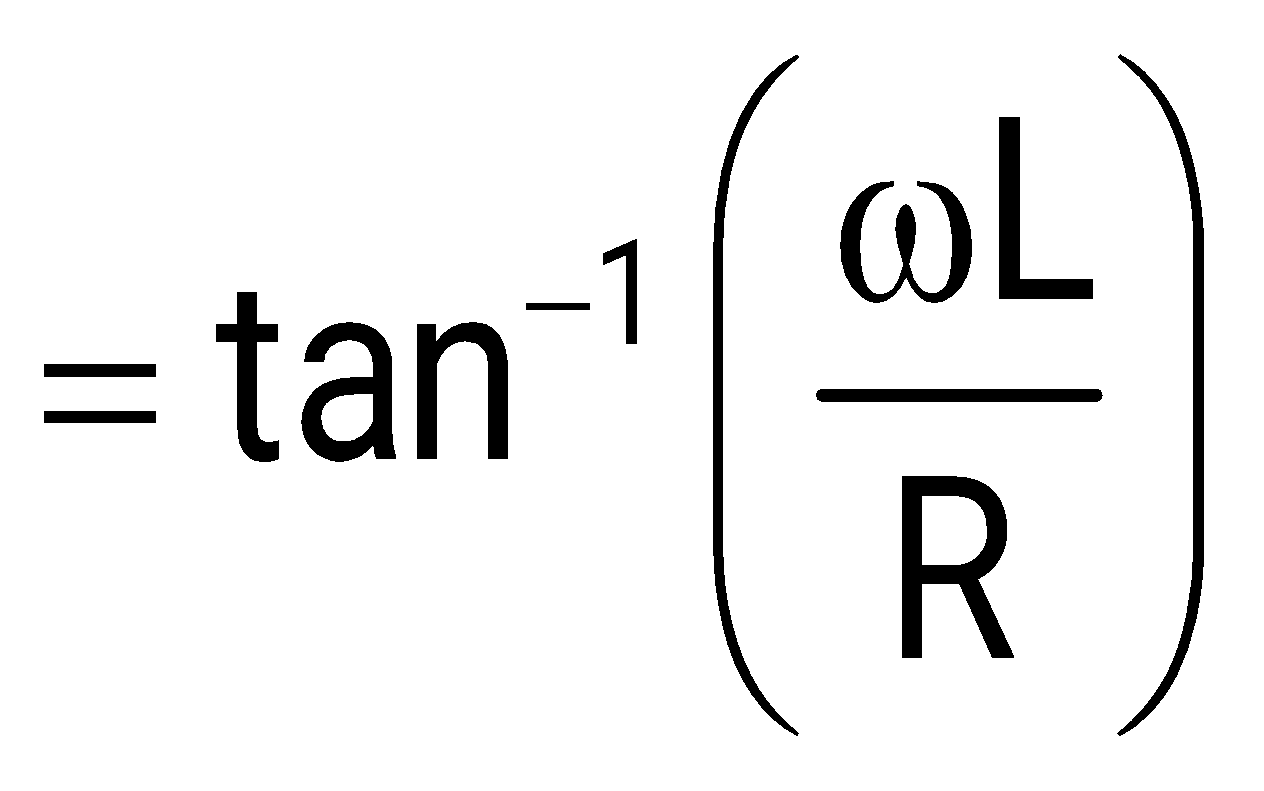

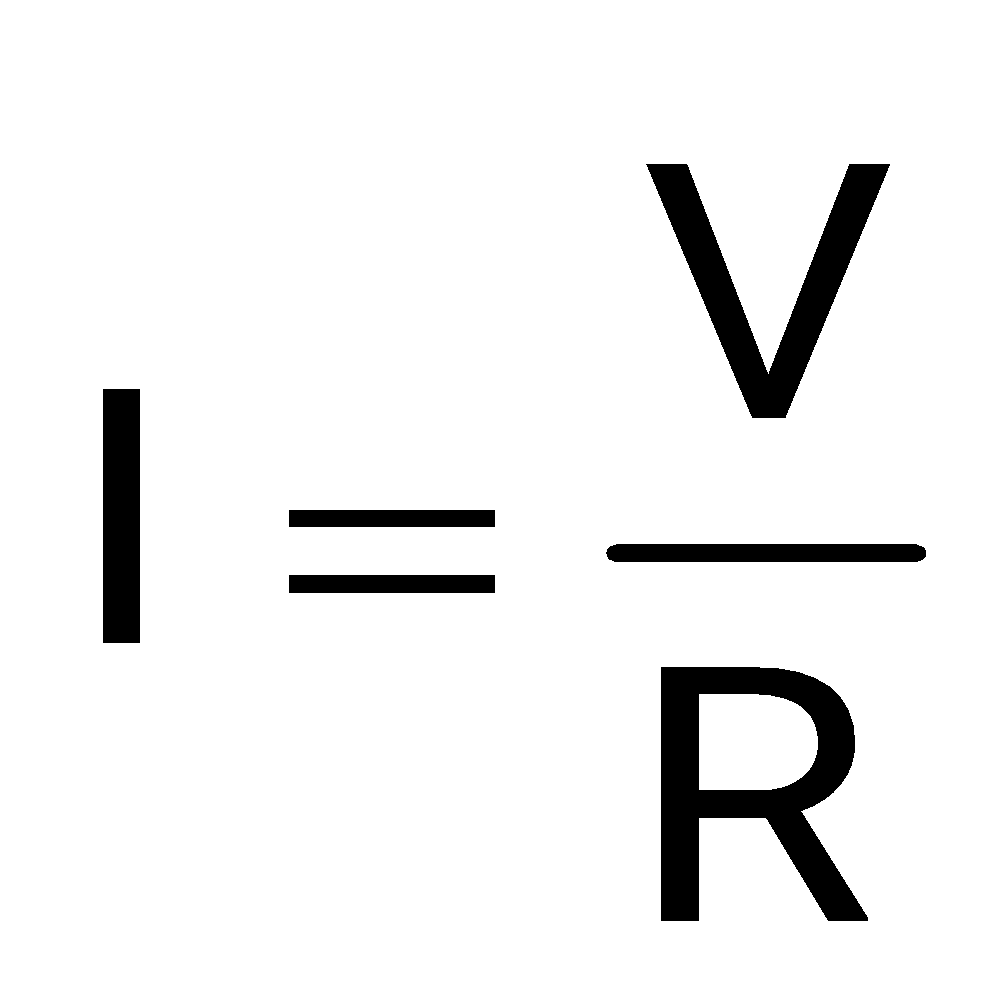

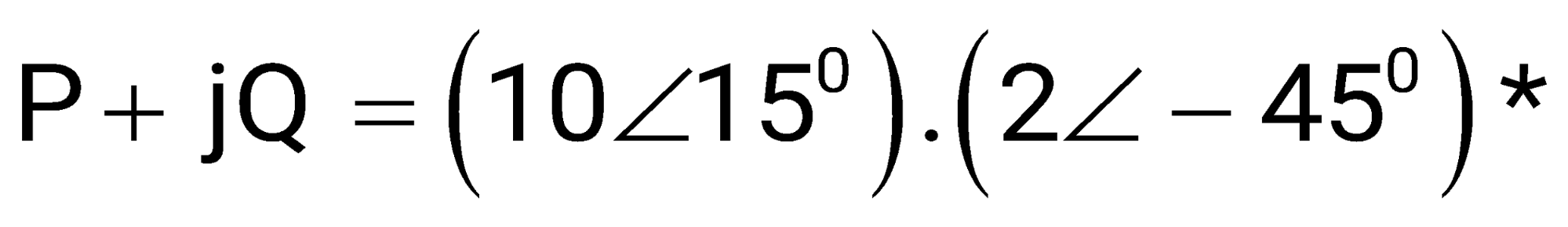

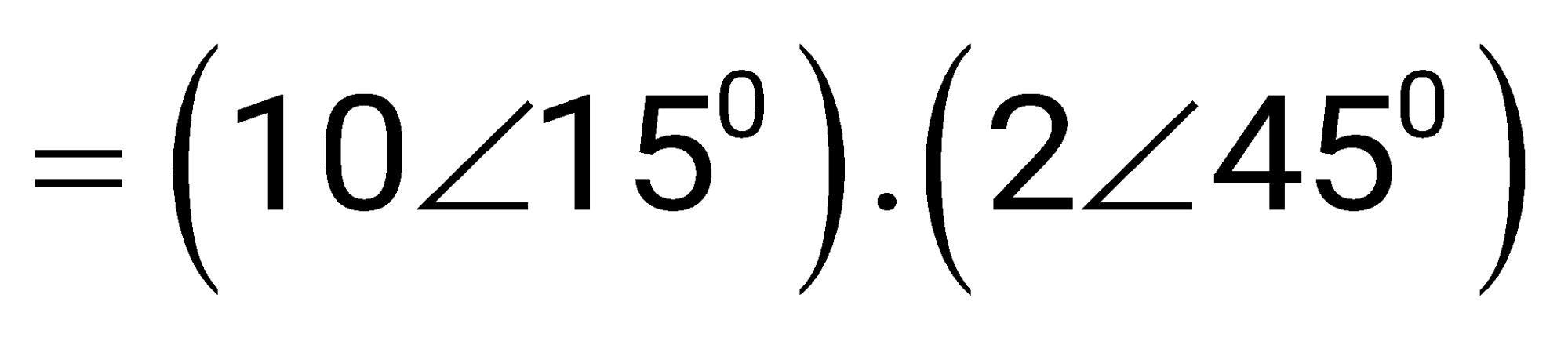

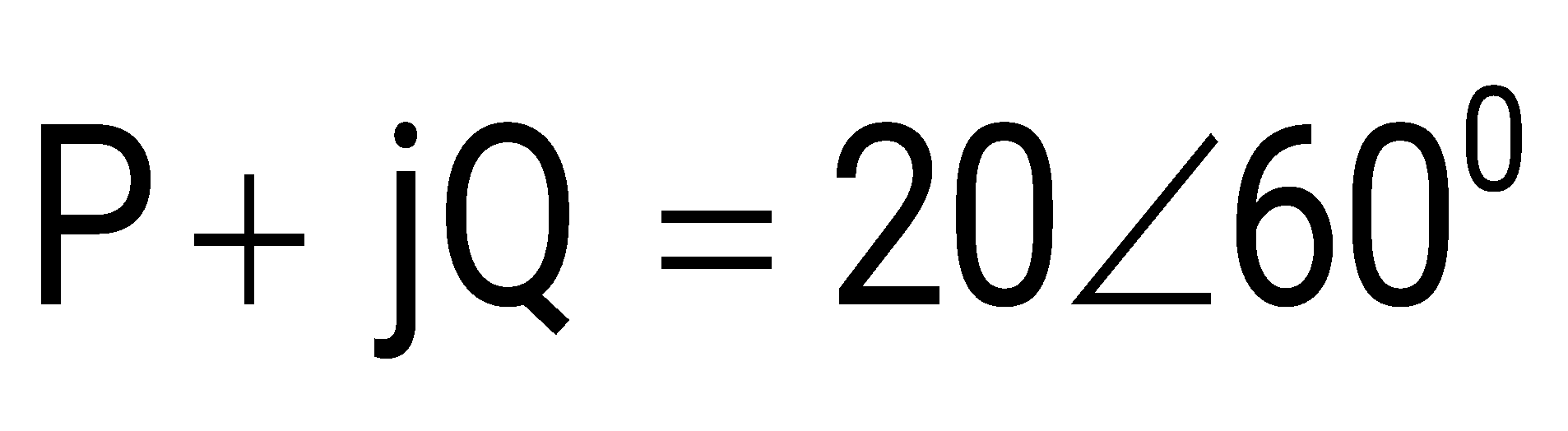

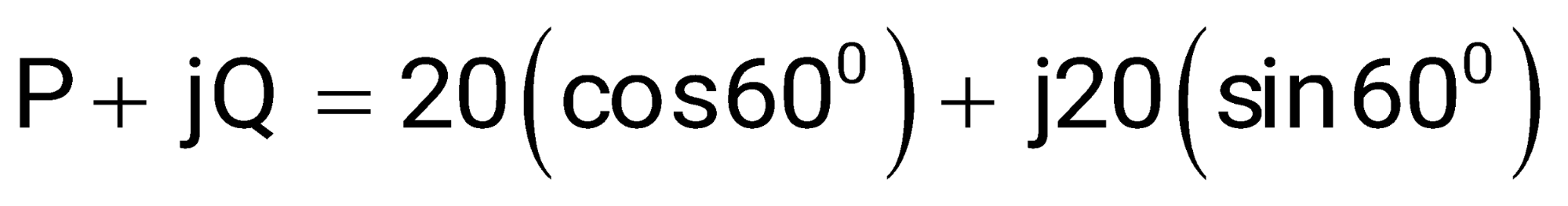

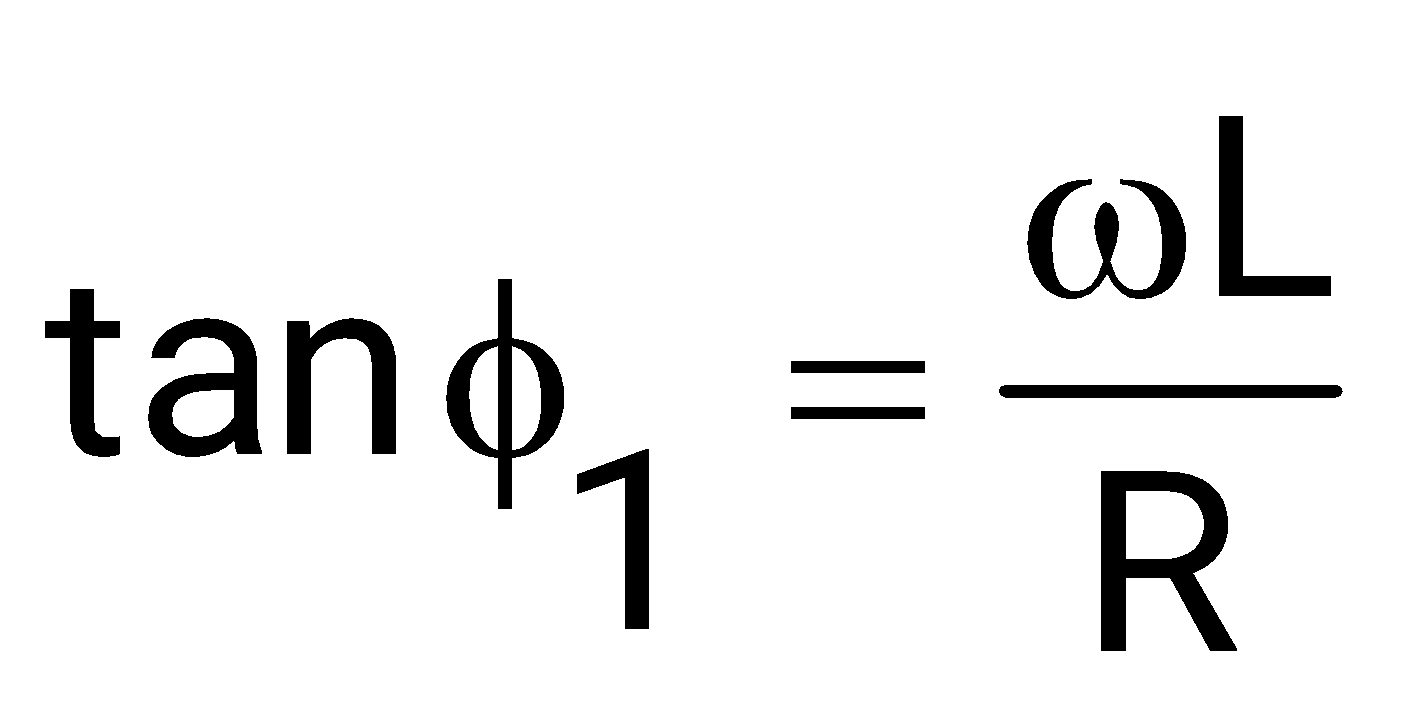

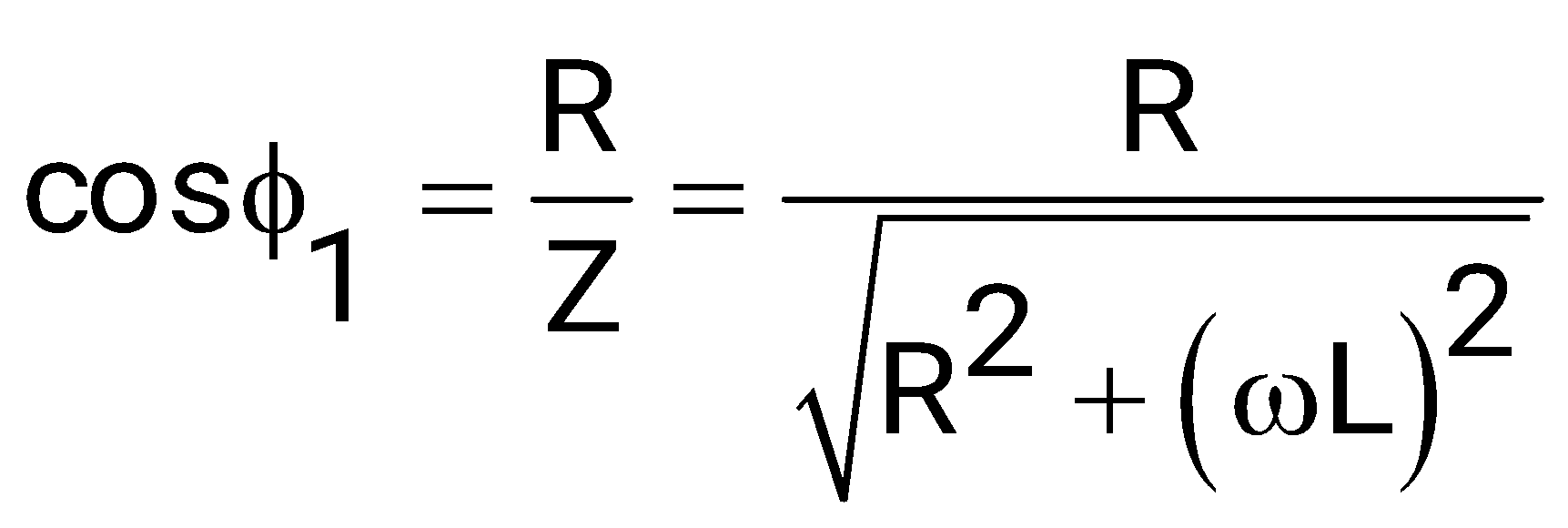

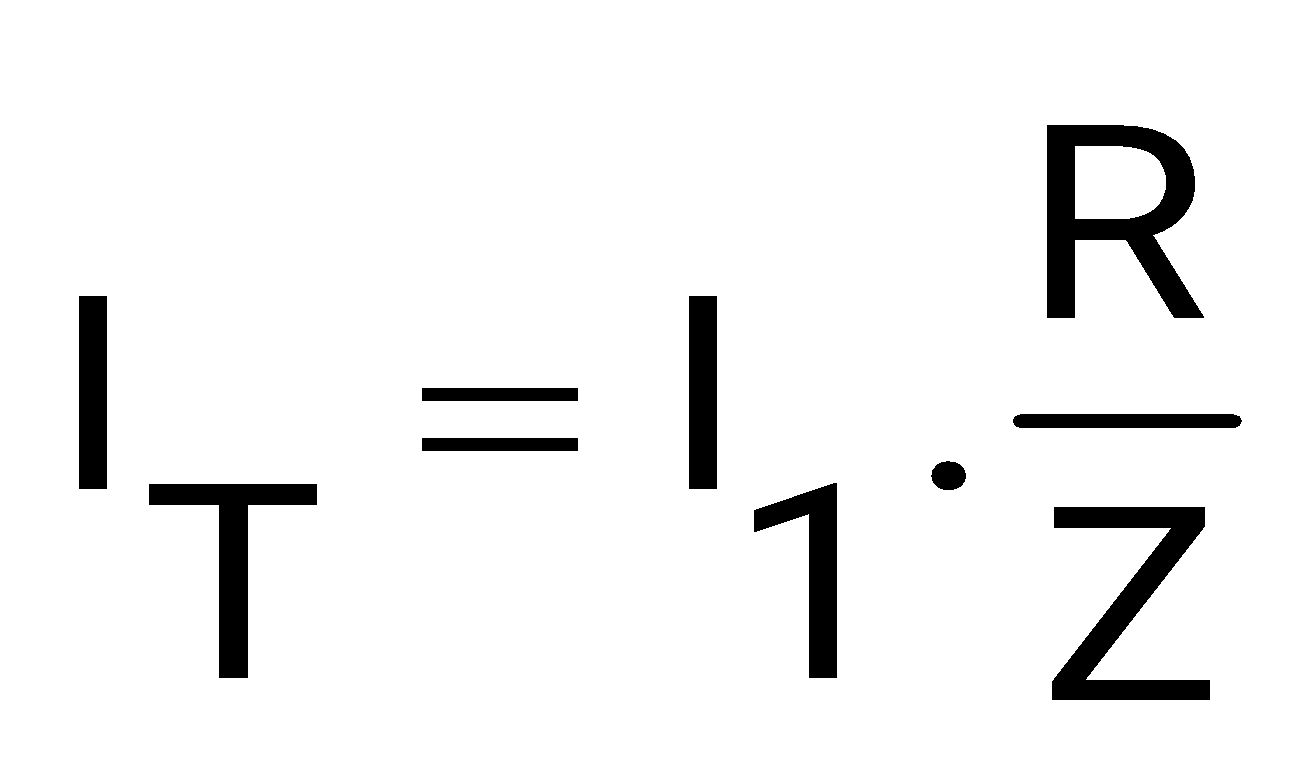

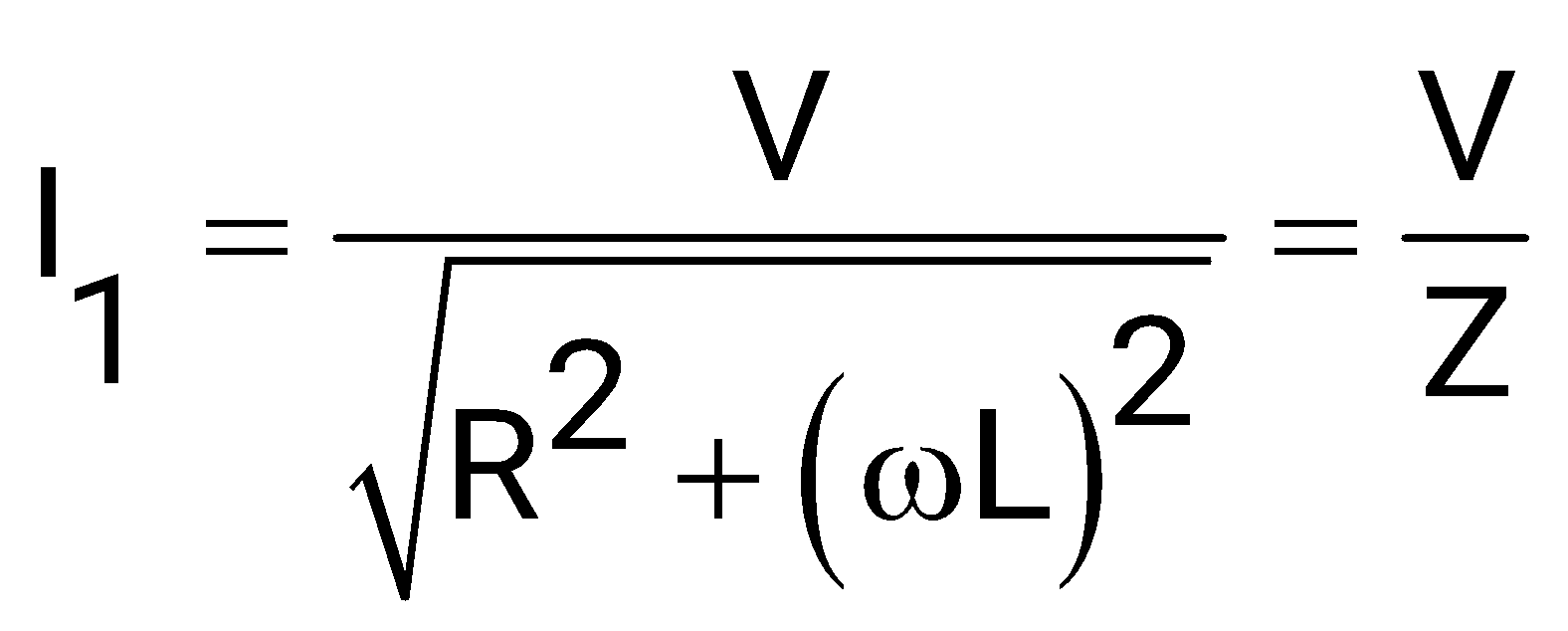

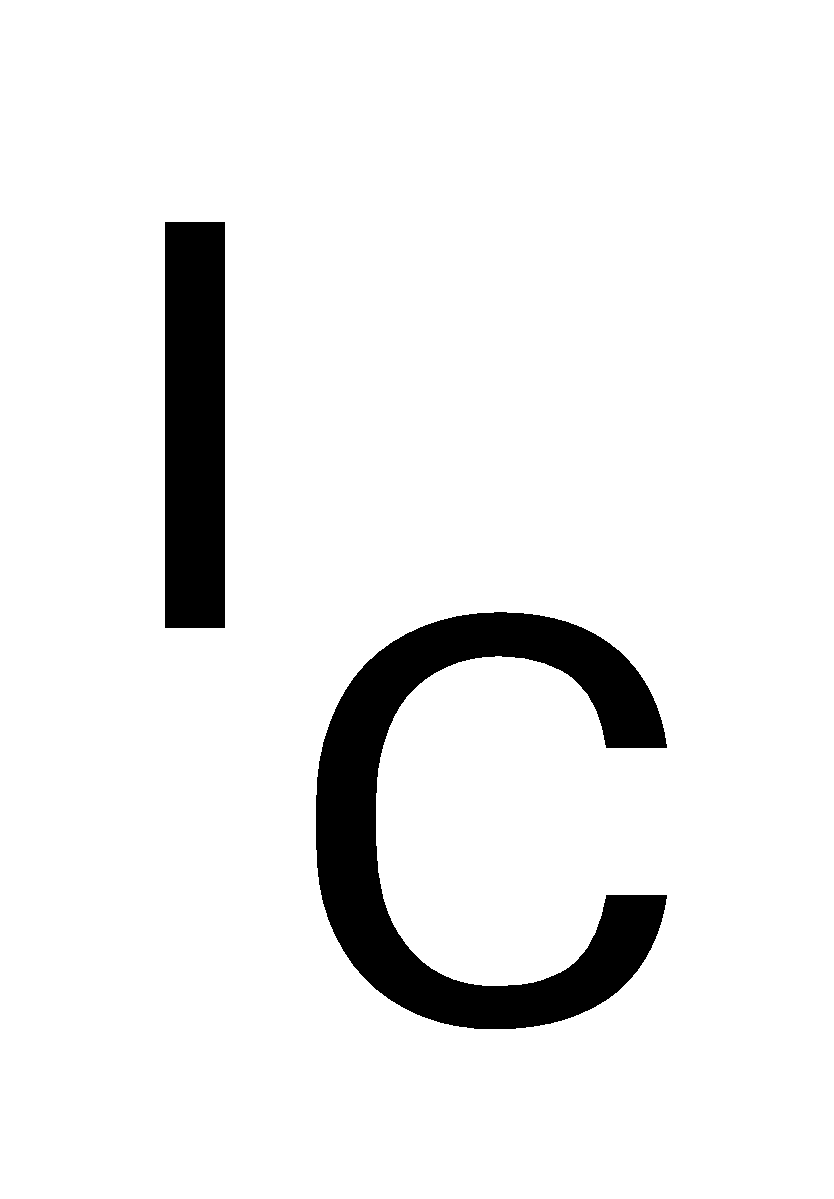

Let be the Load pf angle.

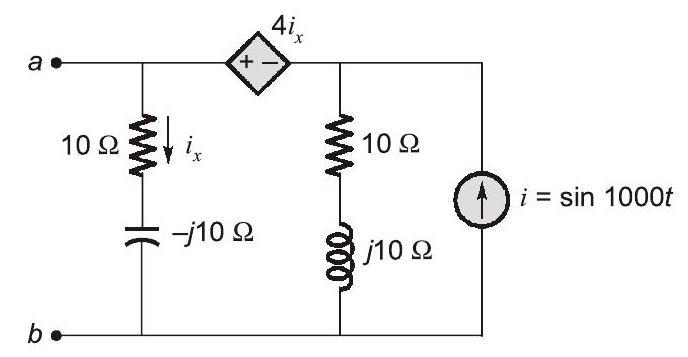

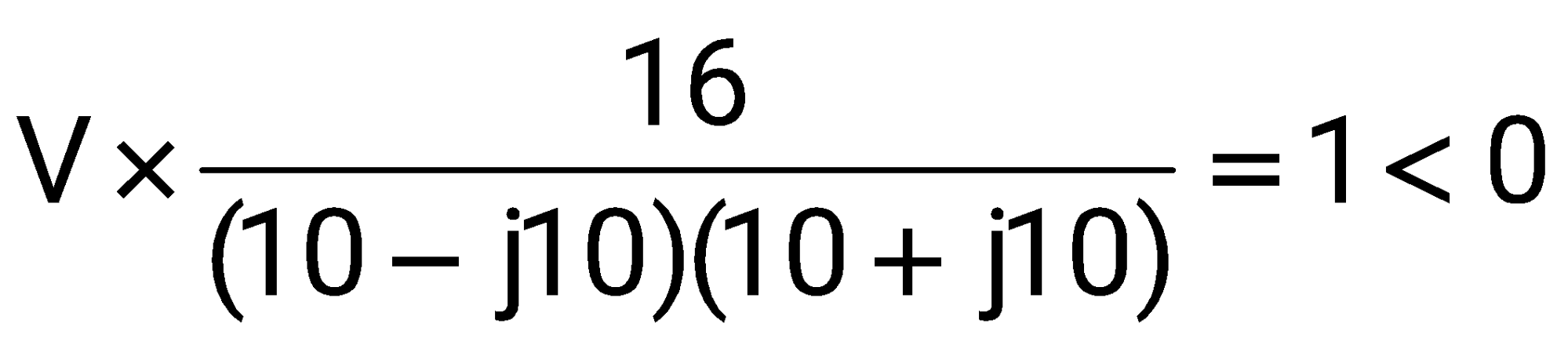

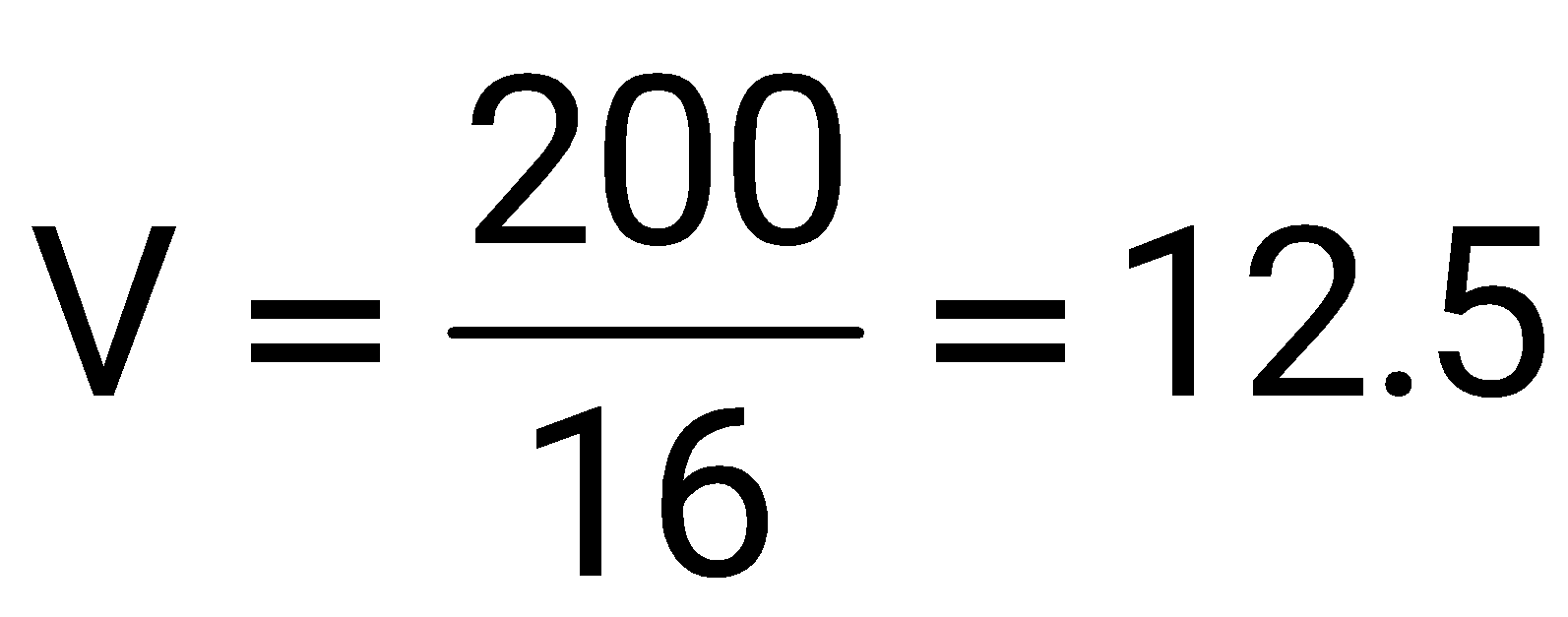

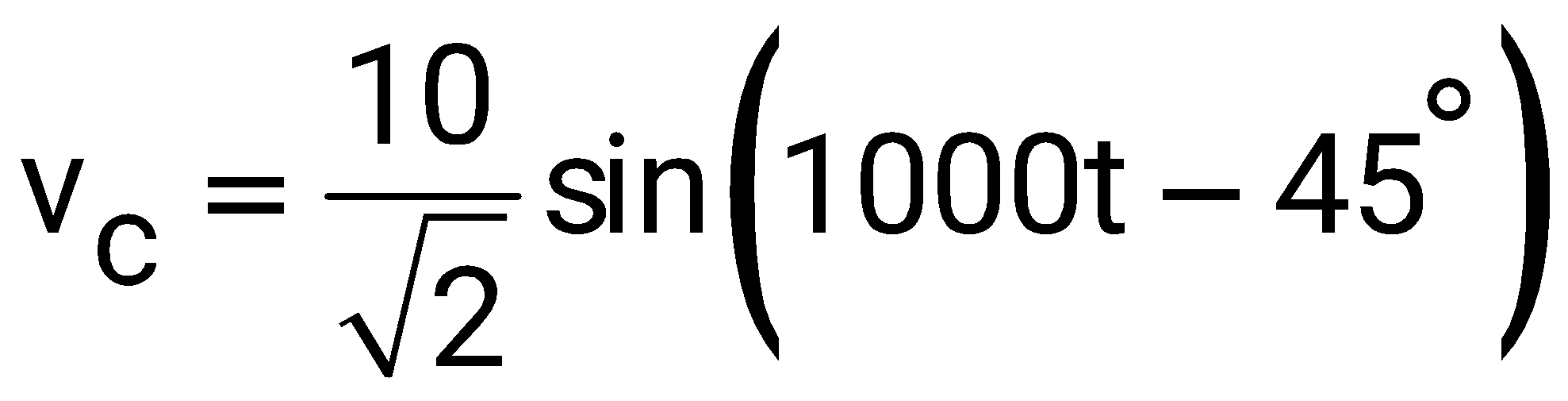

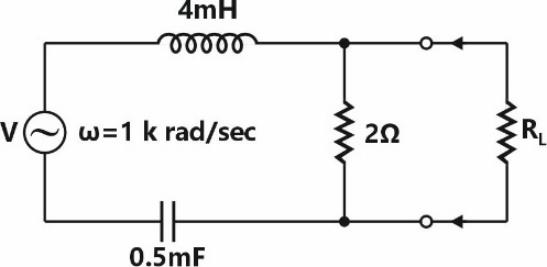

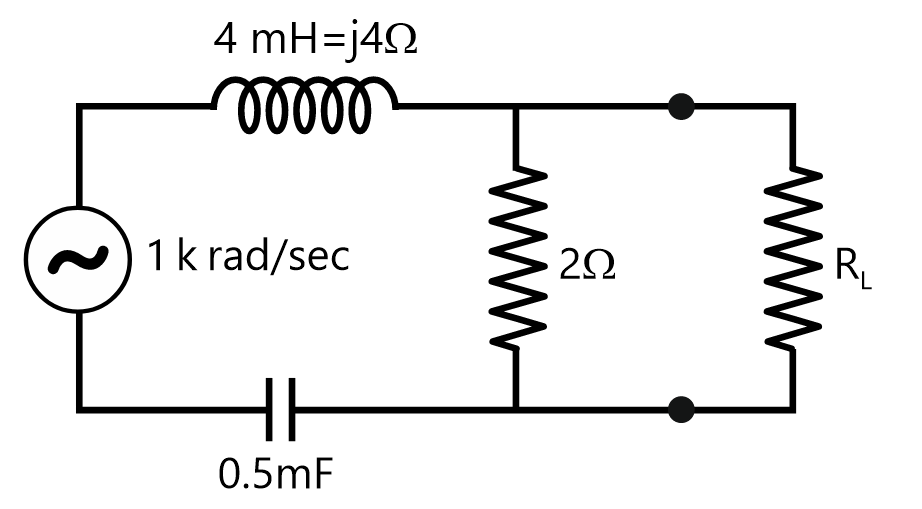

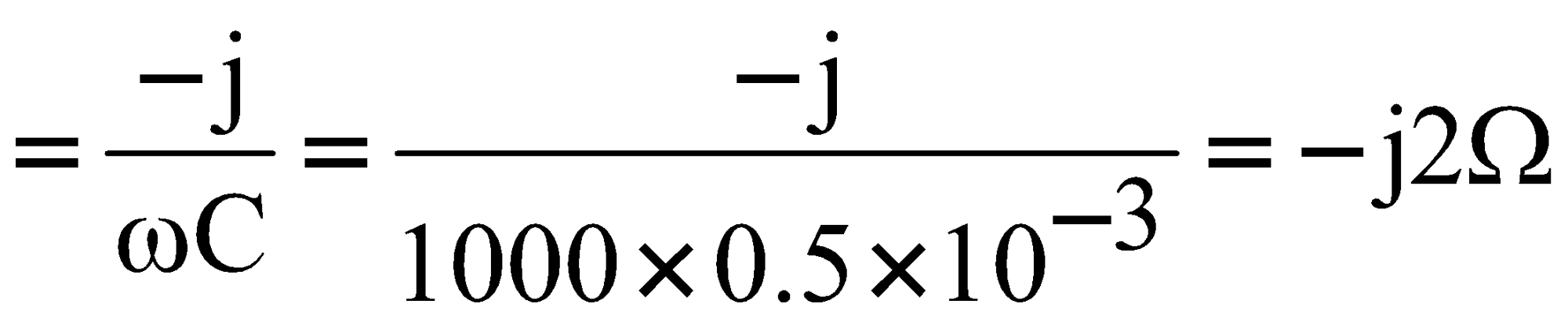

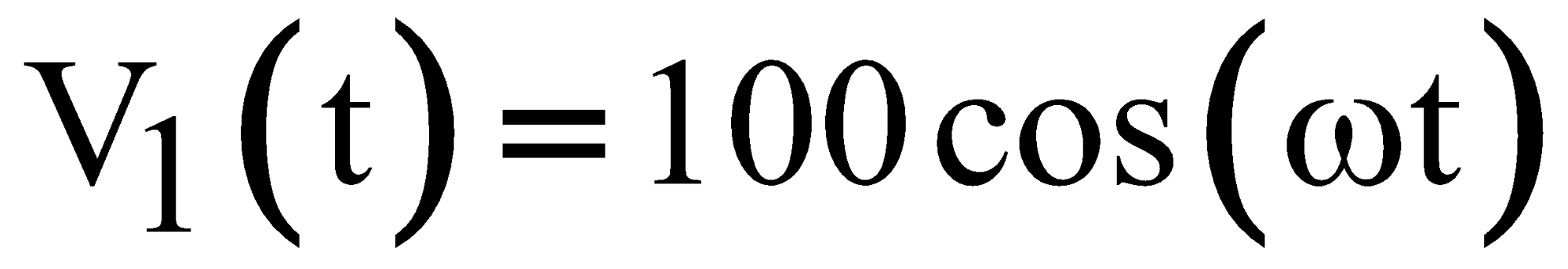

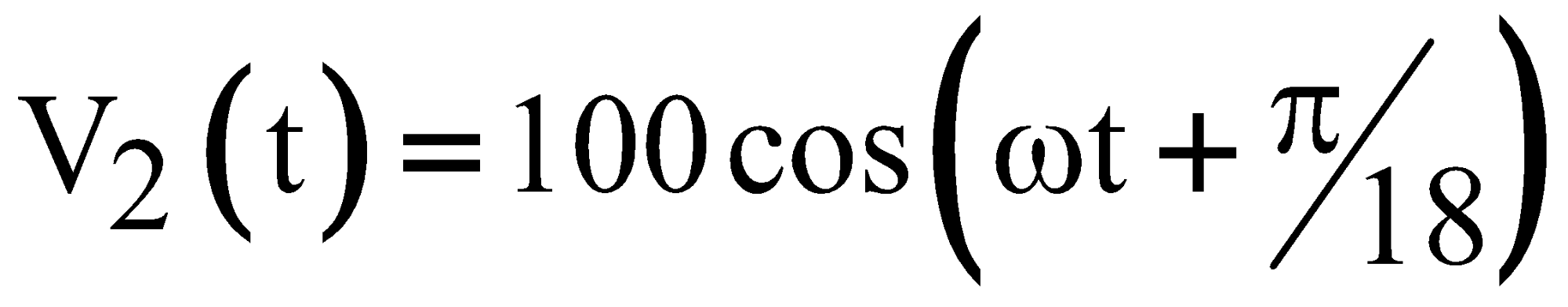

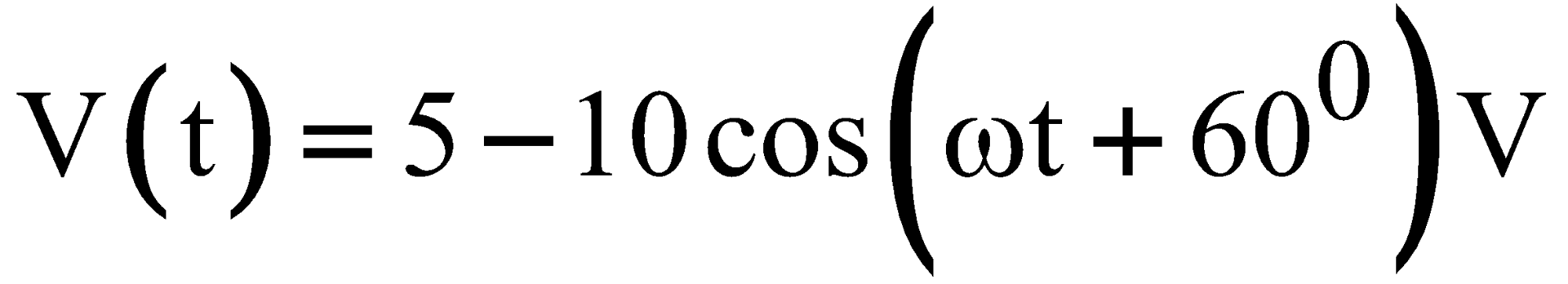

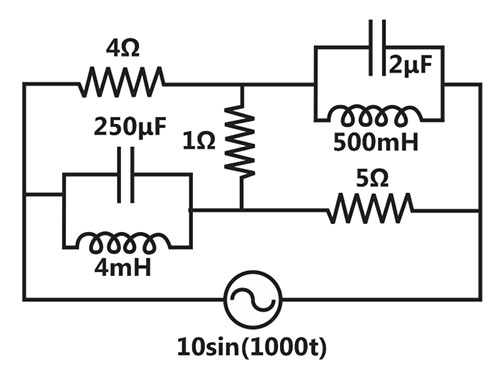

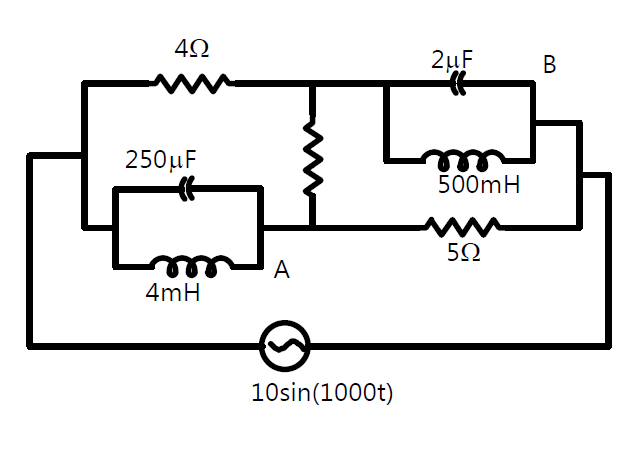

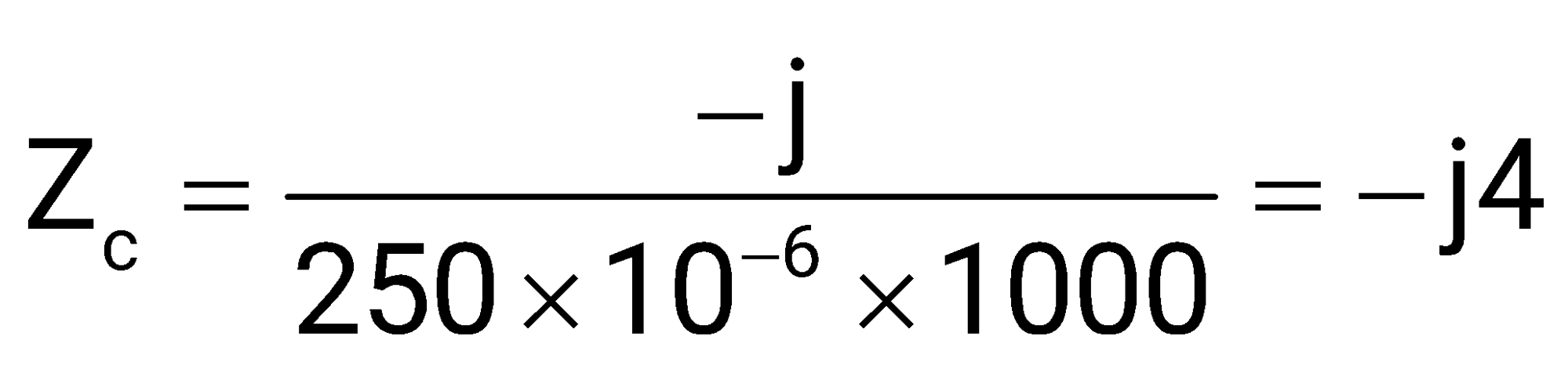

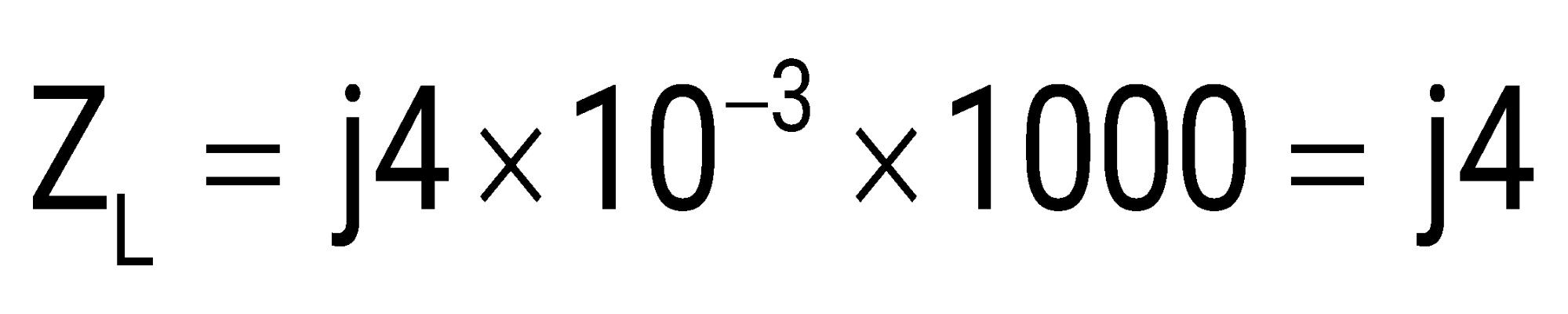

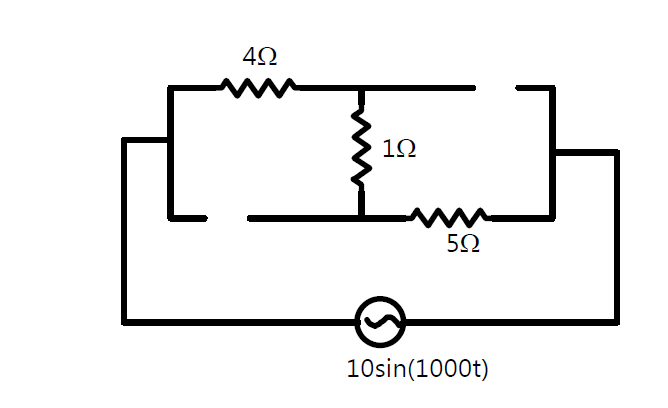

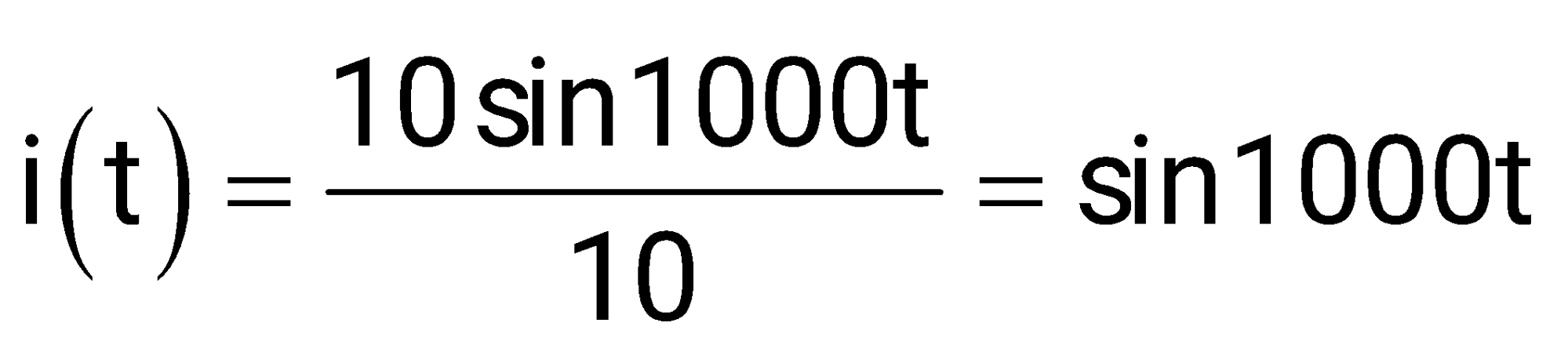

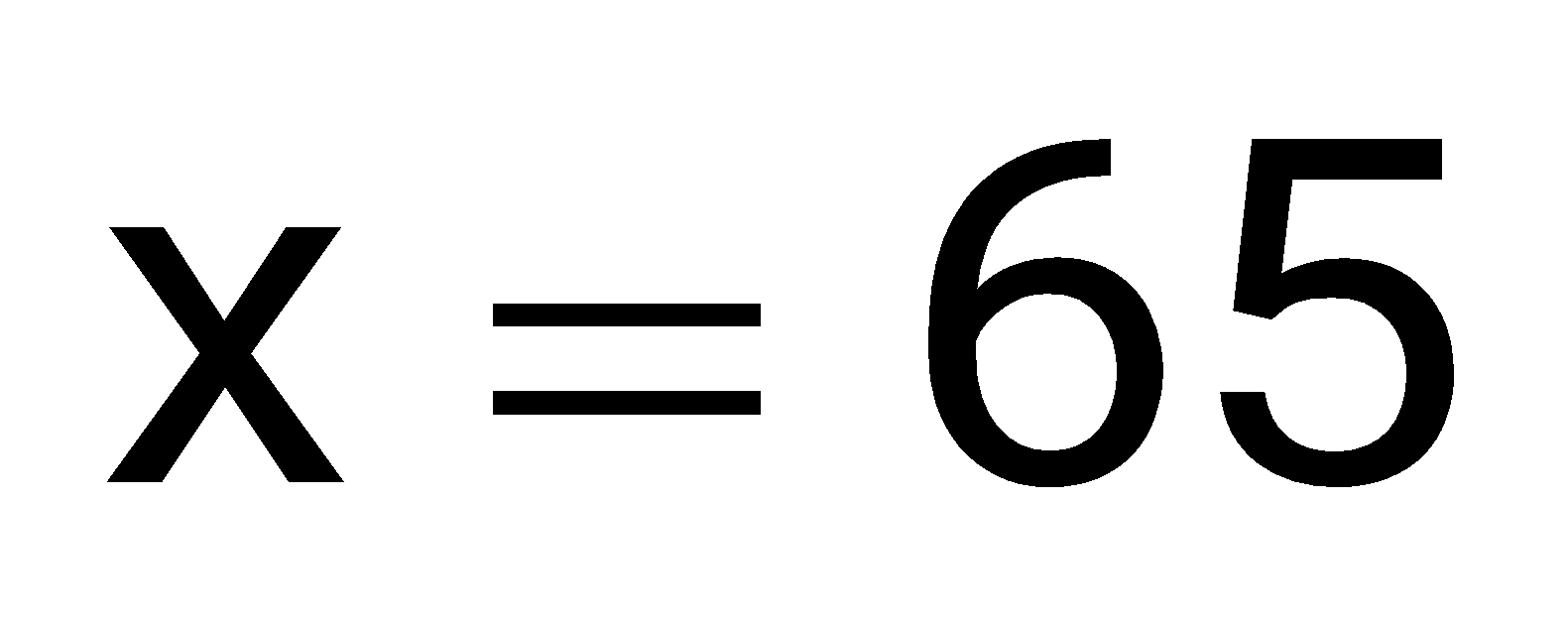

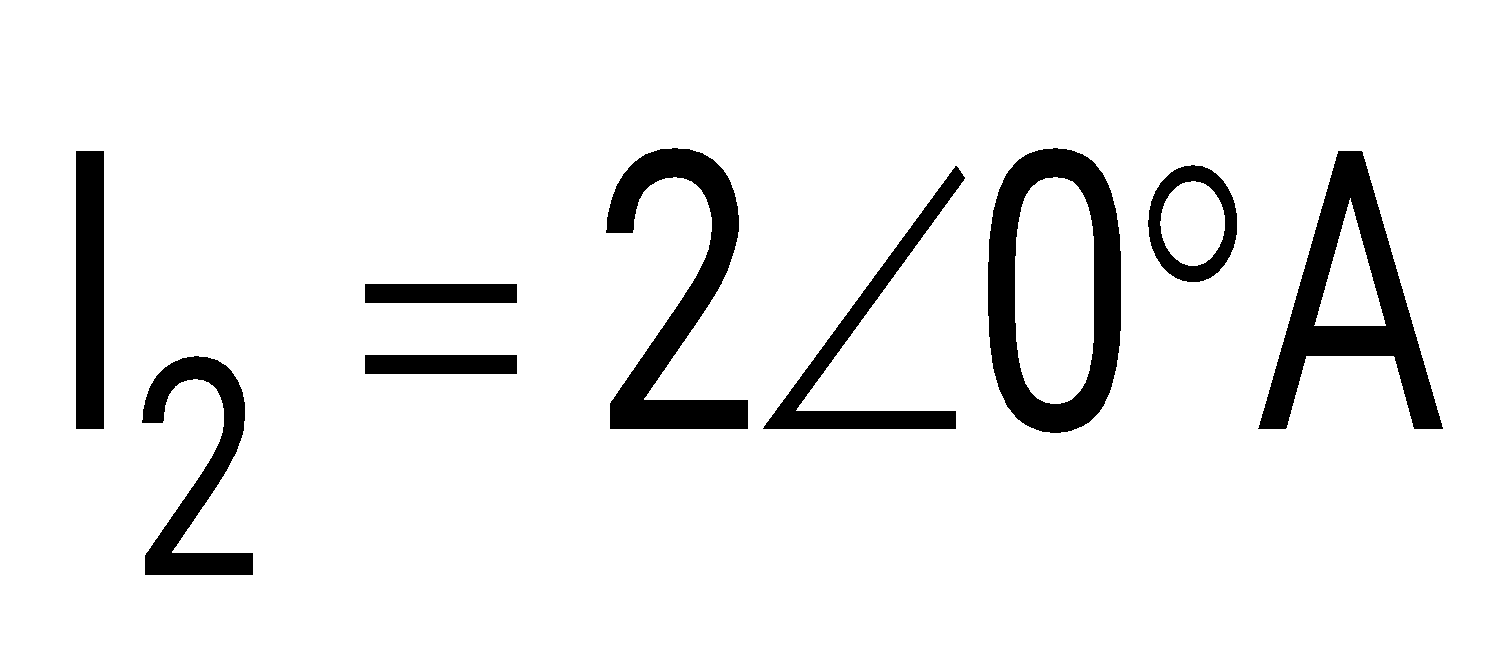

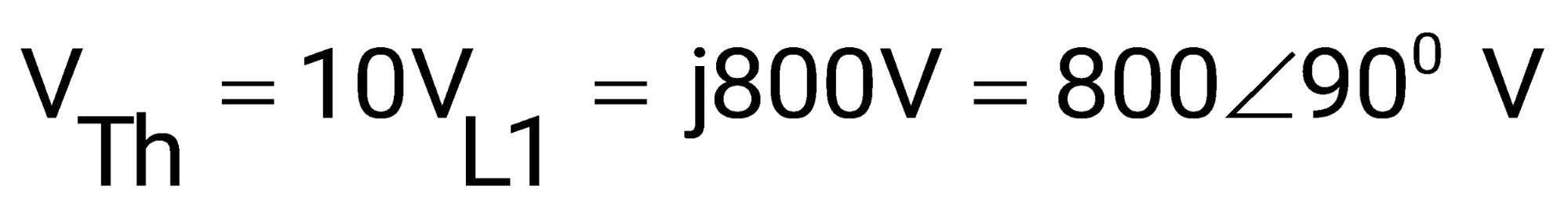

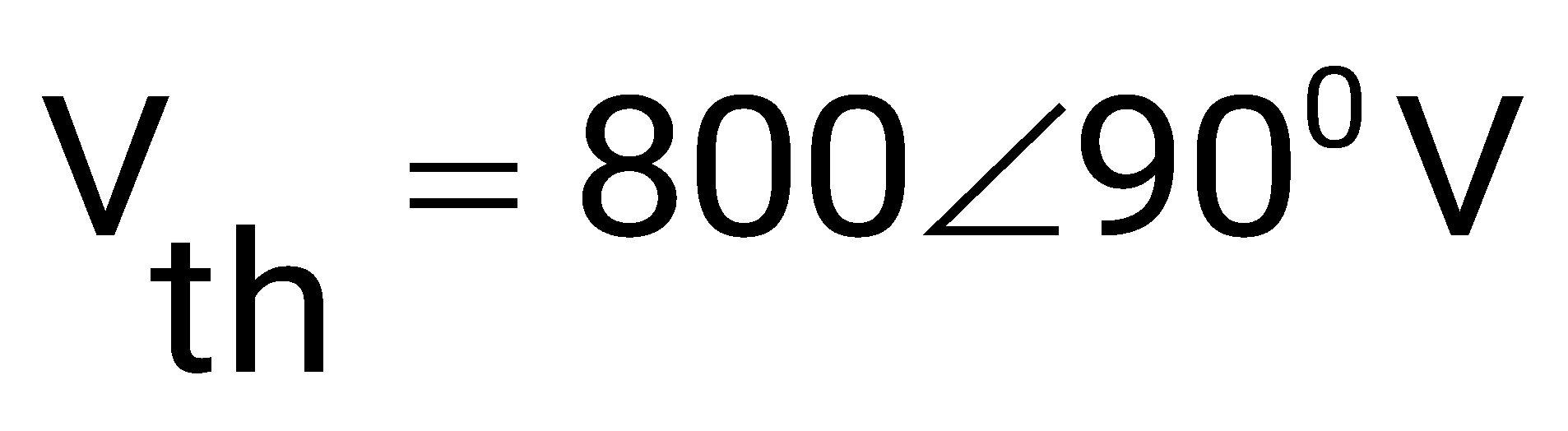

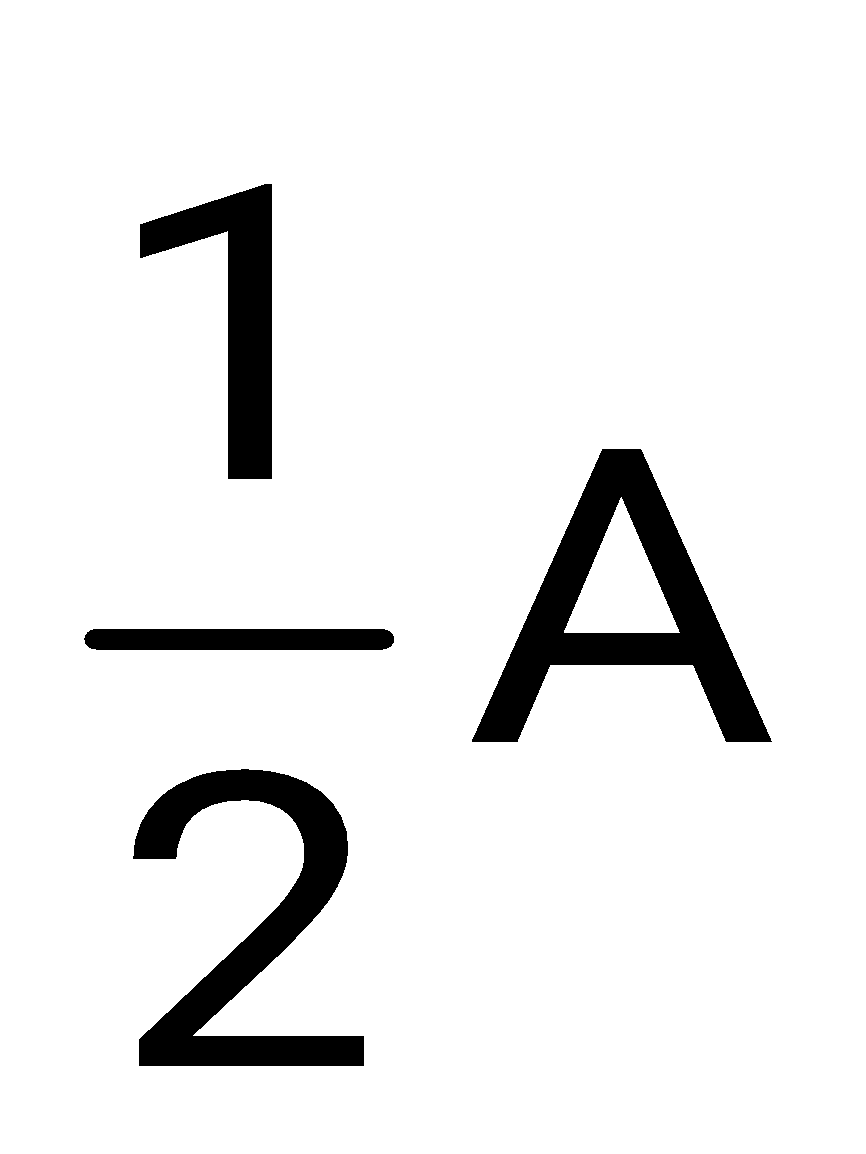

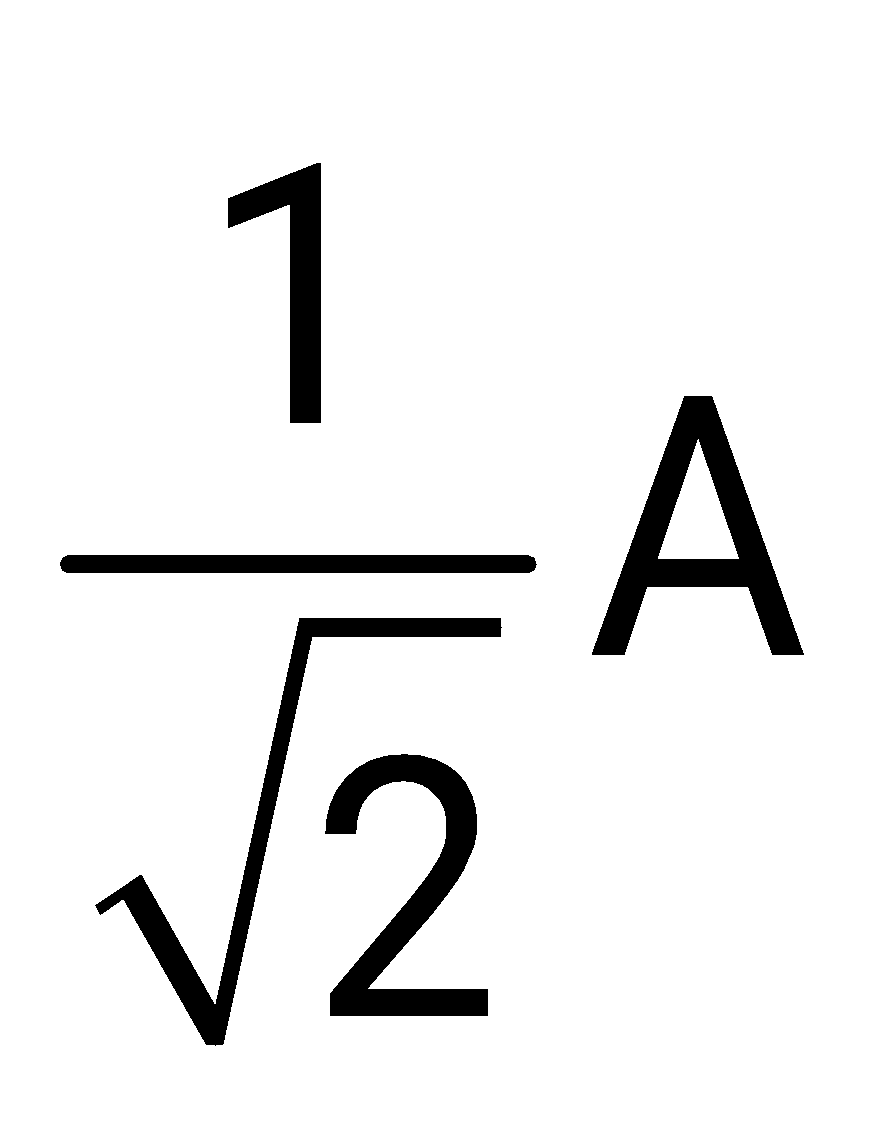

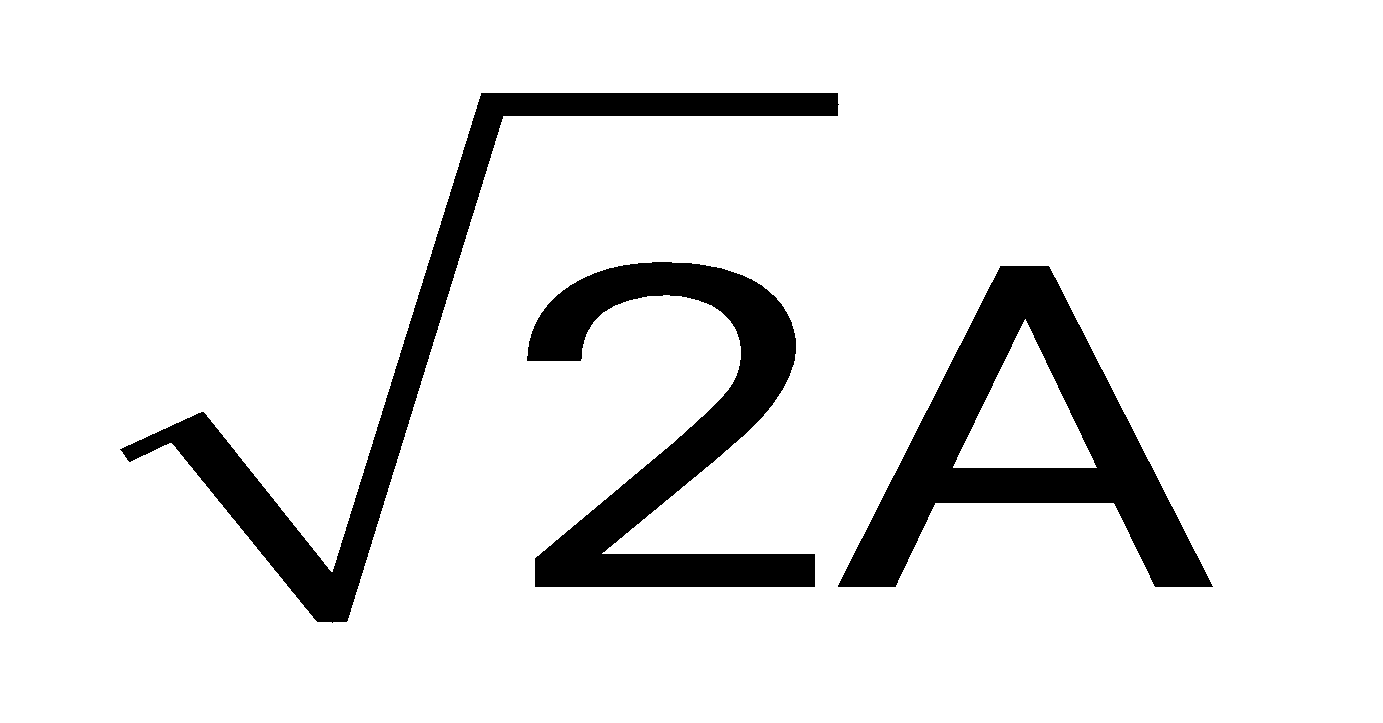

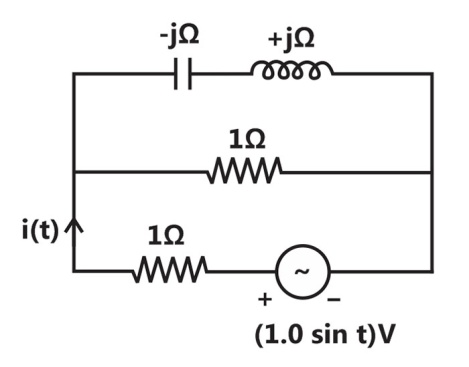

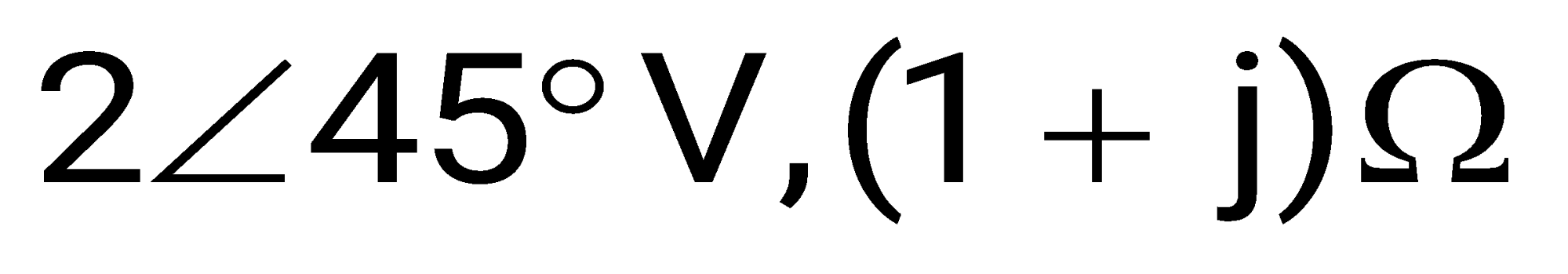

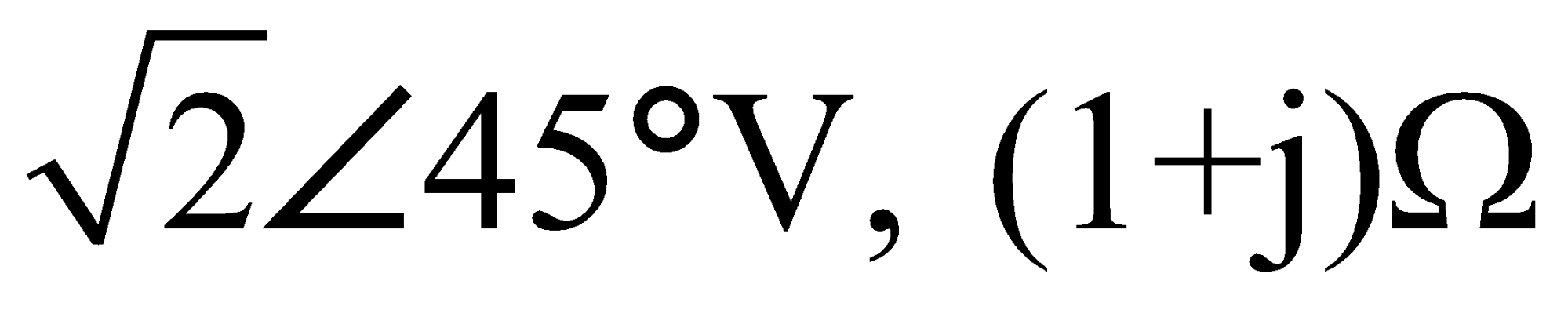

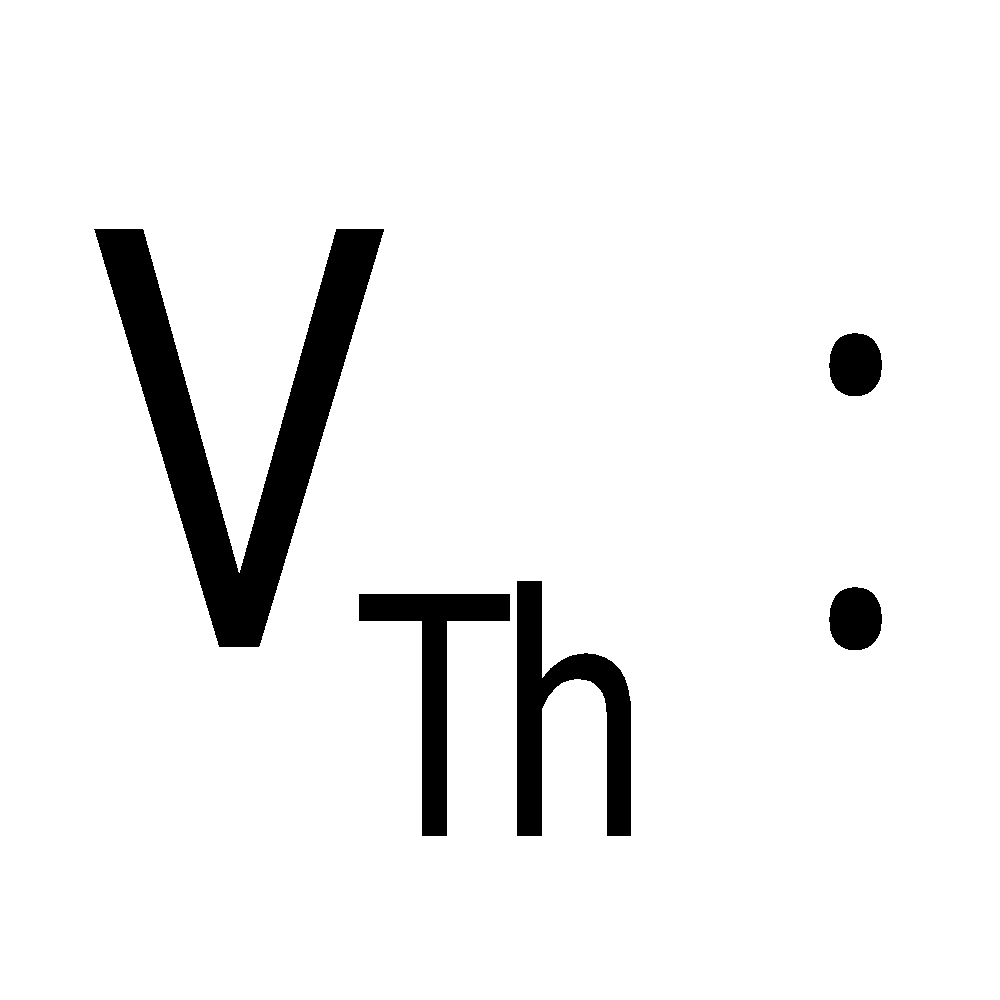

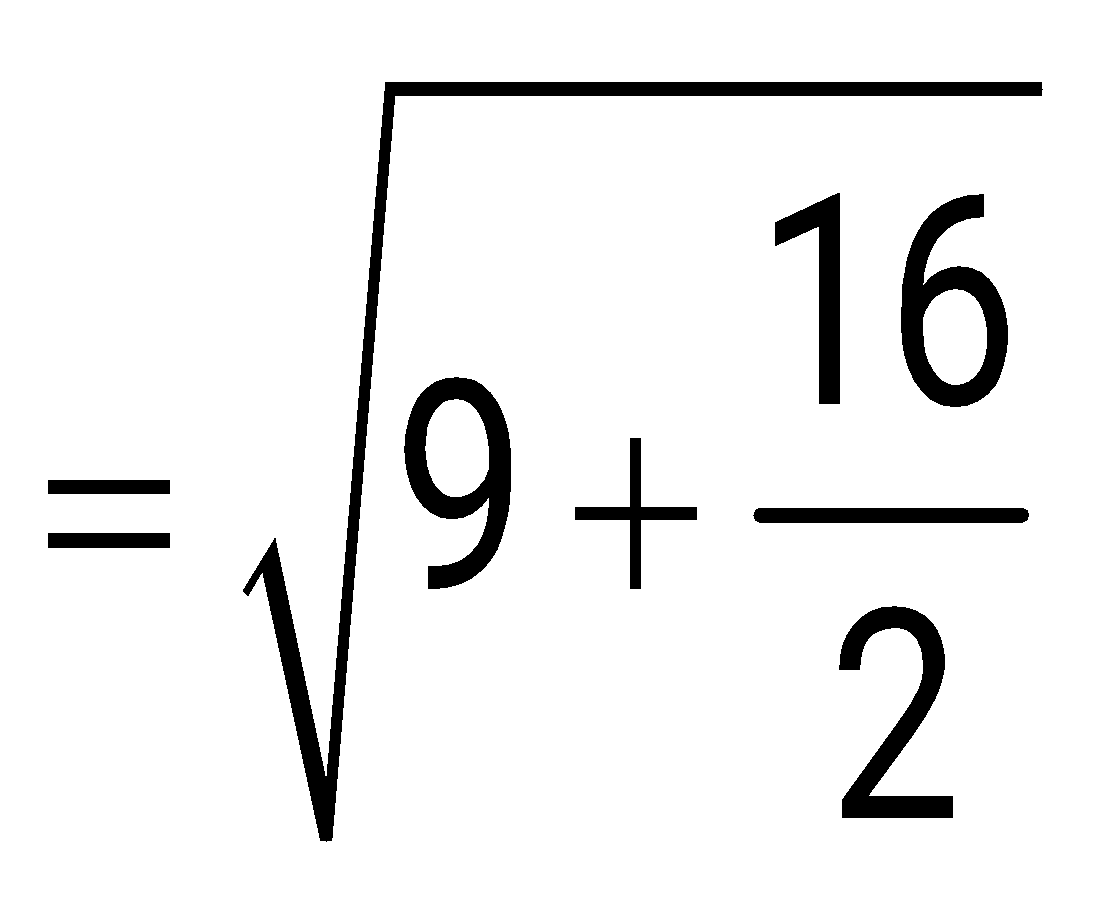

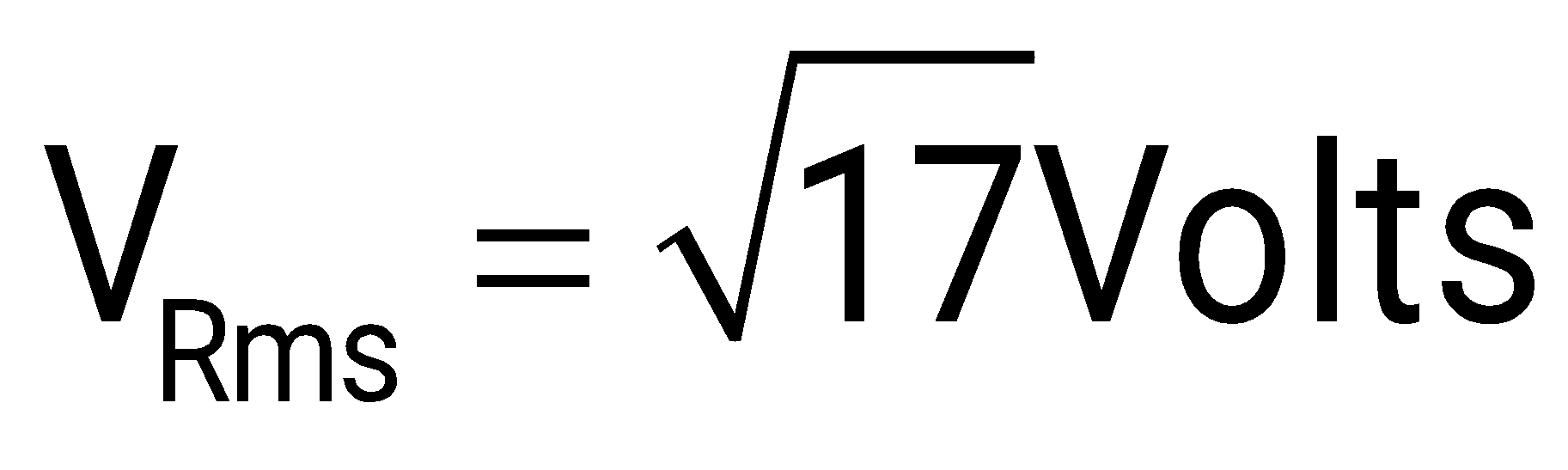

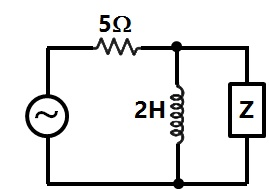

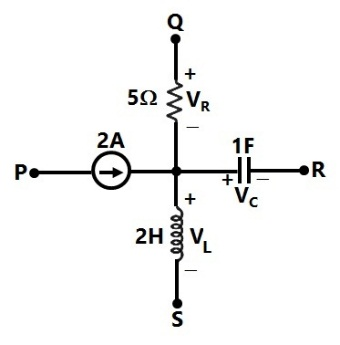

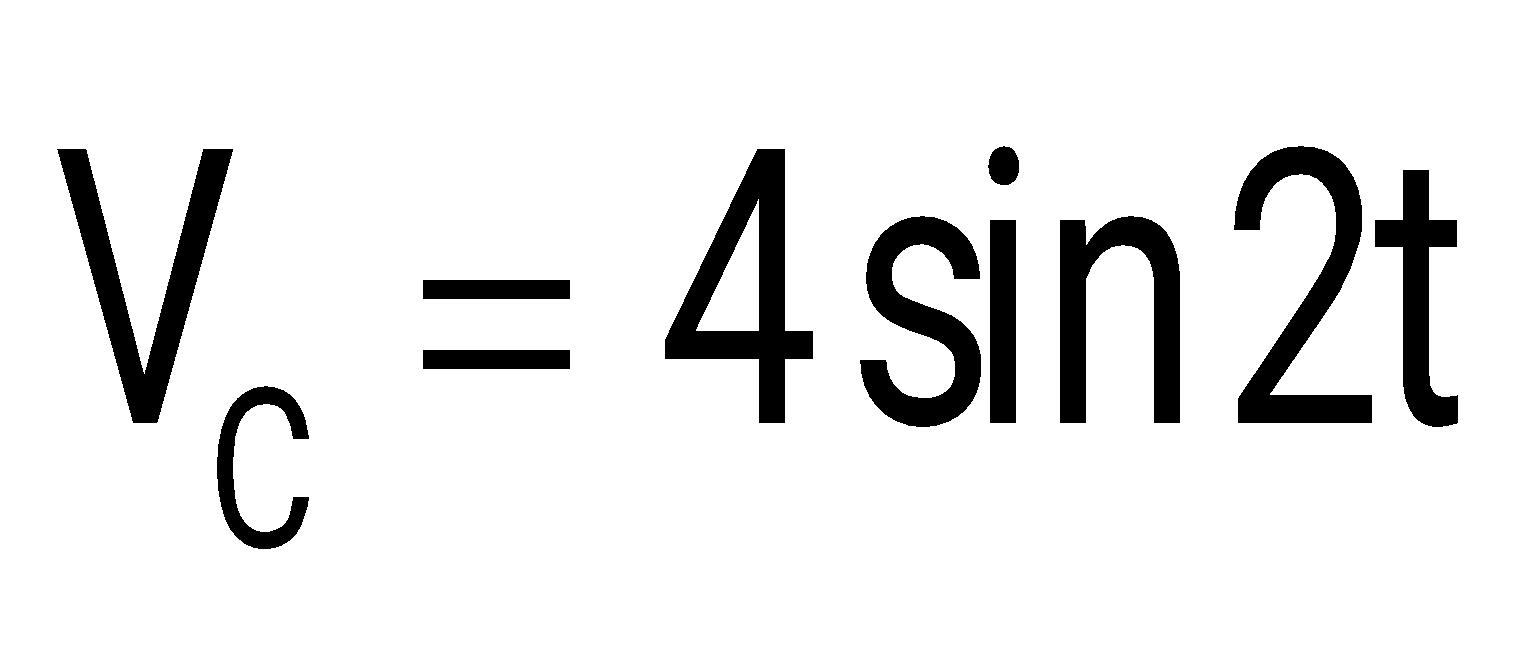

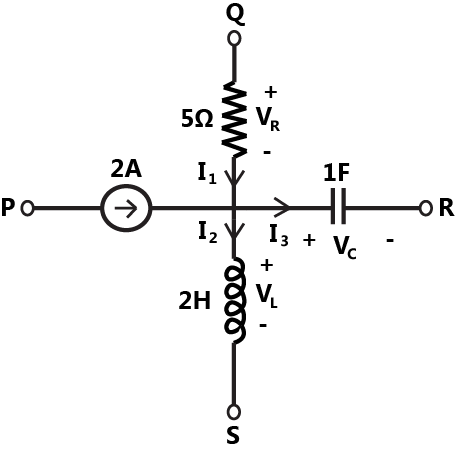

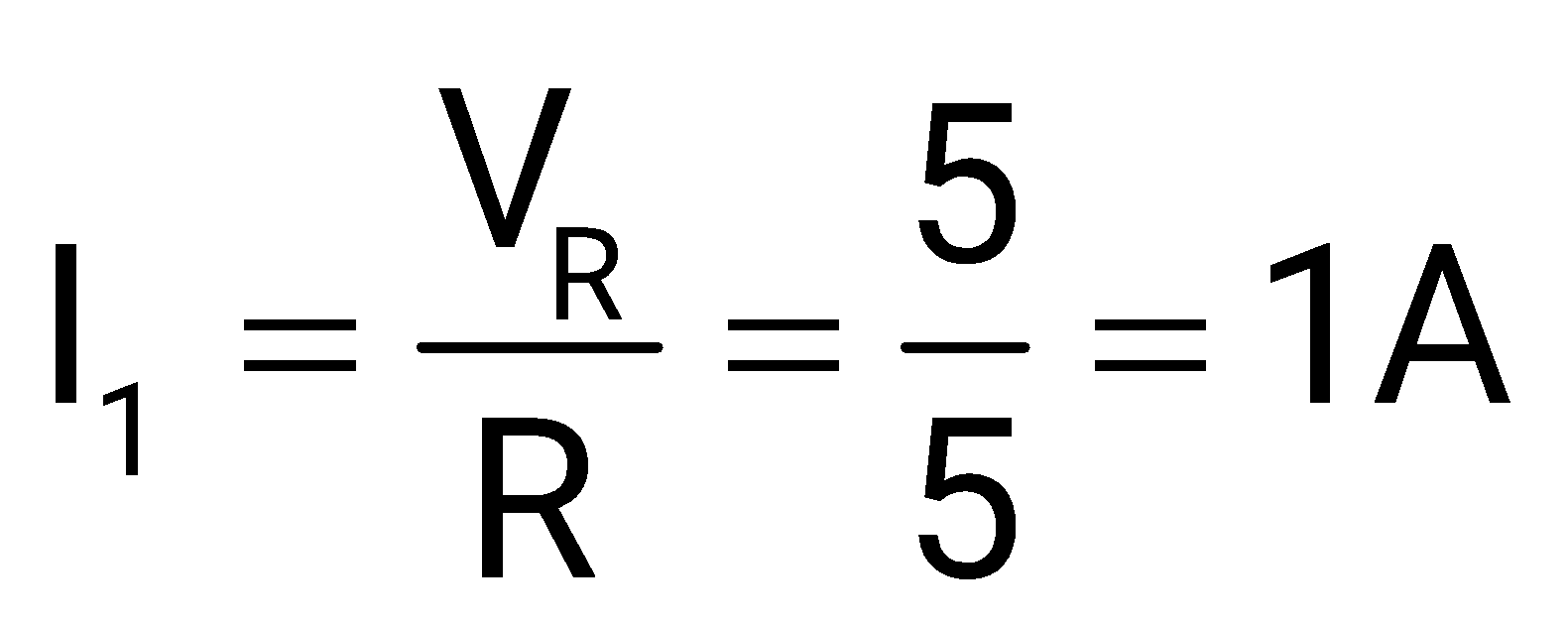

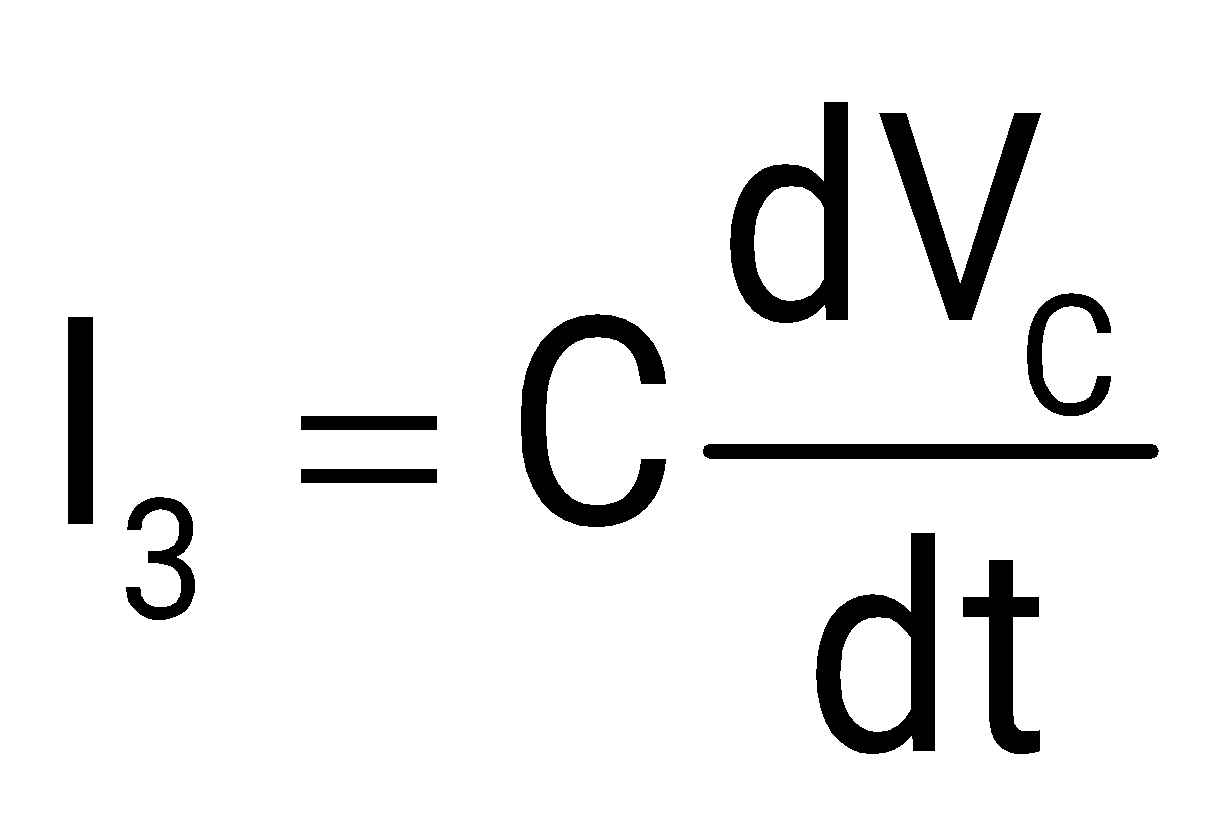

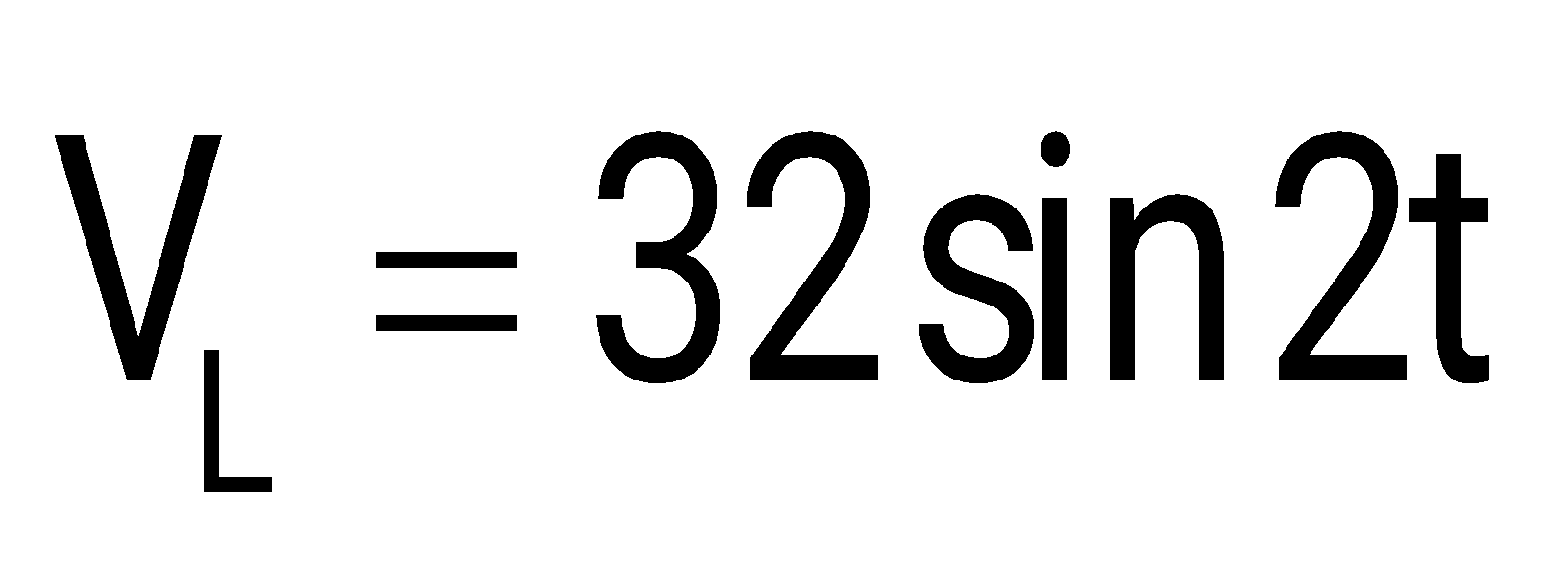

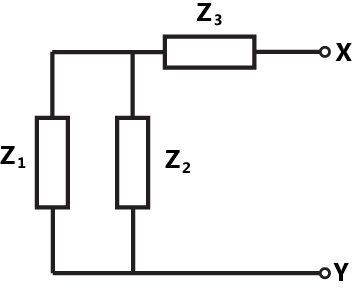

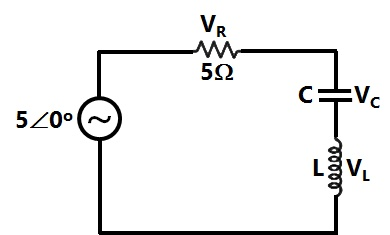

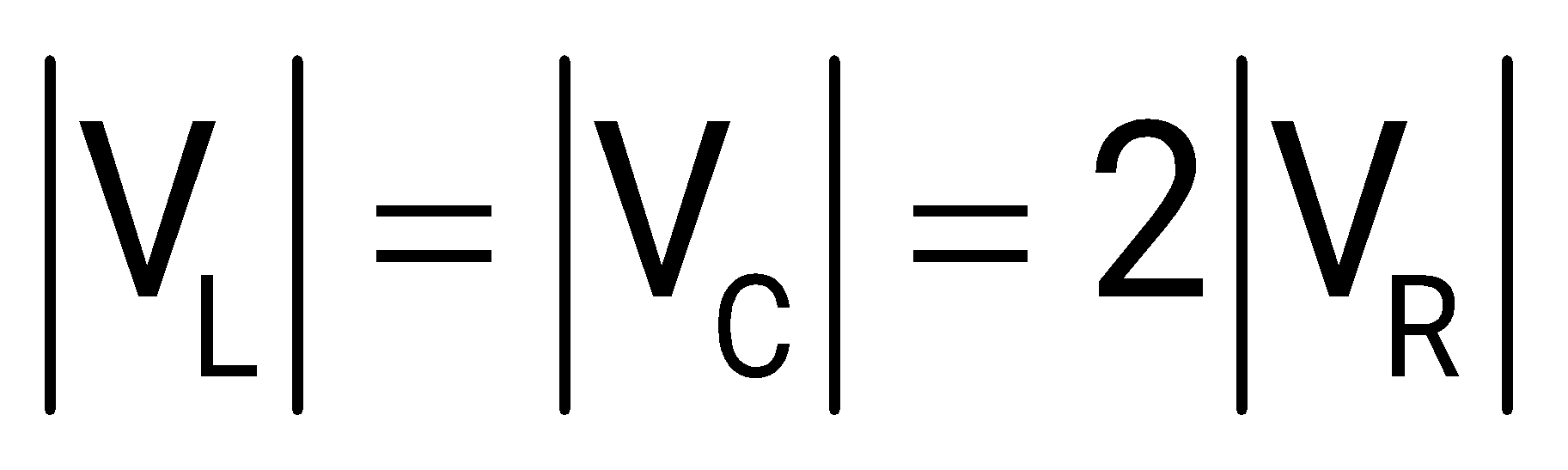

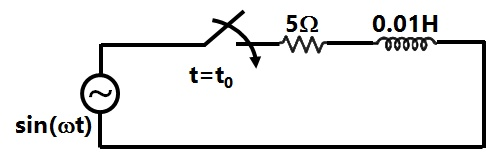

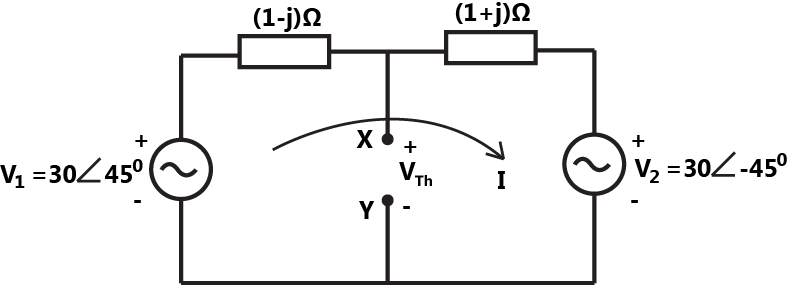

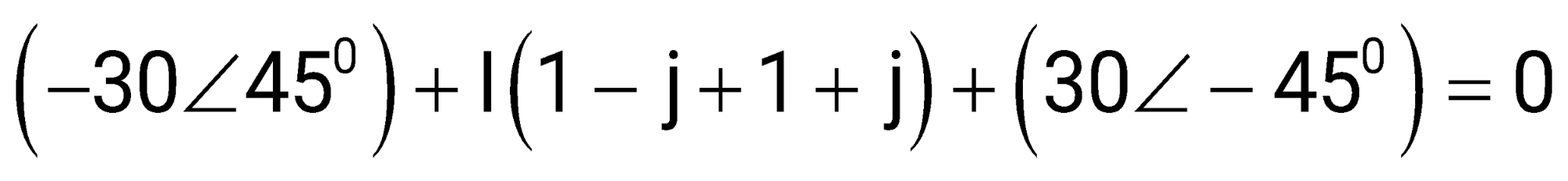

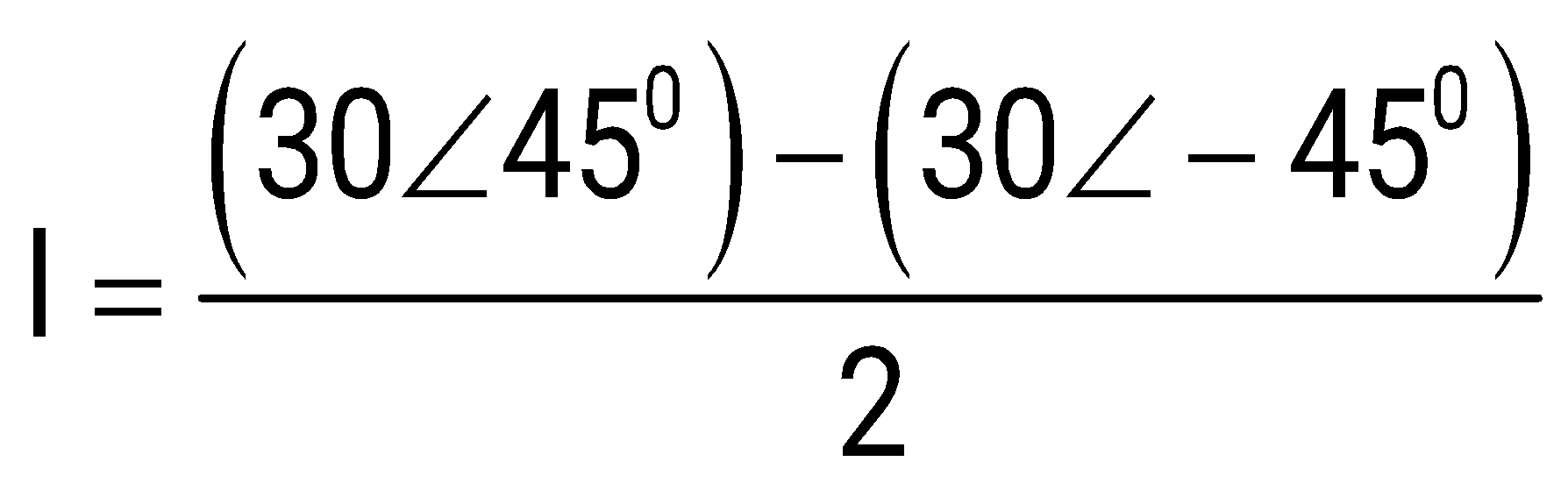

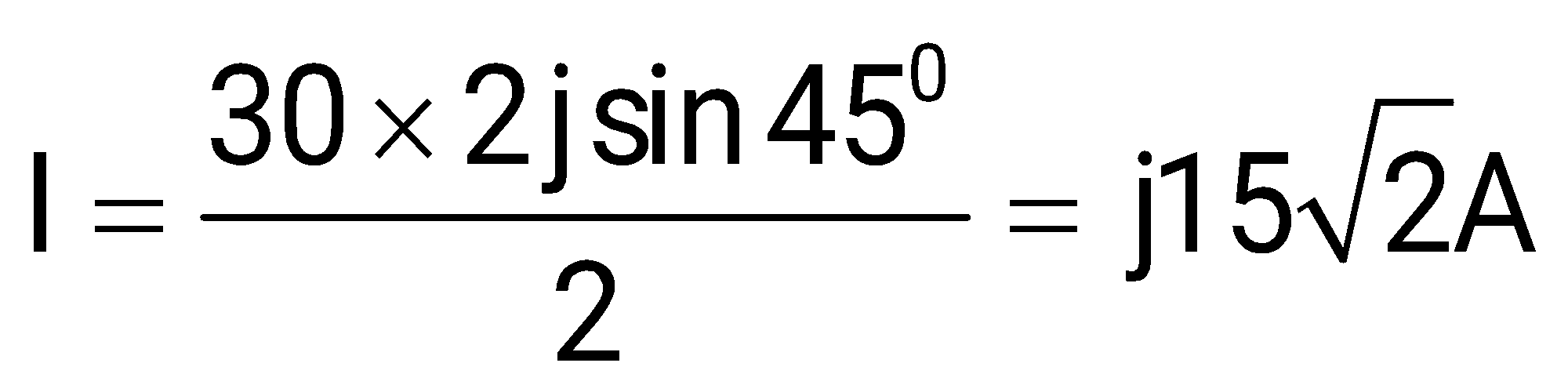

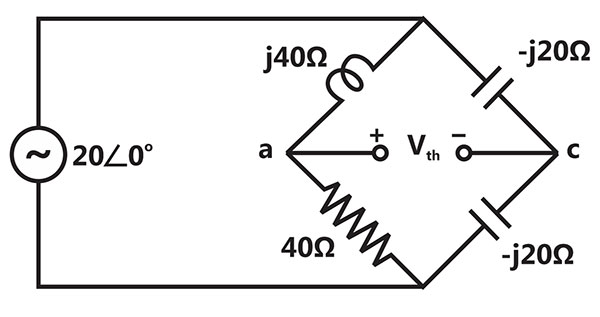

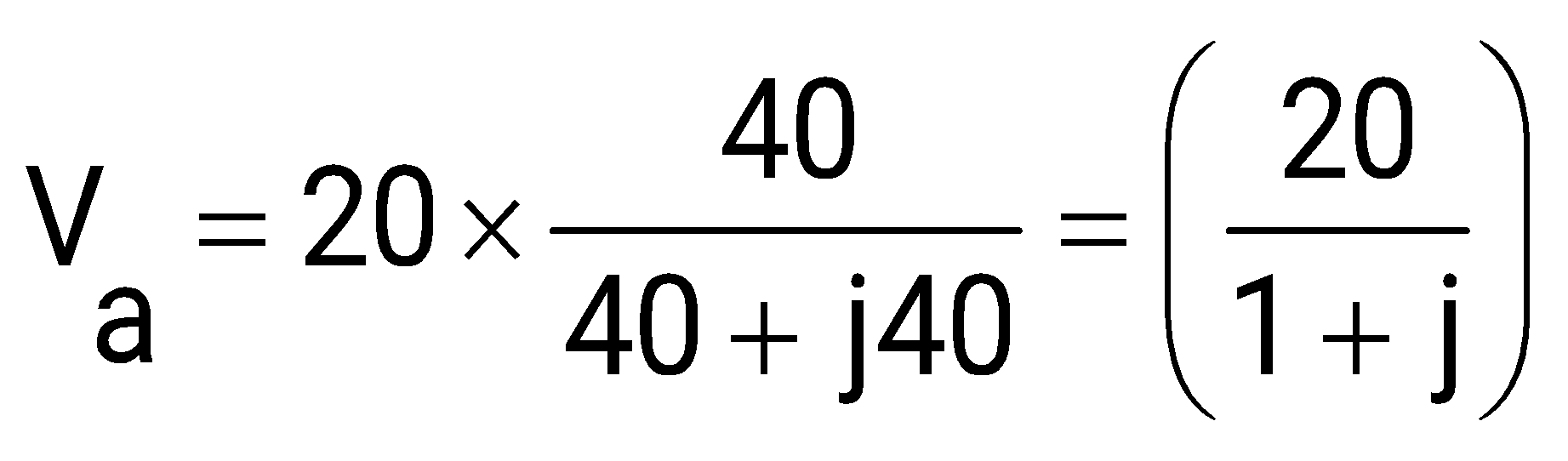

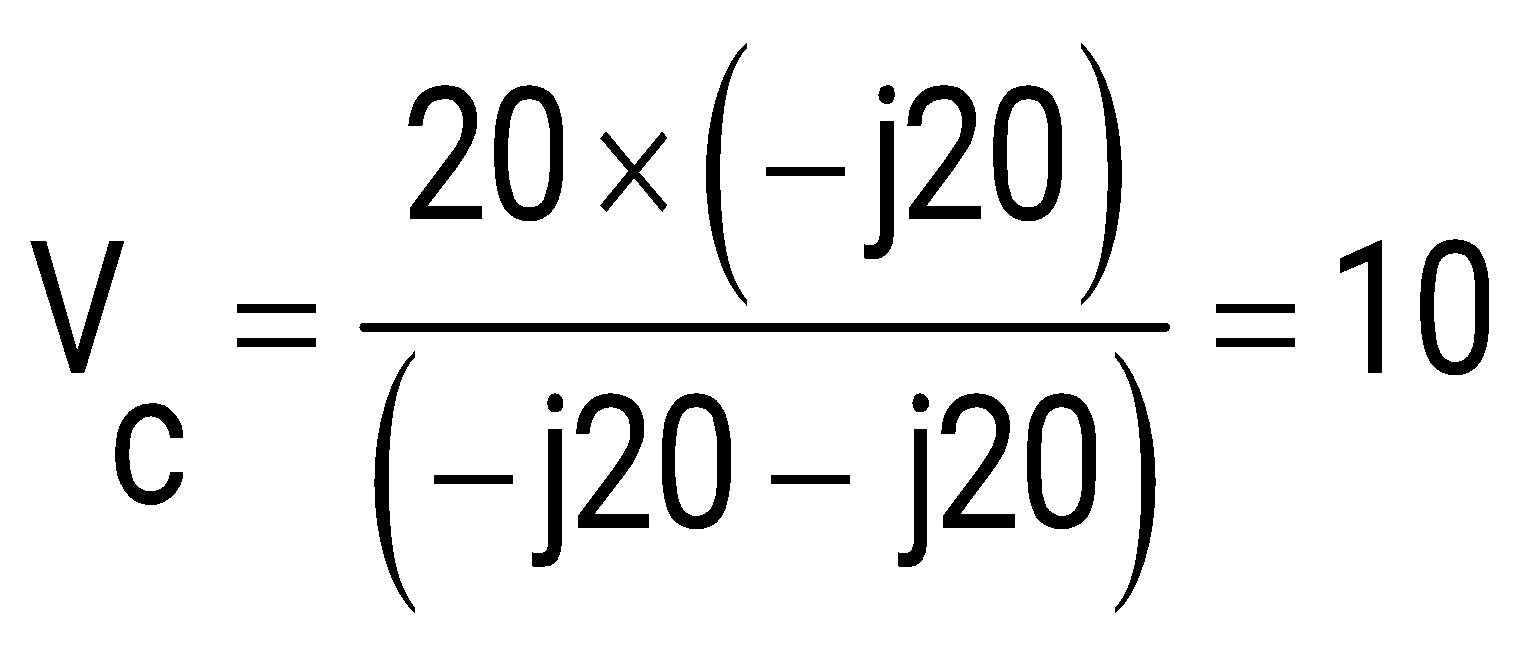

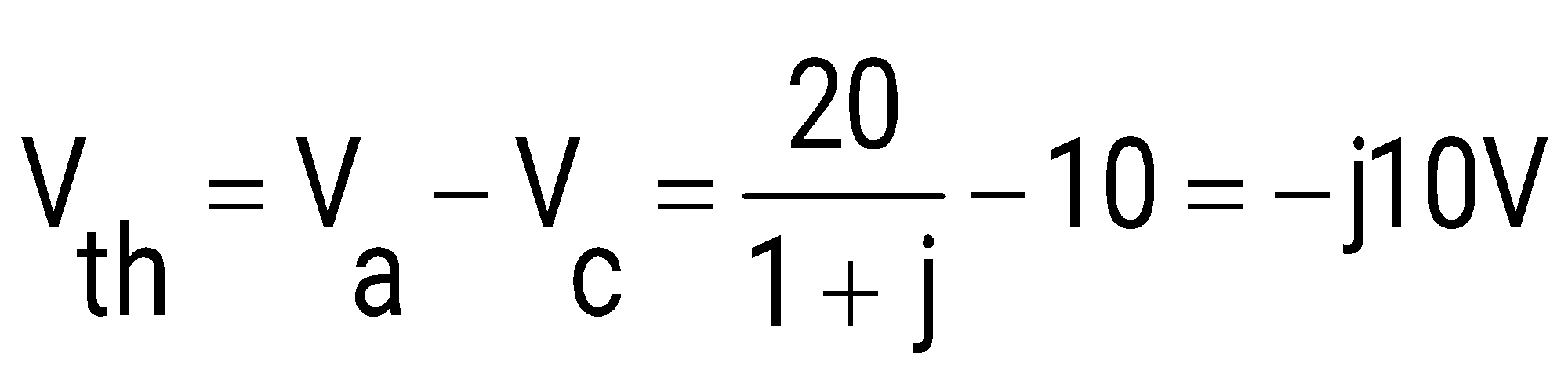

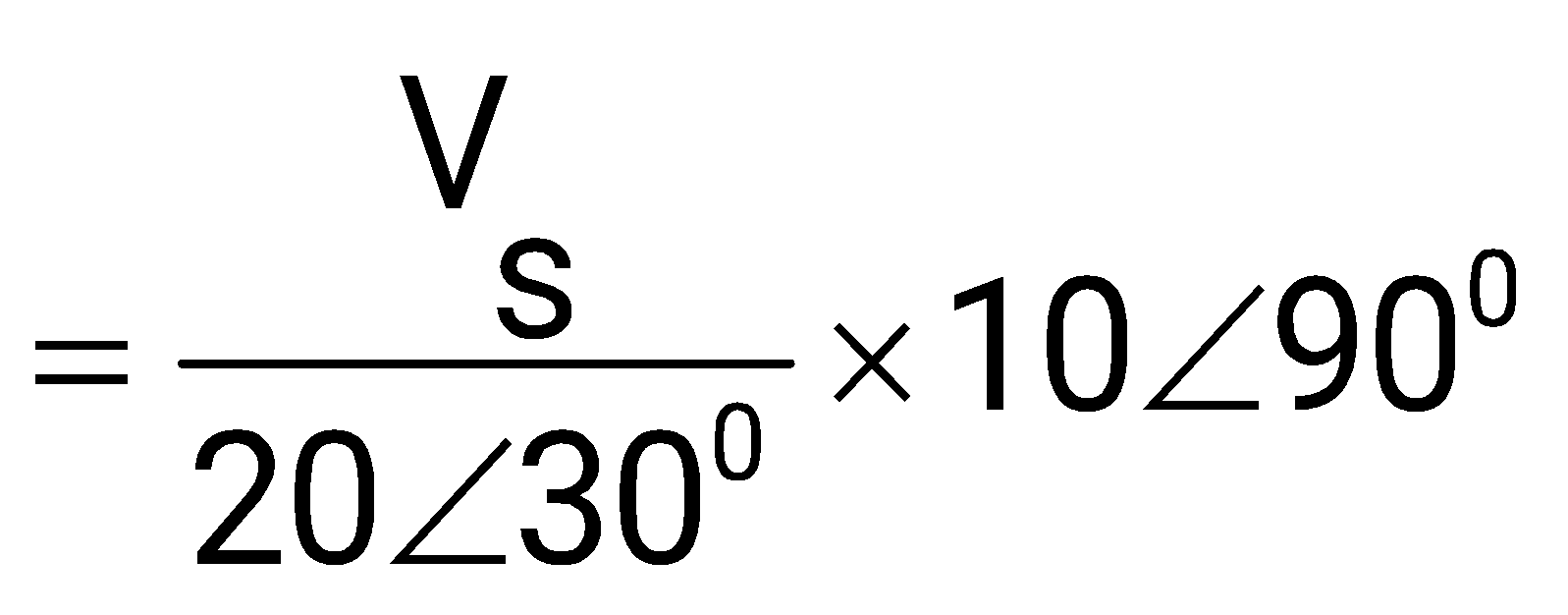

For the circuit shown, if , the instantaneous value of the Thevenin's equivalent voltage (in Volts) across the terminals at time is __________ (Round off to 2 decimal places).

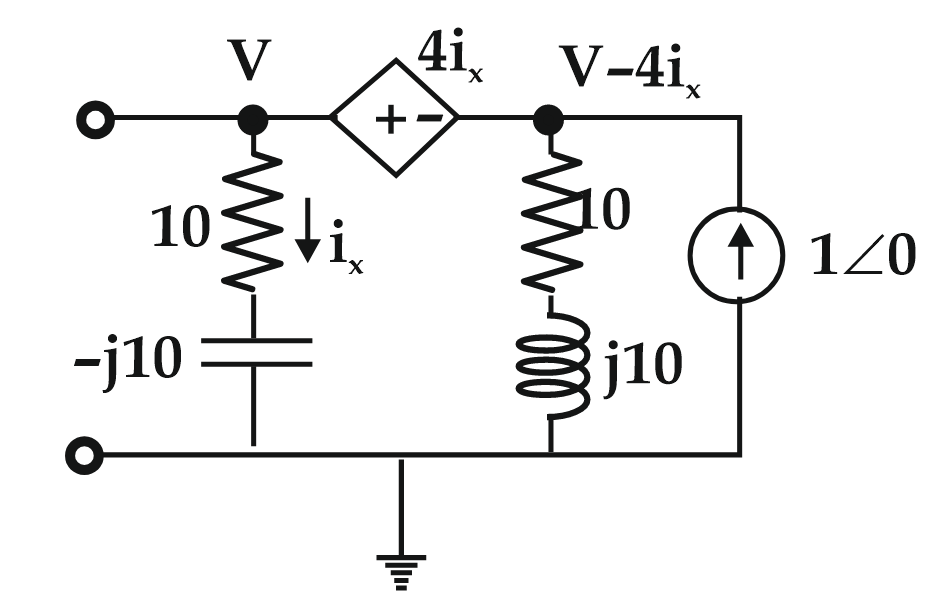

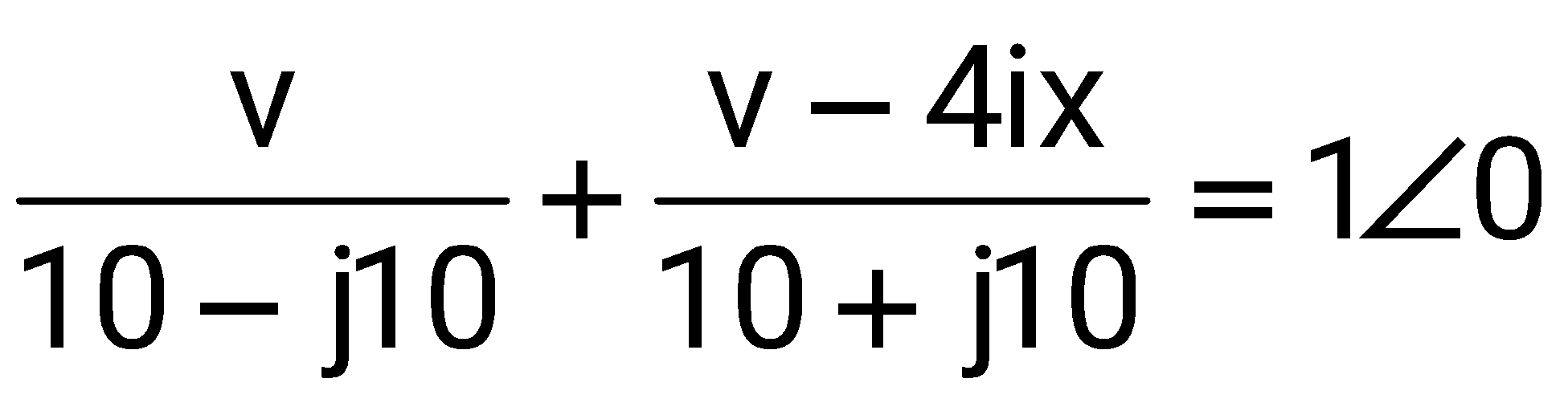

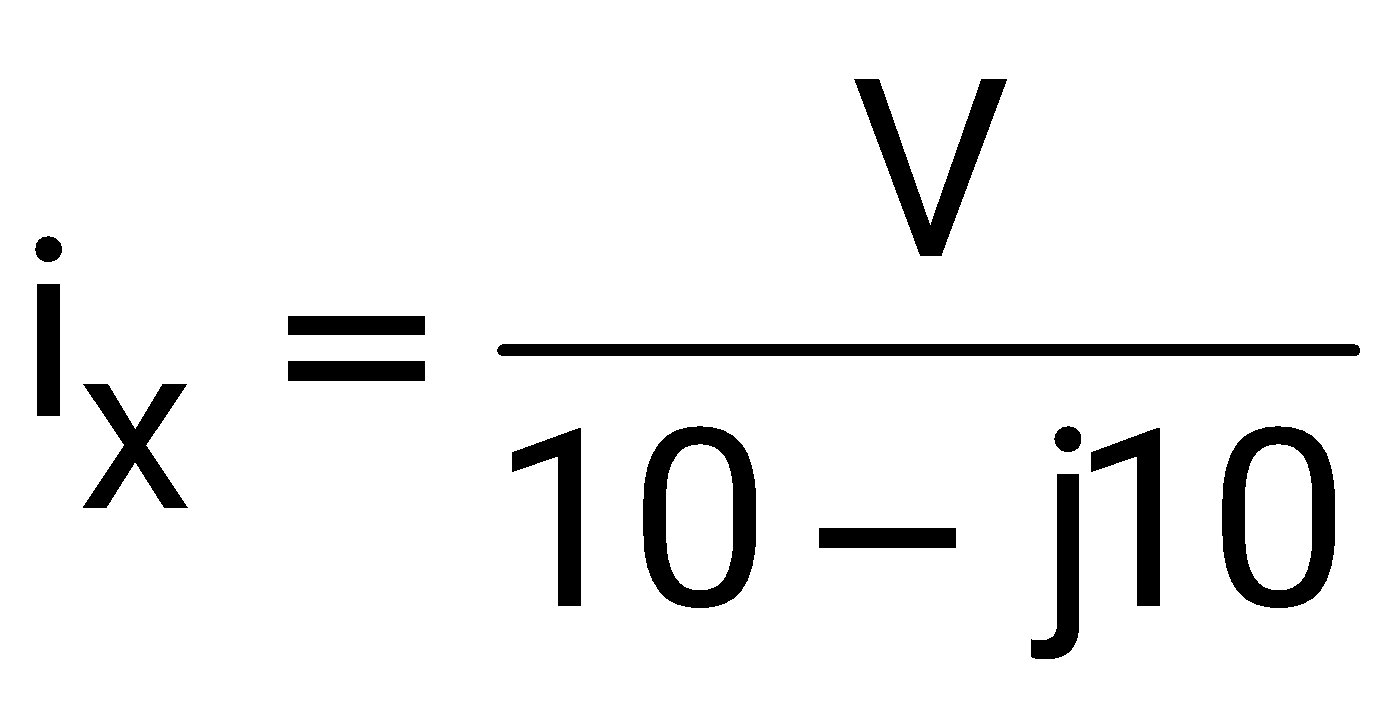

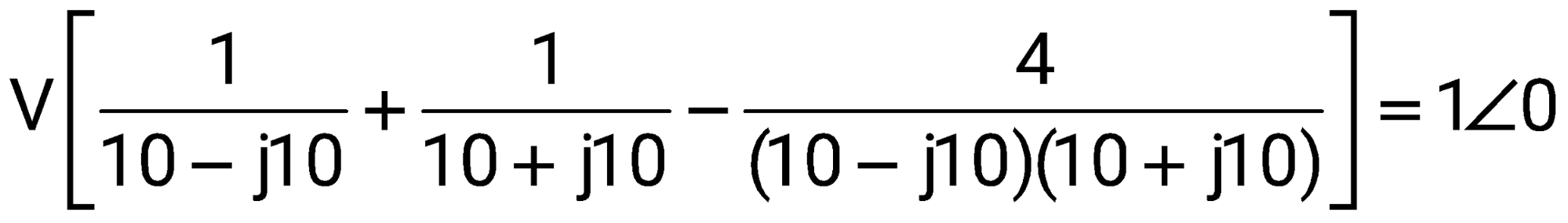

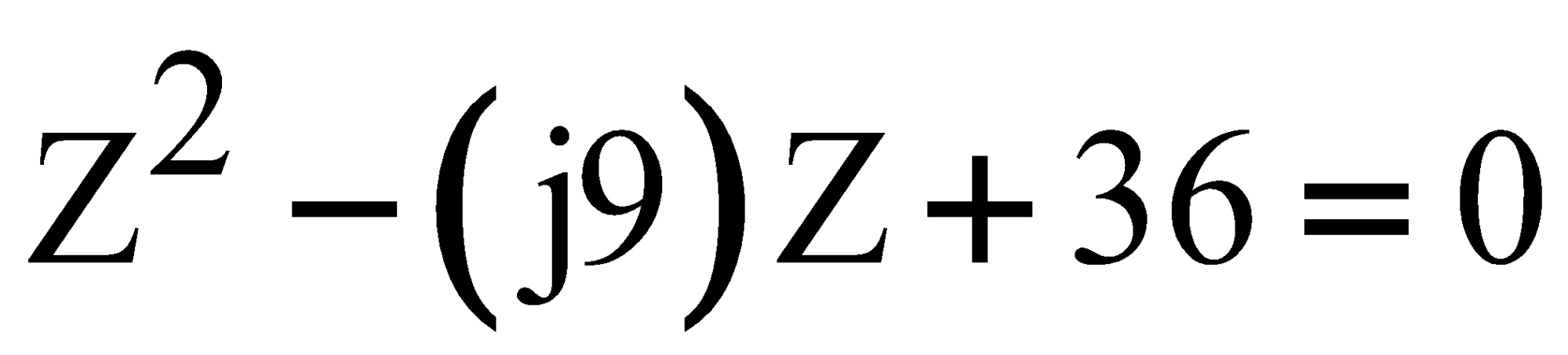

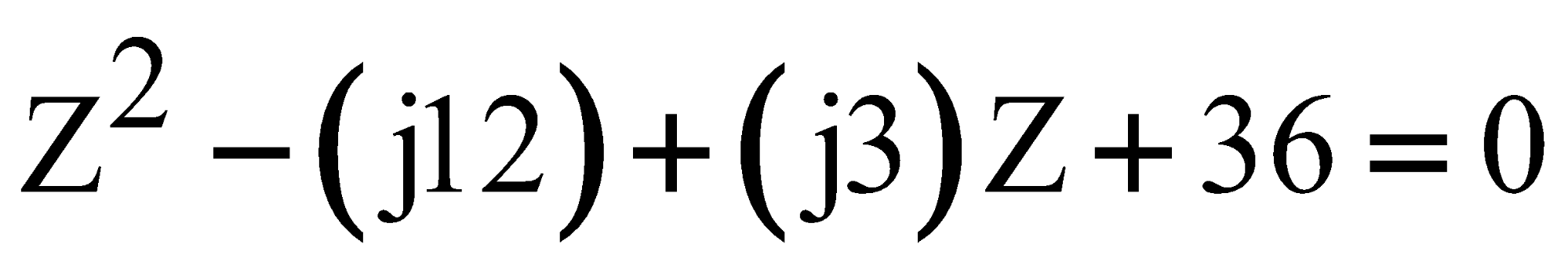

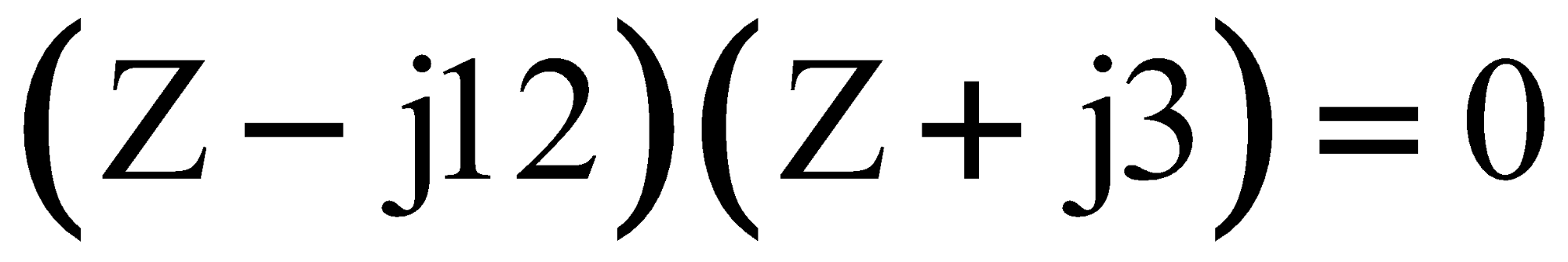

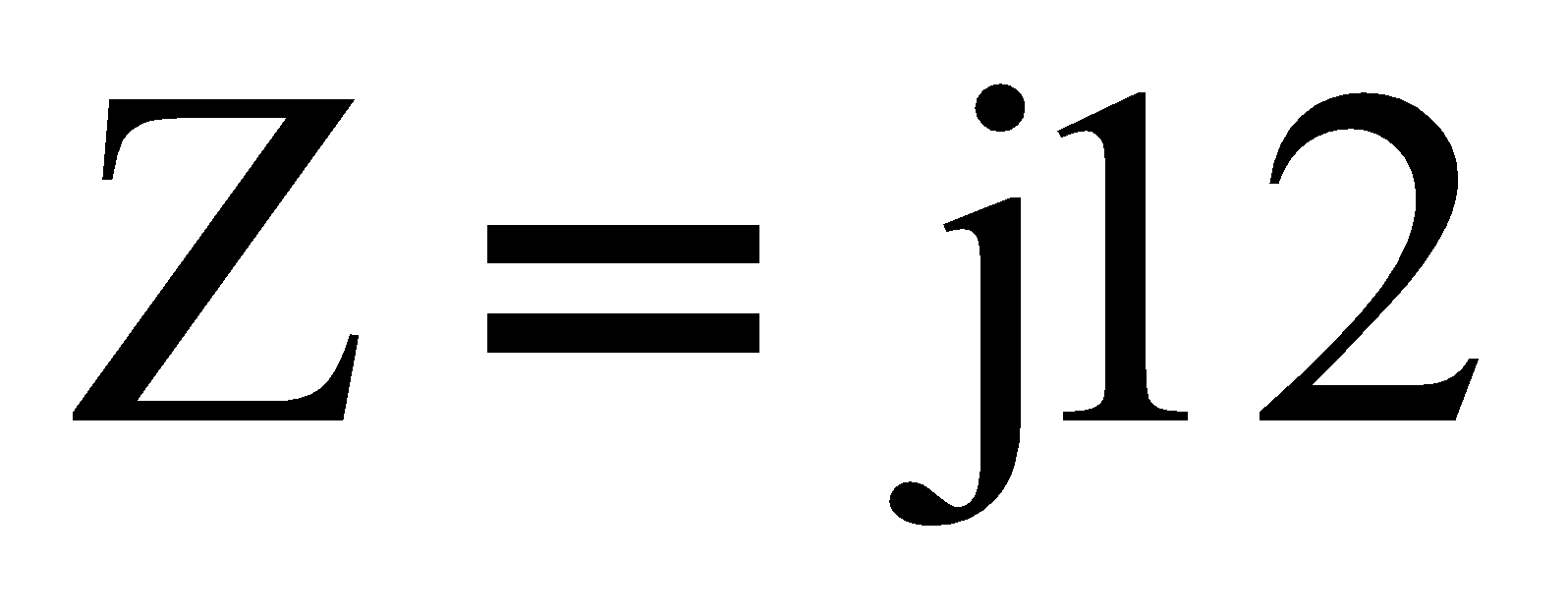

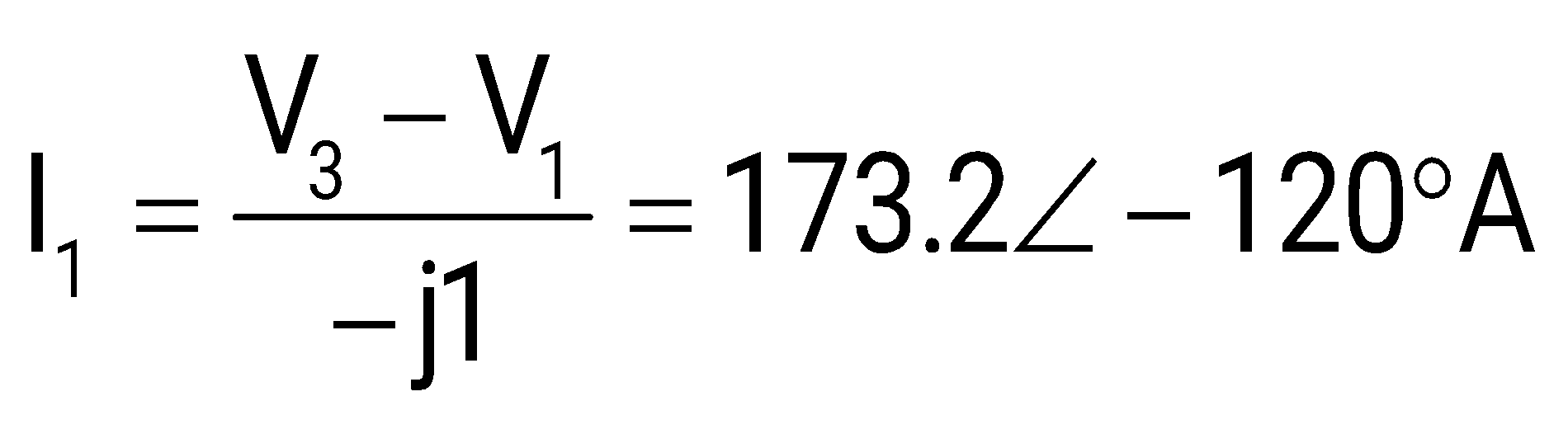

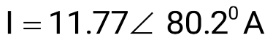

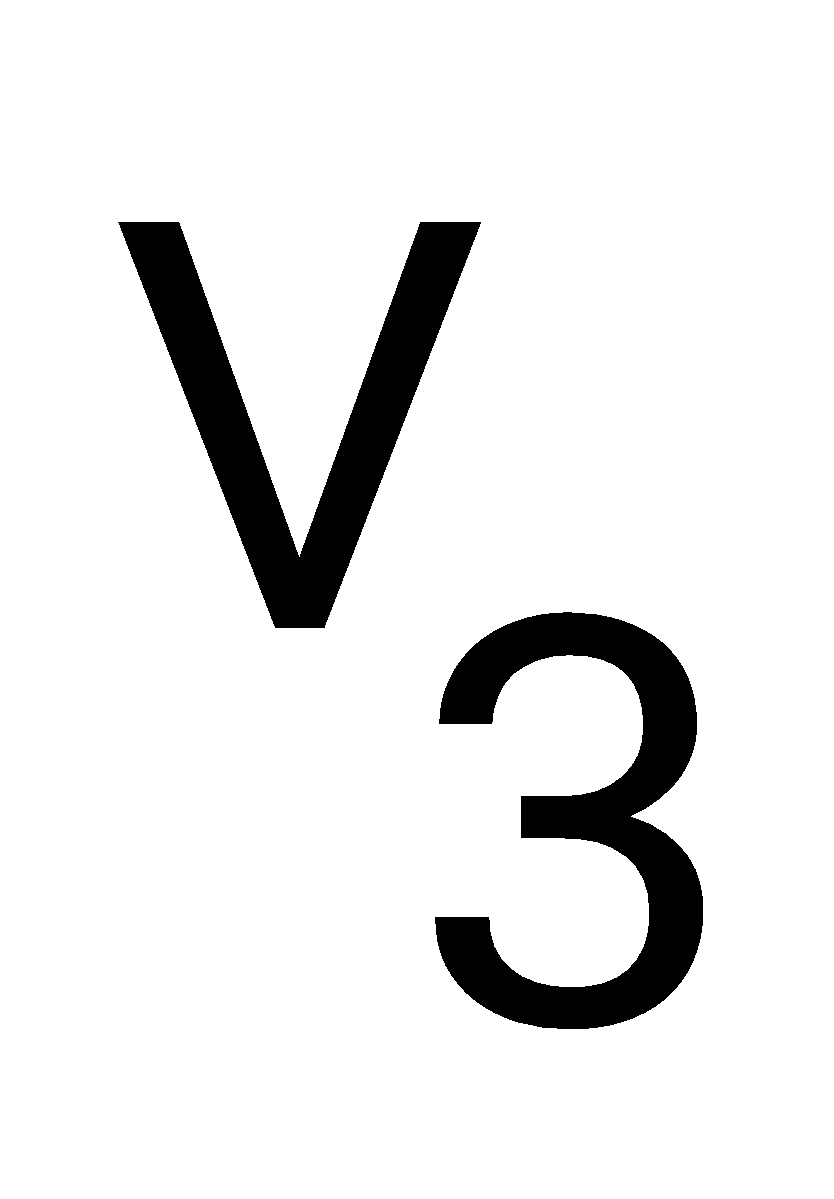

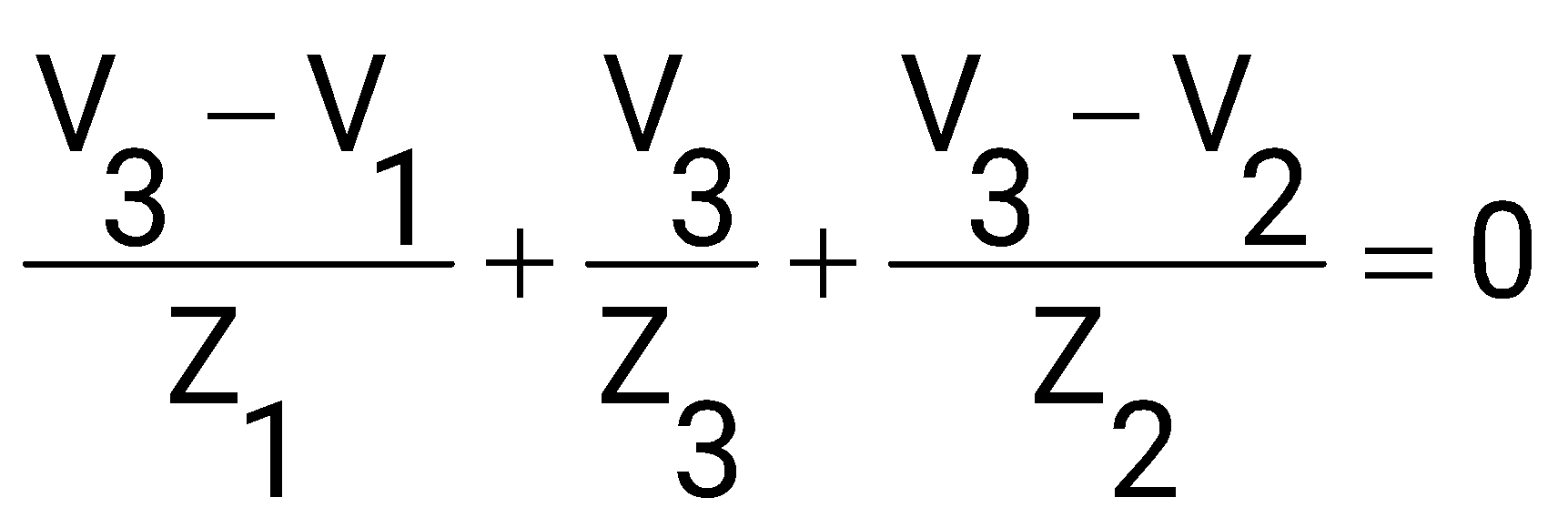

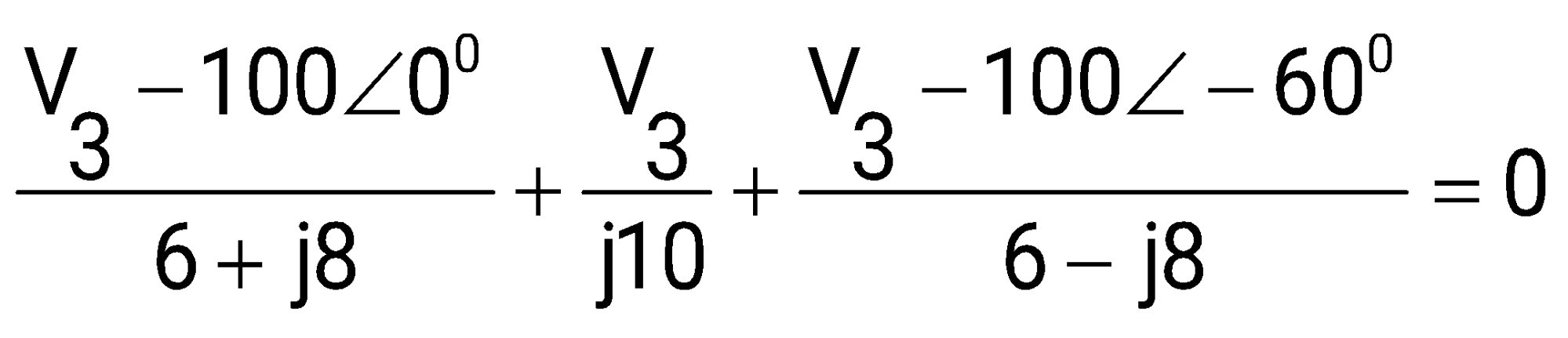

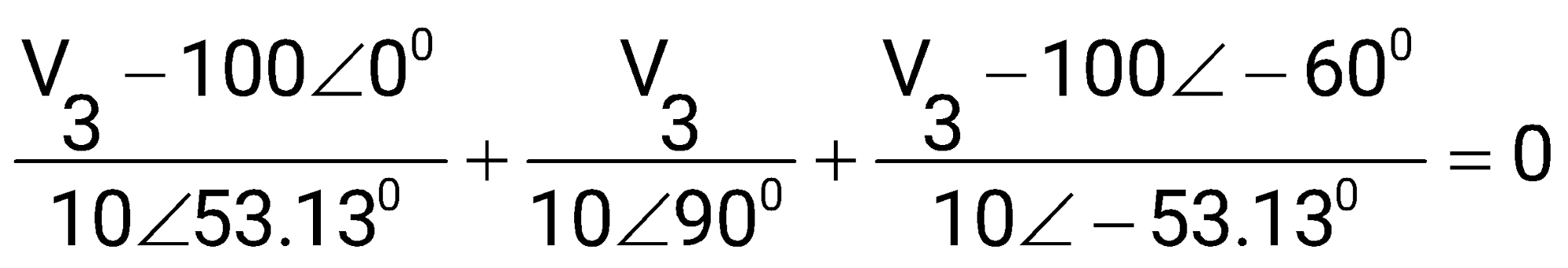

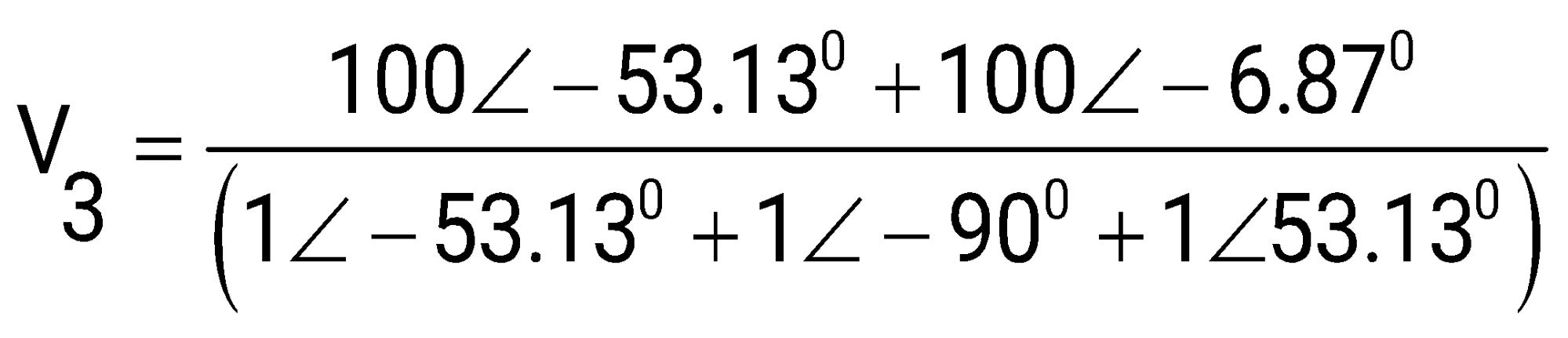

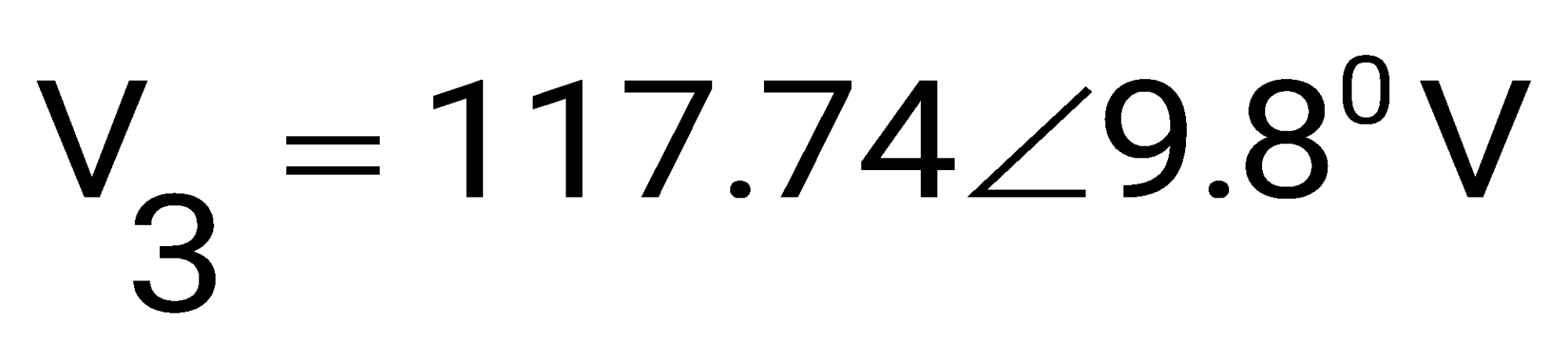

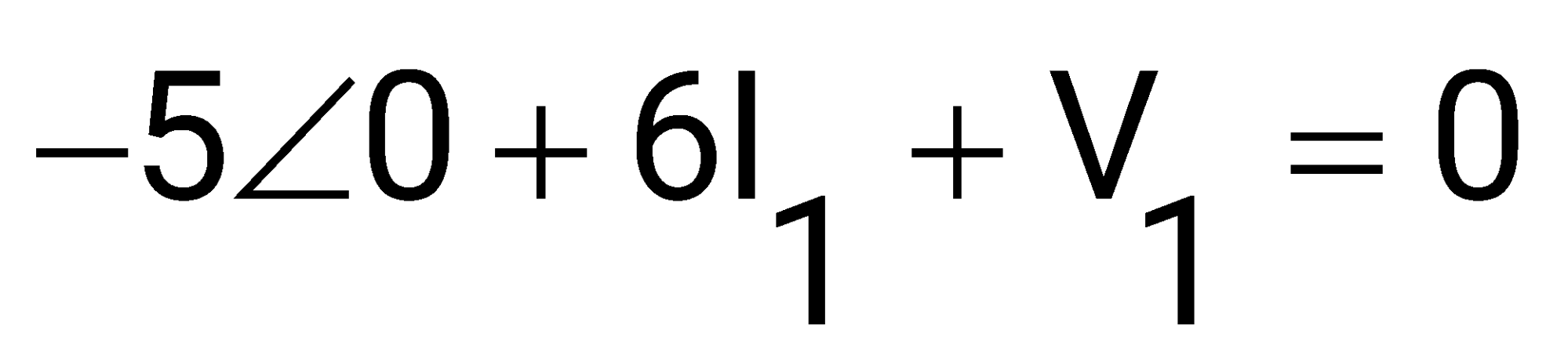

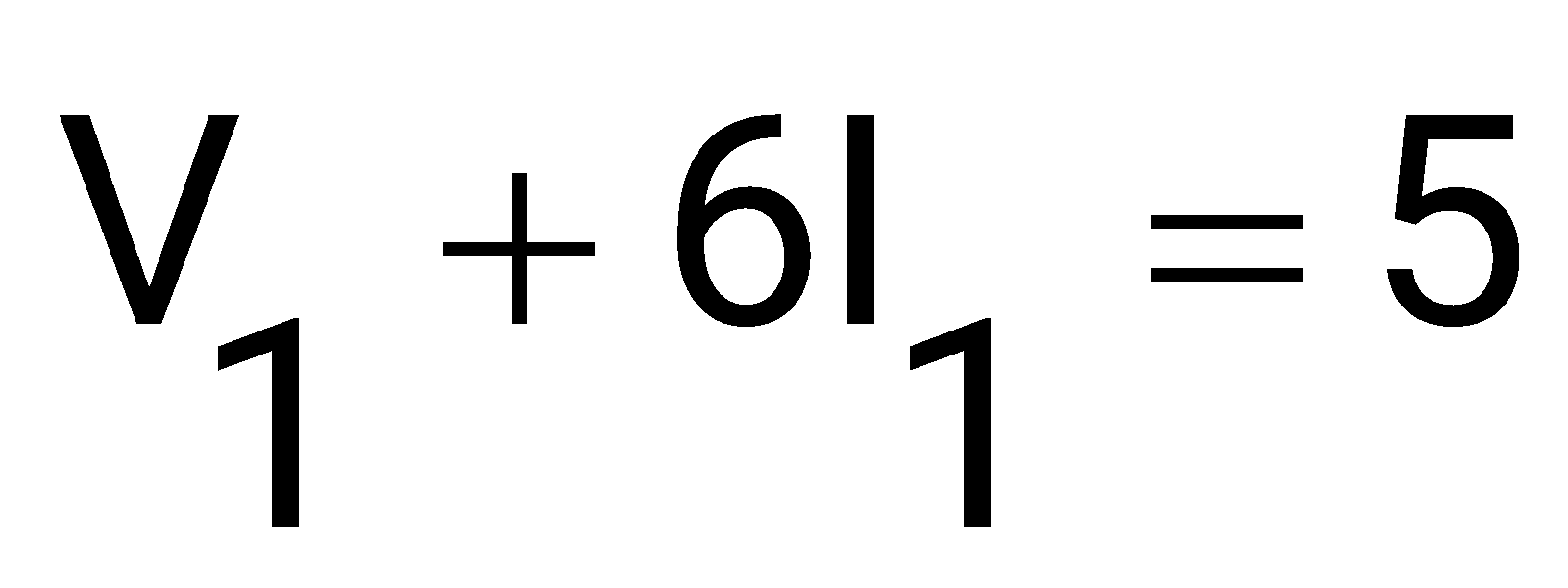

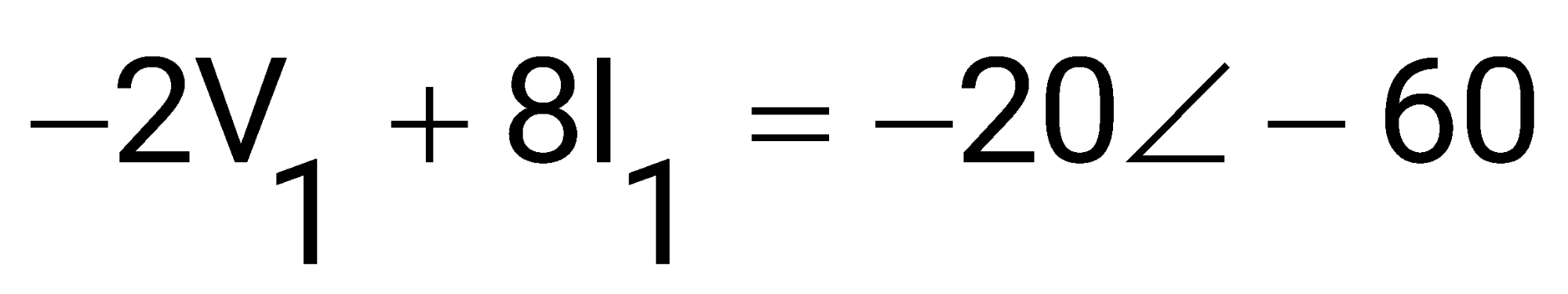

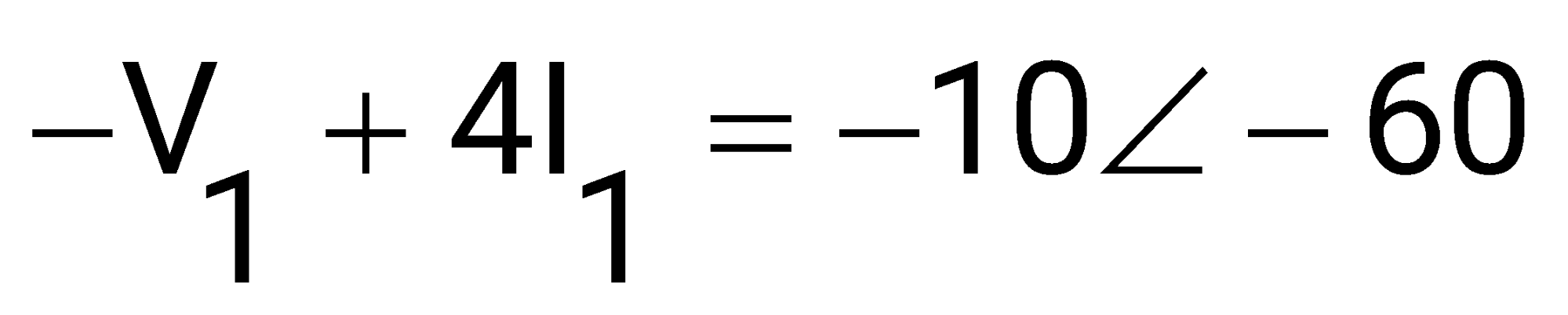

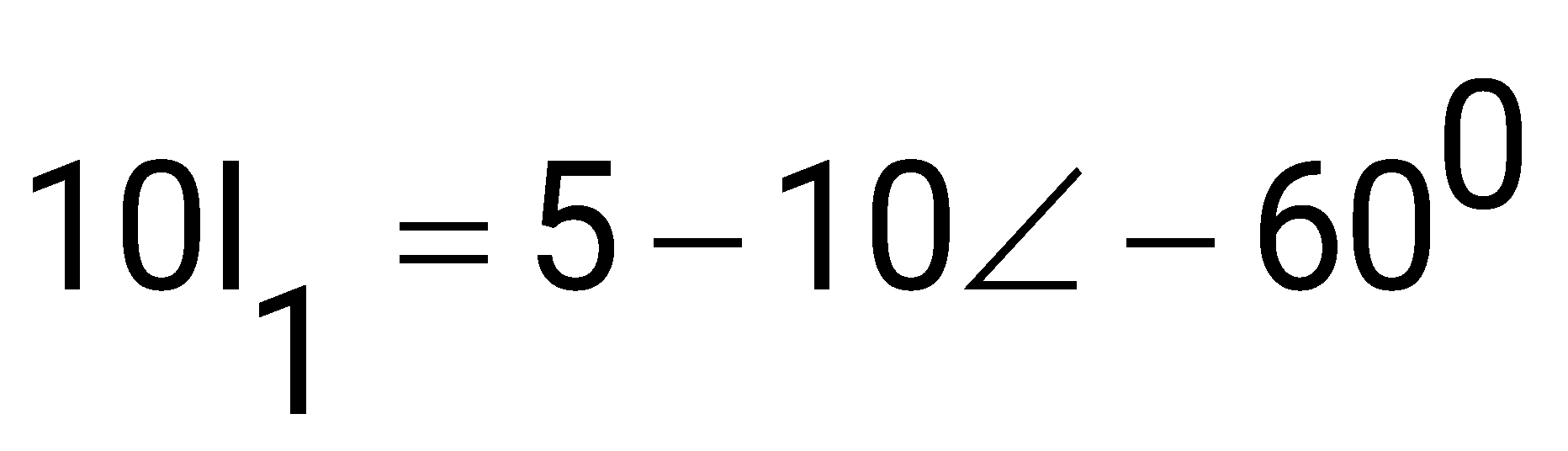

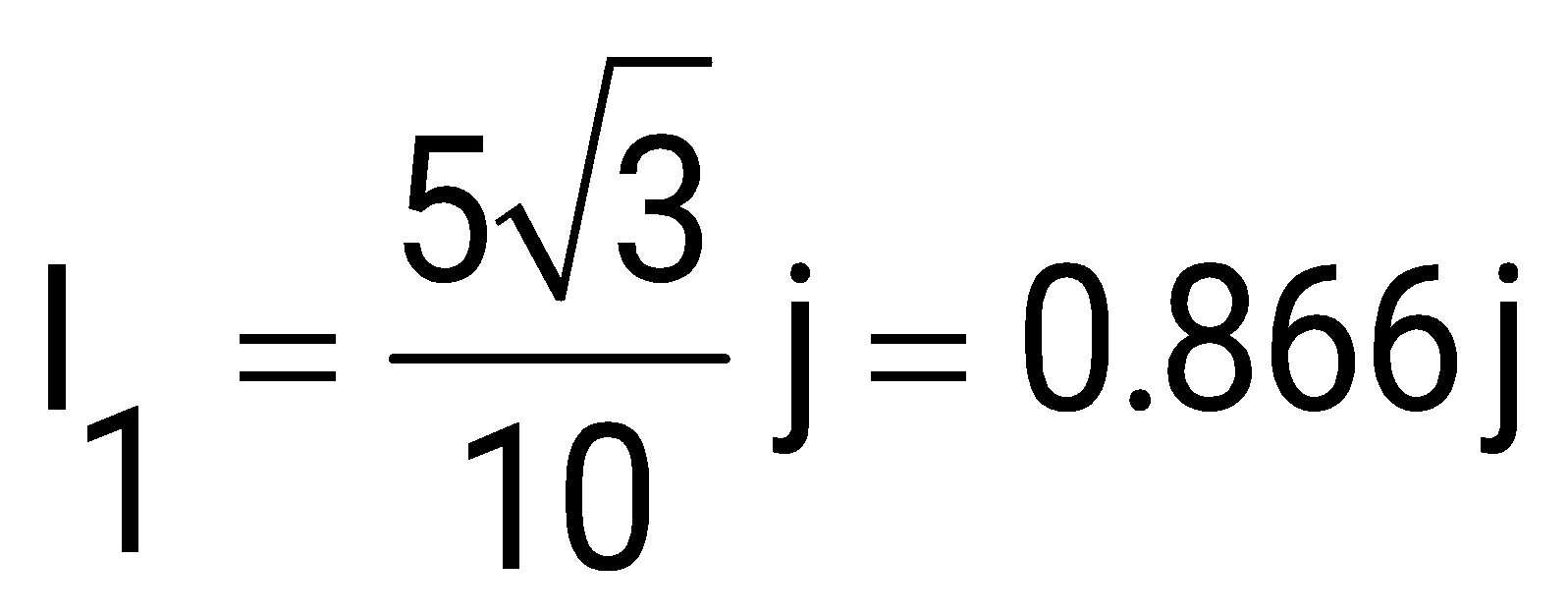

Applying nodal analysis to super node

∴ v(t) = 12.5 sin (1000t)

At t = 5 msec v(t) = 12.5 sin 5 = -11.986

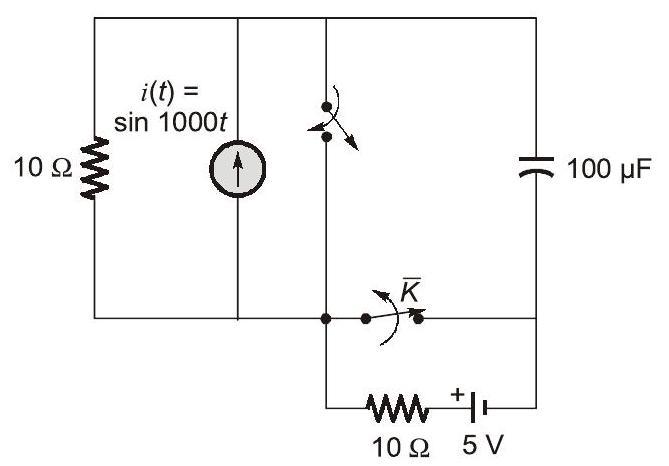

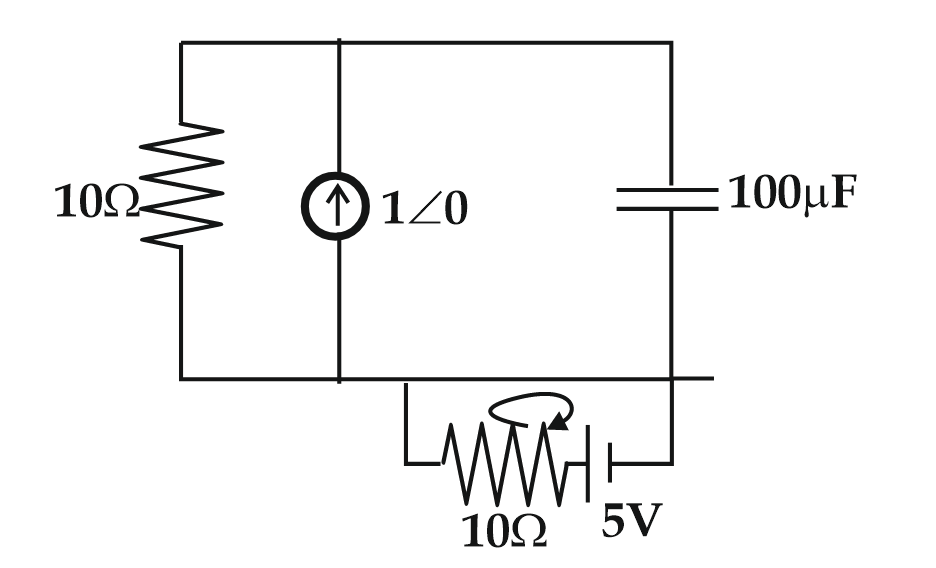

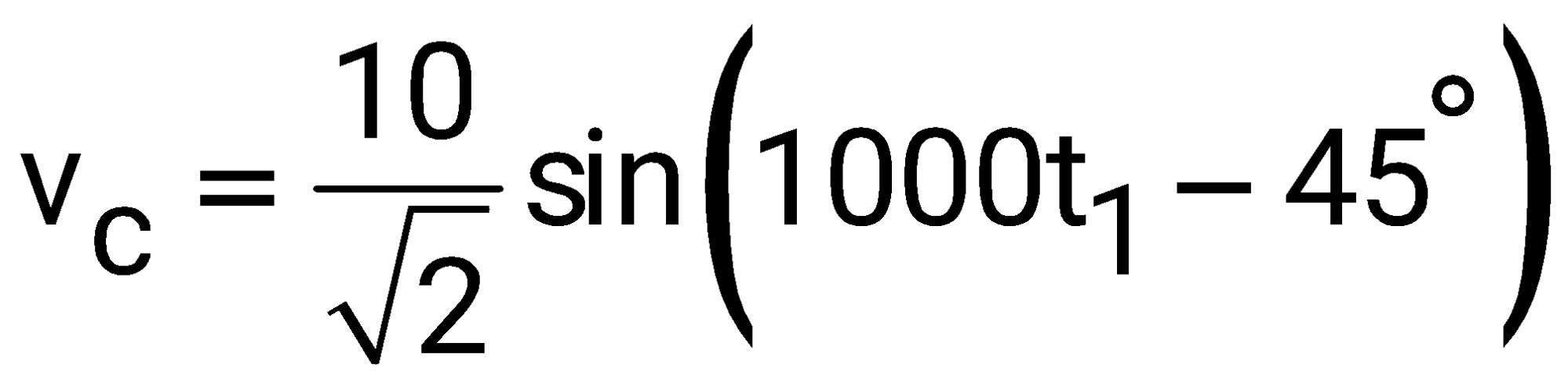

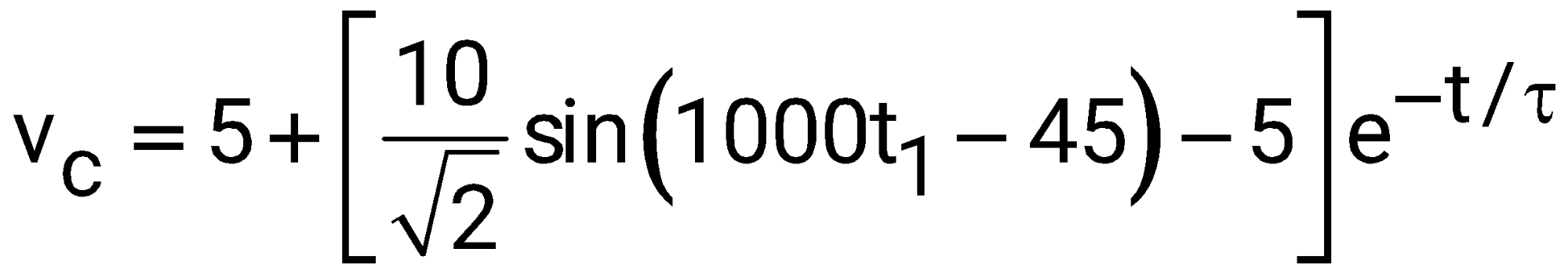

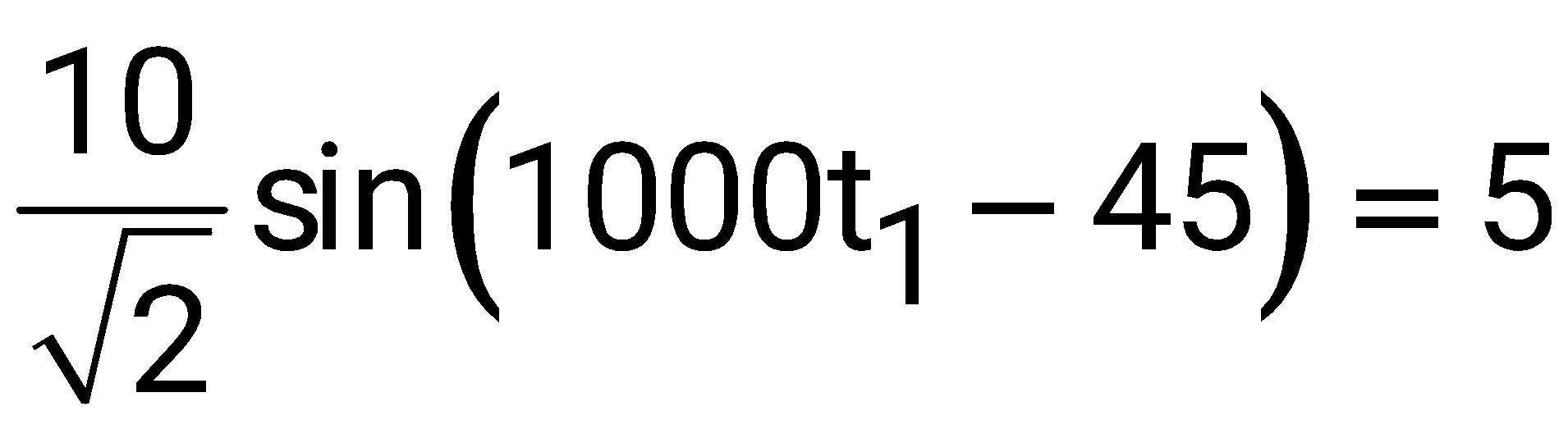

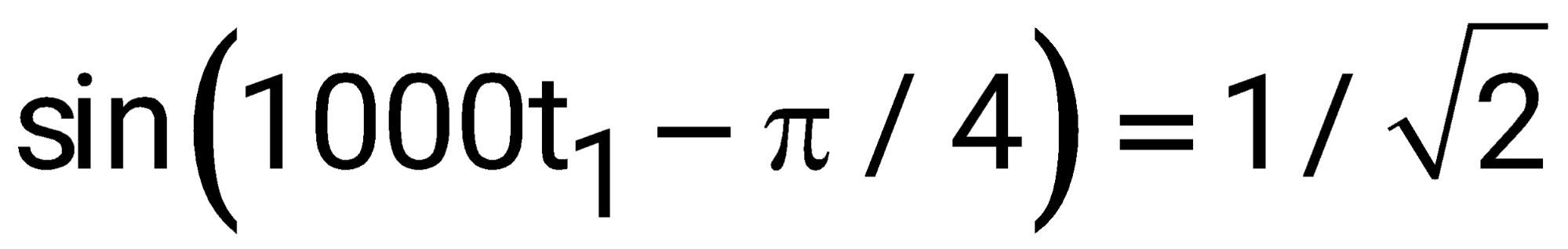

The circuit shown in the figure is initially in the steady state with the switch in open condition and in closed condition. The switch is closed and is opened simultaneously at the instant , where . The minimum value of in milliseconds, such that there is no transient in the voltage across the capacitor, is (Round off to 2 decimal places).

Before t = t1 Kcs open & is closed & circuit reaches steady state

The current of 5V dc source keeps circulating in a loop & does not affect capacitor.

at t = t1,

after t = t1 k closed so ac current source is shorted & is open so a series RC circuit with 5V dc source is formed.

Initial capacitor voltage

Steady state capacitor voltage = 5V

Second term represents transient

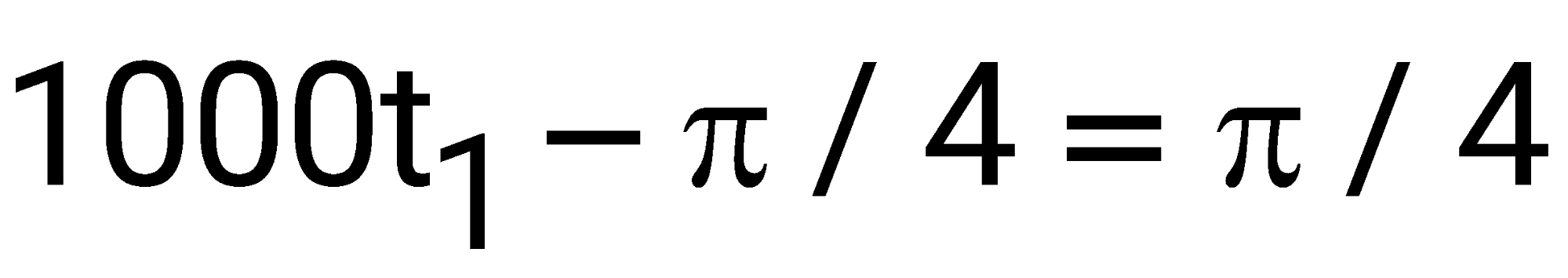

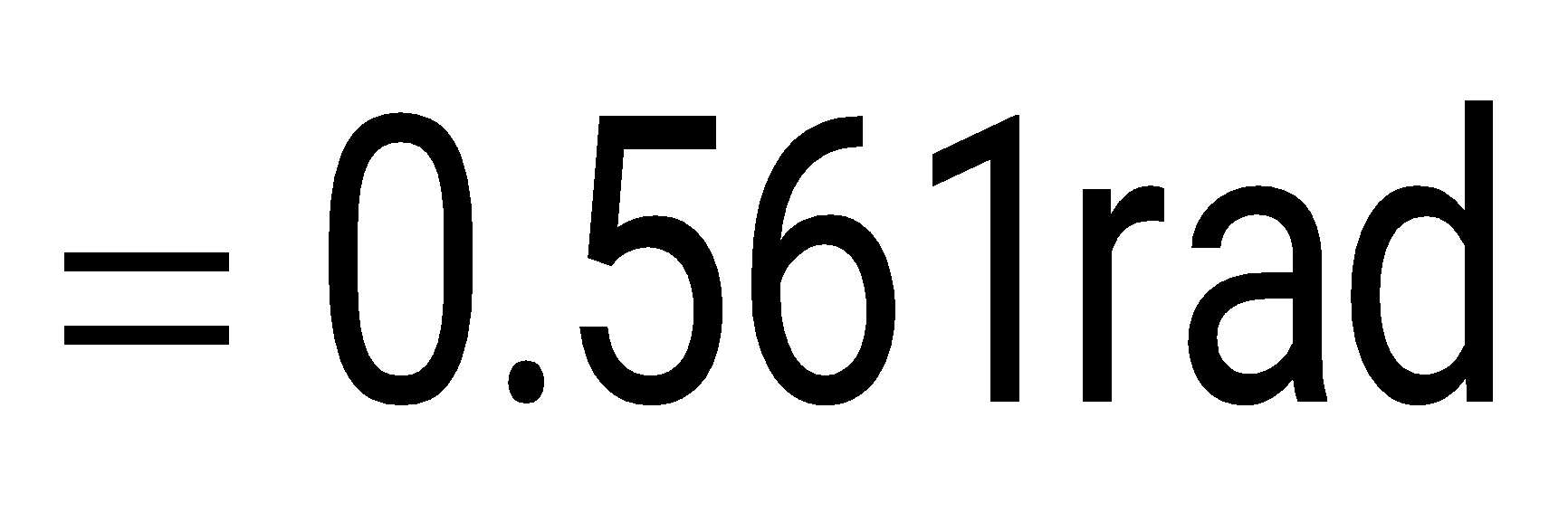

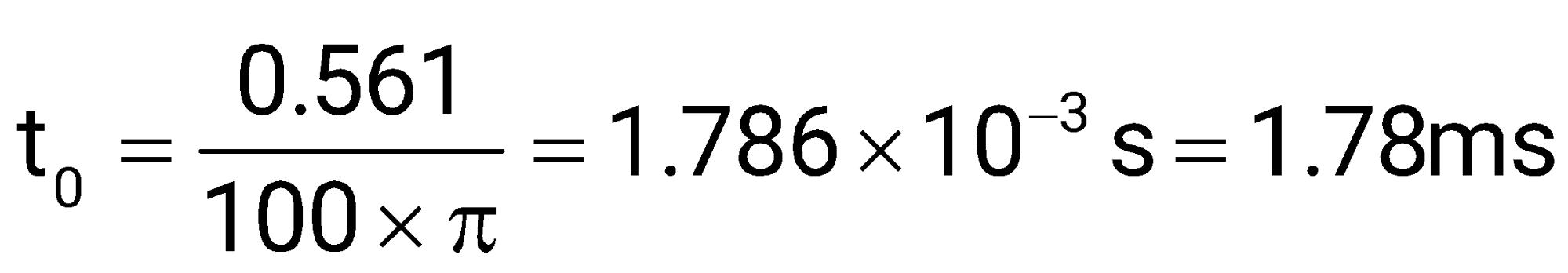

For transient-free response

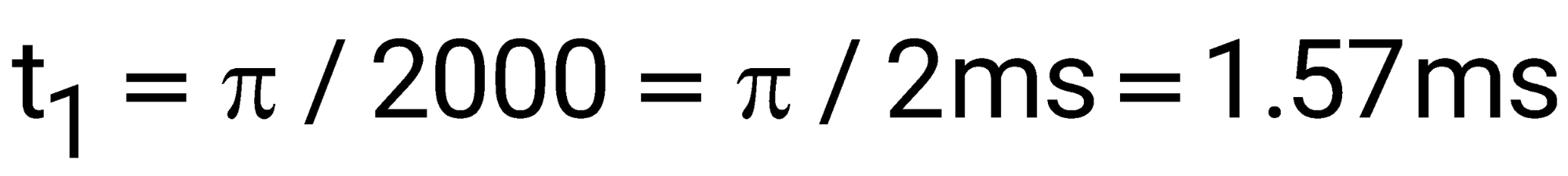

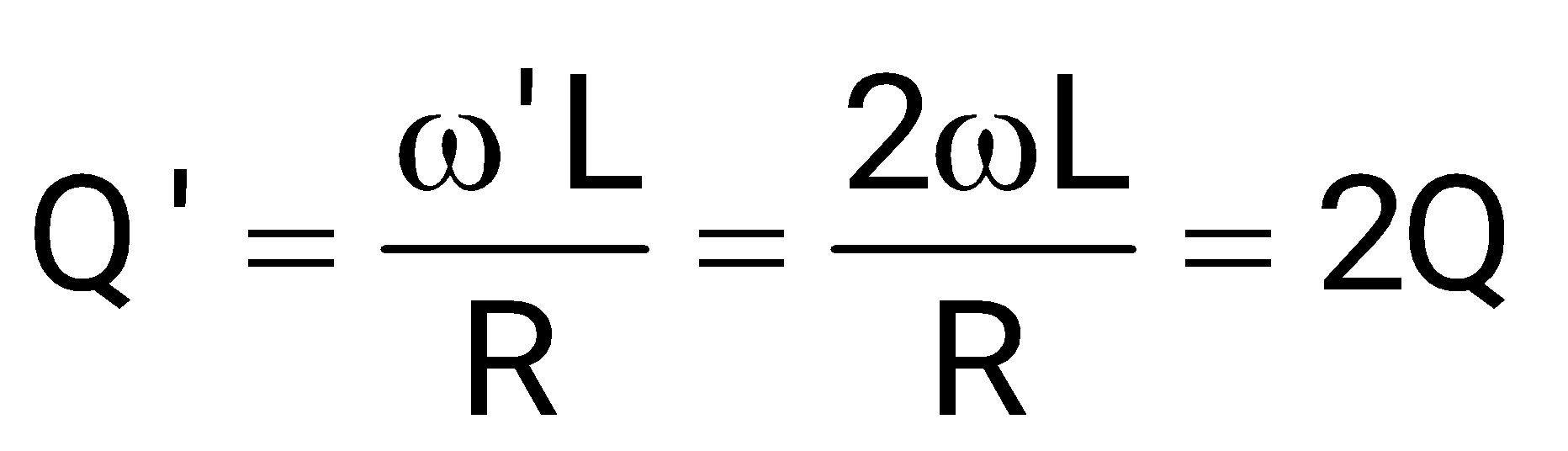

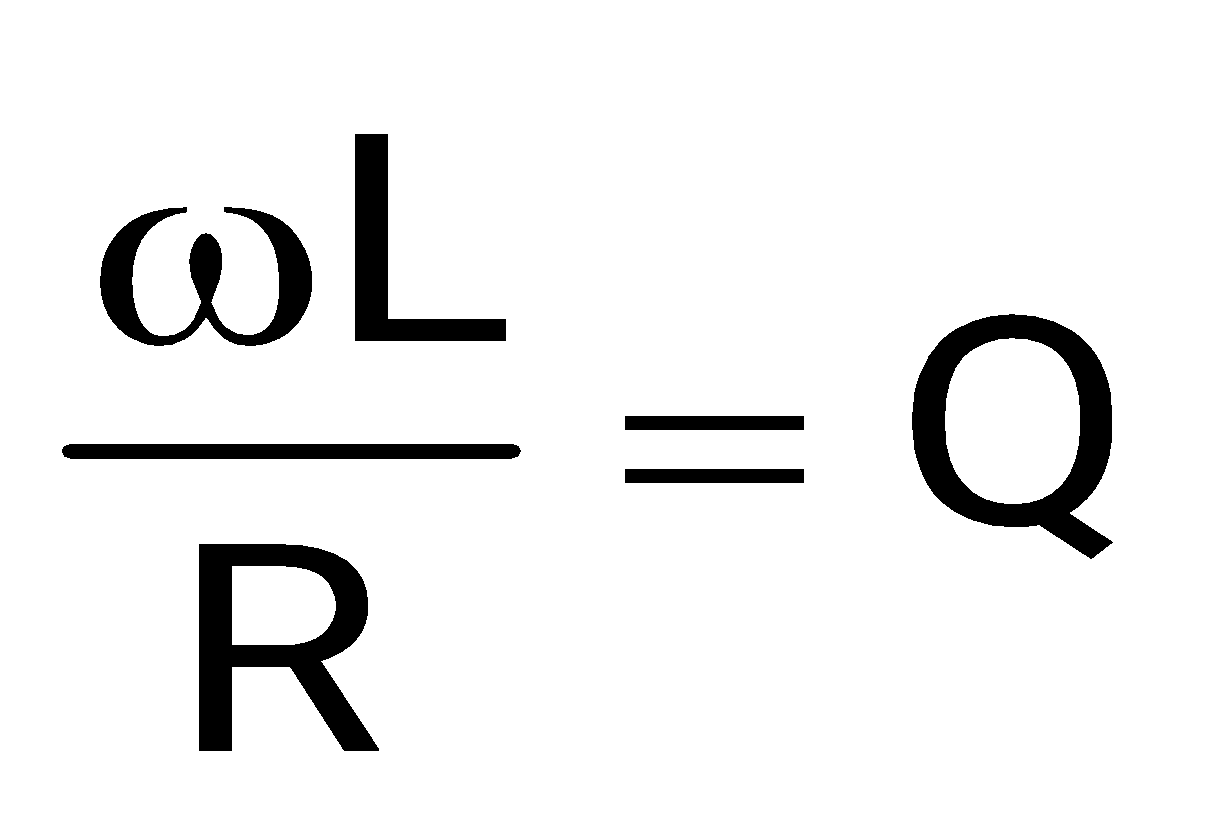

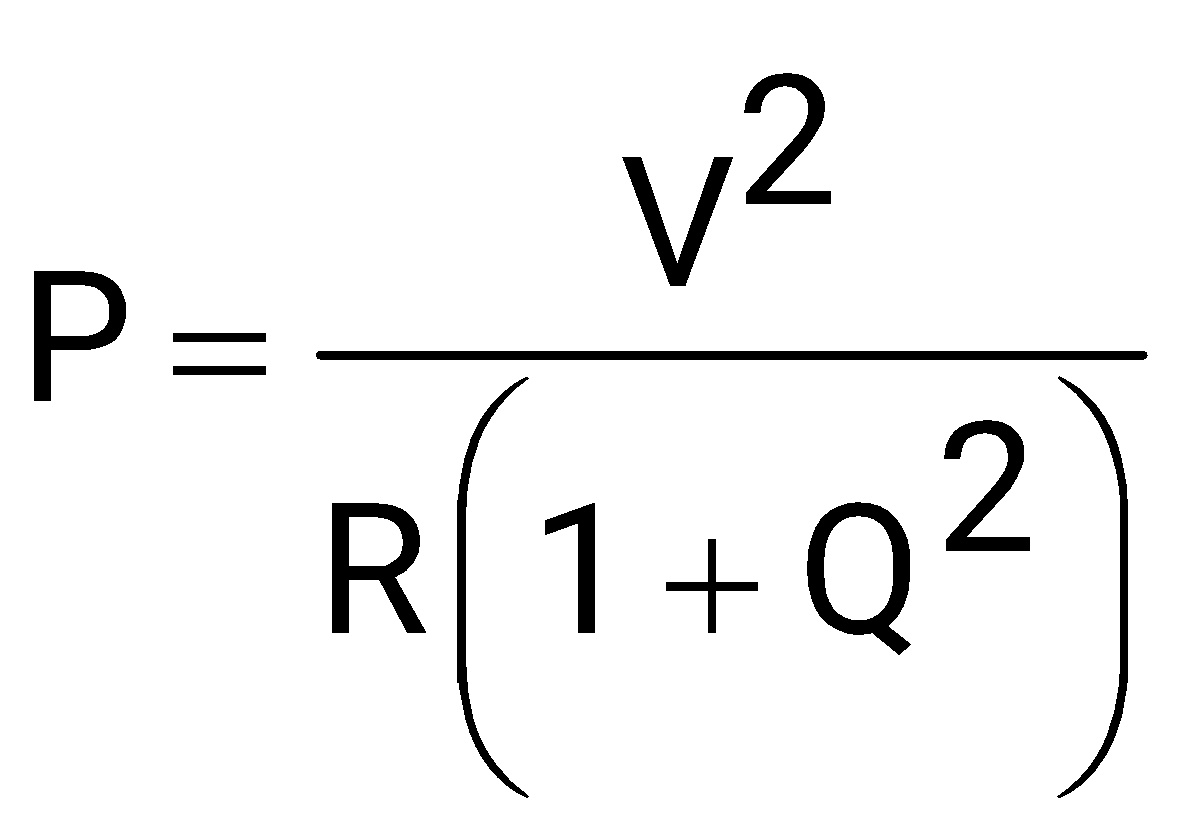

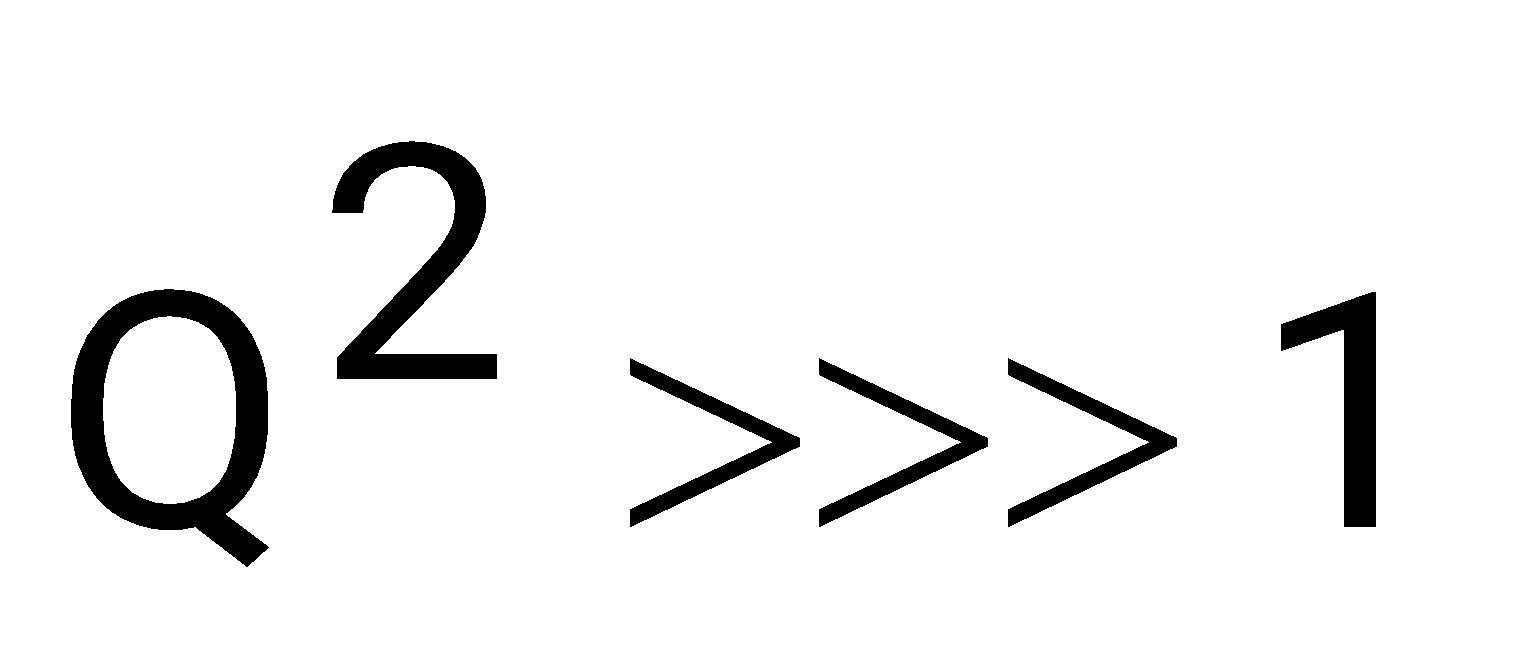

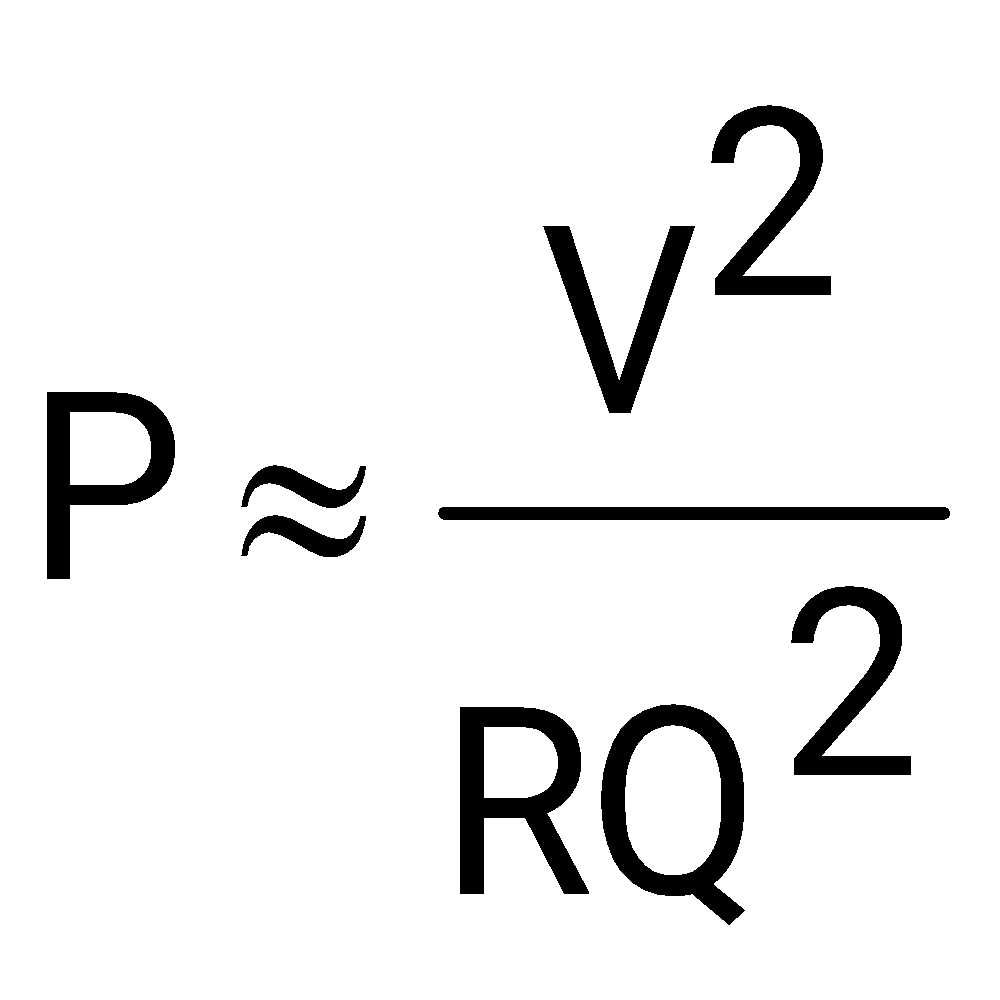

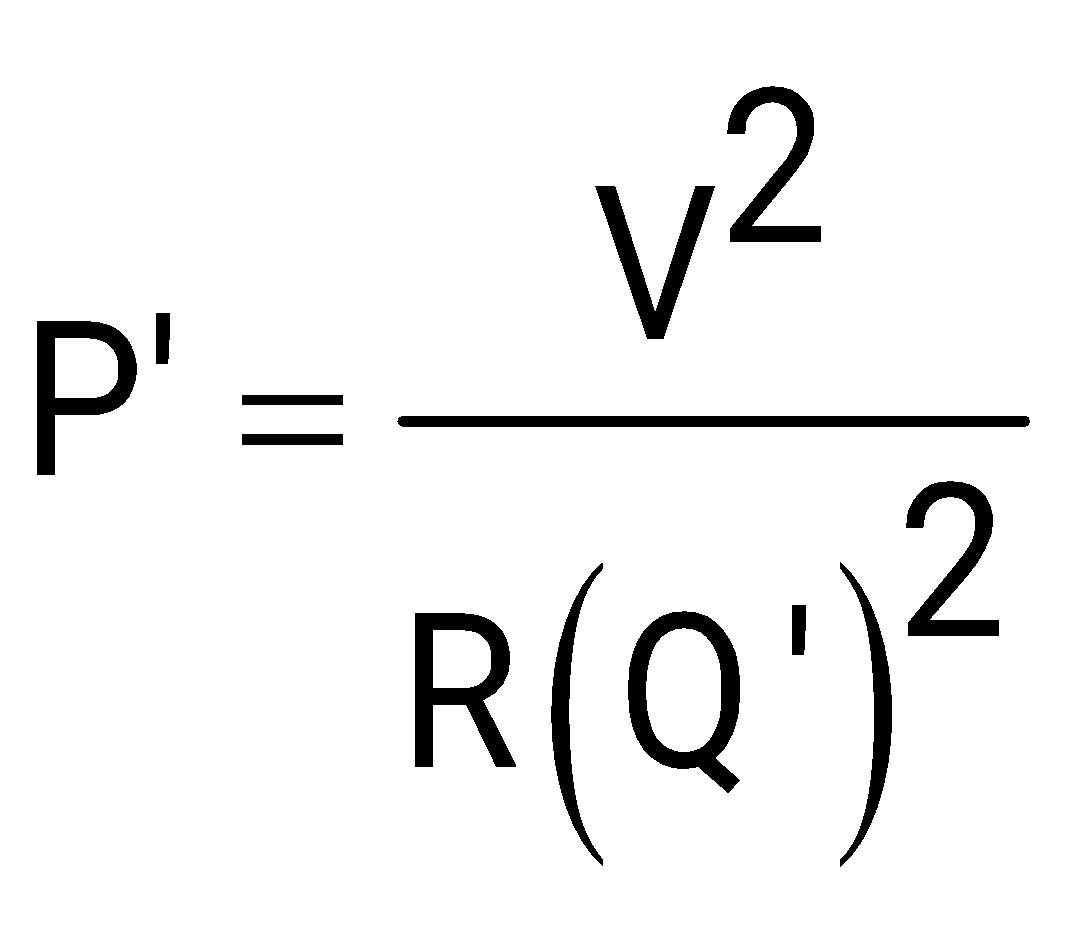

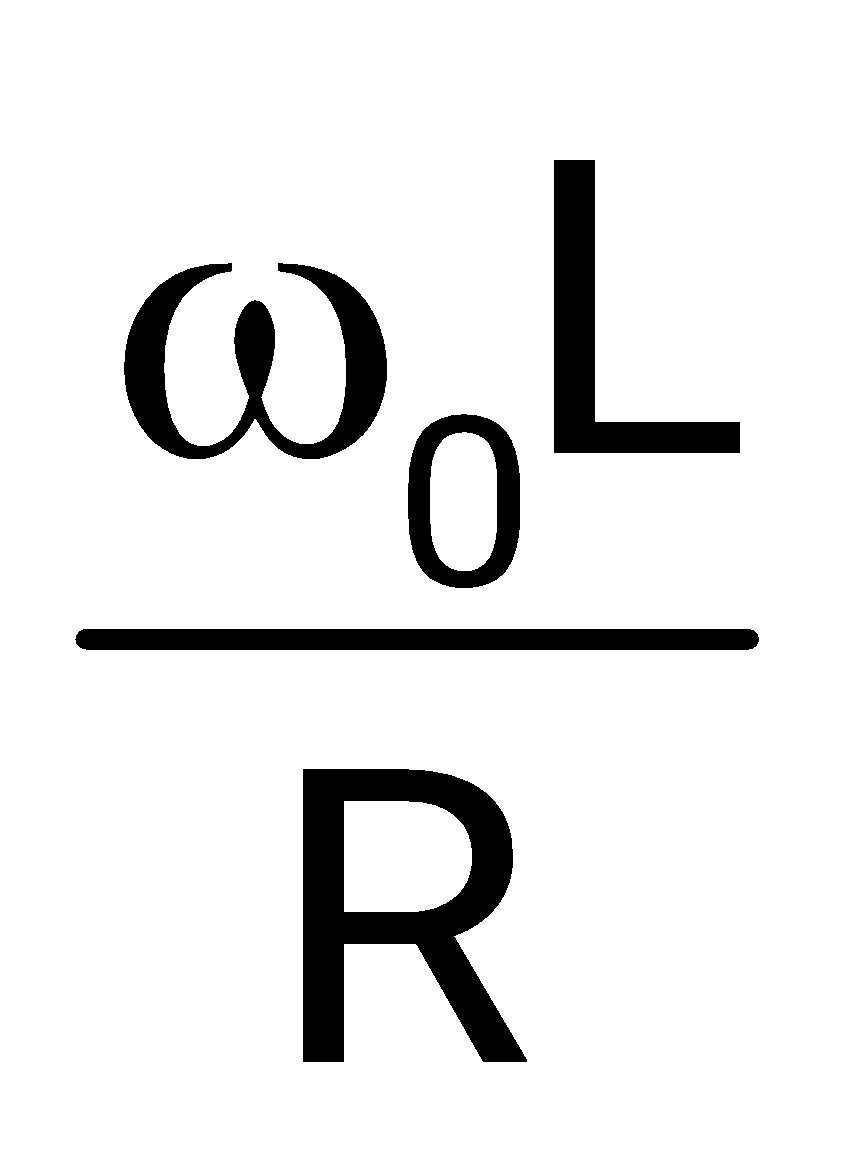

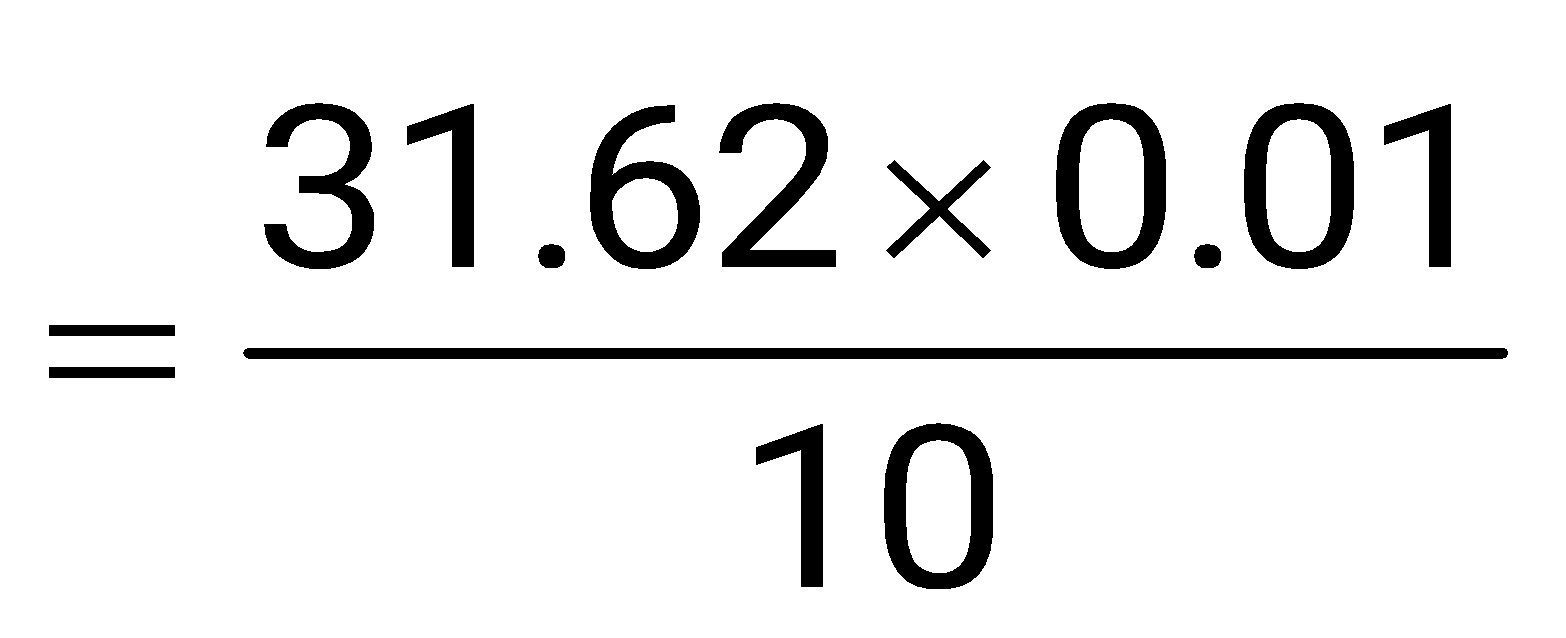

An inductor having a 𝑄-factor of 60 is connected in series with a capacitor having a 𝑄-factor of 240. The overall 𝑄-factor of the circuit is ________. (round off to nearest integer)

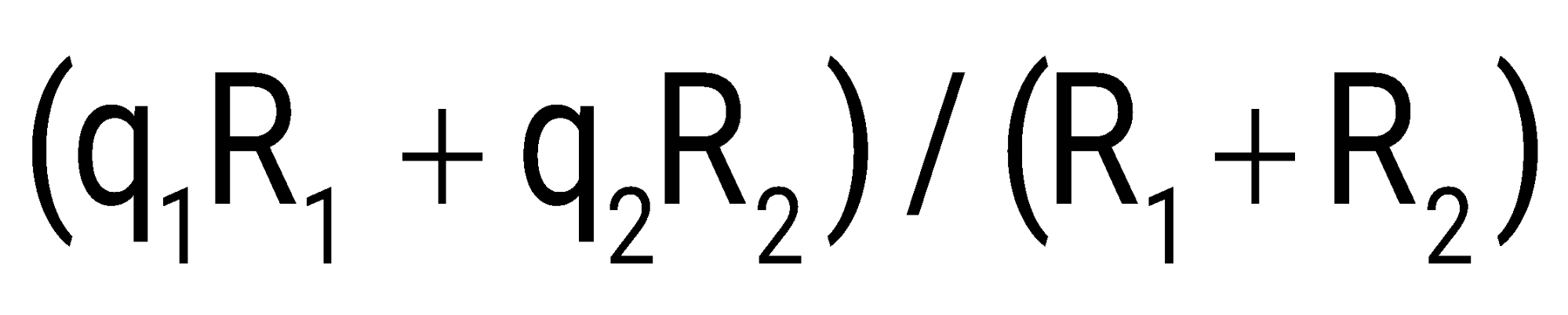

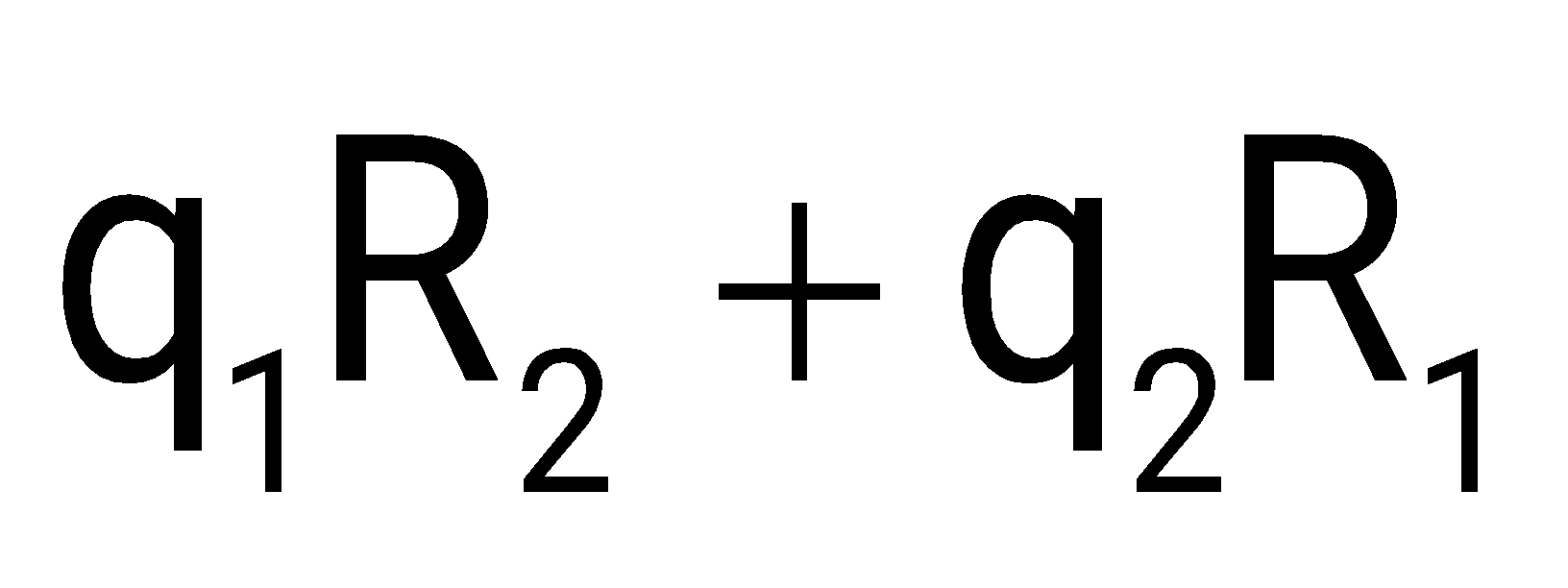

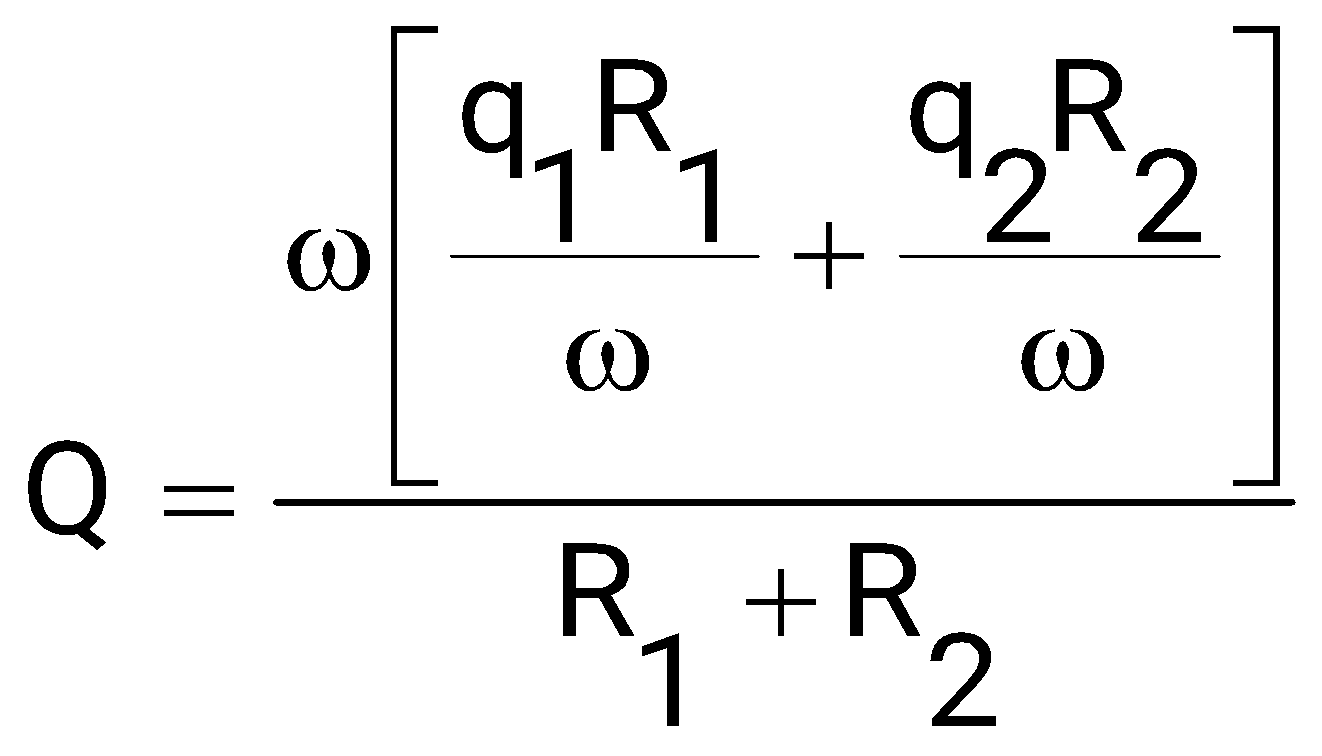

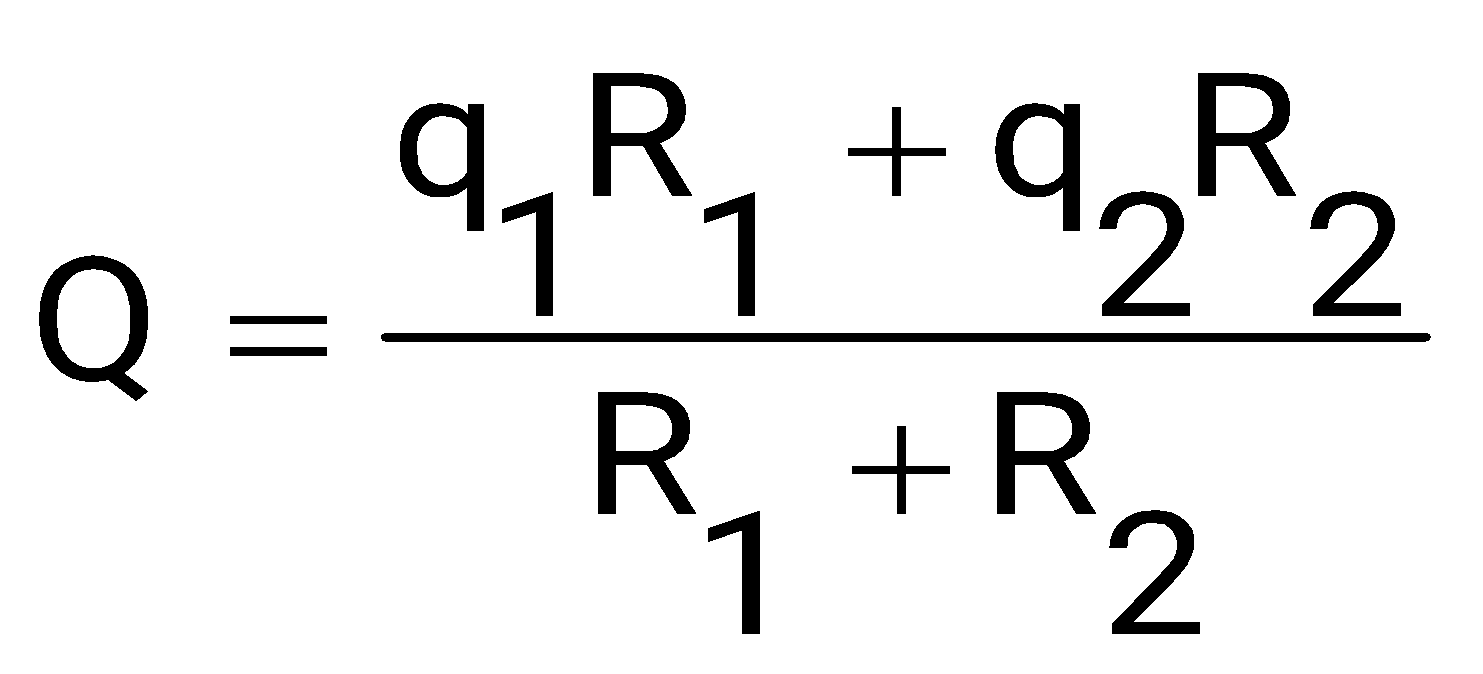

When a coil a capacitor are connected in series then overall Q-factor is

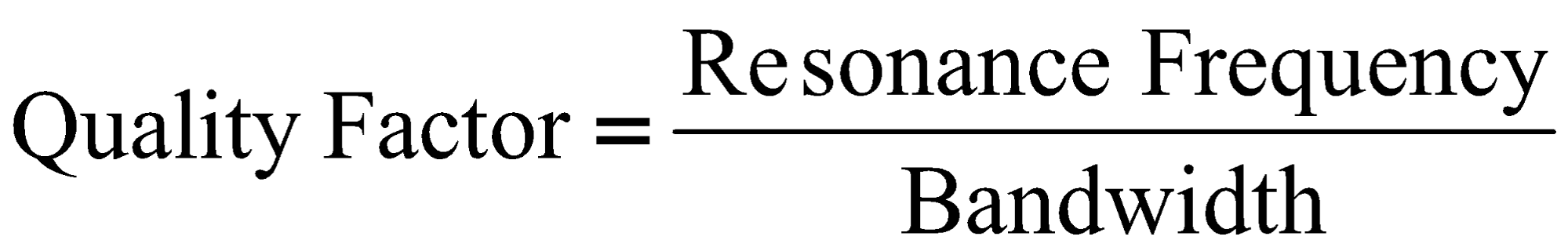

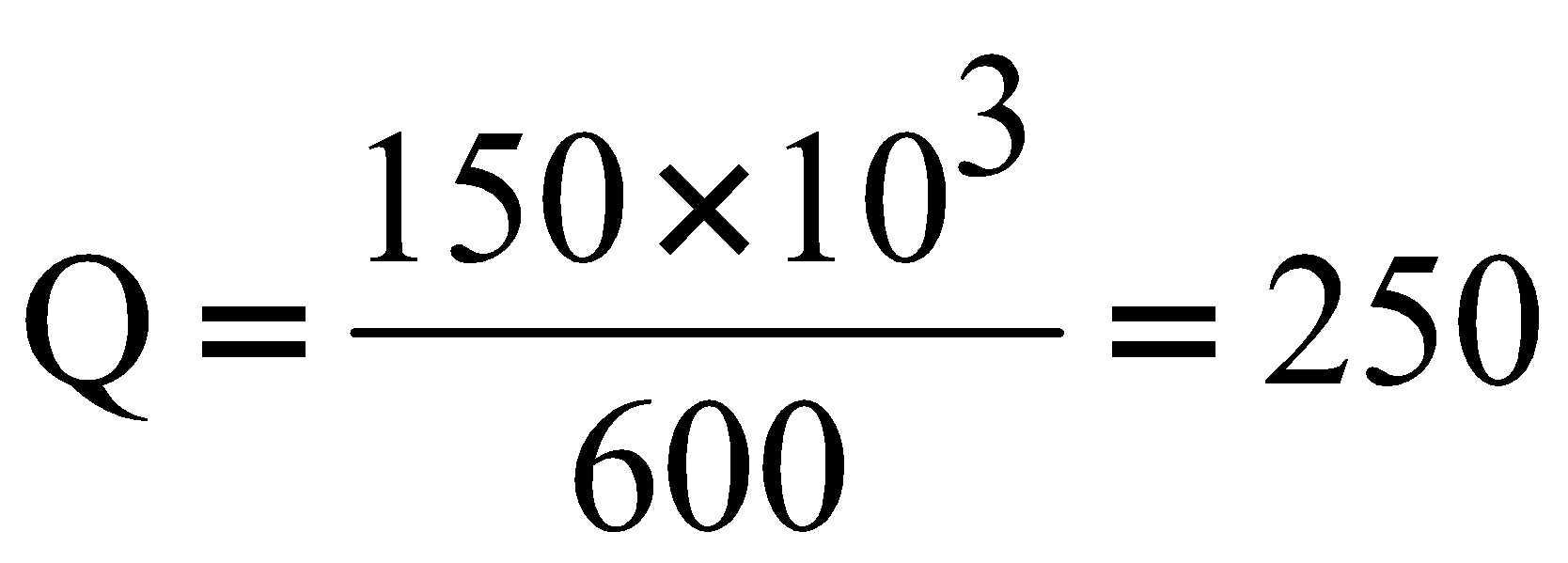

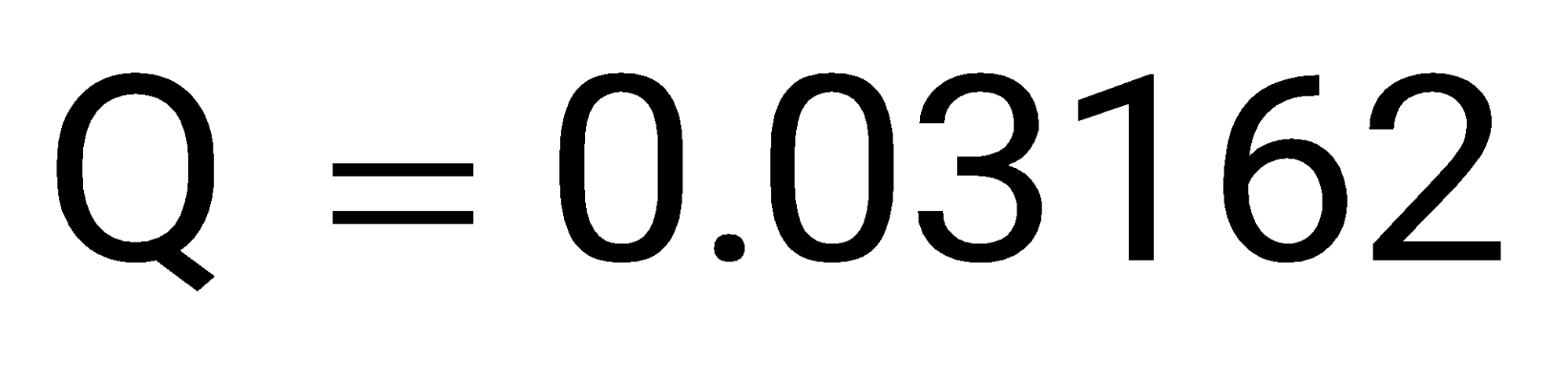

The network shown below has a resonant frequency of 150 kHz and a bandwidth of 600 Hz. The 𝑄-factor of the network is __________. (round off to nearest integer)

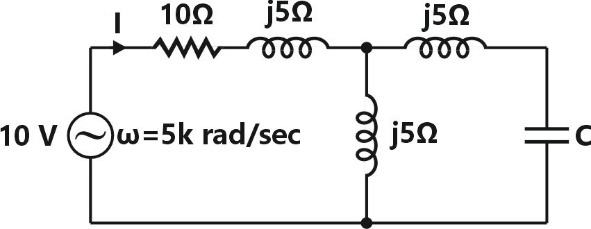

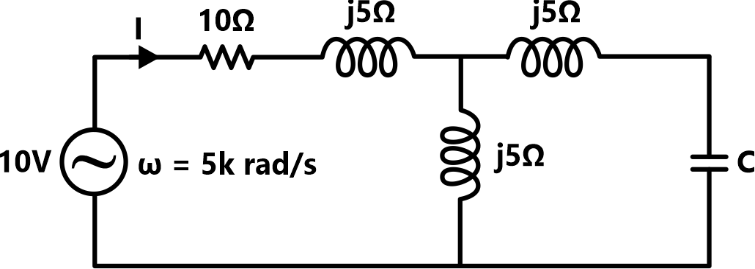

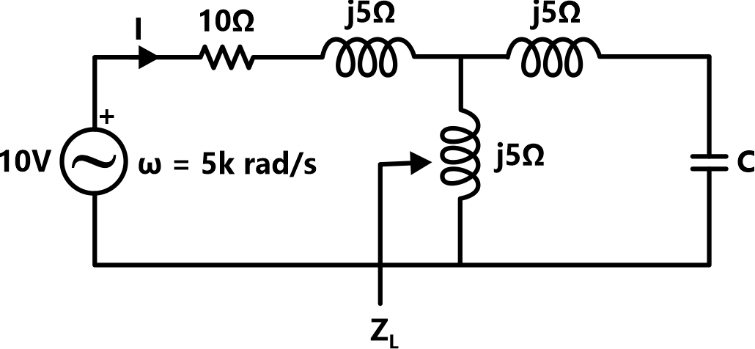

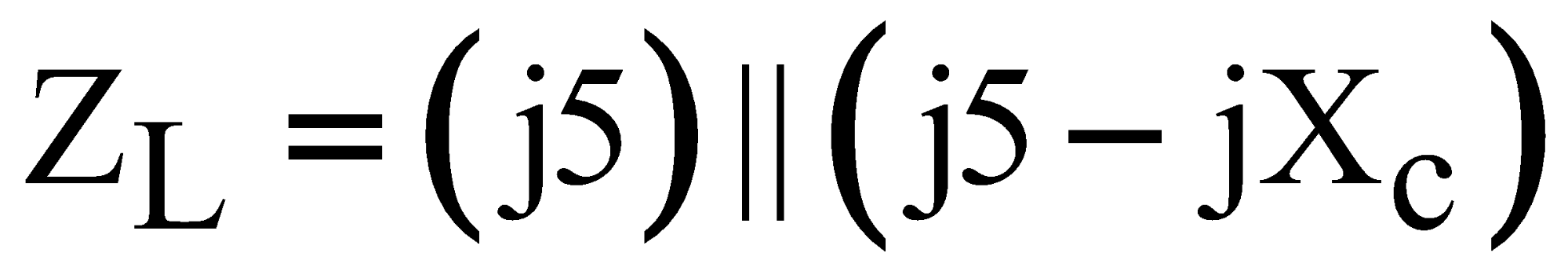

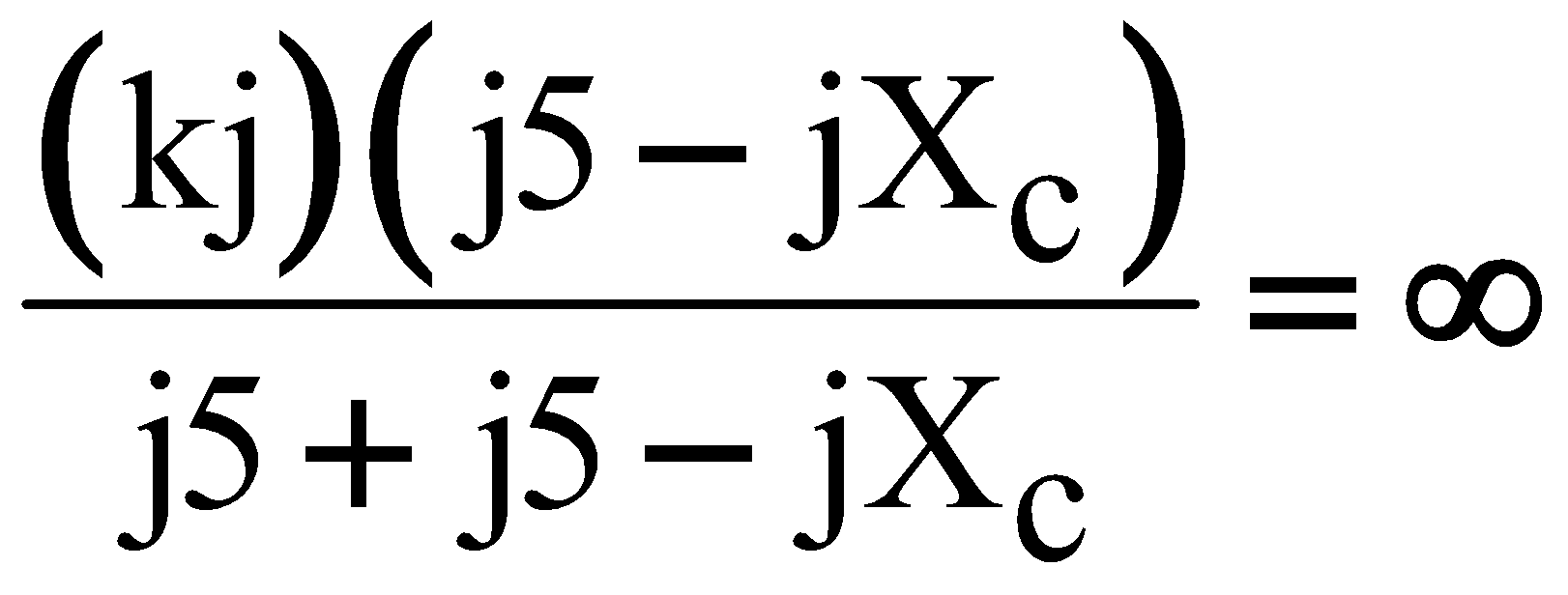

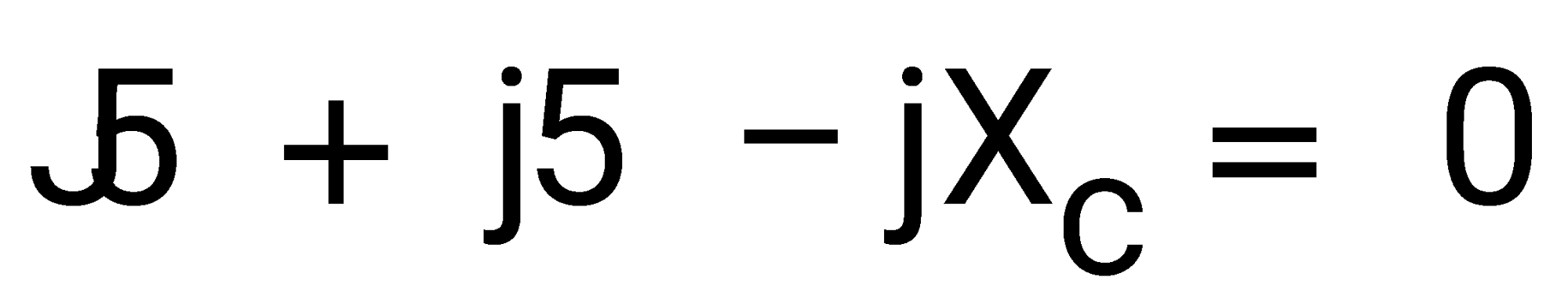

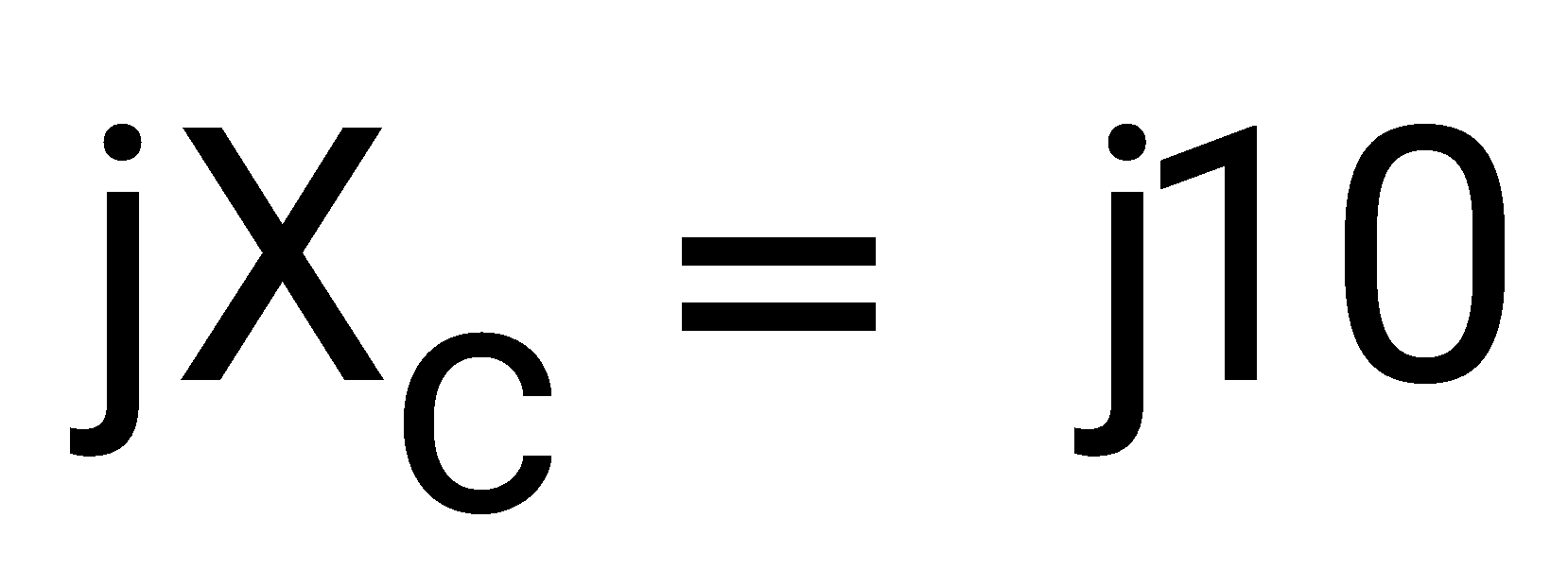

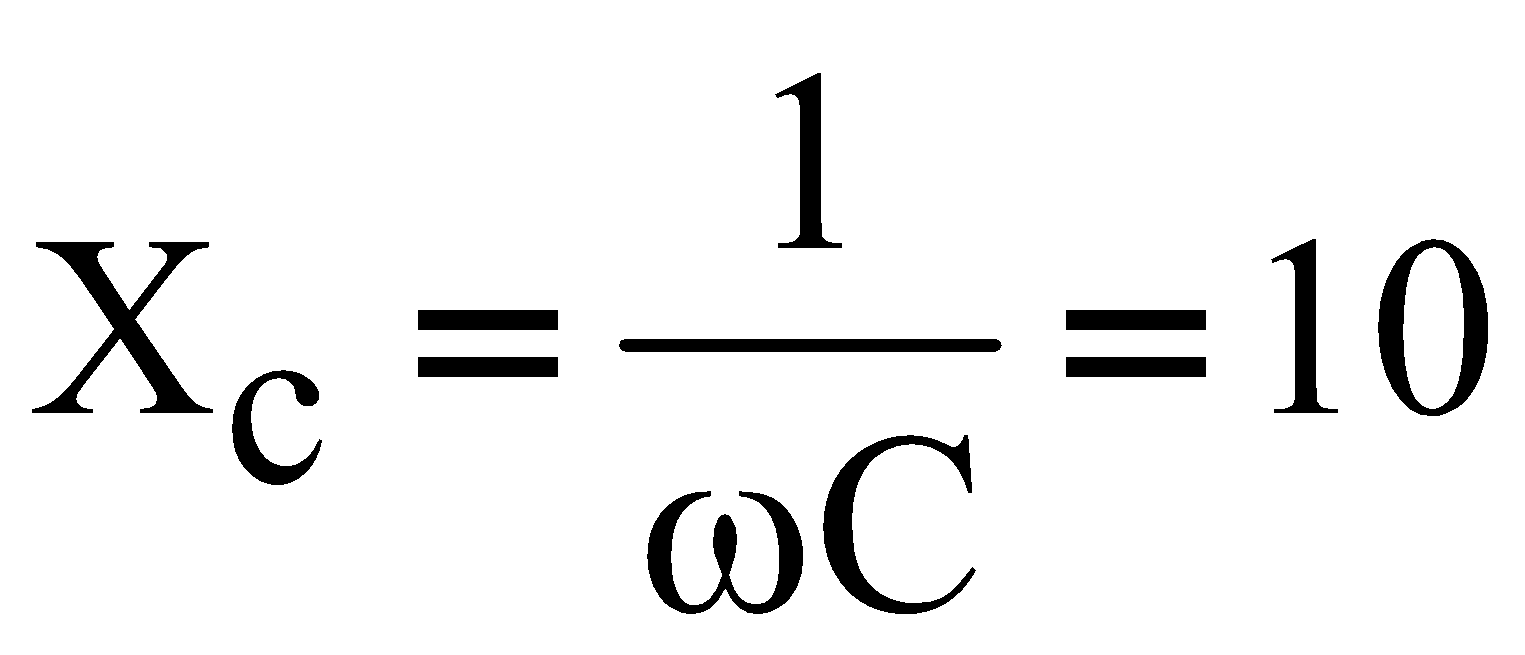

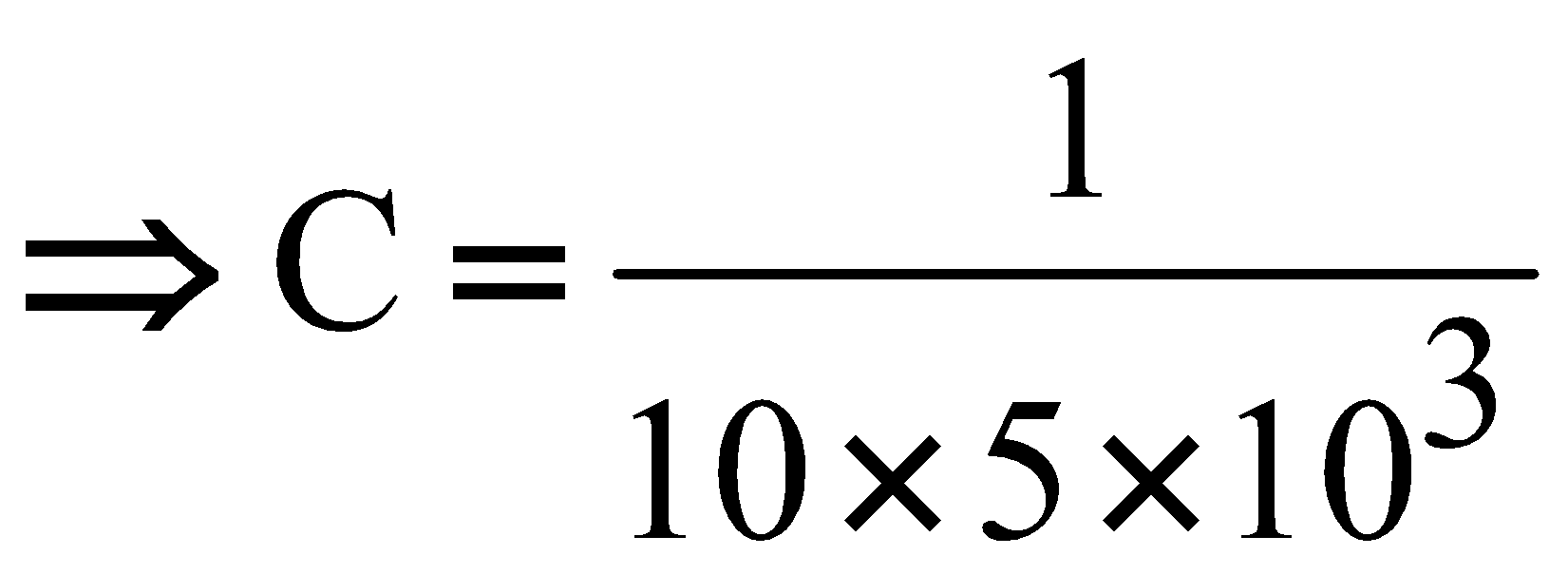

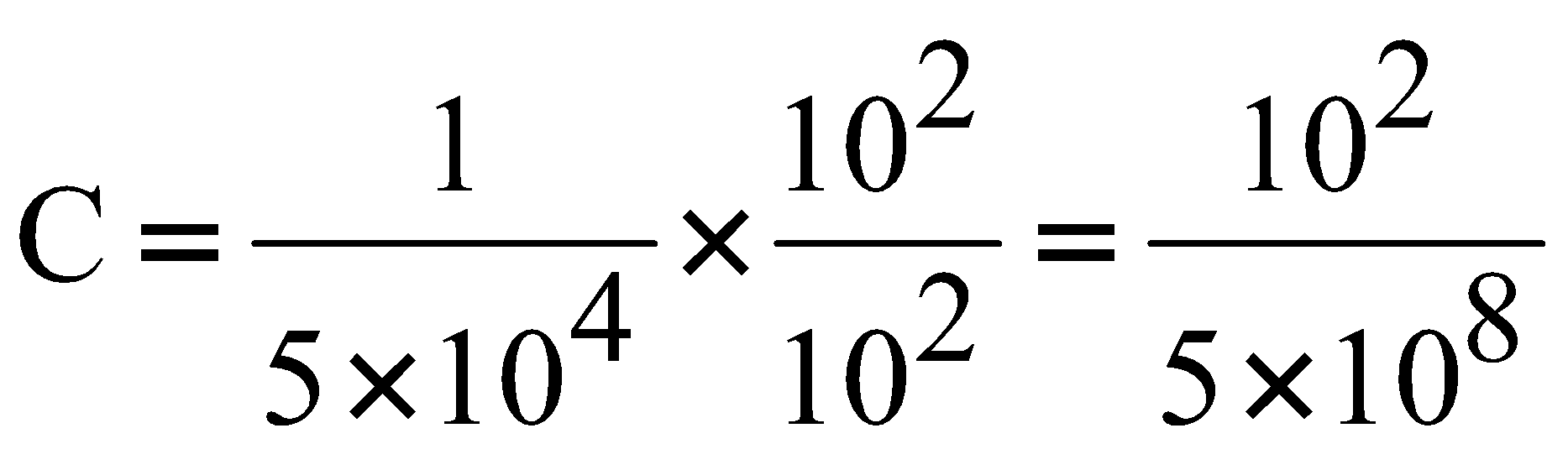

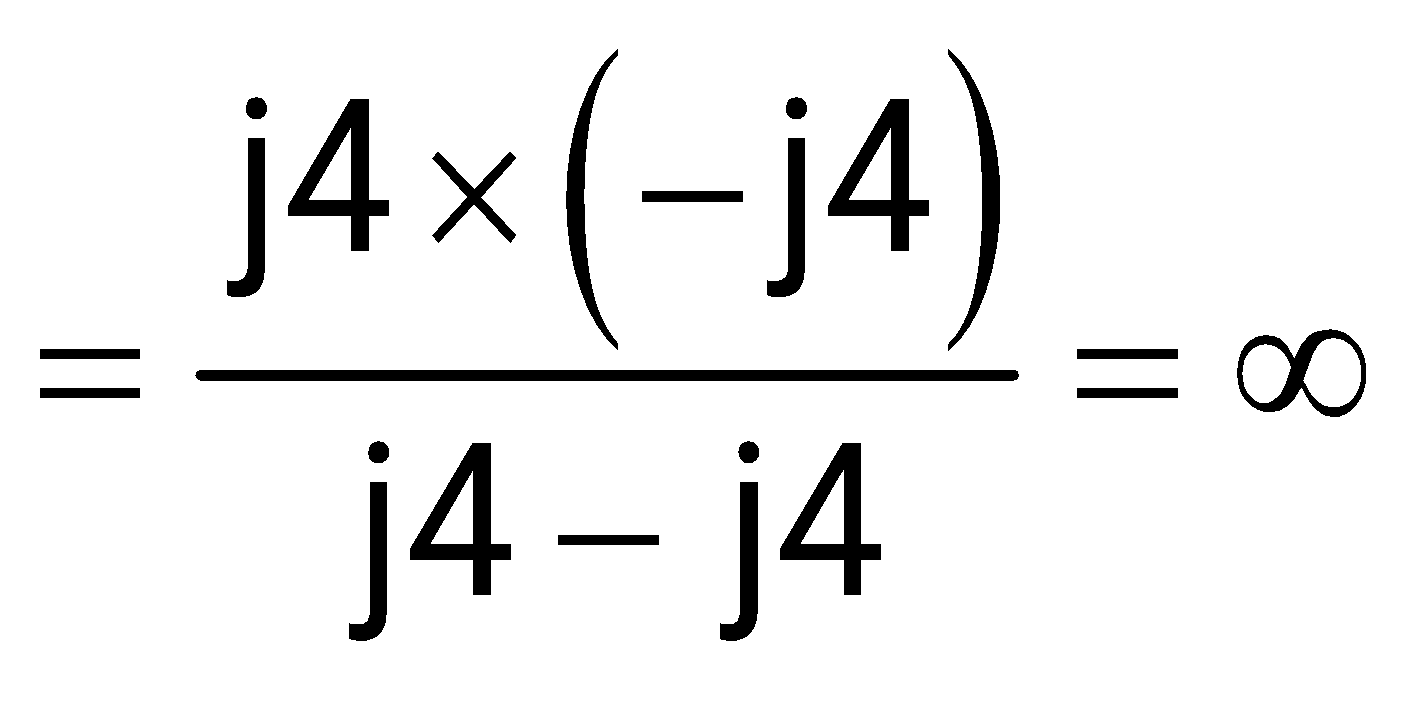

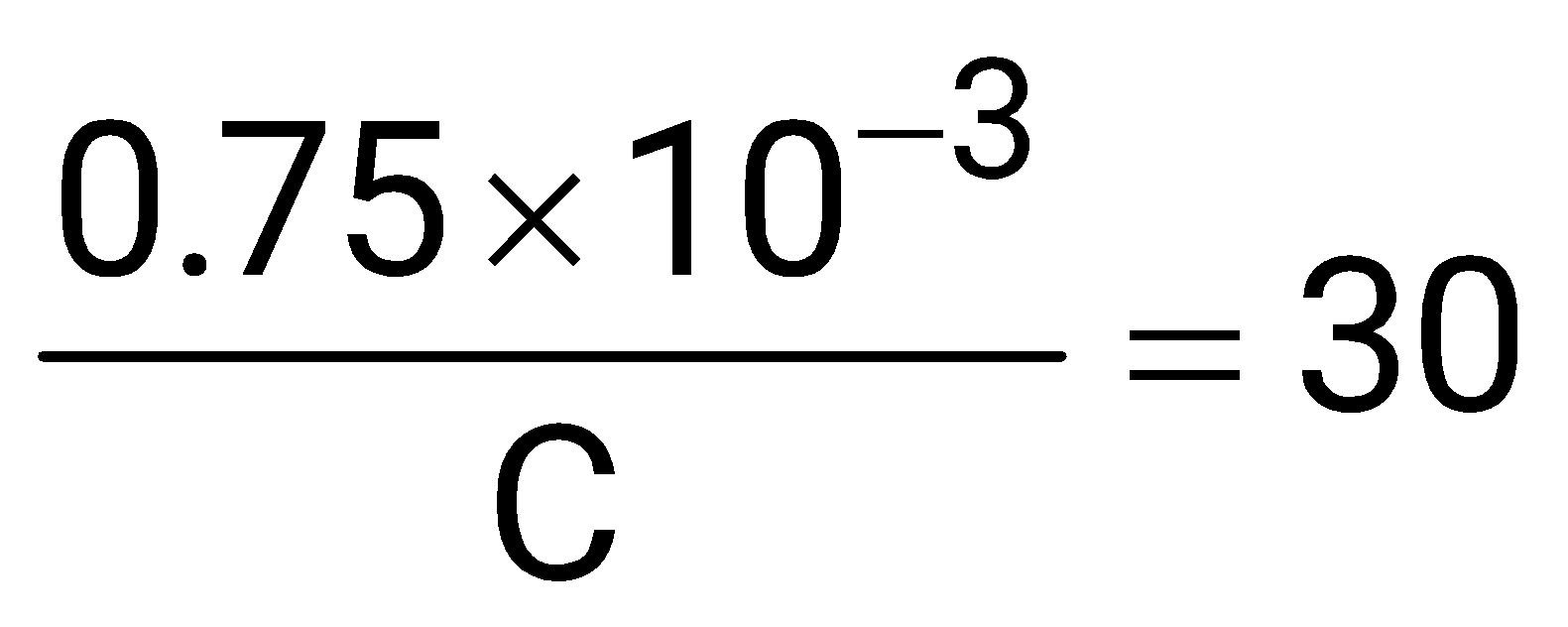

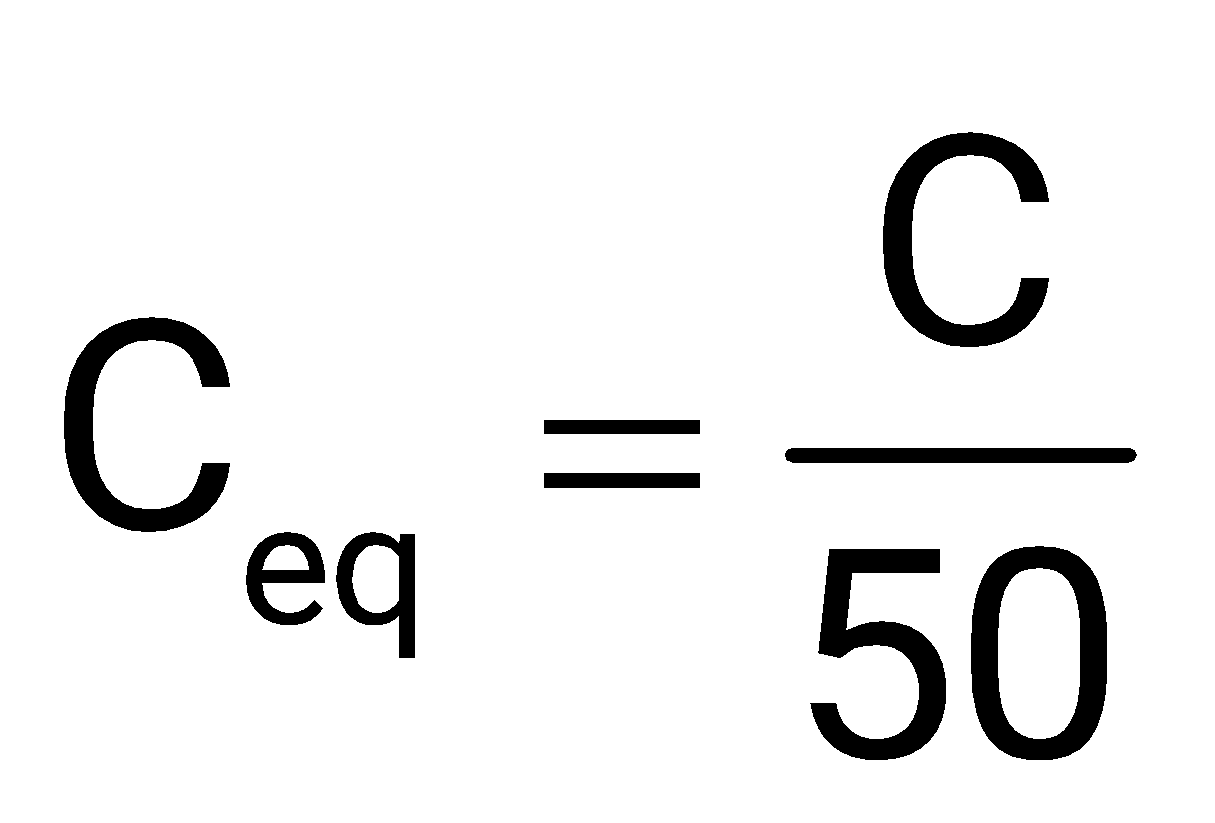

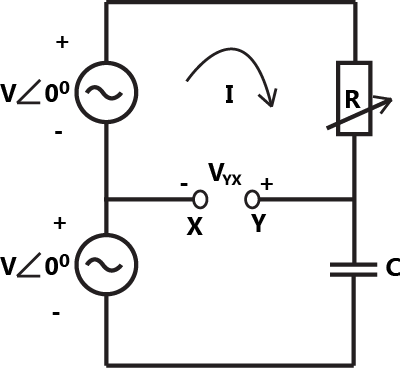

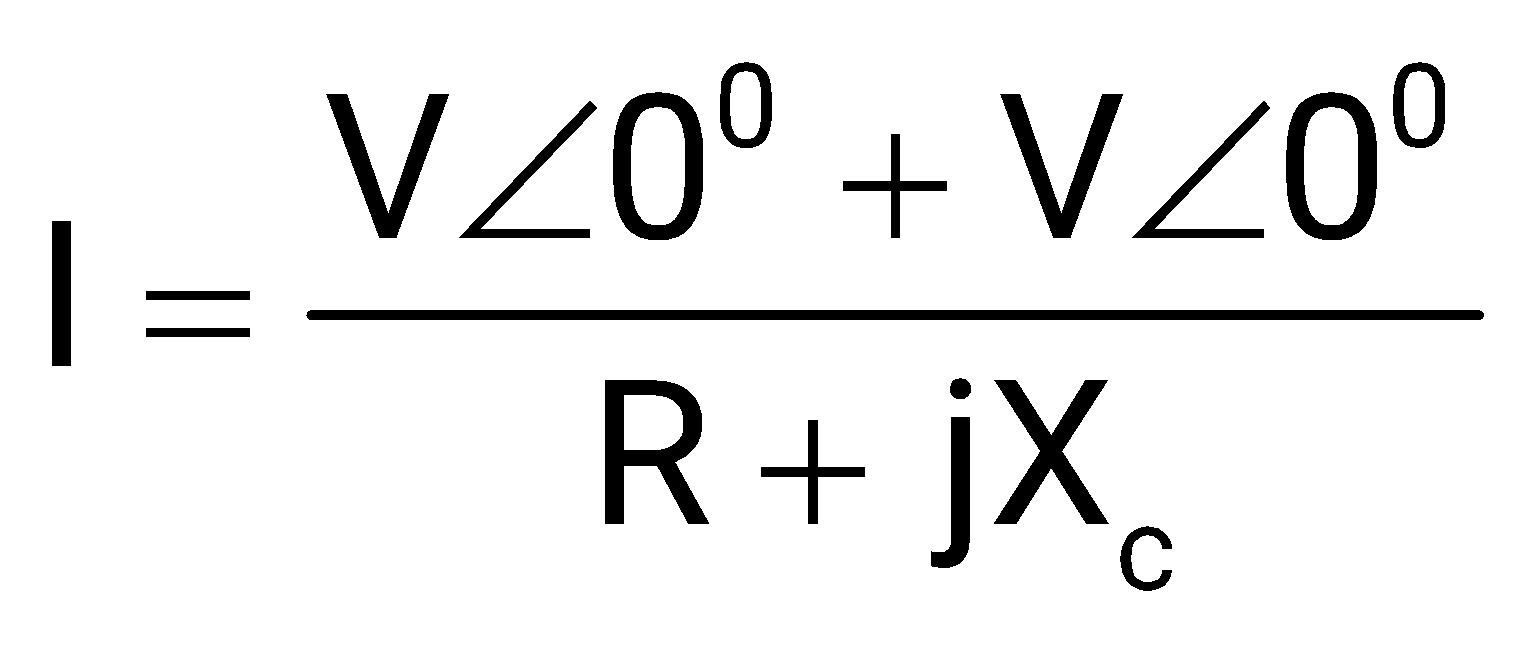

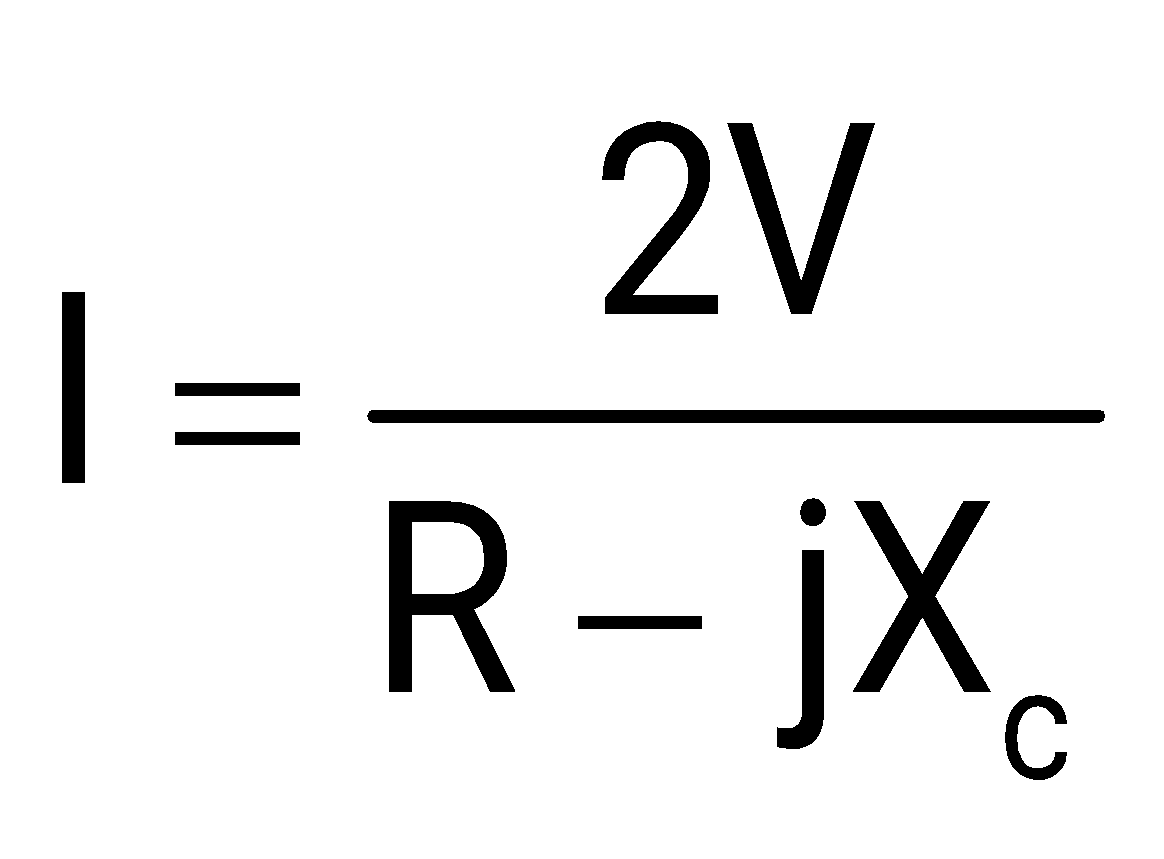

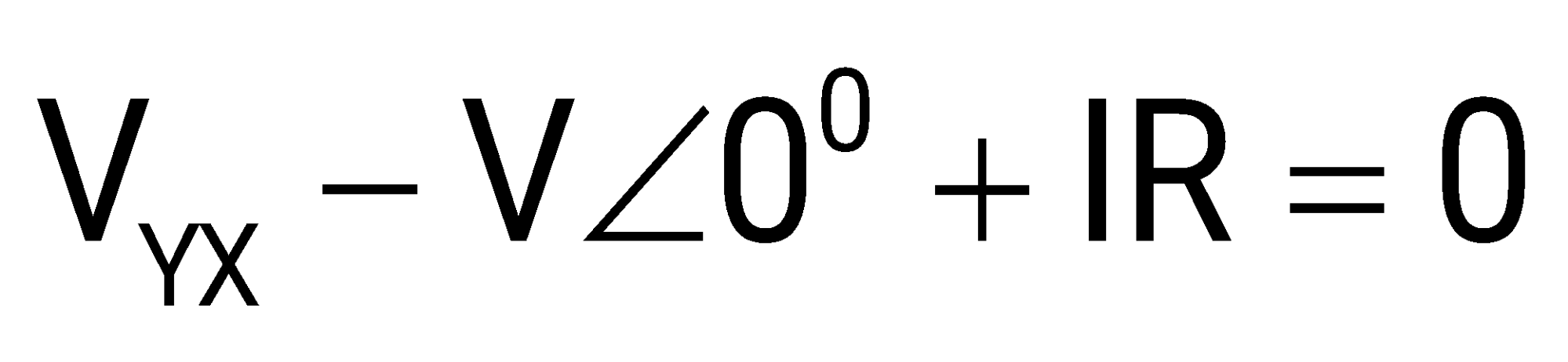

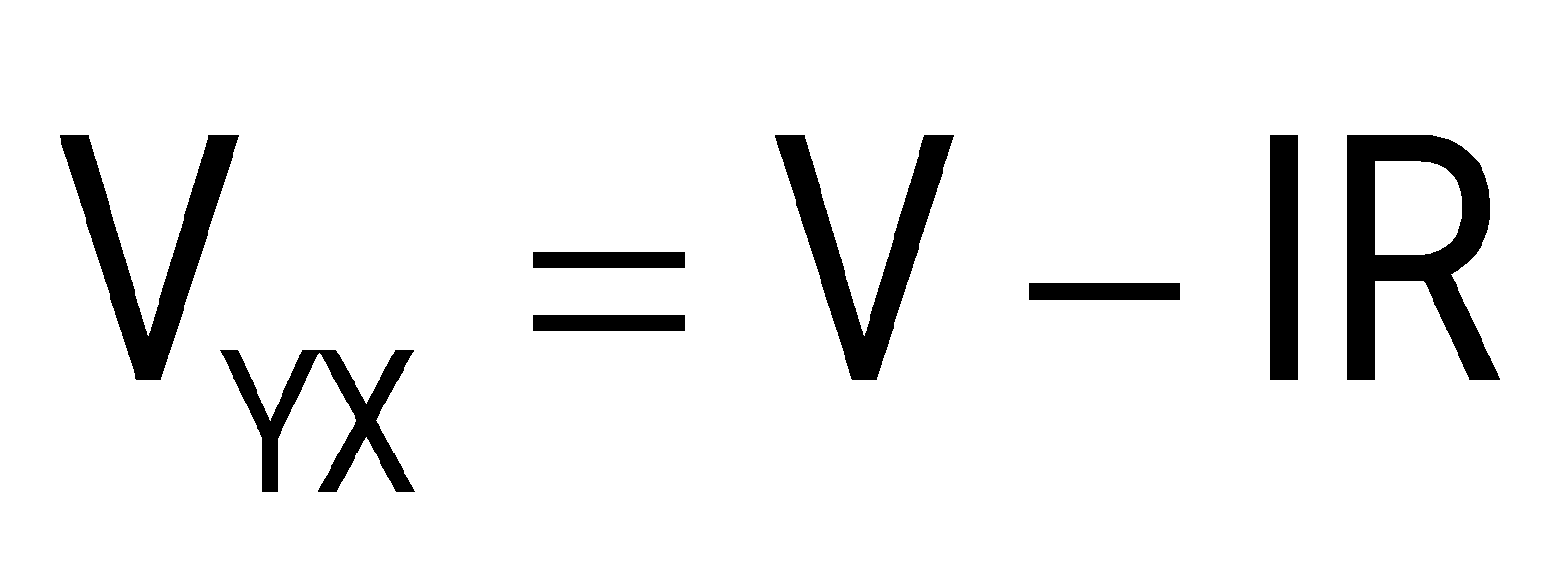

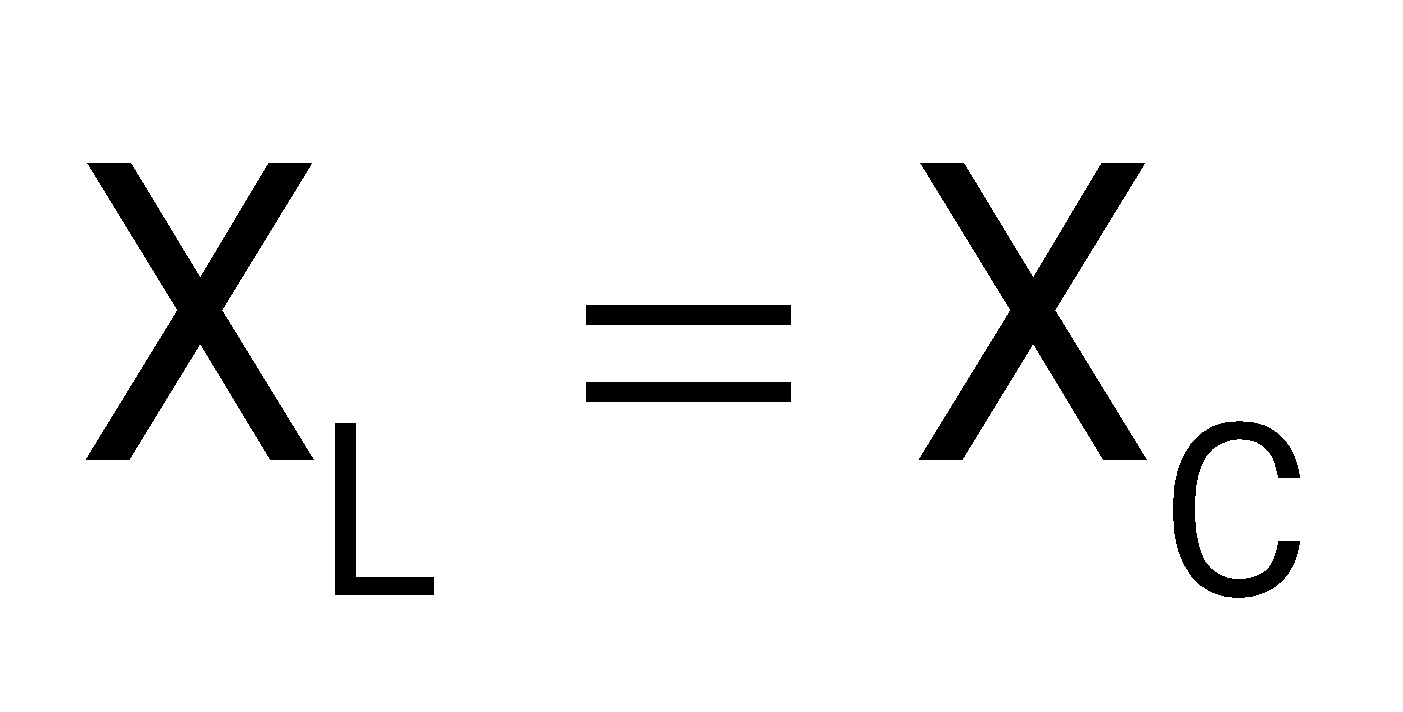

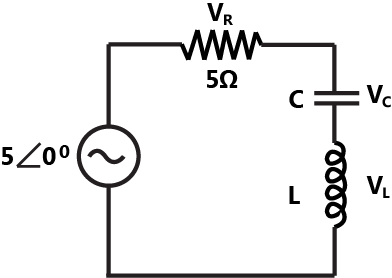

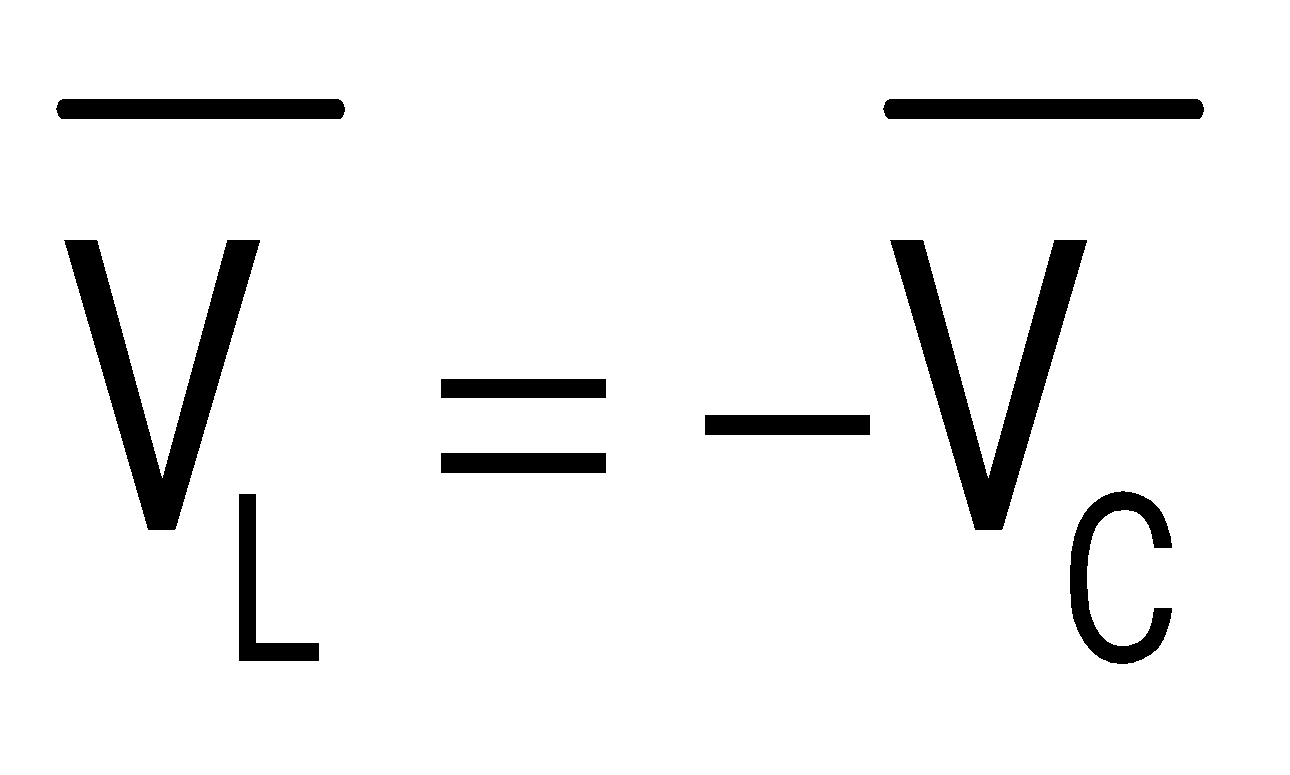

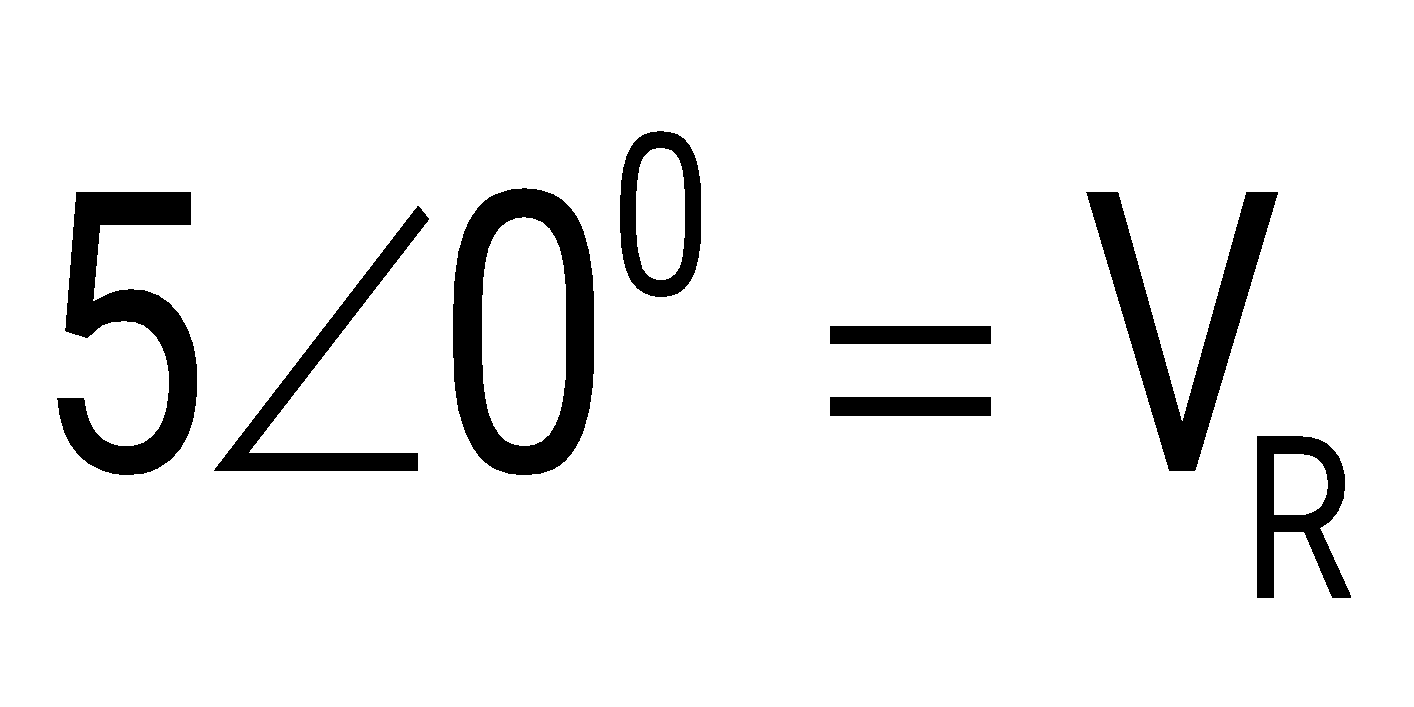

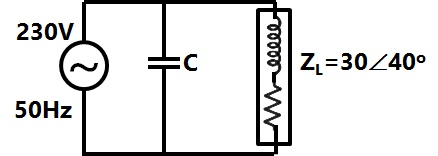

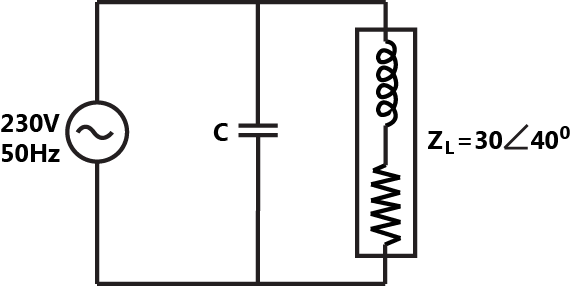

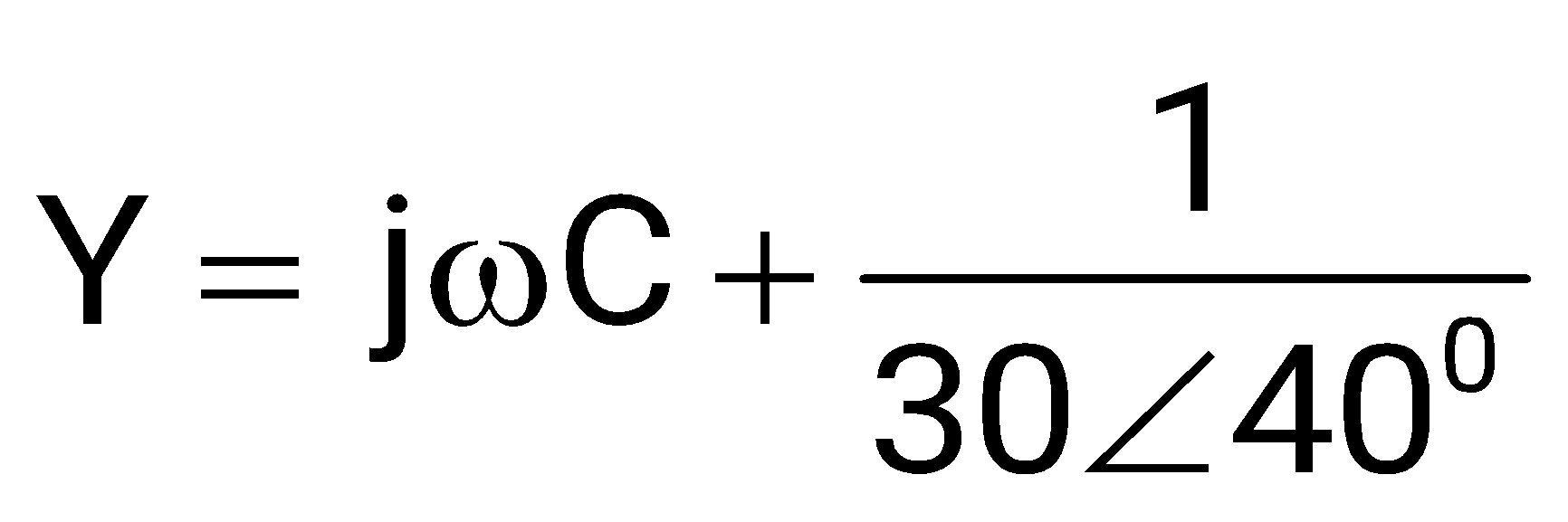

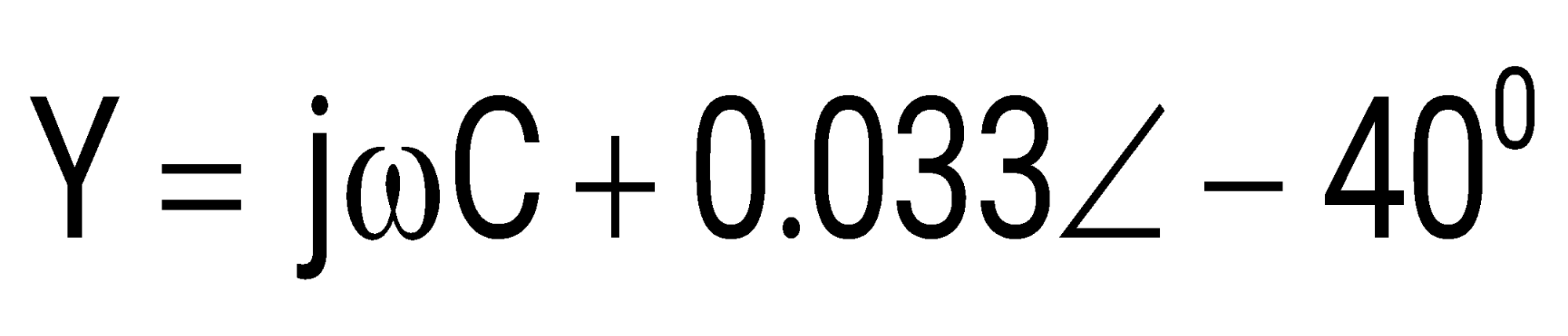

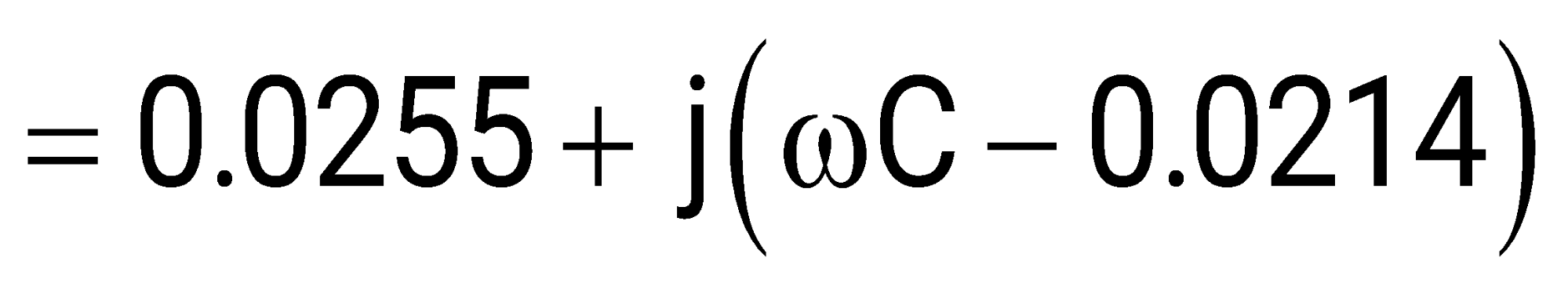

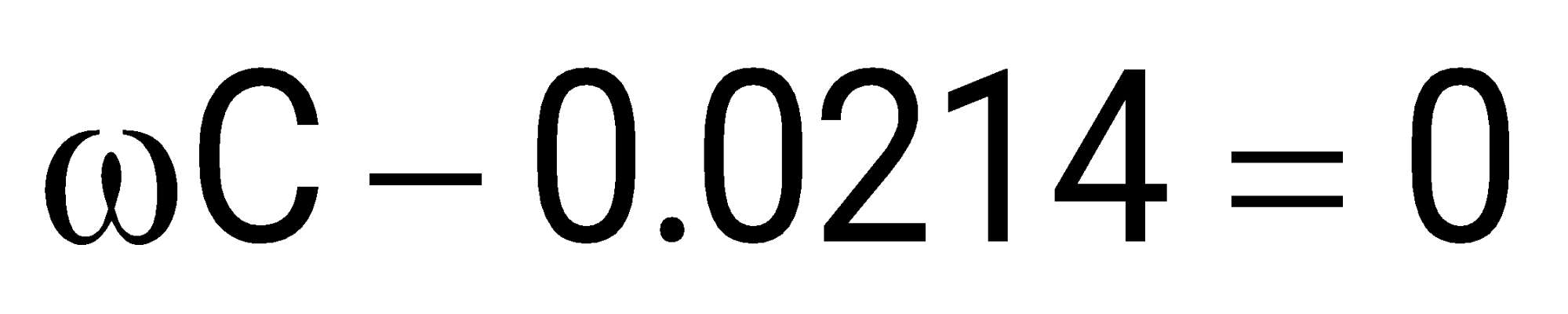

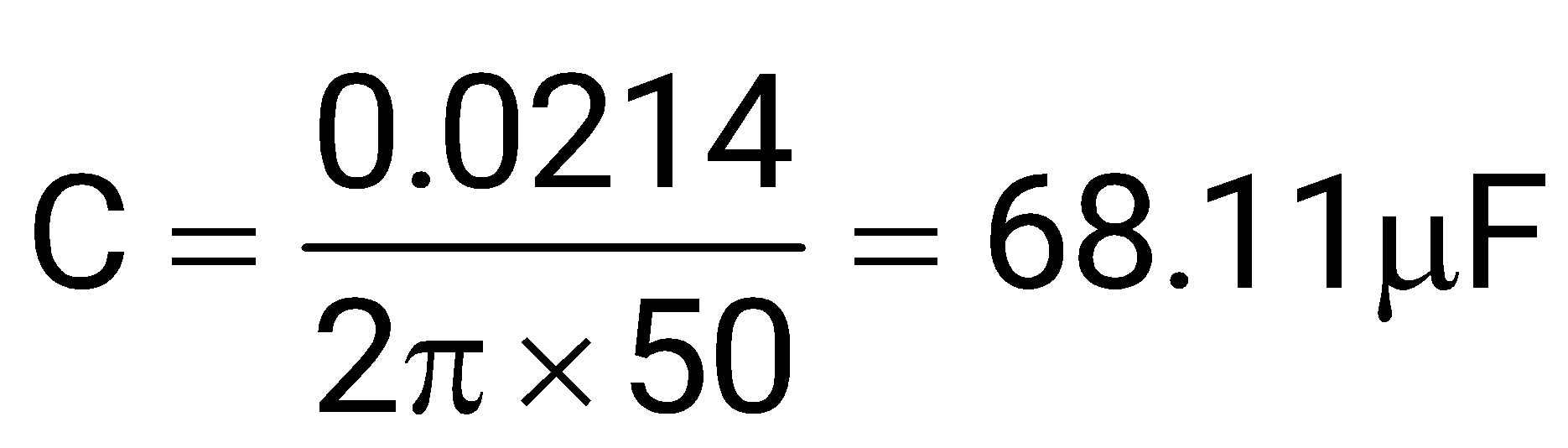

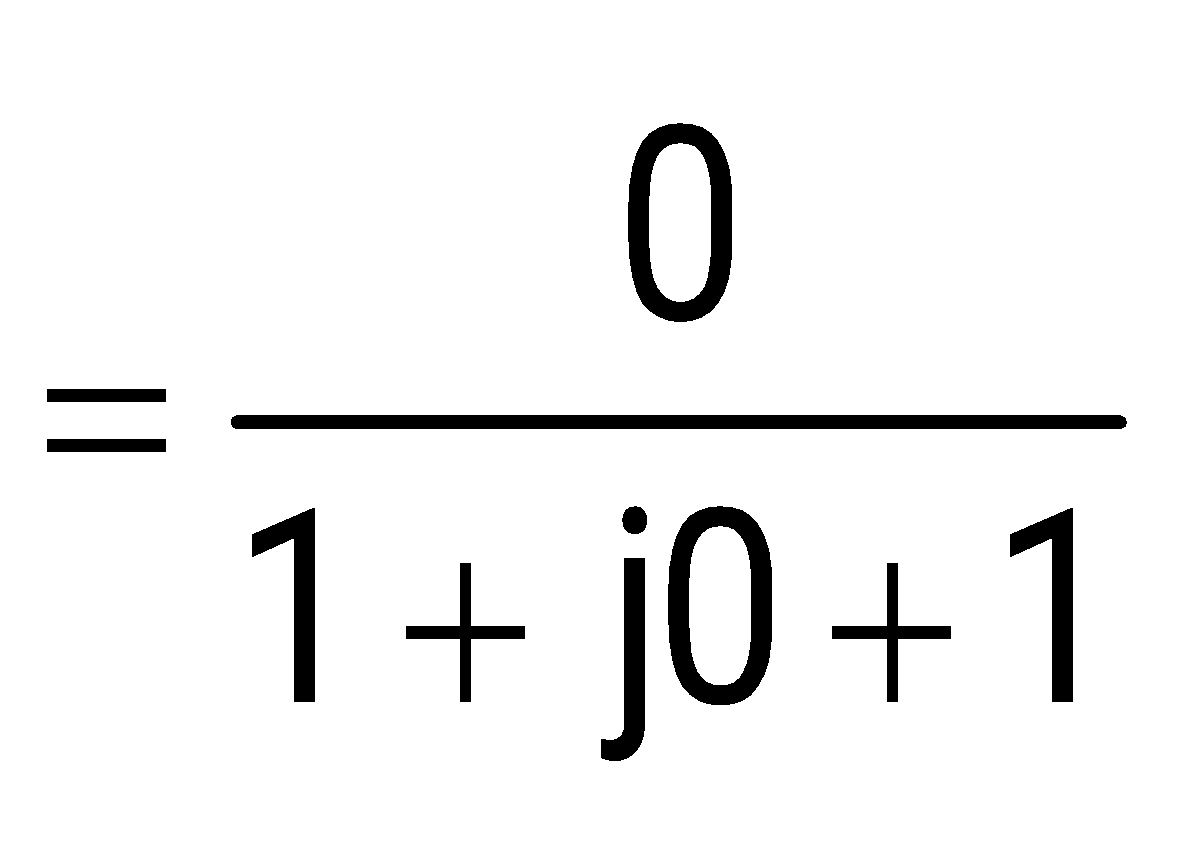

In the given circuit, the value of capacitor C that makes current I = 0 is _________ μF.

⇒

⇒ Xc = 10 Ω

= 20 μF

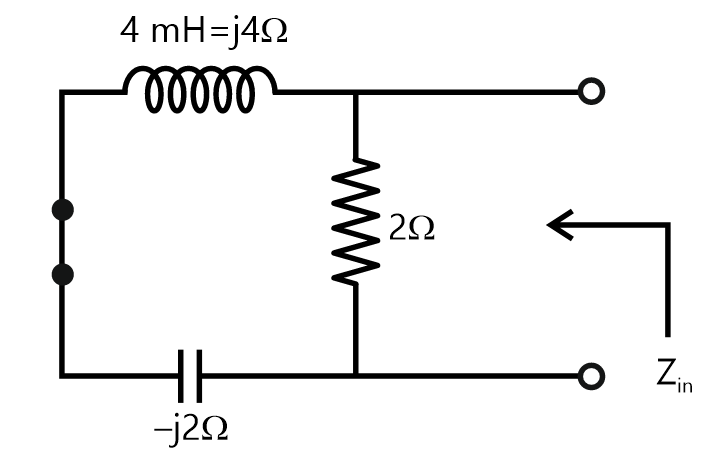

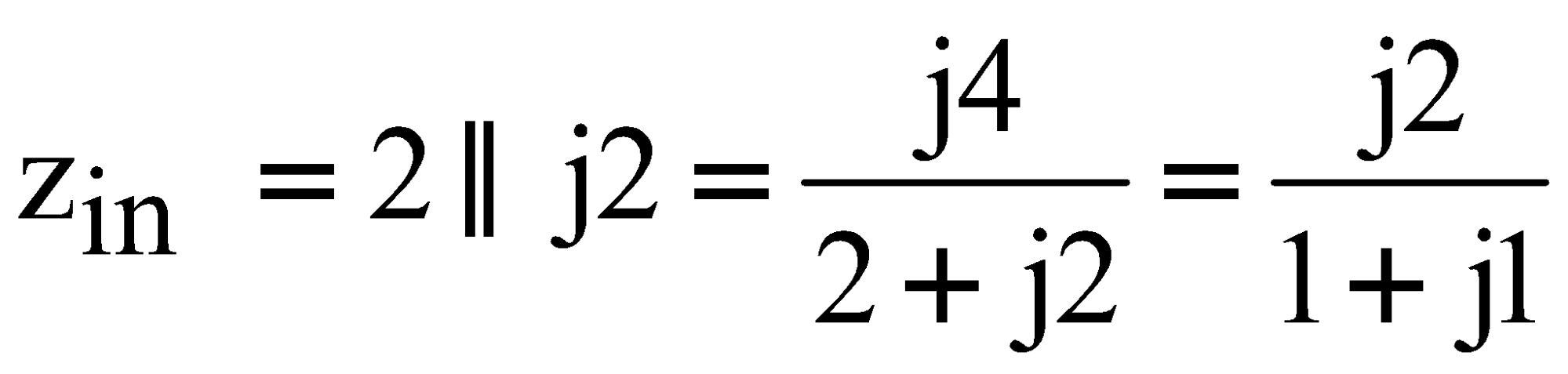

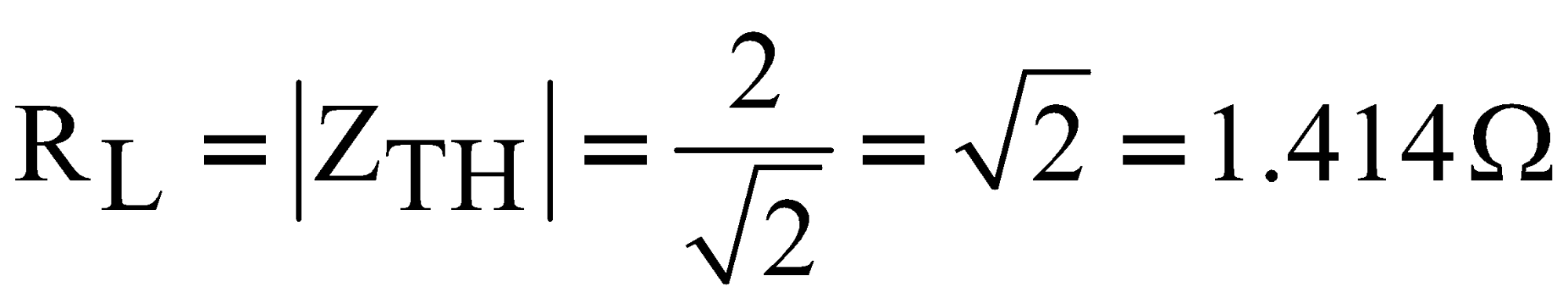

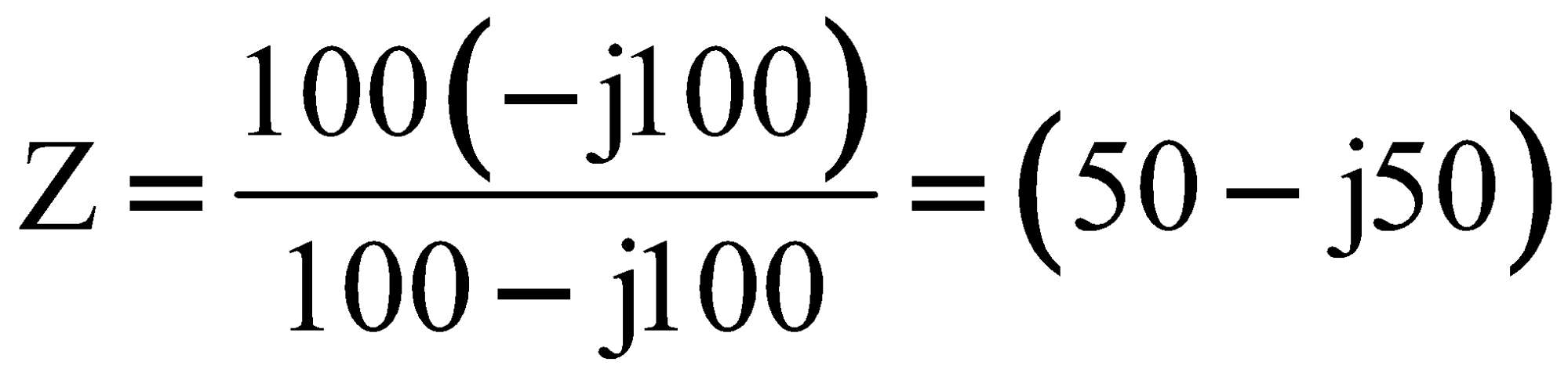

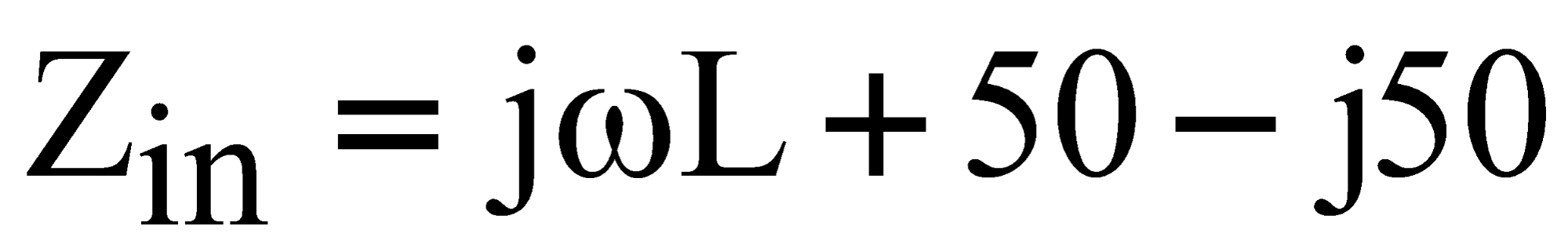

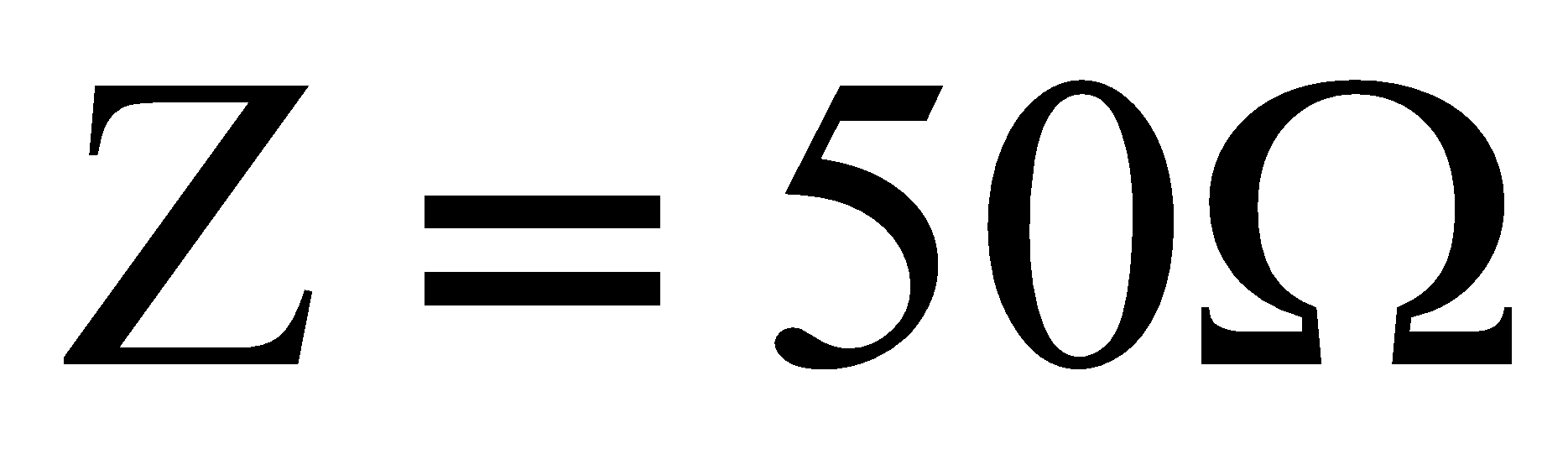

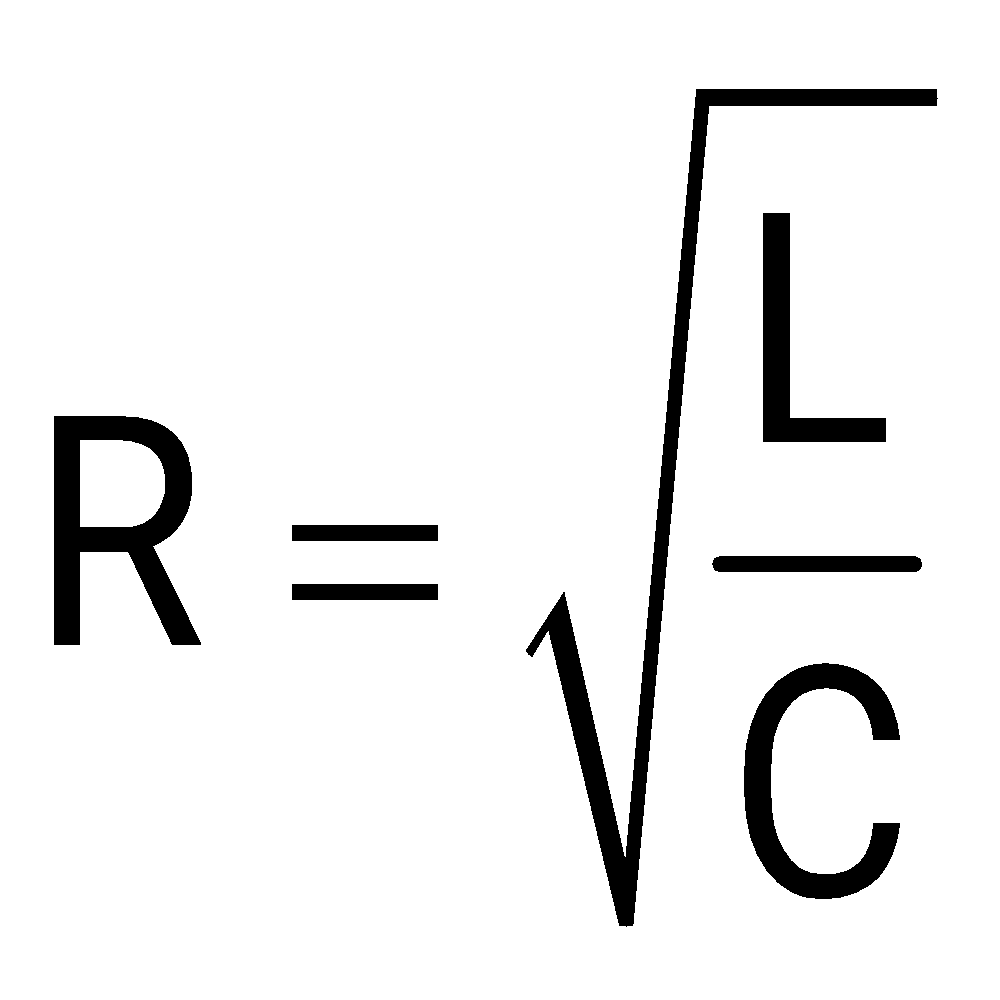

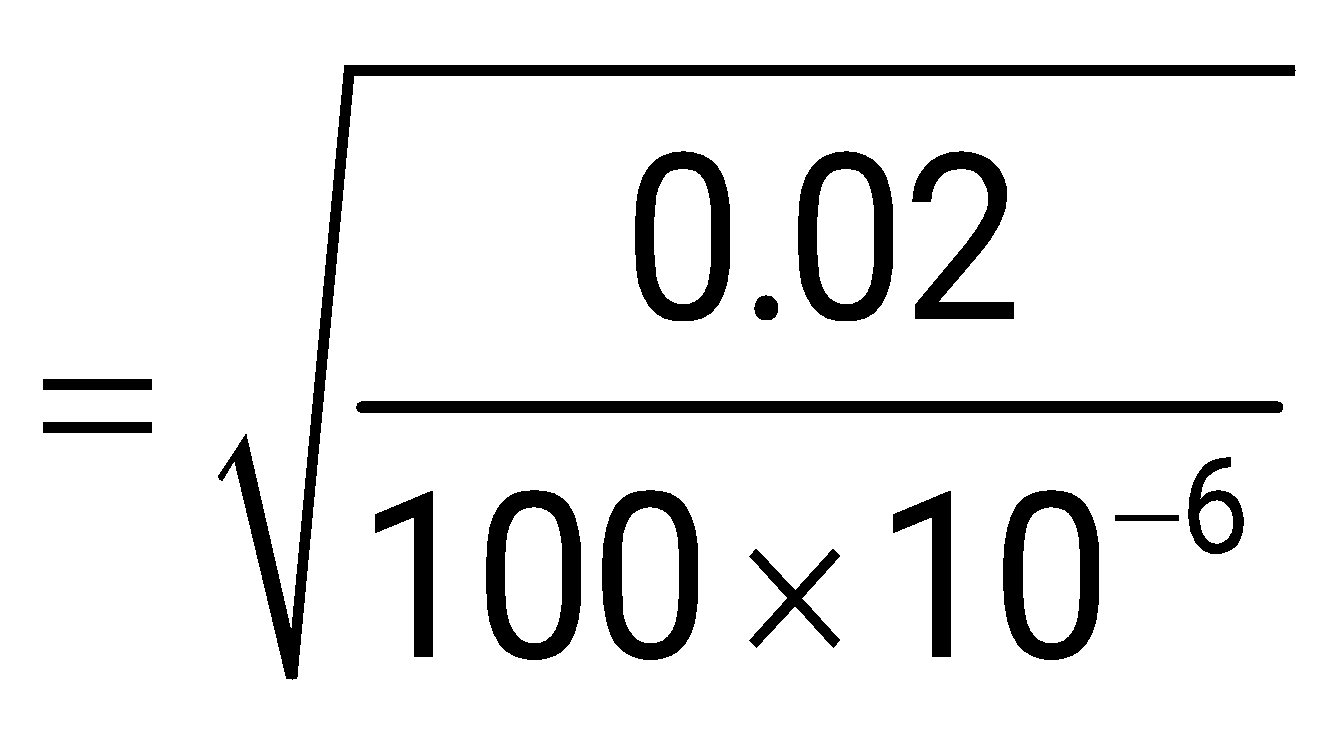

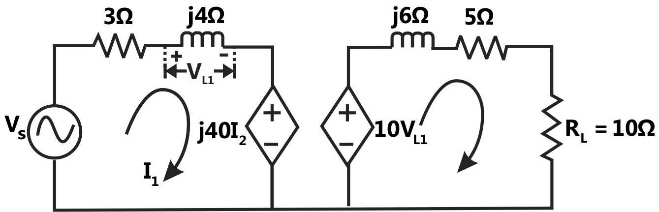

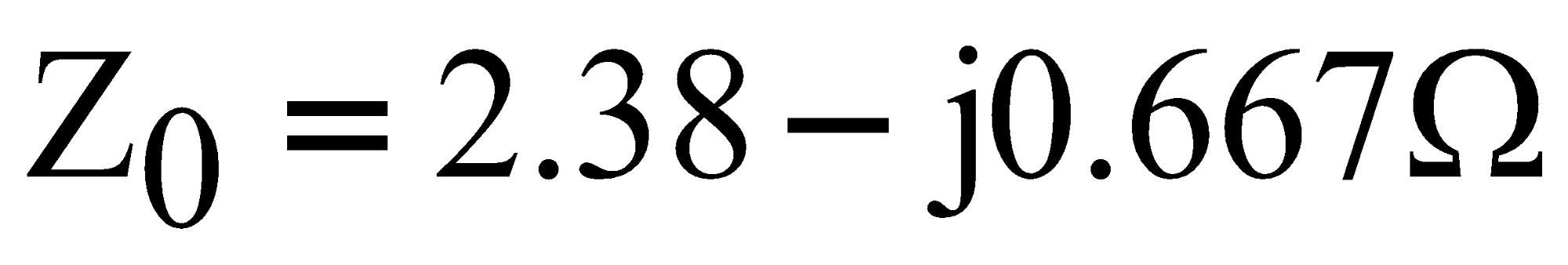

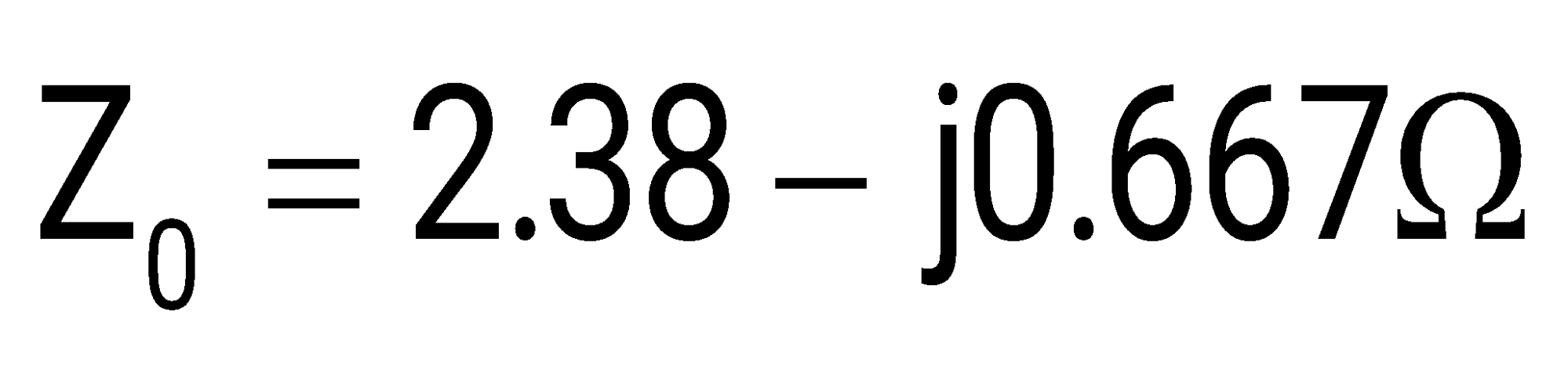

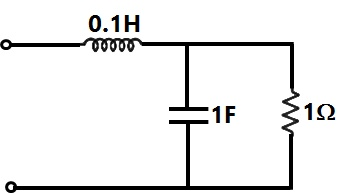

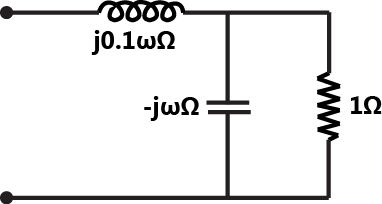

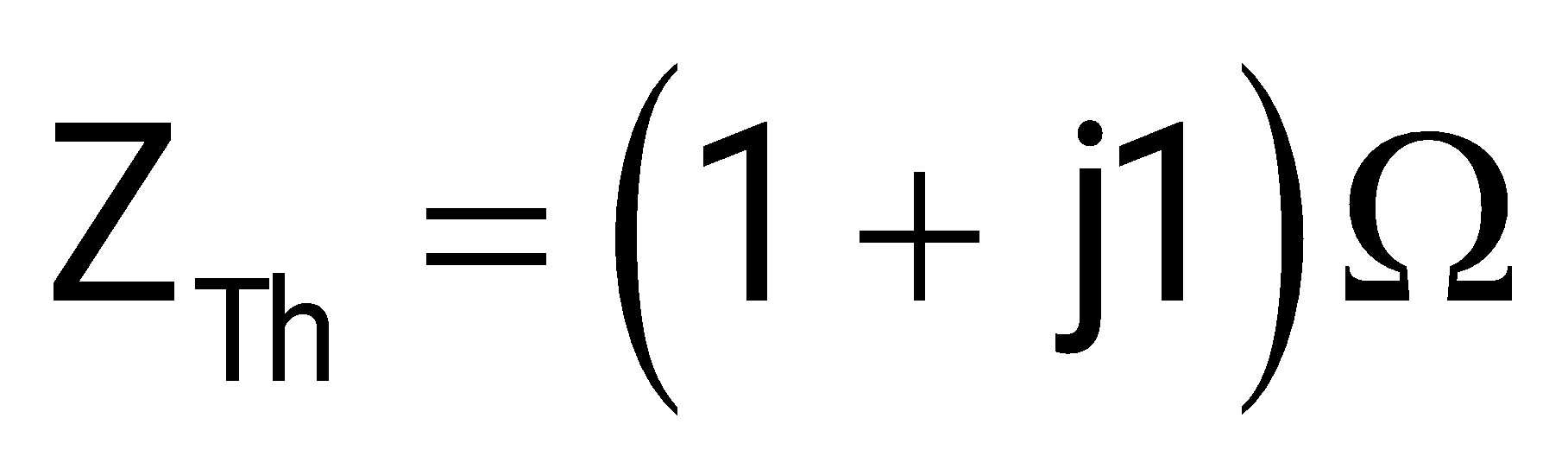

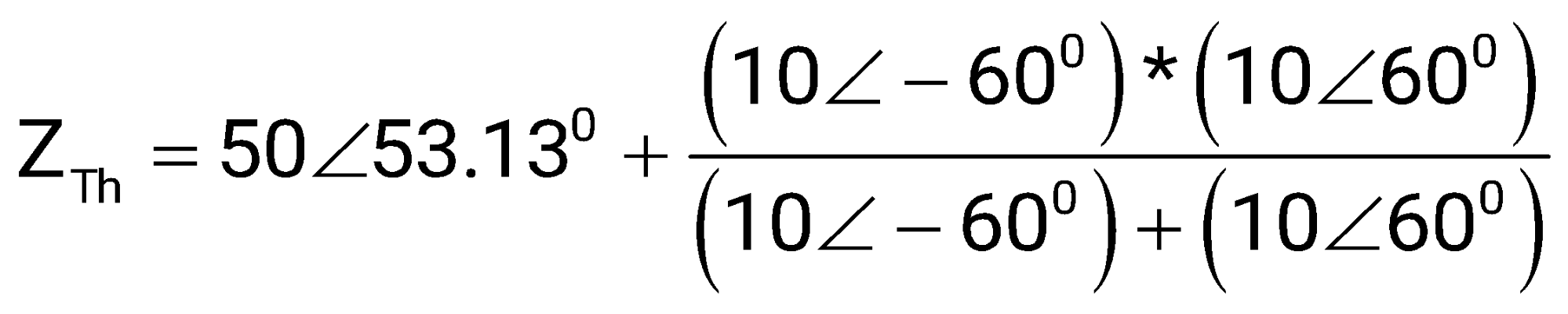

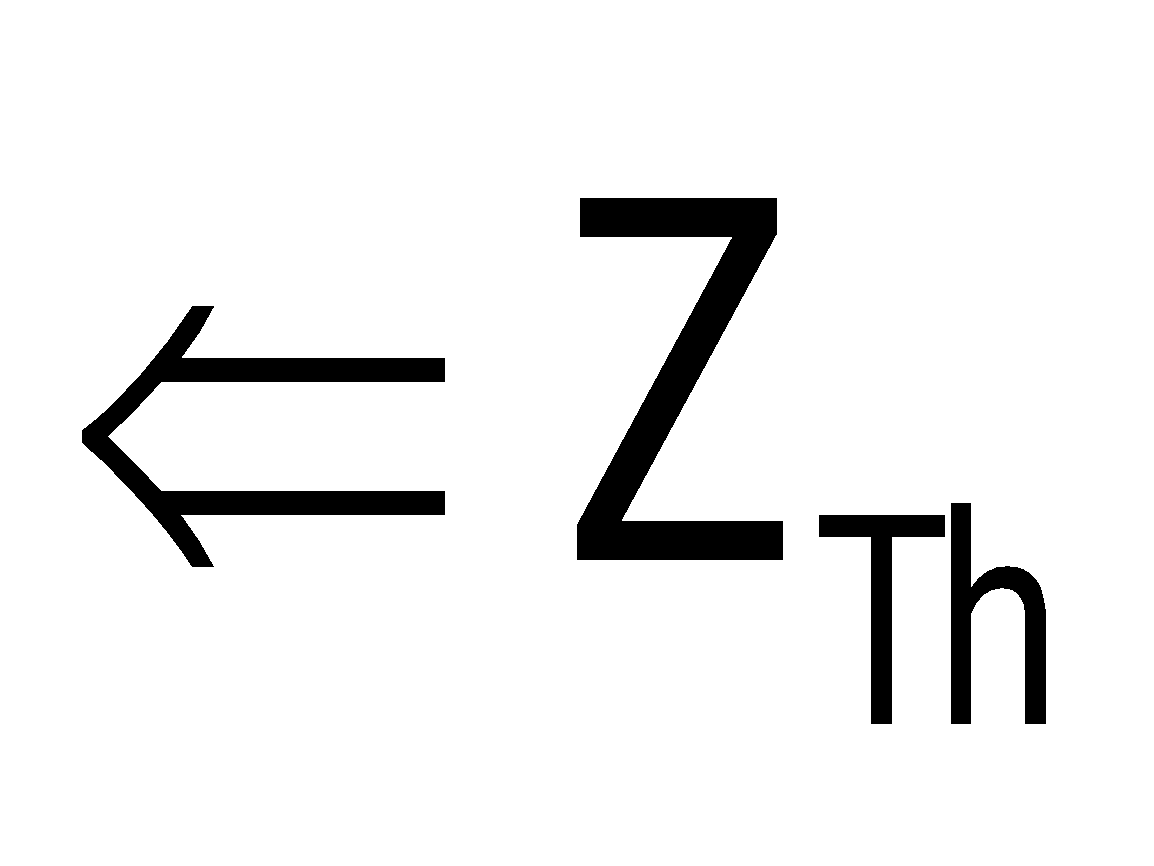

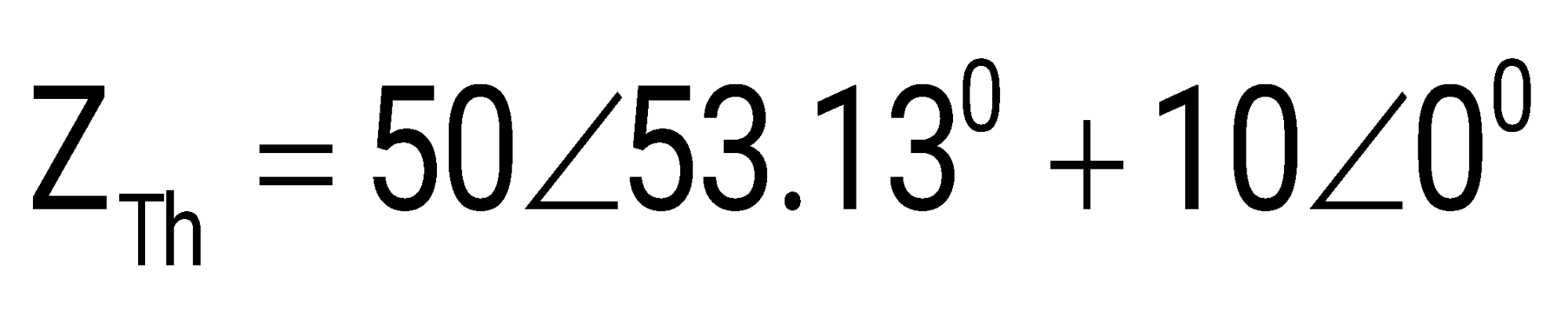

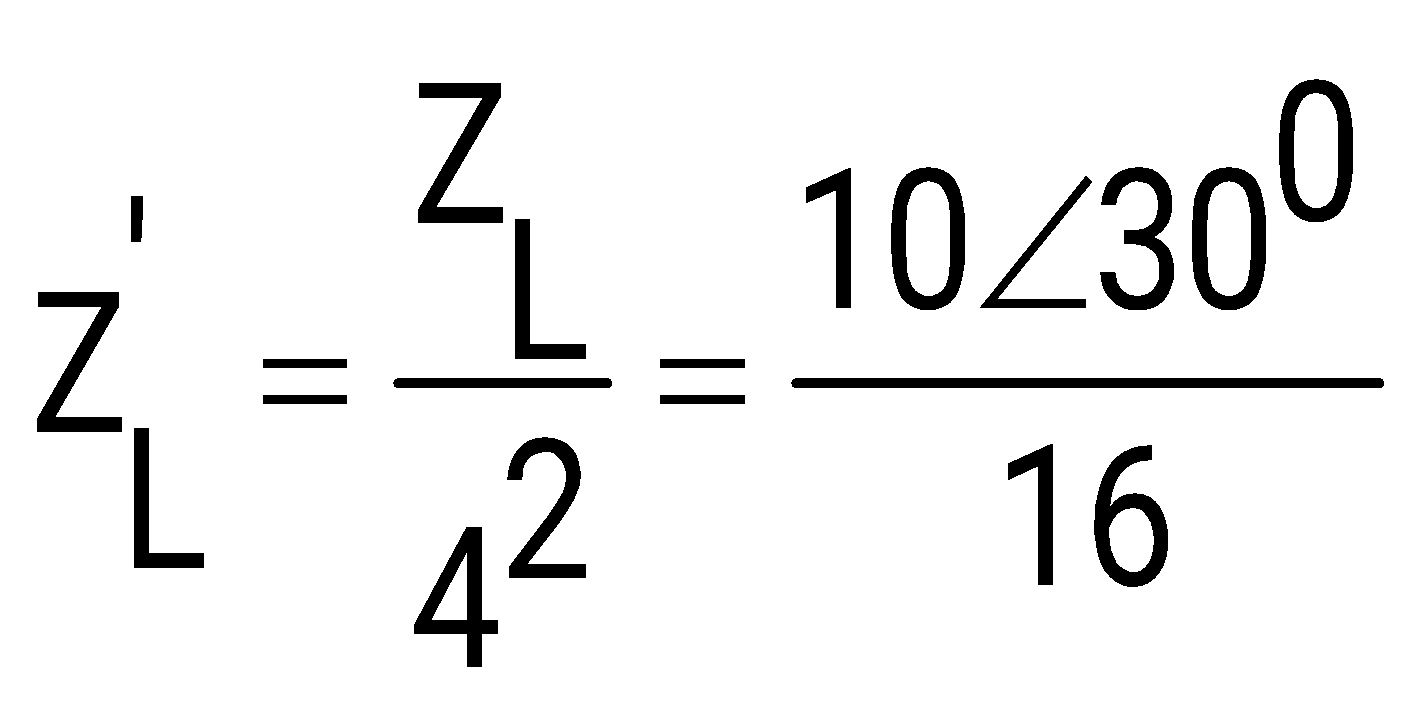

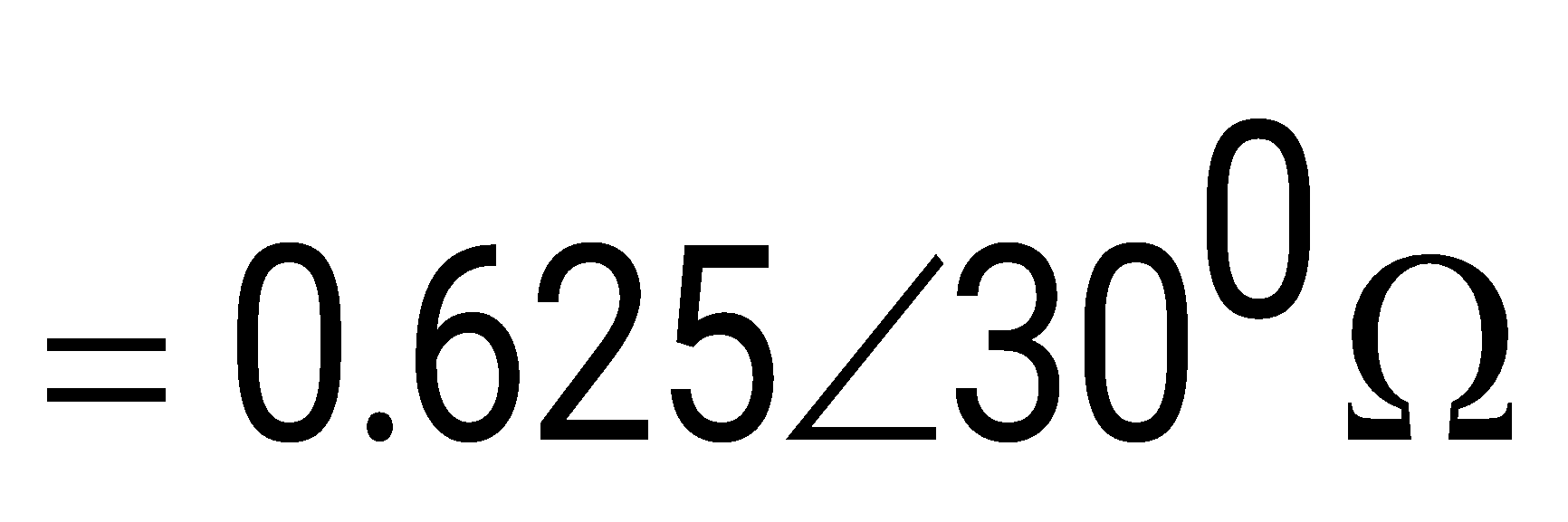

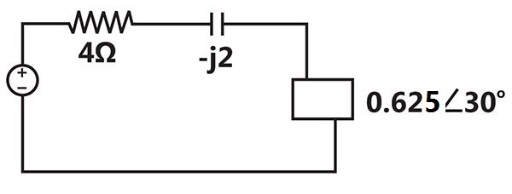

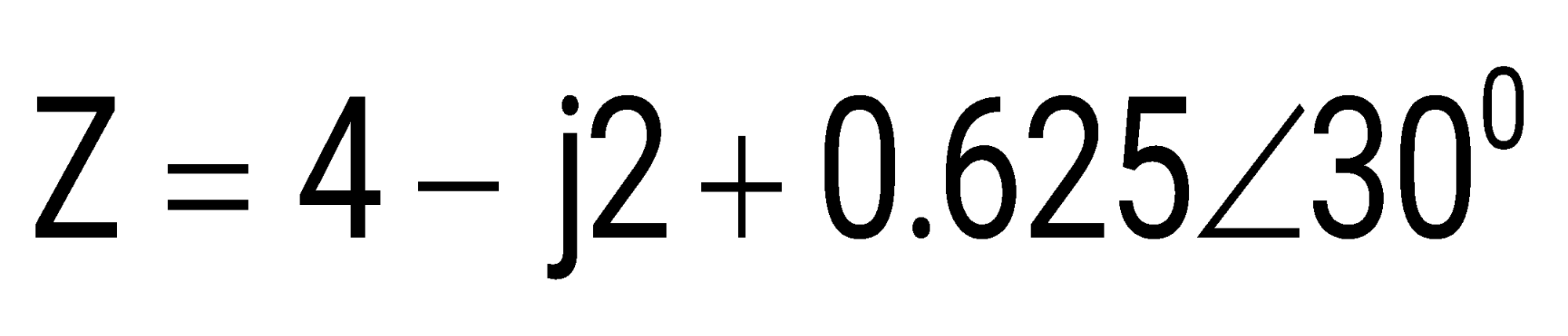

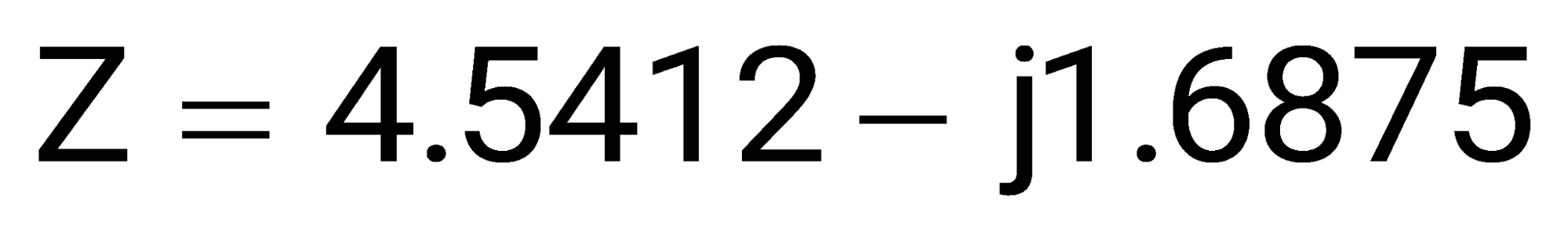

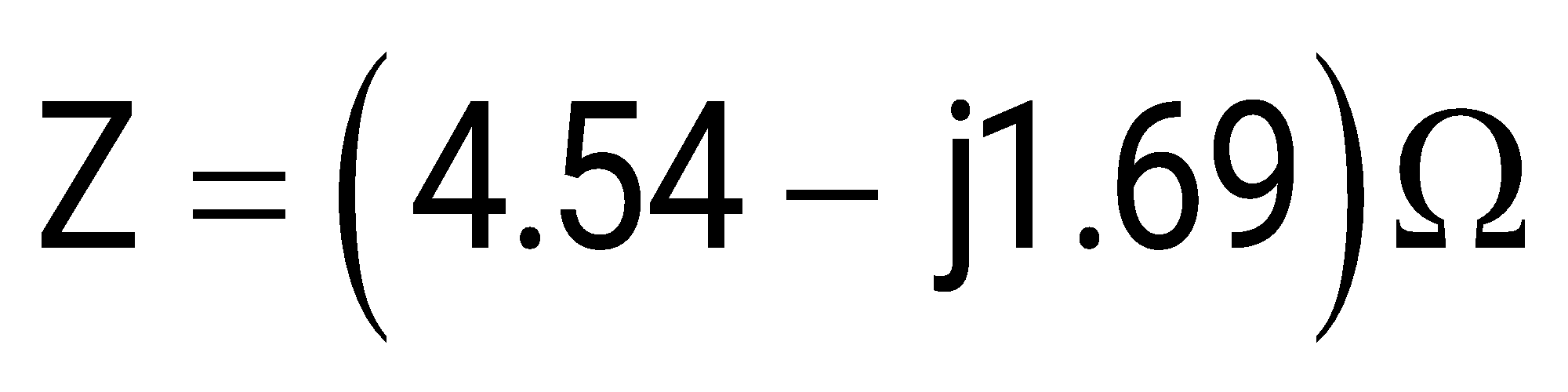

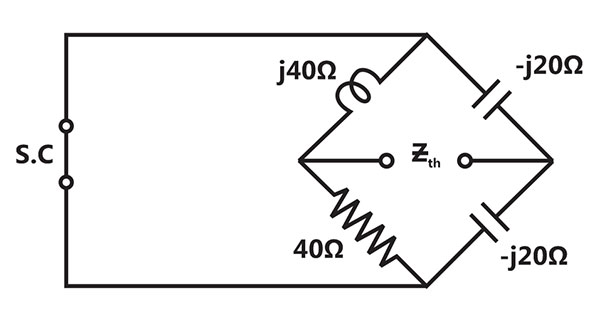

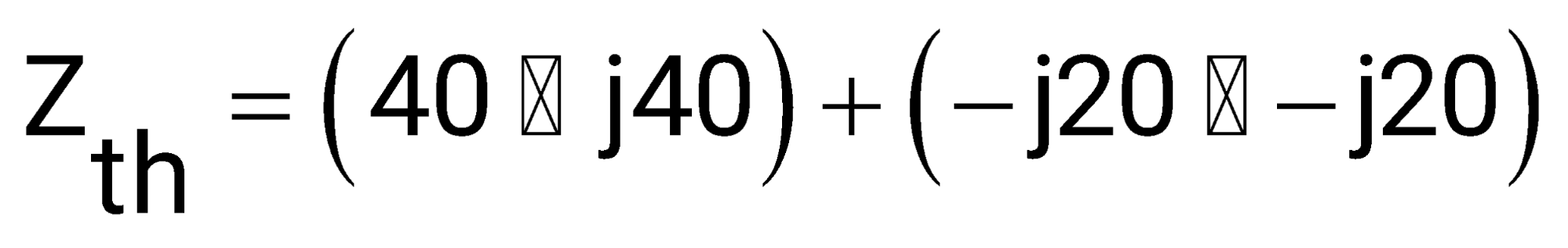

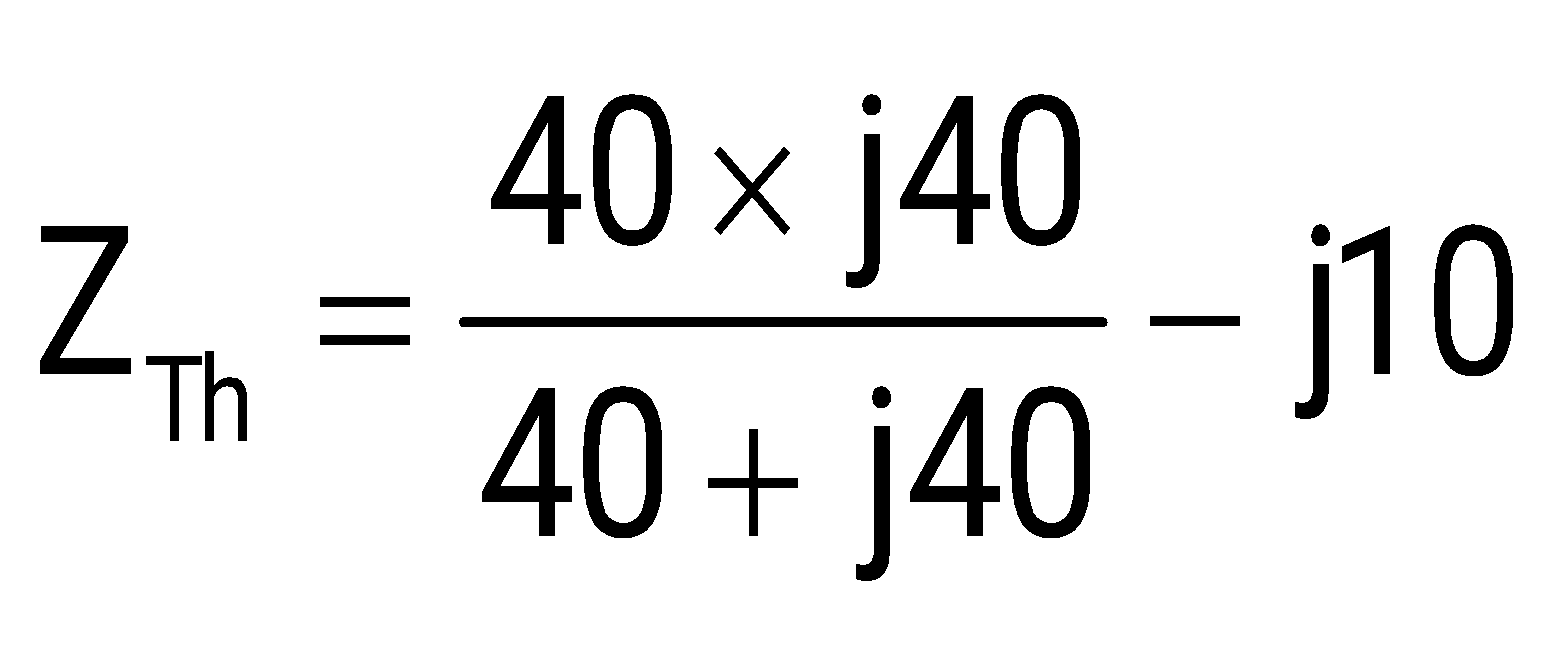

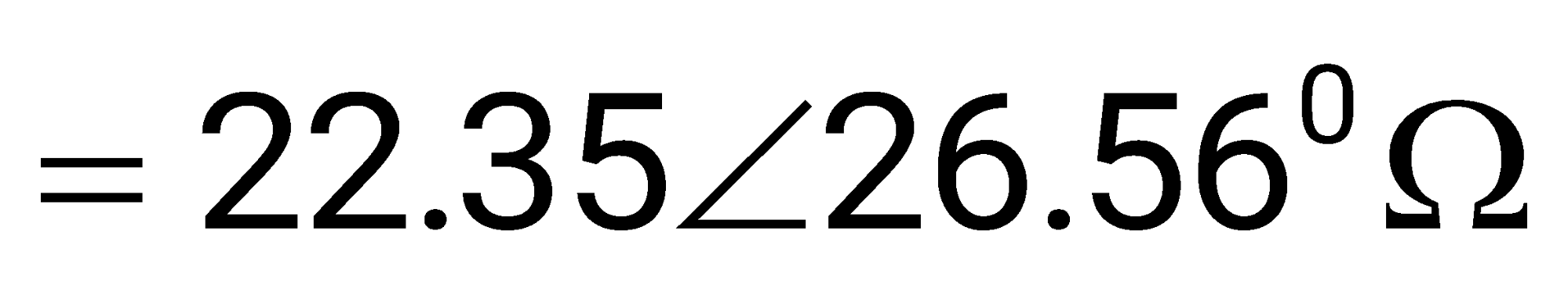

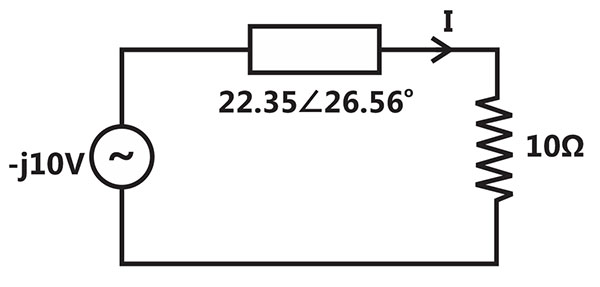

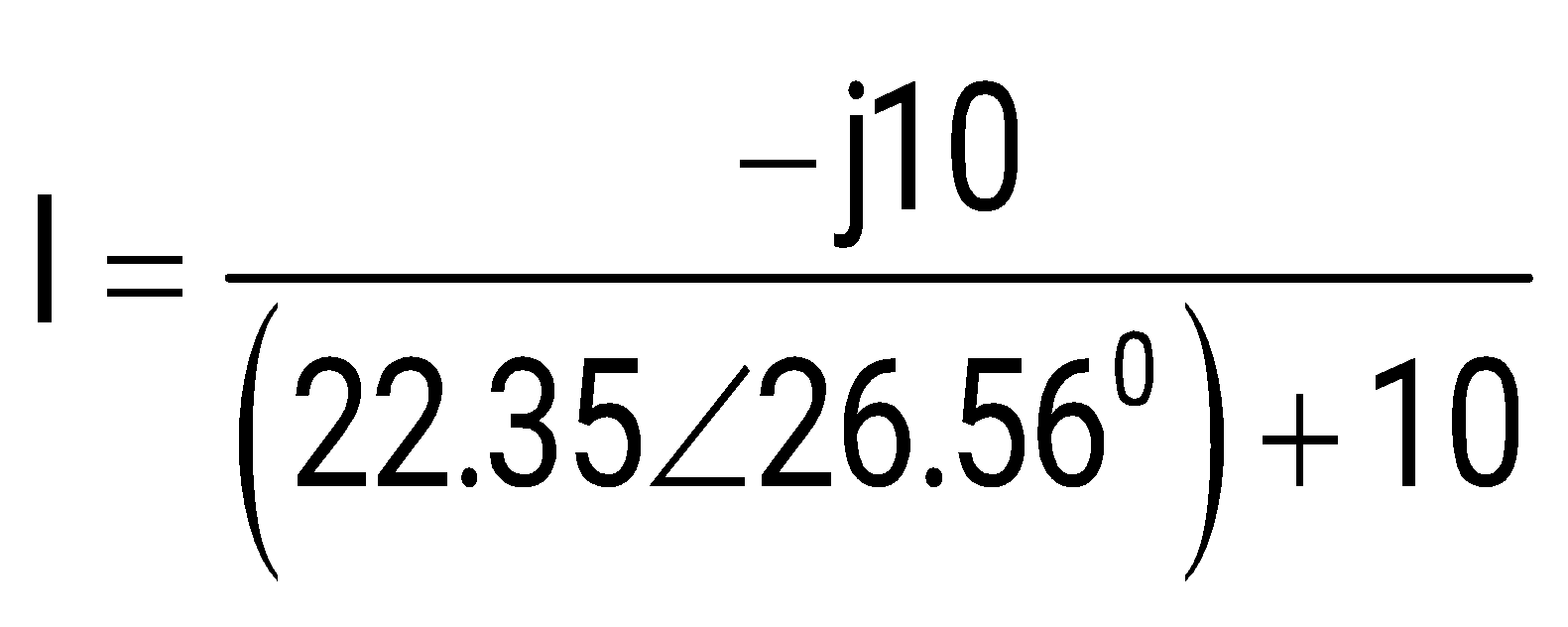

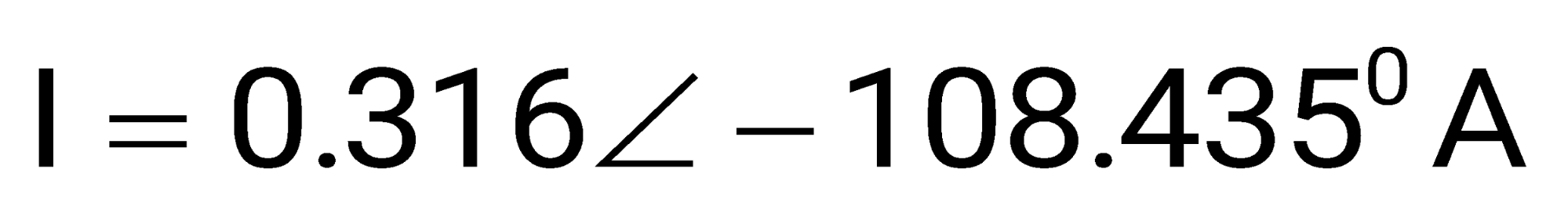

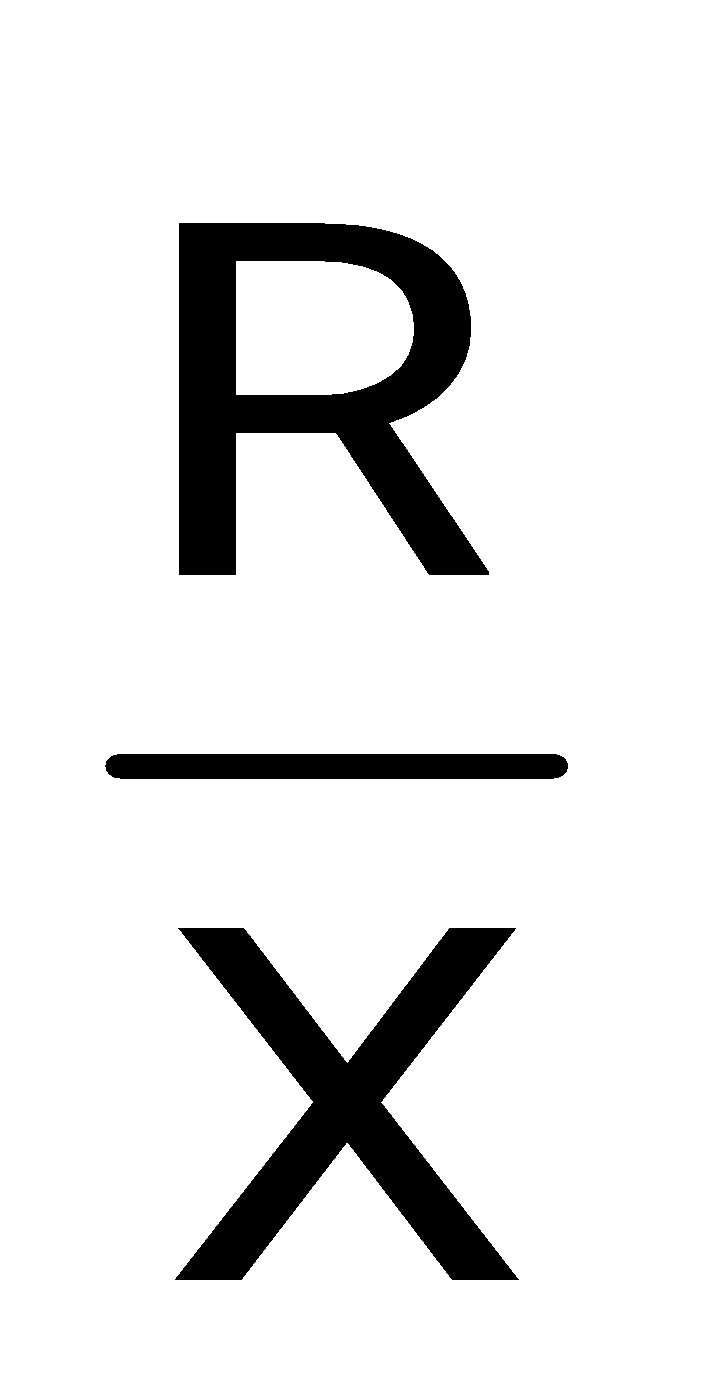

In the given circuit, for maximum power to be delivered to , its value should be …………… Ω. (Round off to 2 decimal places).

For maximum power transfer

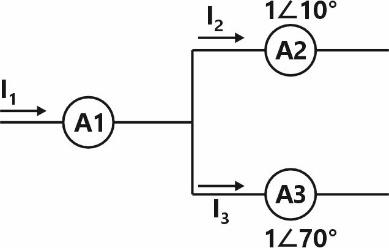

Current through ammeters and in fig. are 1 ∠ 10° and 1 ∠ 70° respectively. The reading of the ammeter A1 (rounded off to 3 decimal places) is _________ A.

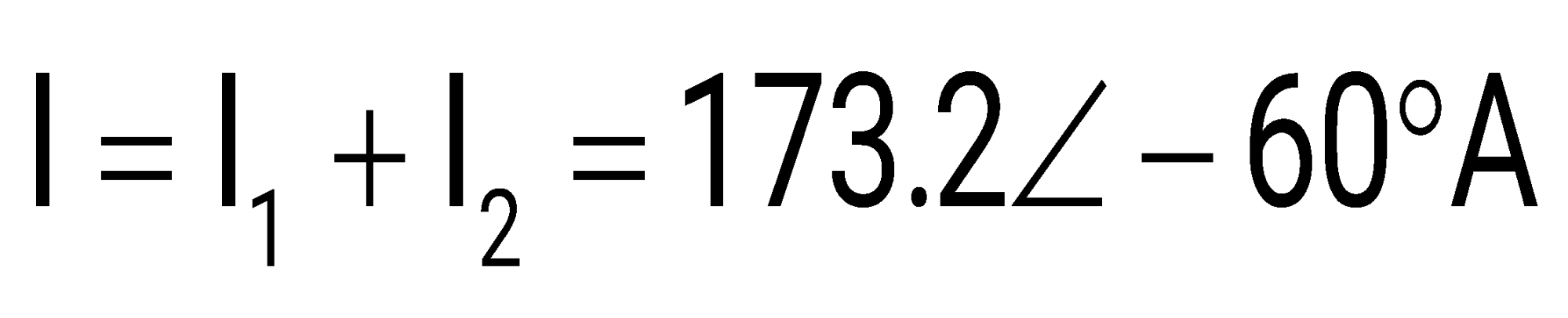

I = 1 ∠ 10° + 1 ∠ 70°

I = 1.732 ∠ 40°

The reading of ammeter is 1.732 A.

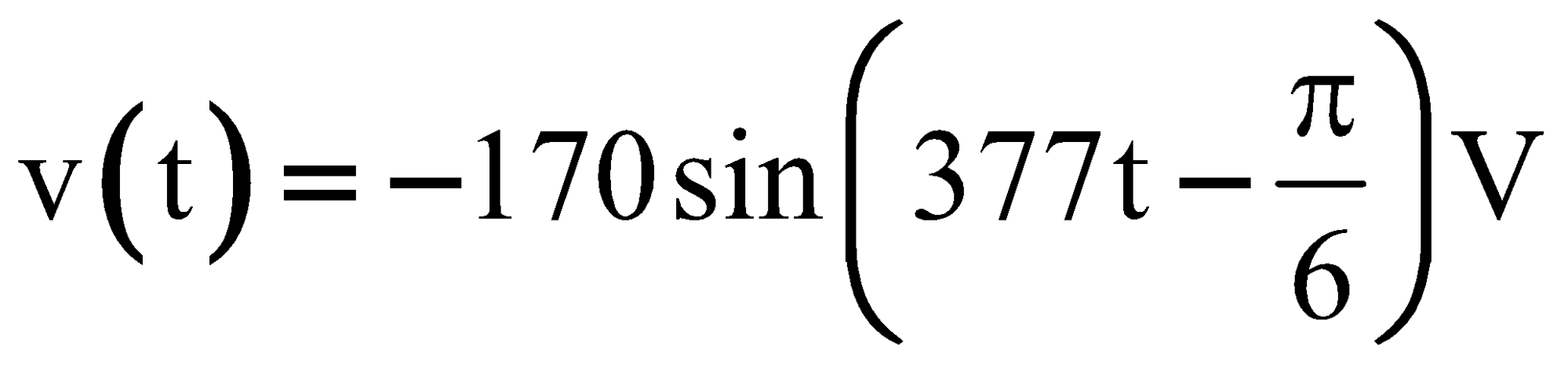

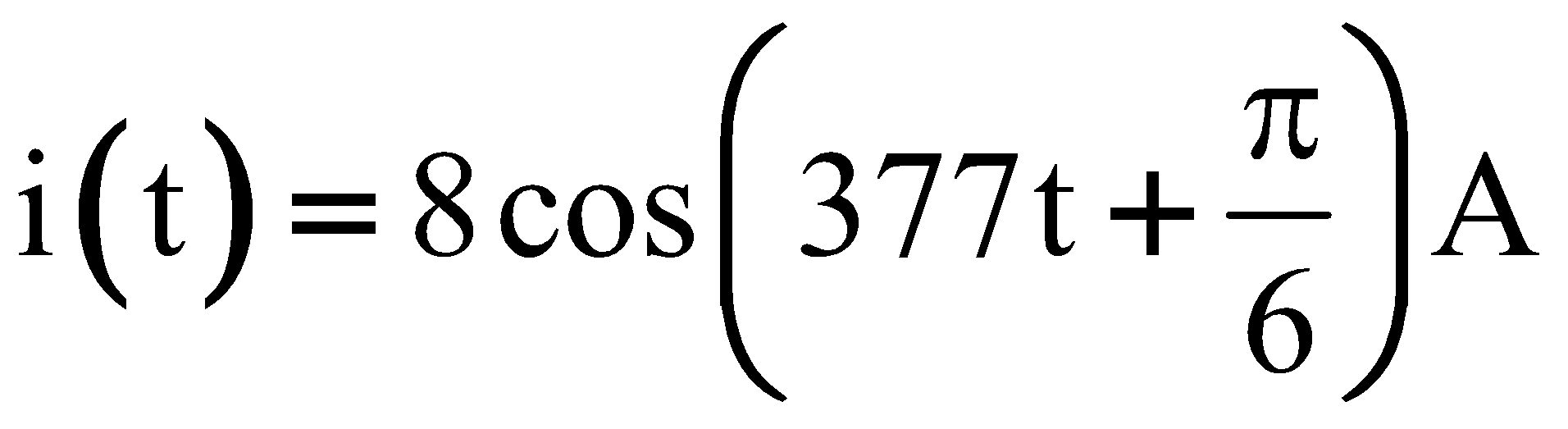

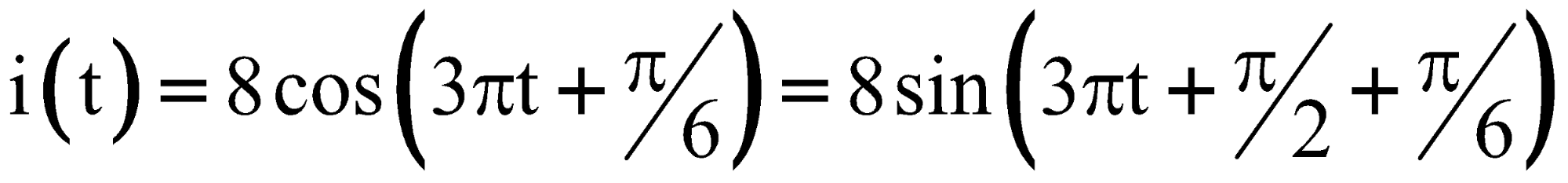

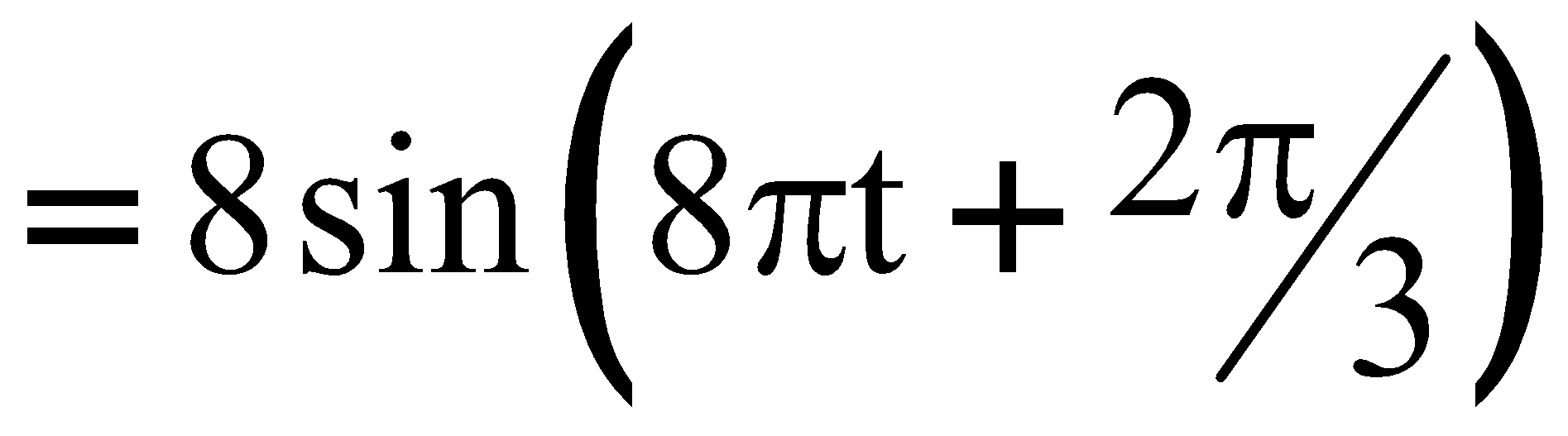

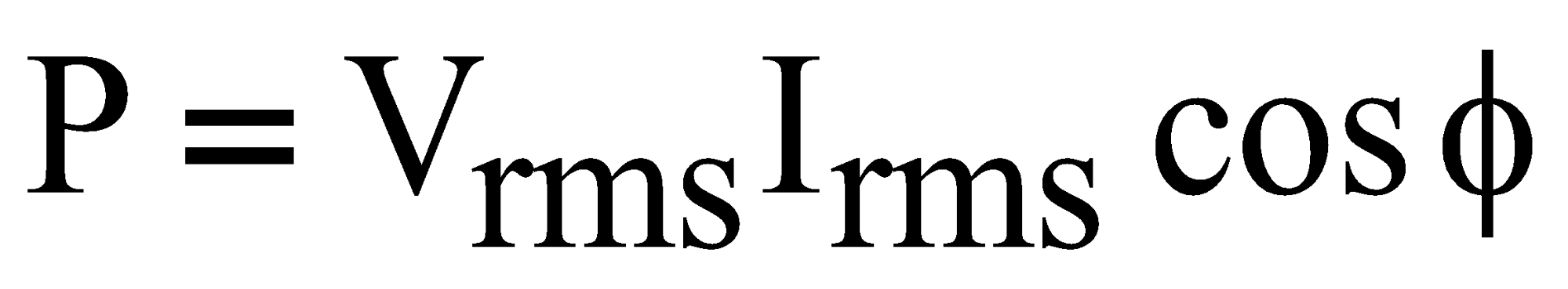

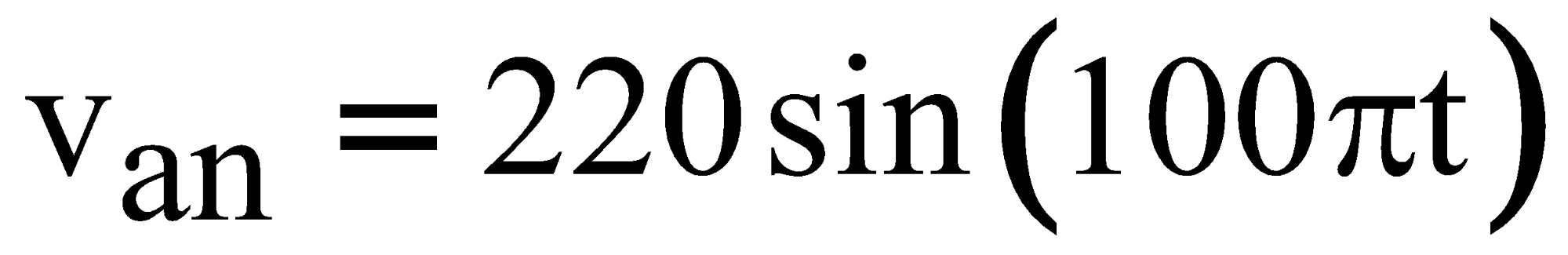

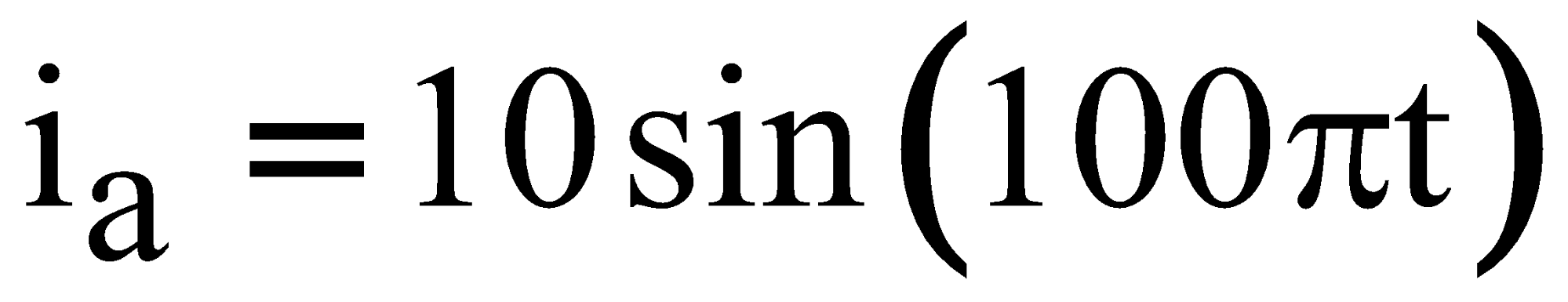

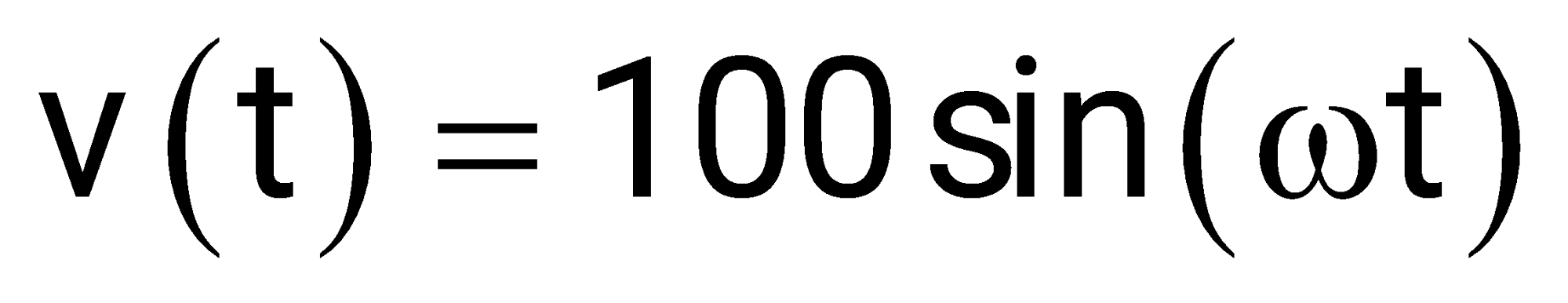

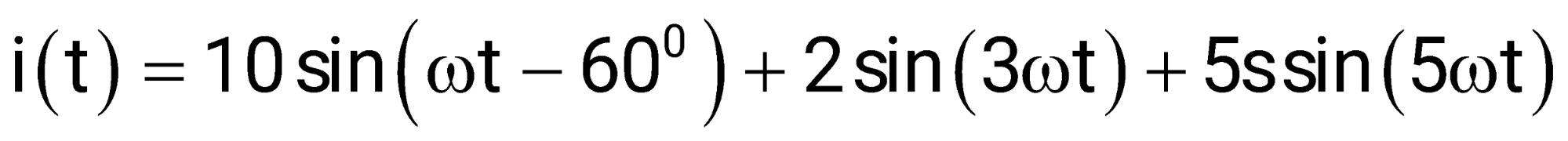

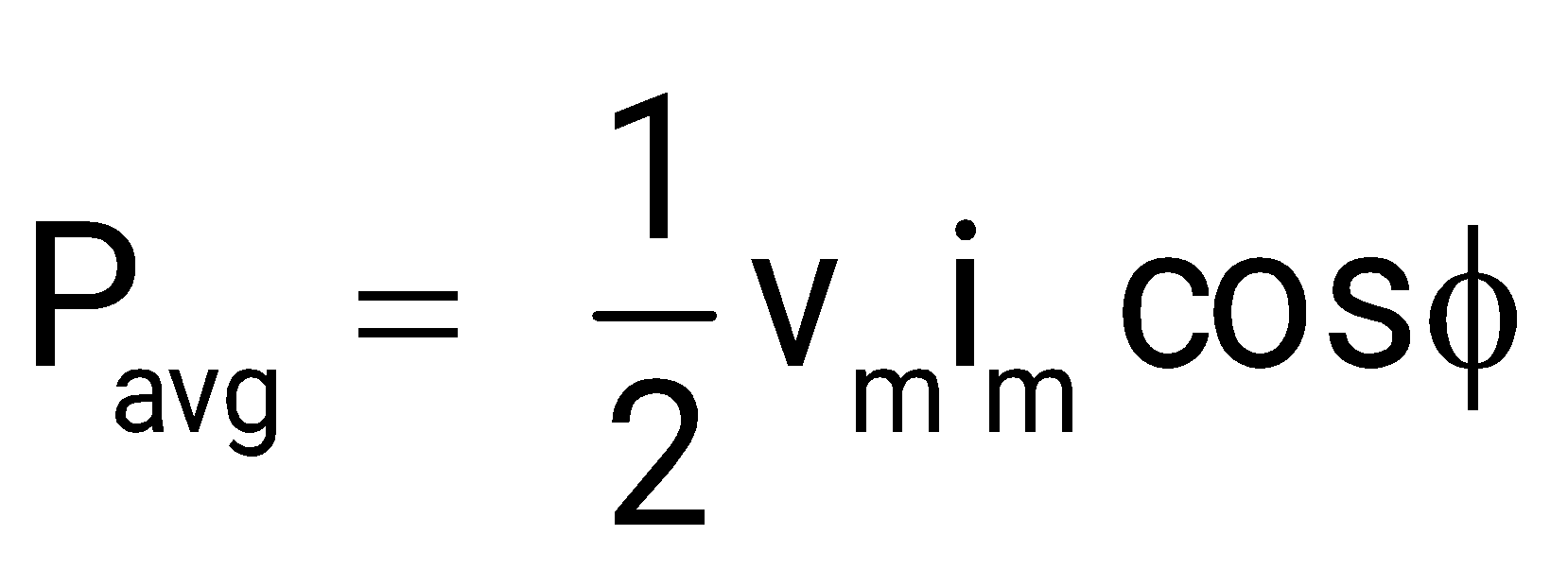

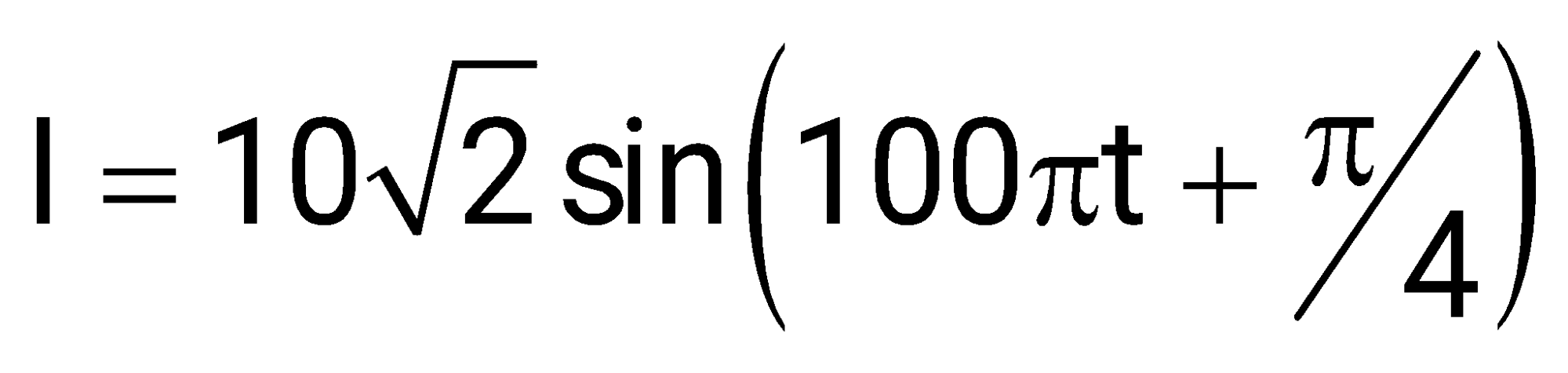

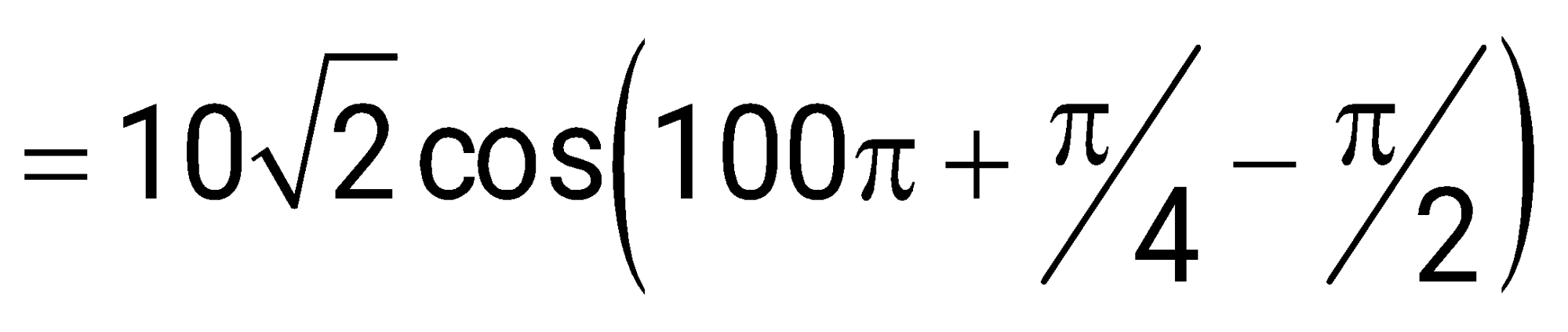

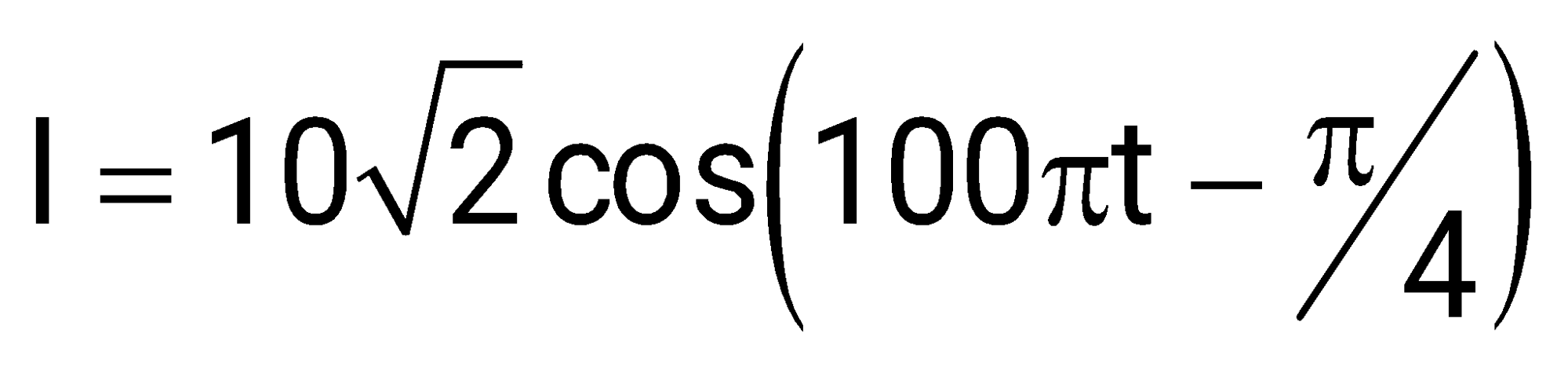

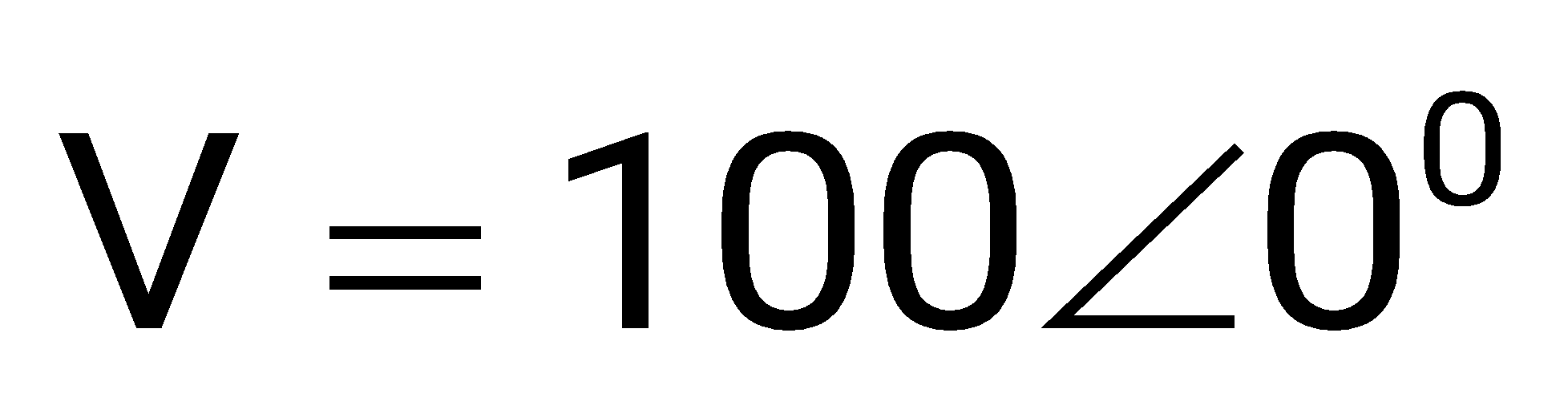

The voltage across and the current through a load are expressed as follows

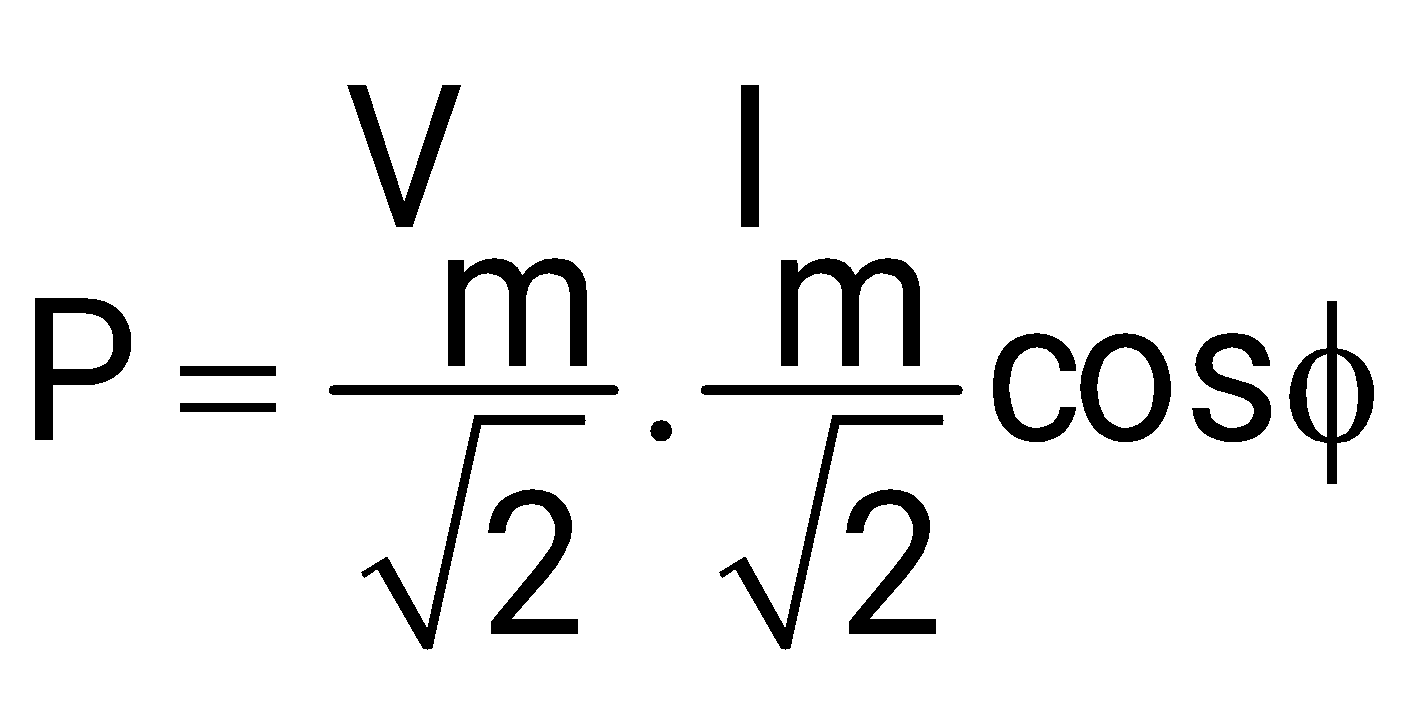

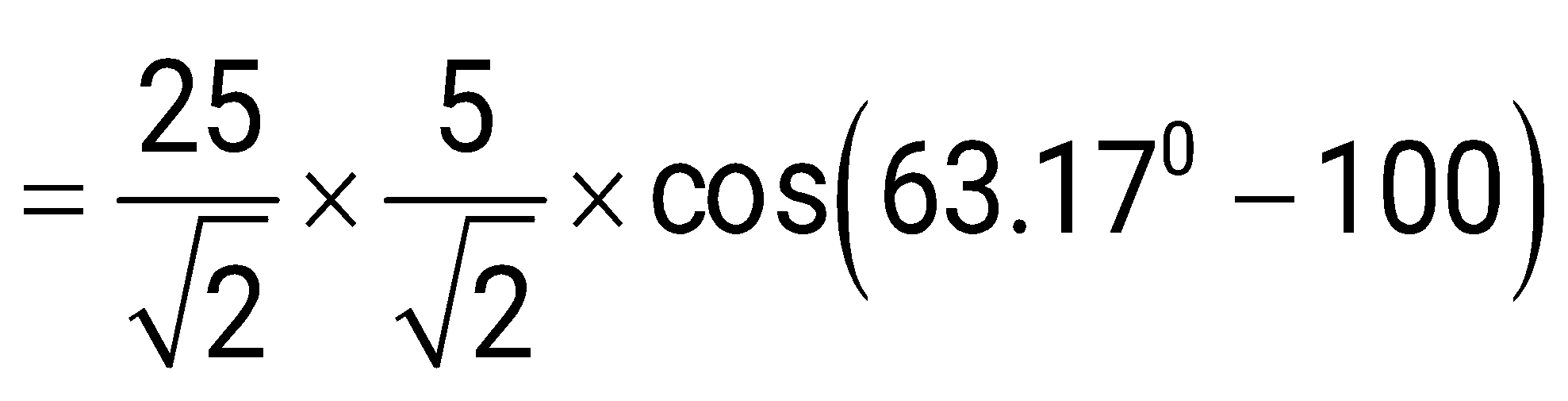

The average power in watts (round off to one decimal place) consumed by the load is _______.

For finding power, constant current to sin

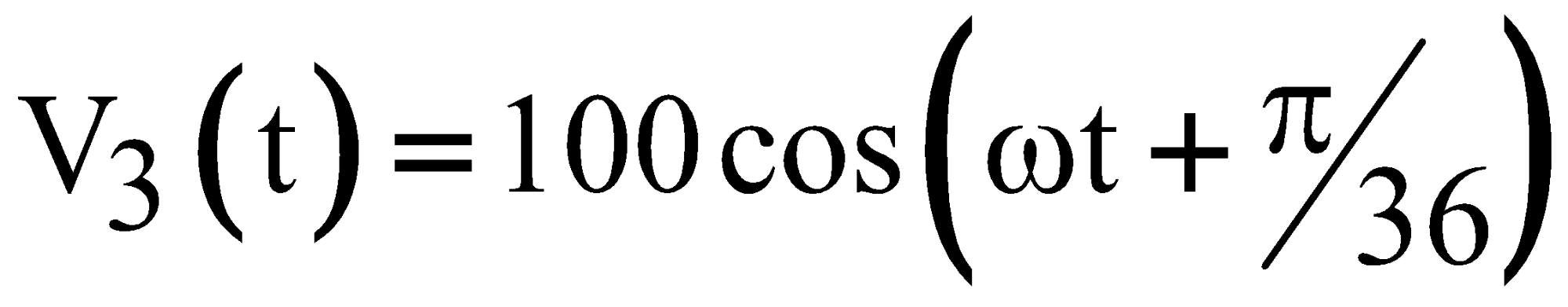

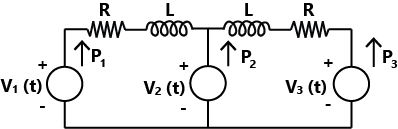

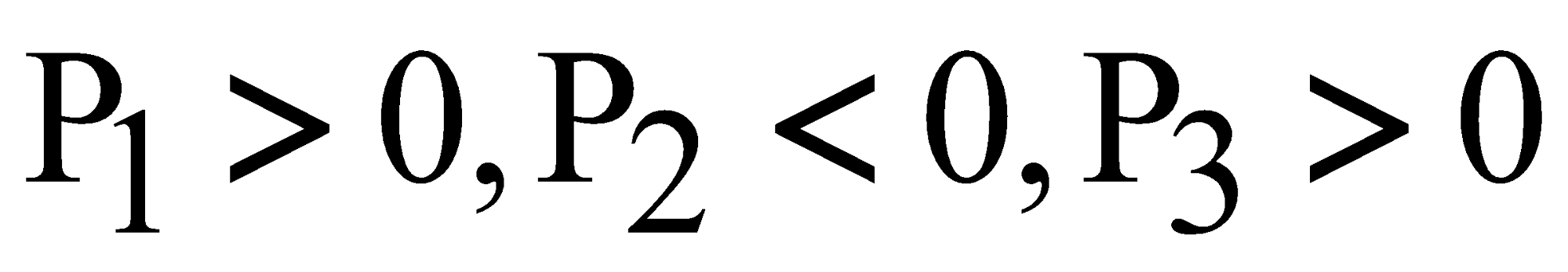

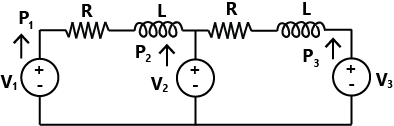

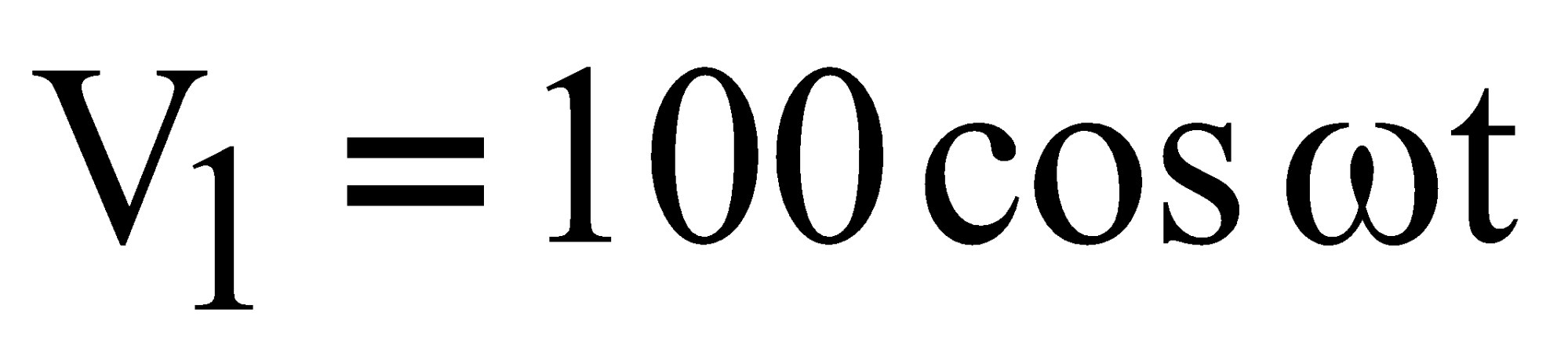

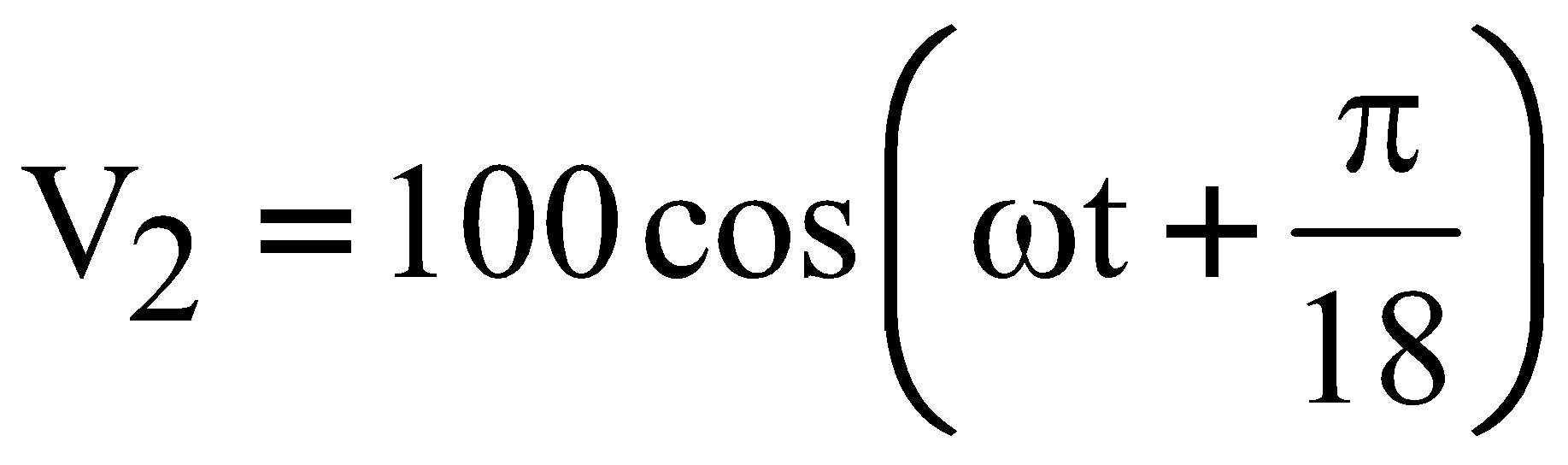

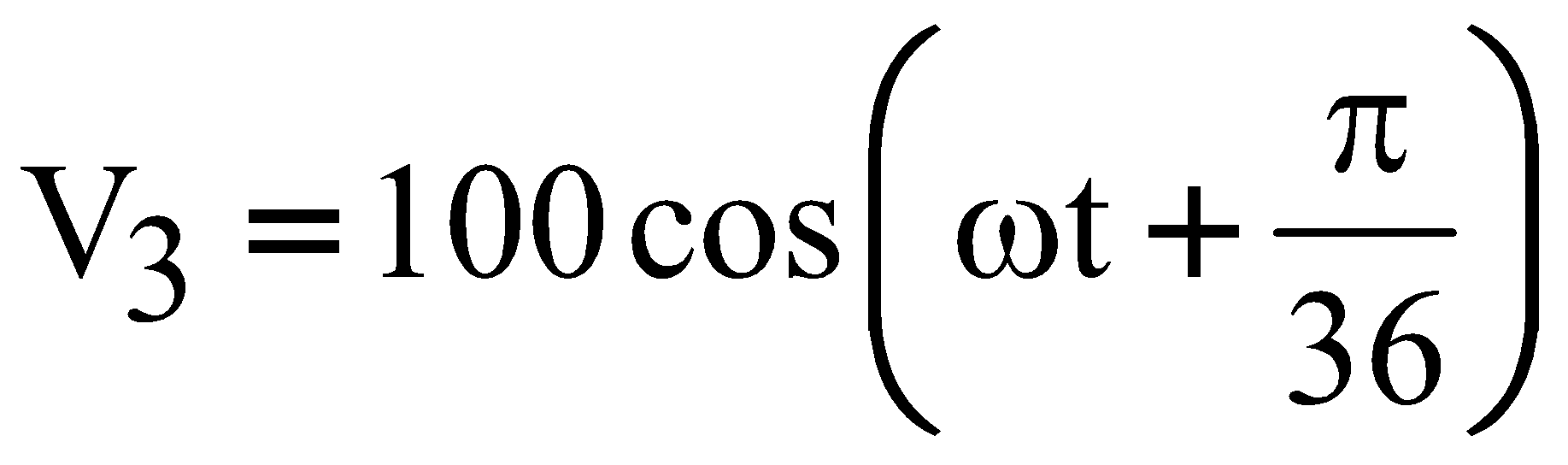

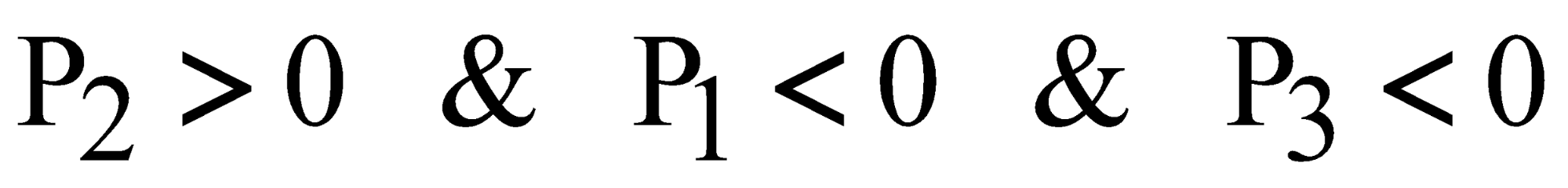

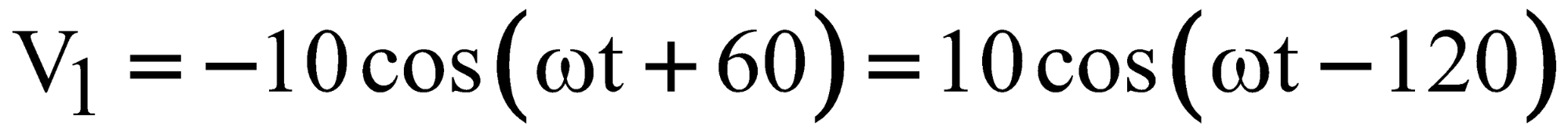

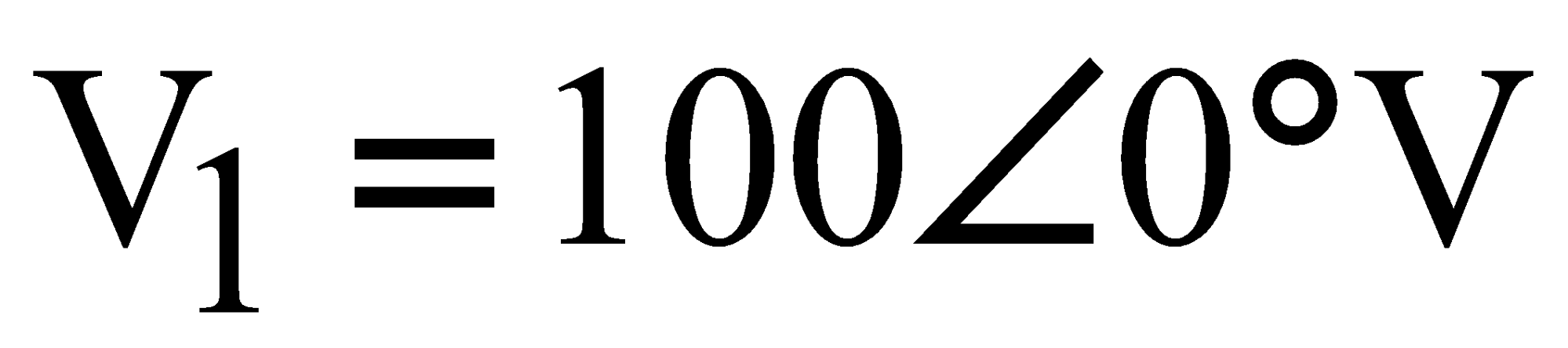

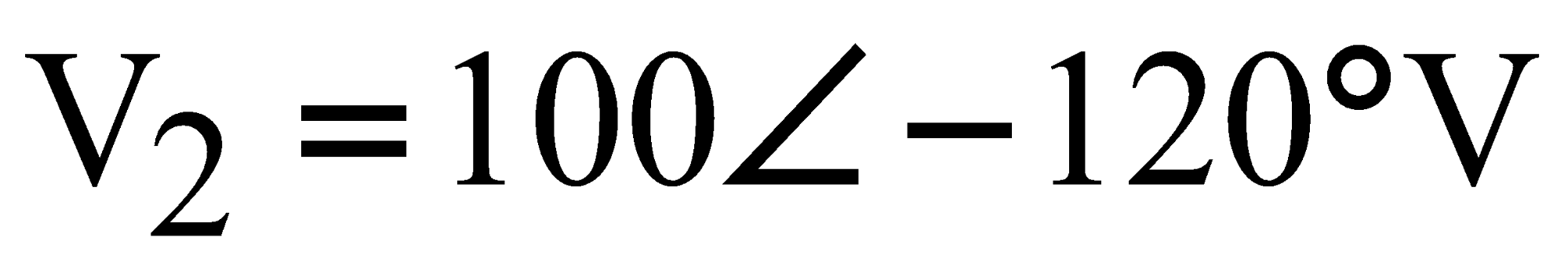

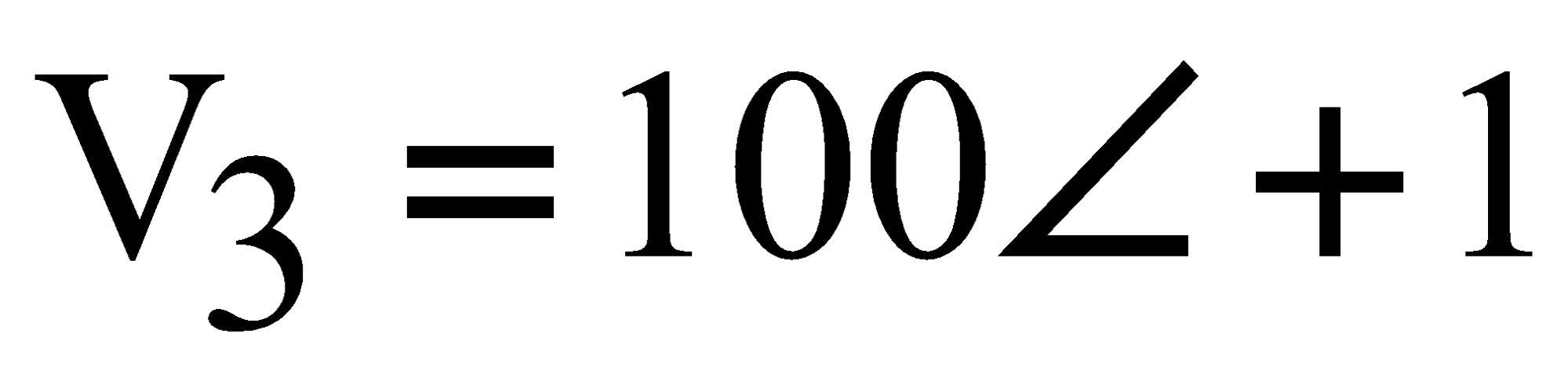

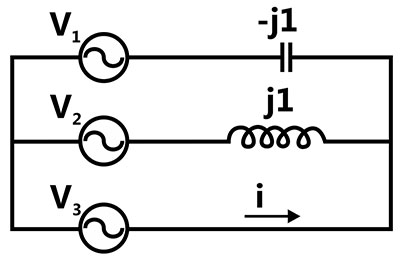

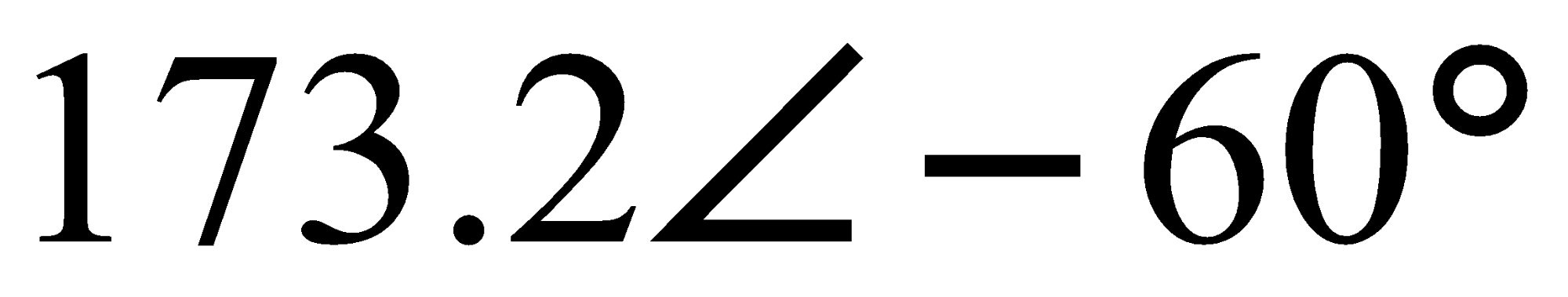

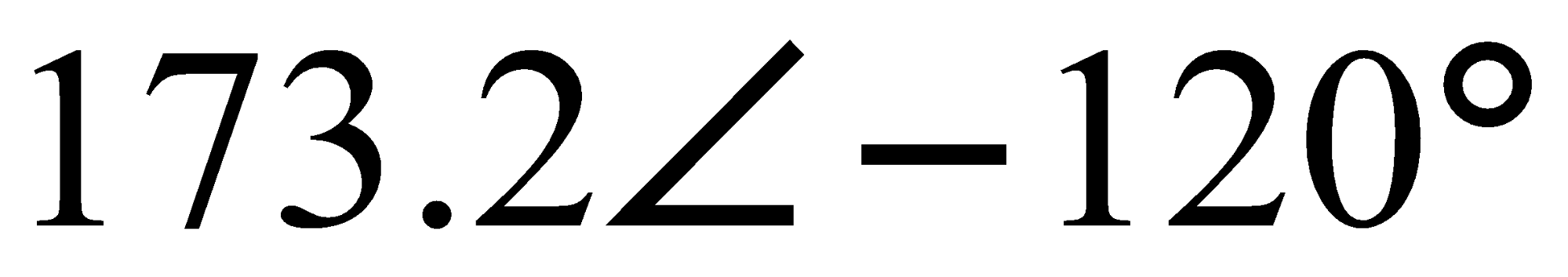

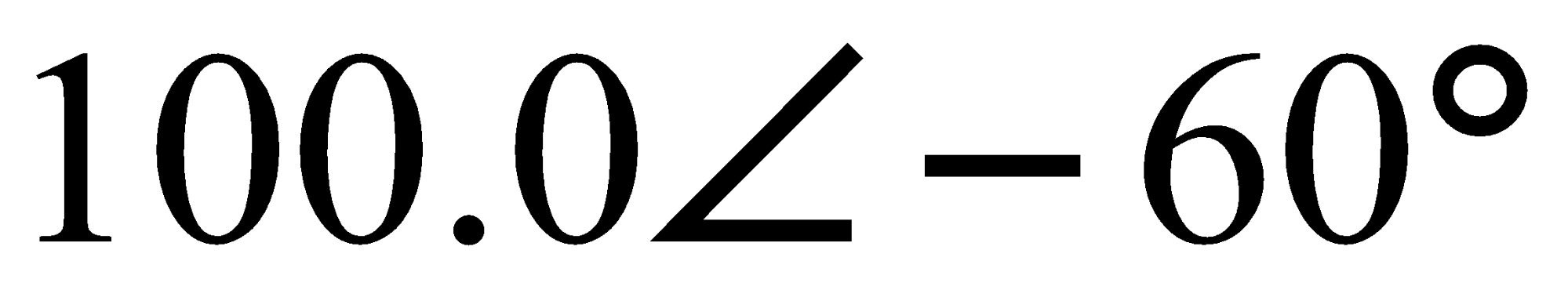

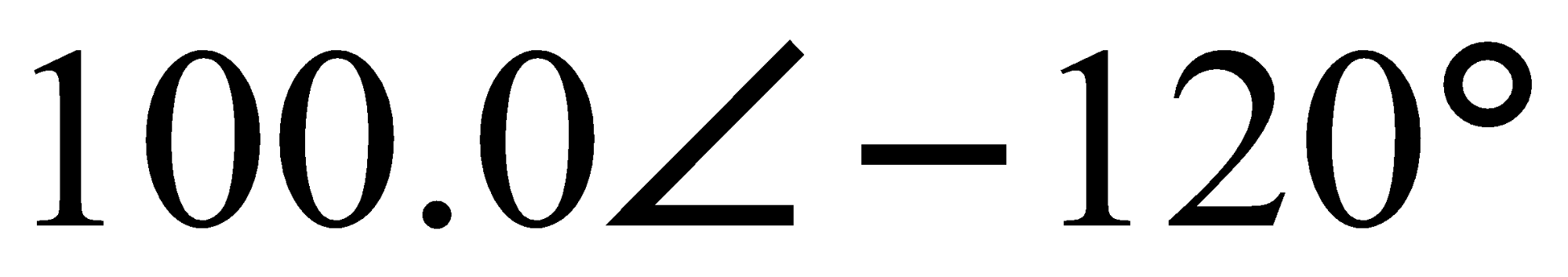

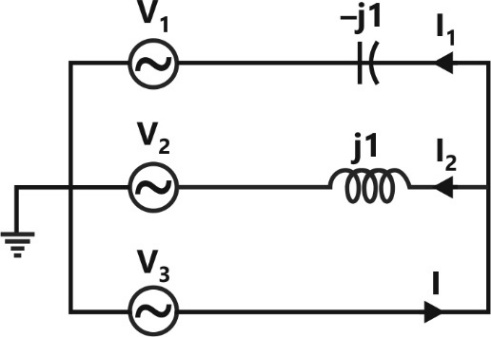

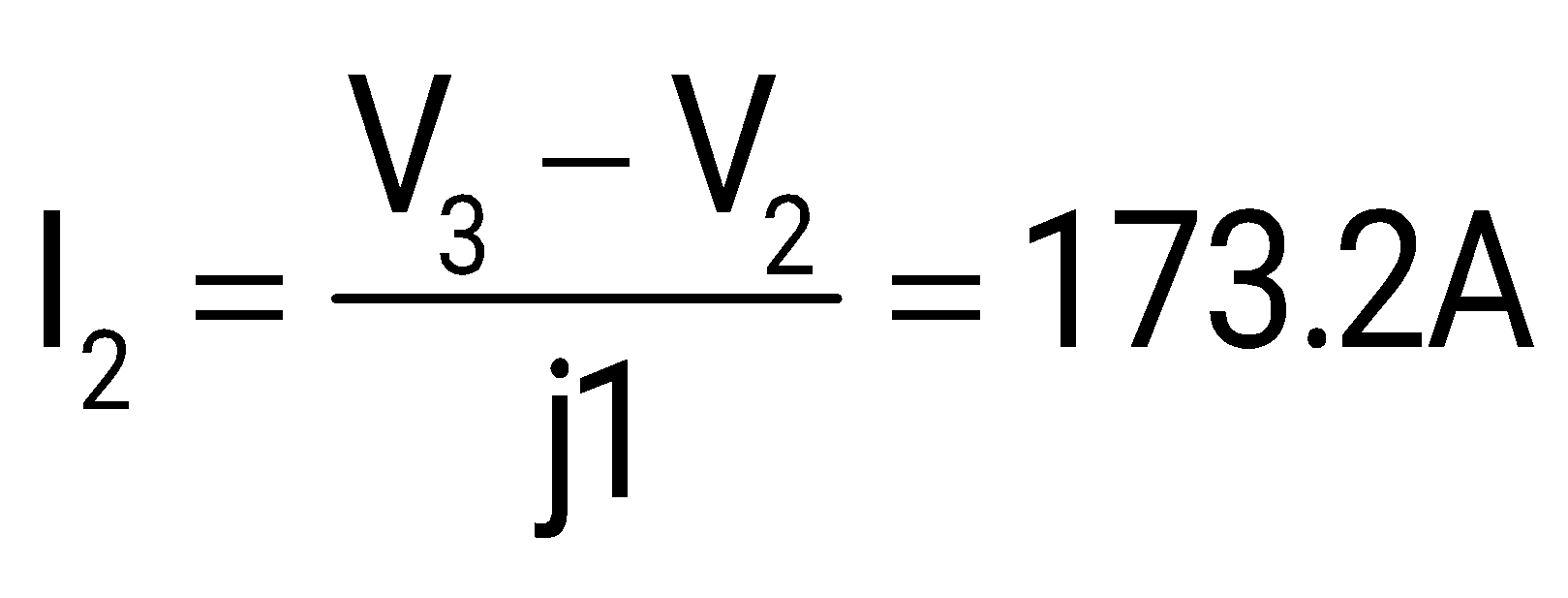

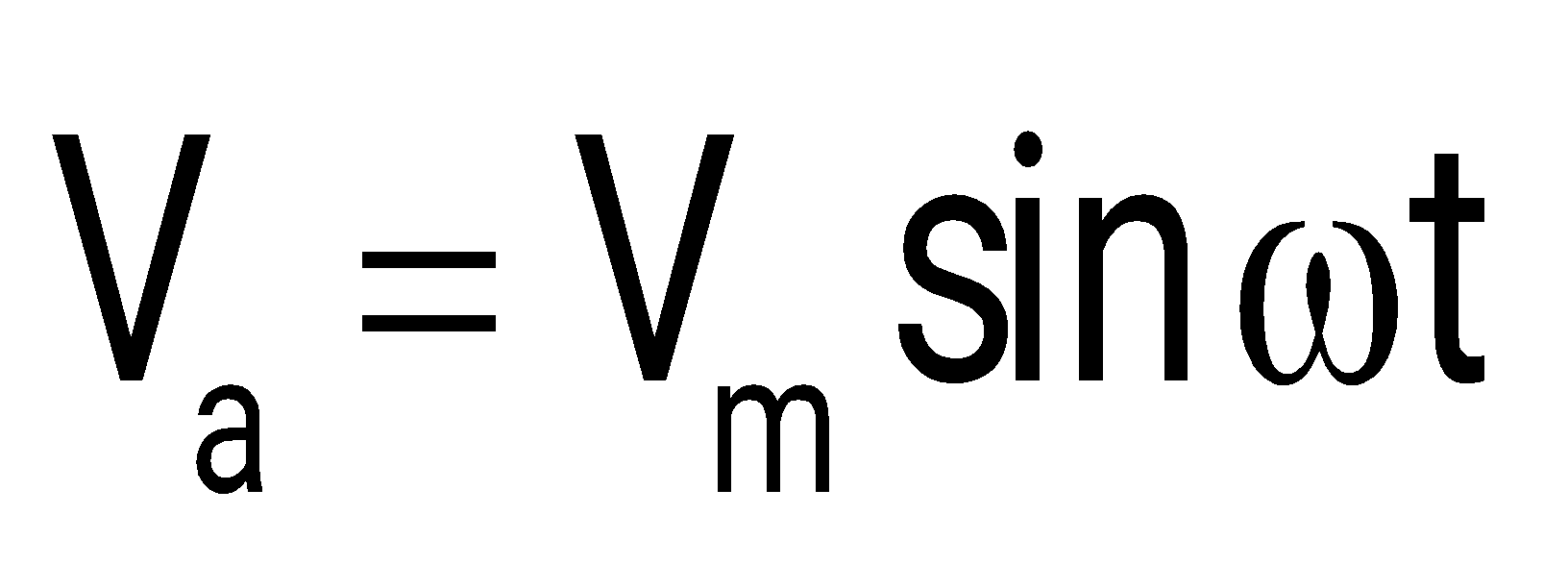

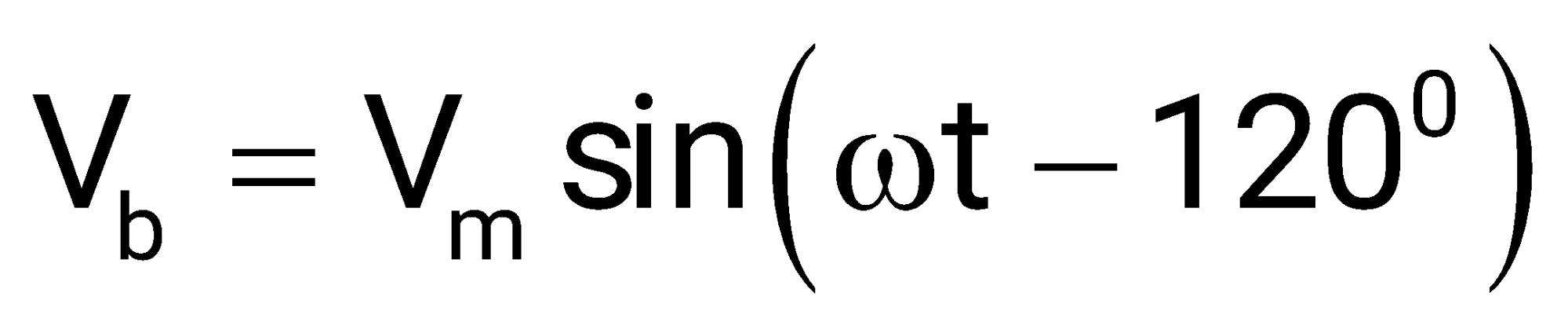

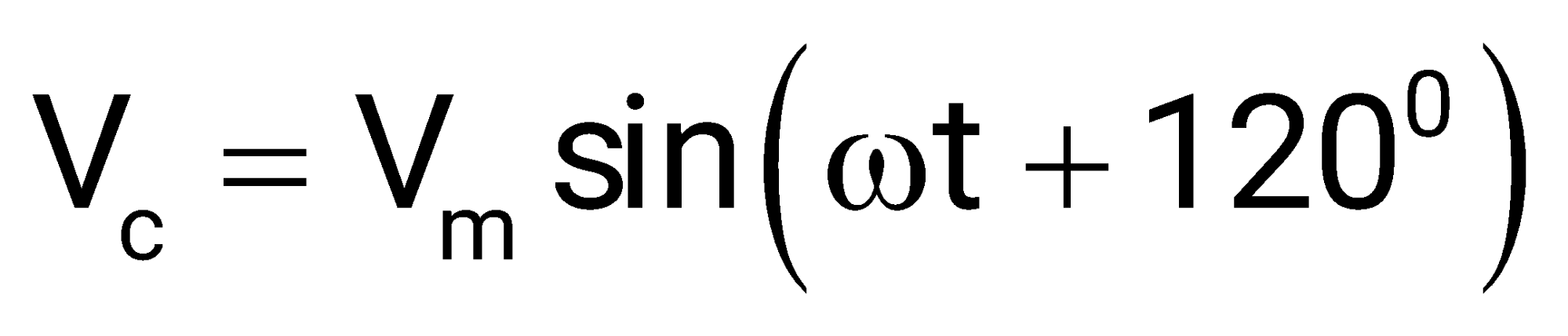

In the figure, the voltages are , and

. The circuit is in sinusoidal steady state, and, and are the average power outputs. Which one of the following statements is true?

In this problem leads both & hence current will flow from towards

Hence,

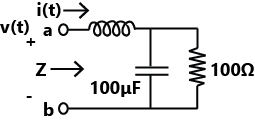

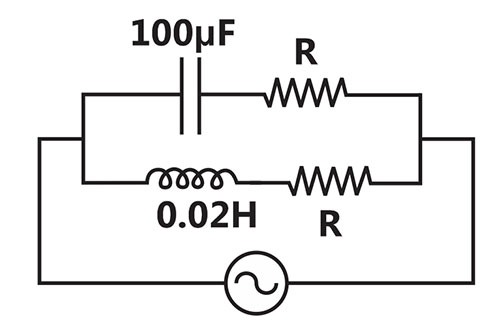

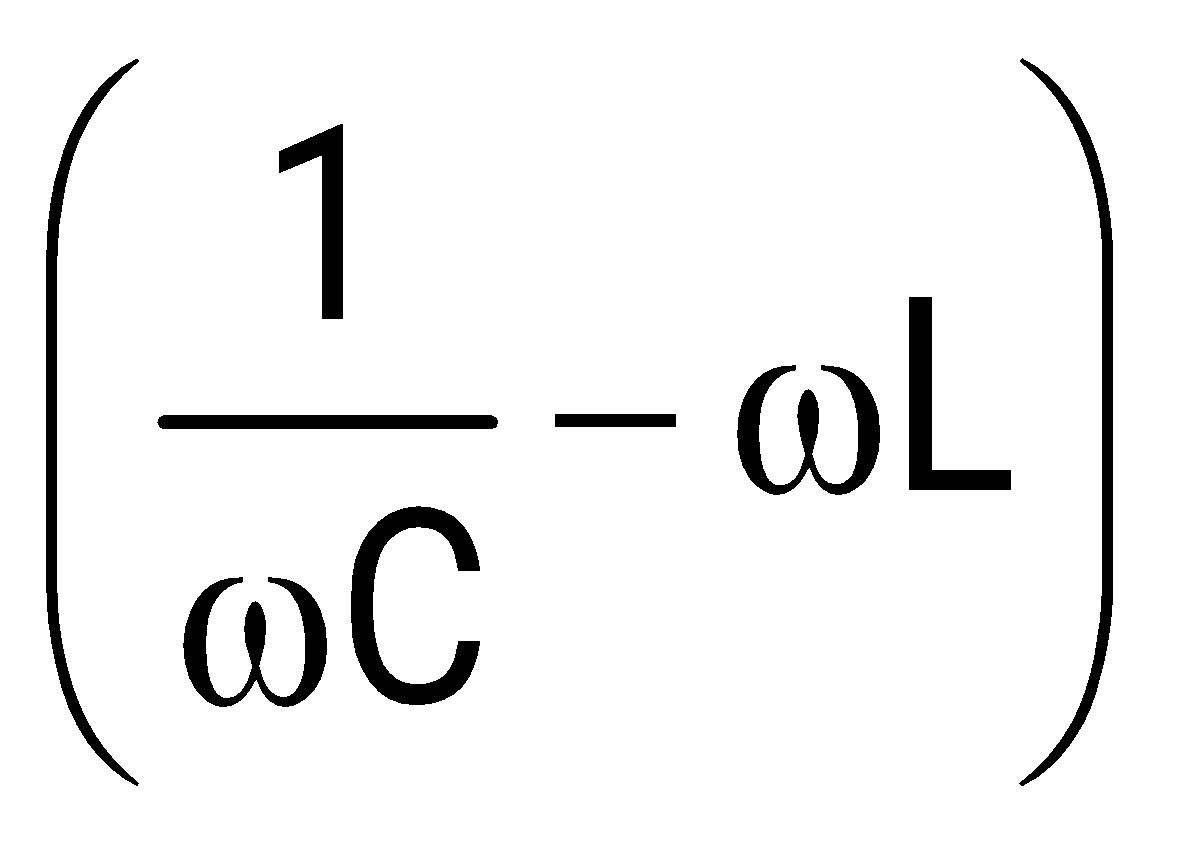

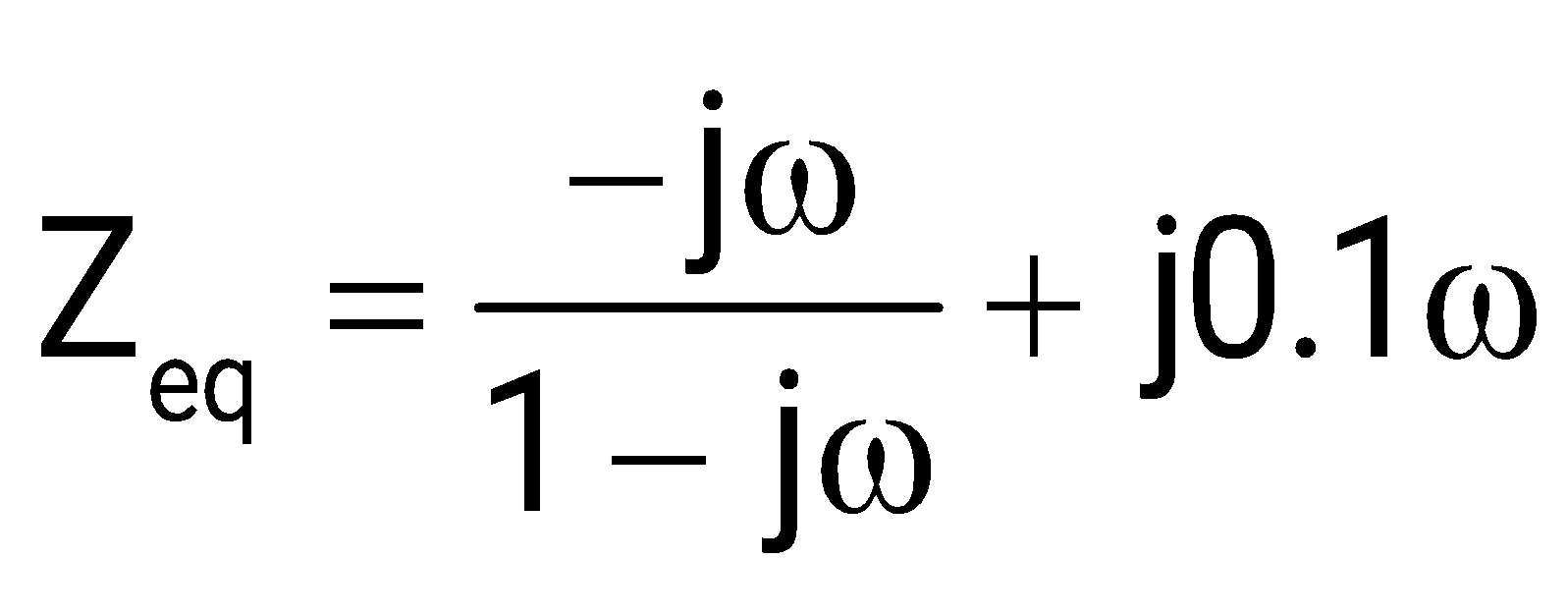

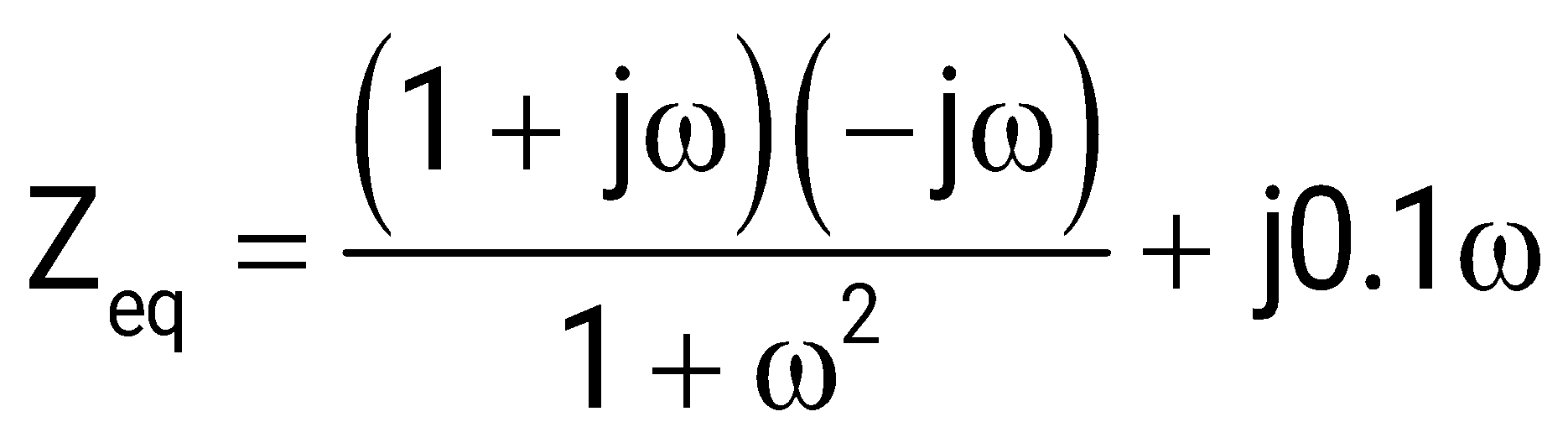

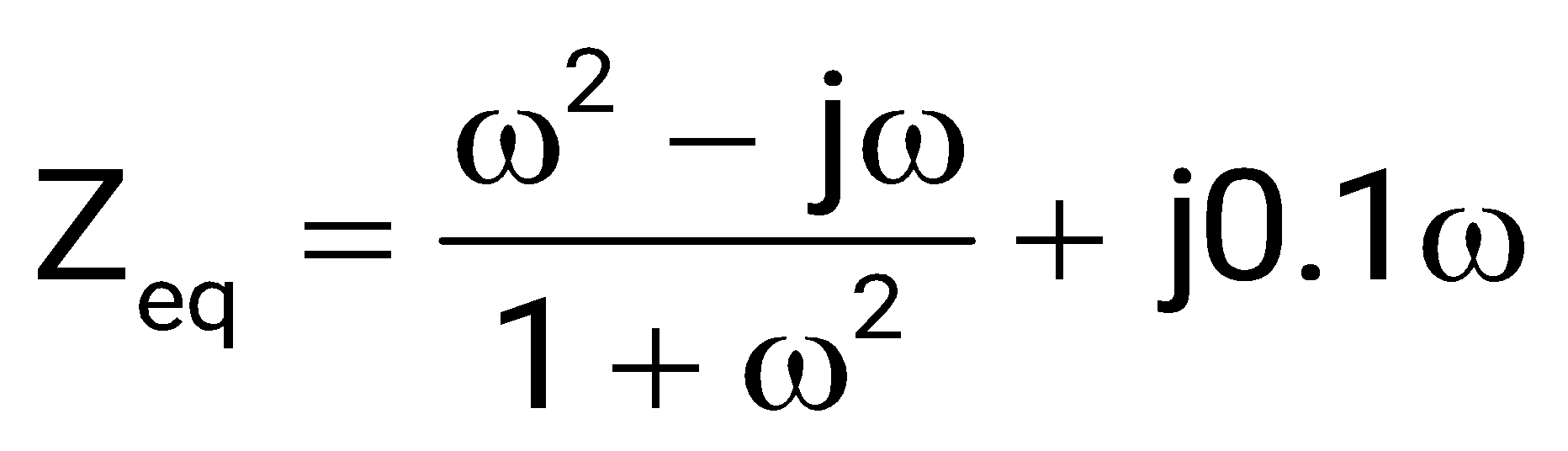

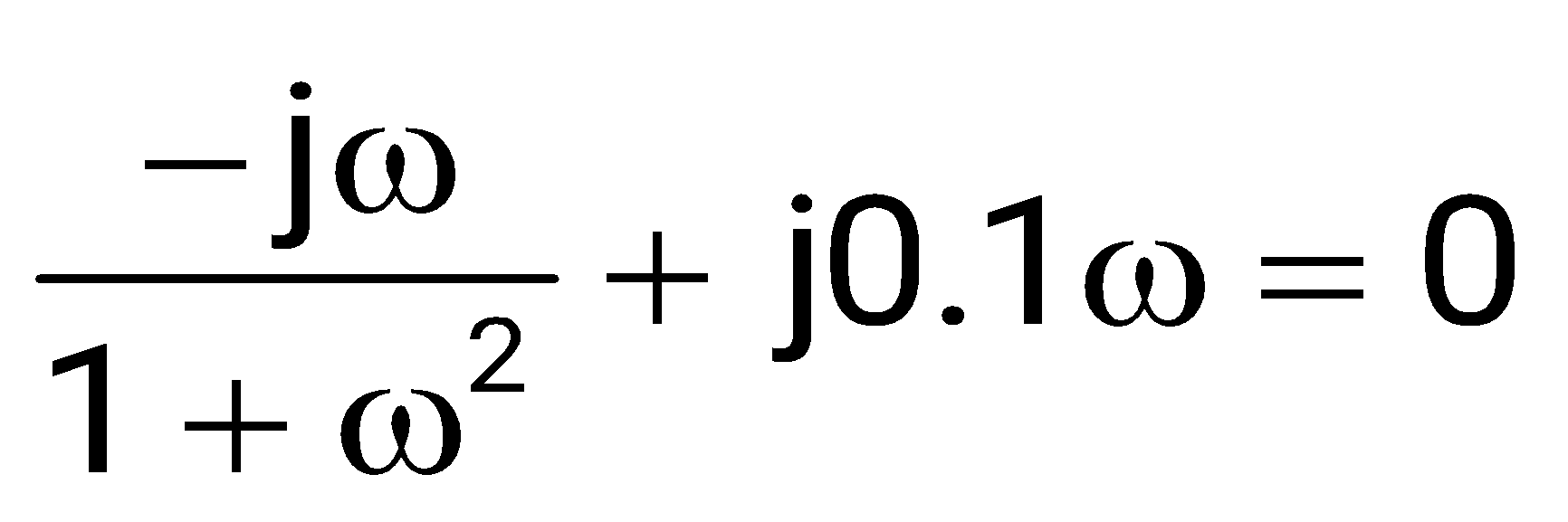

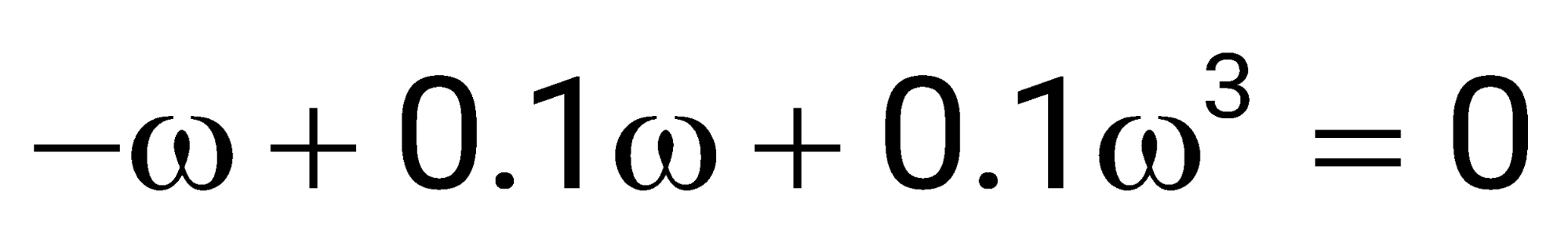

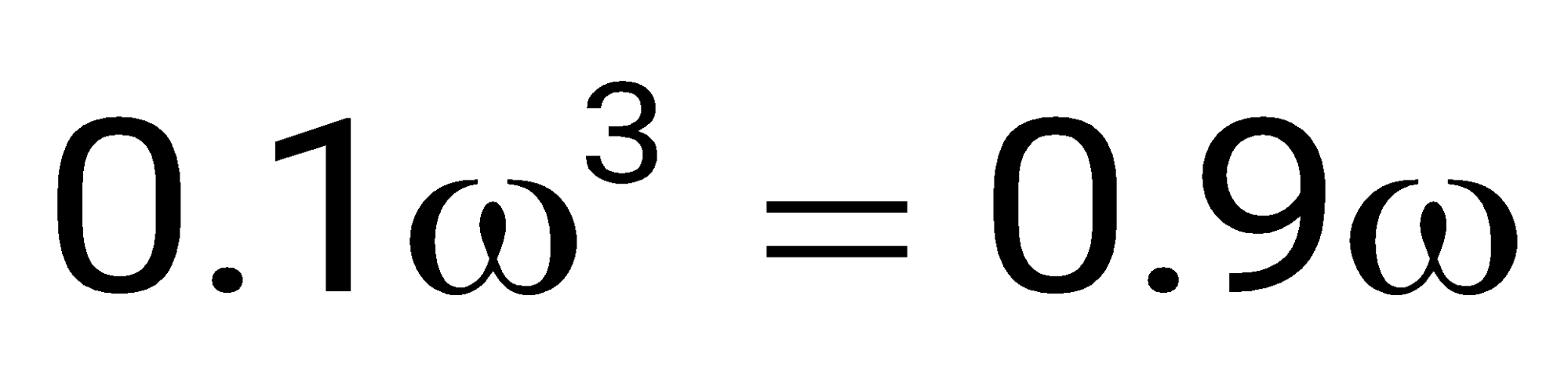

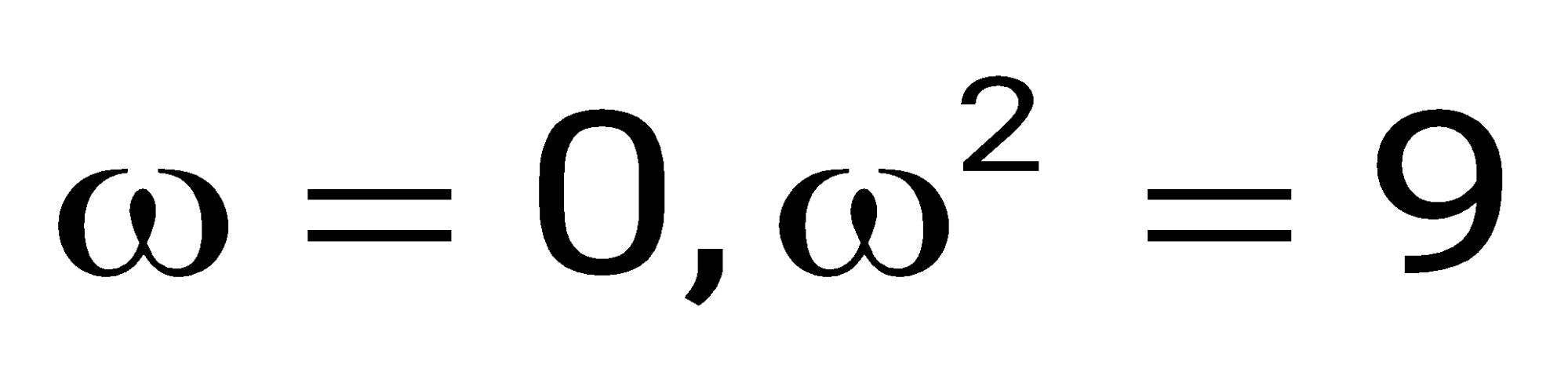

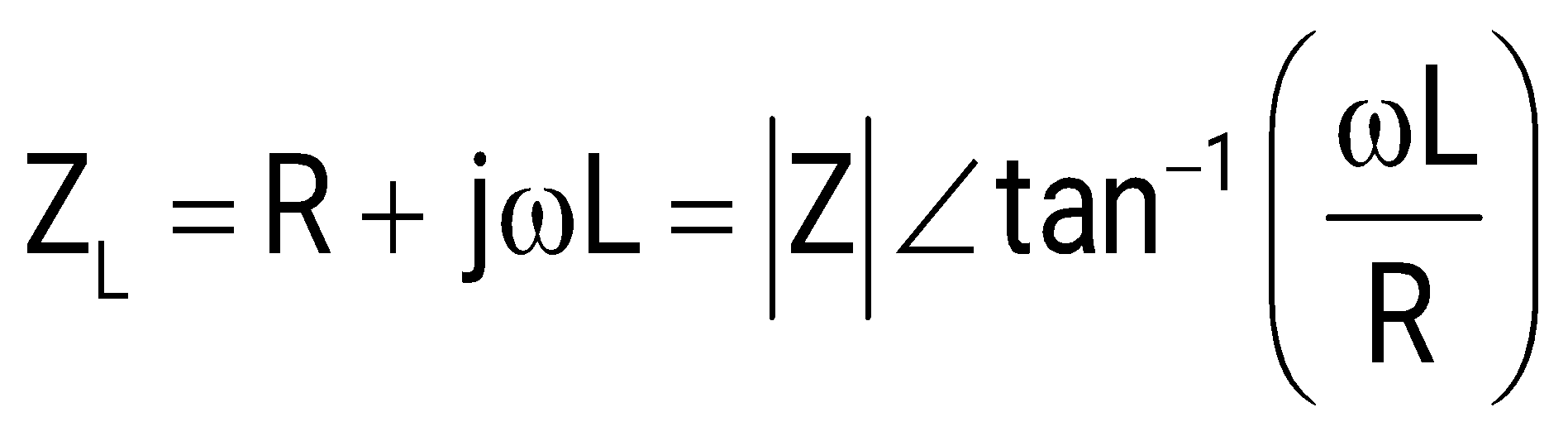

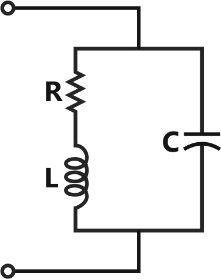

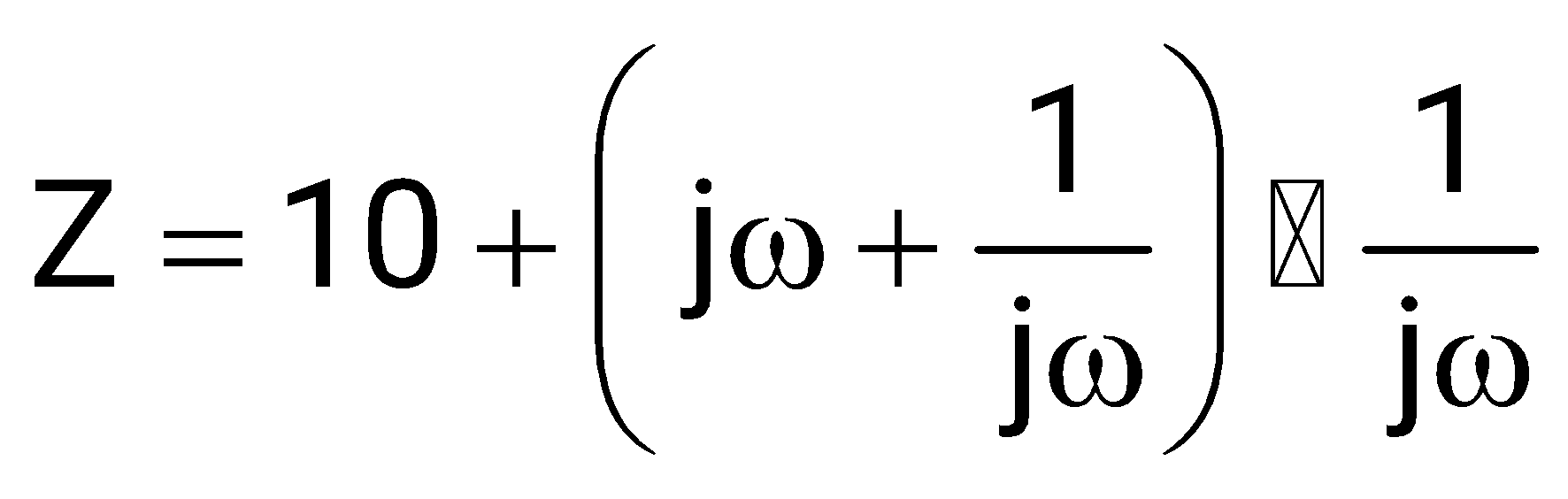

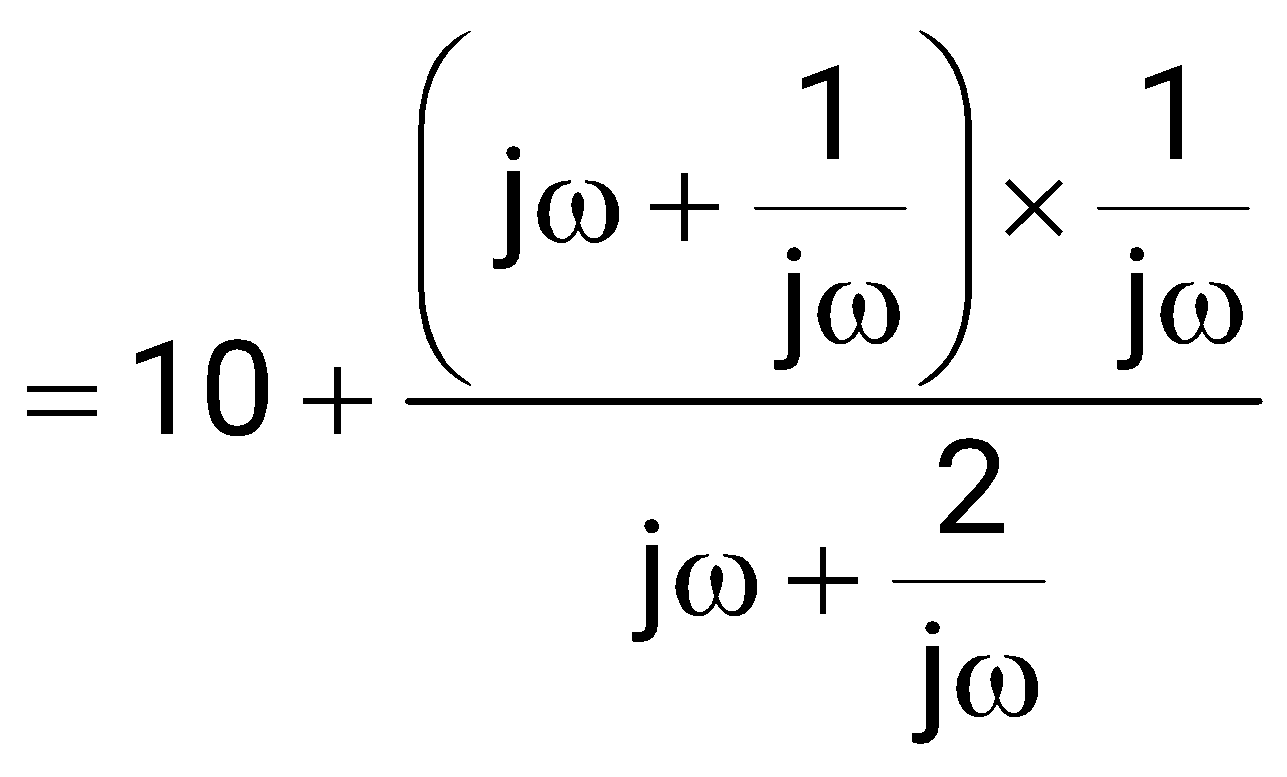

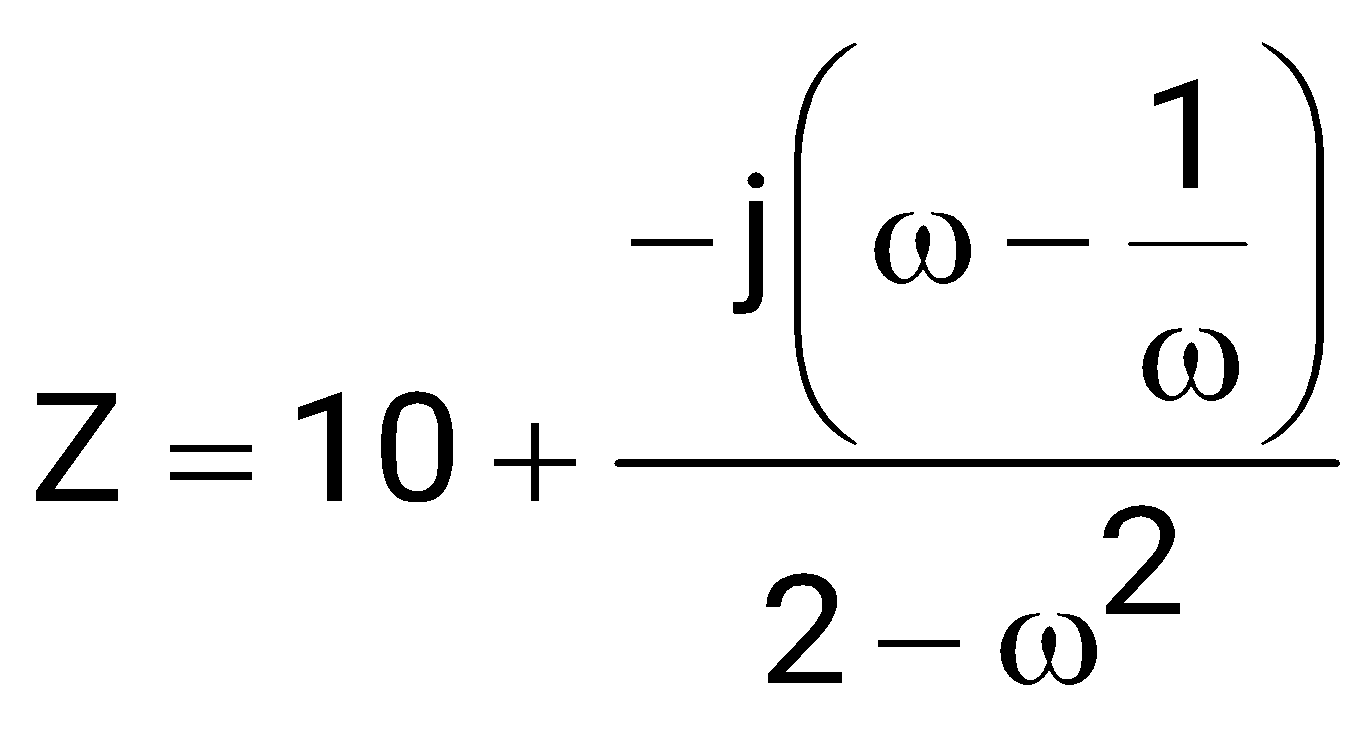

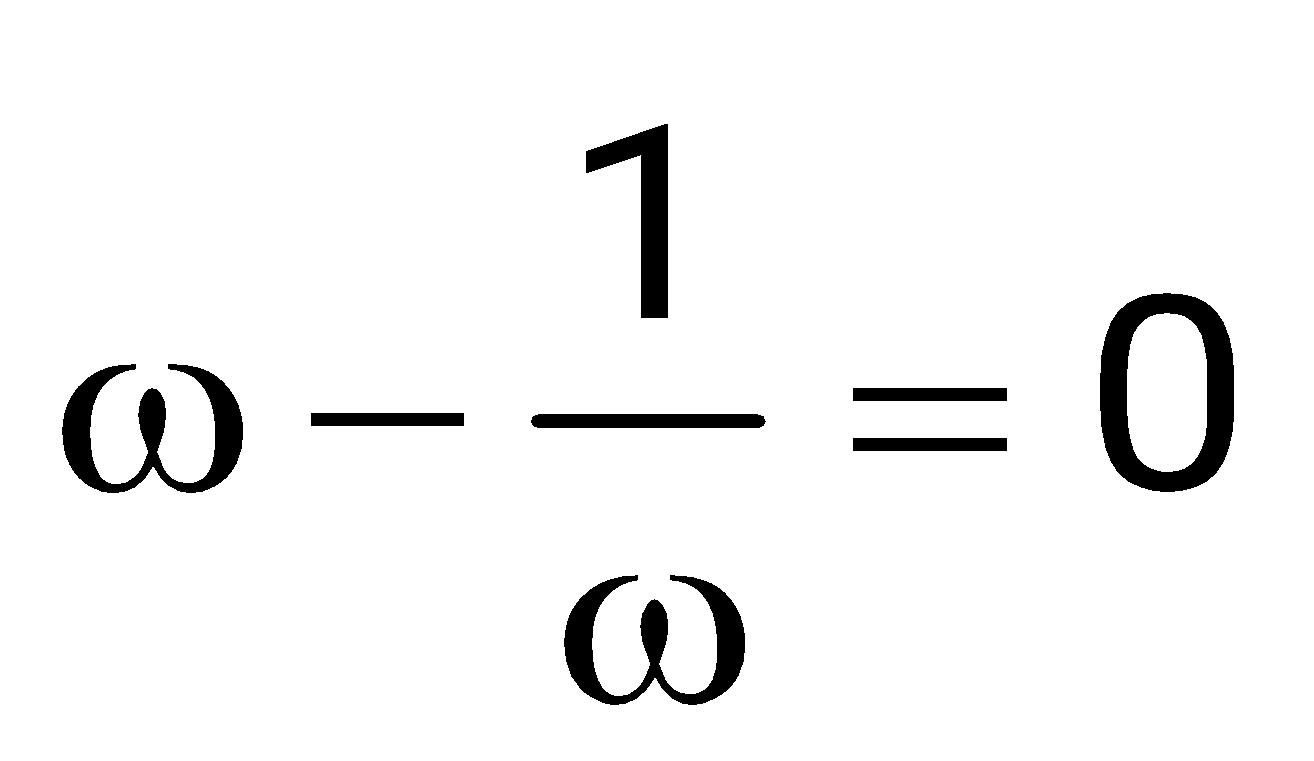

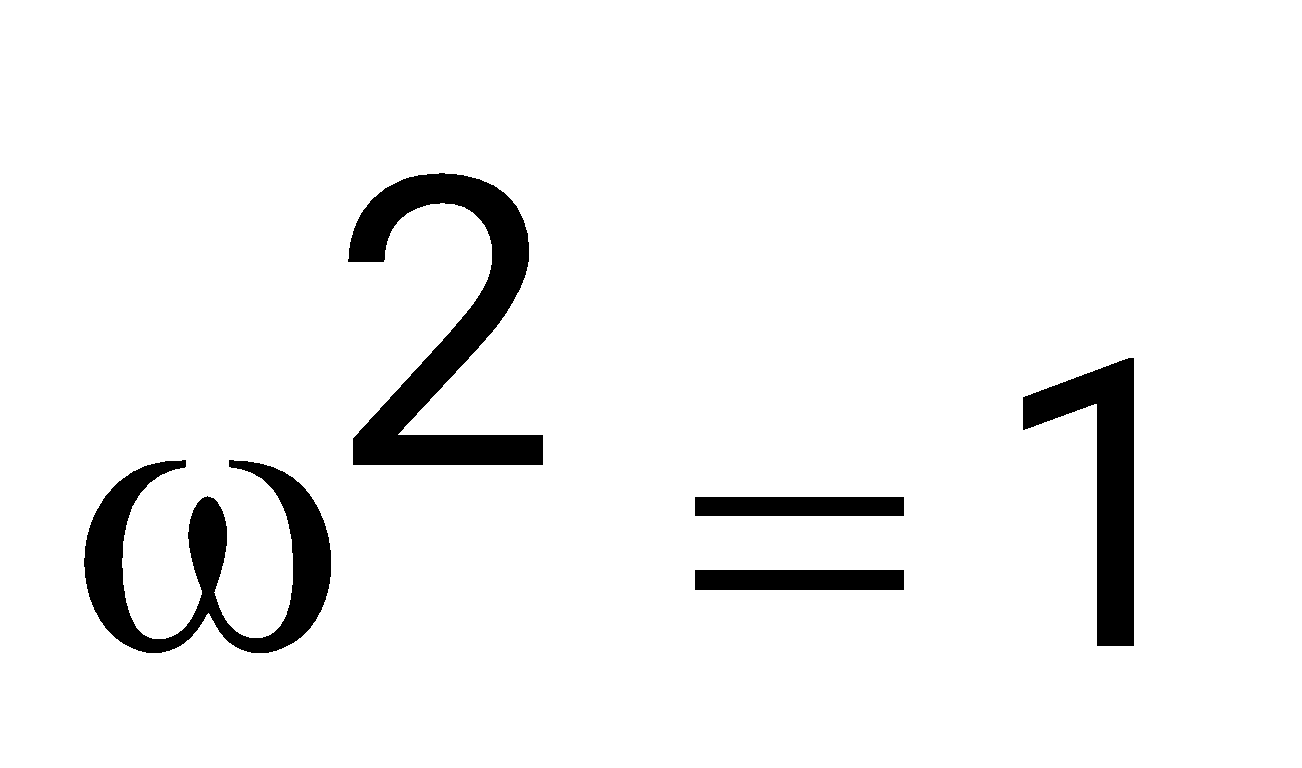

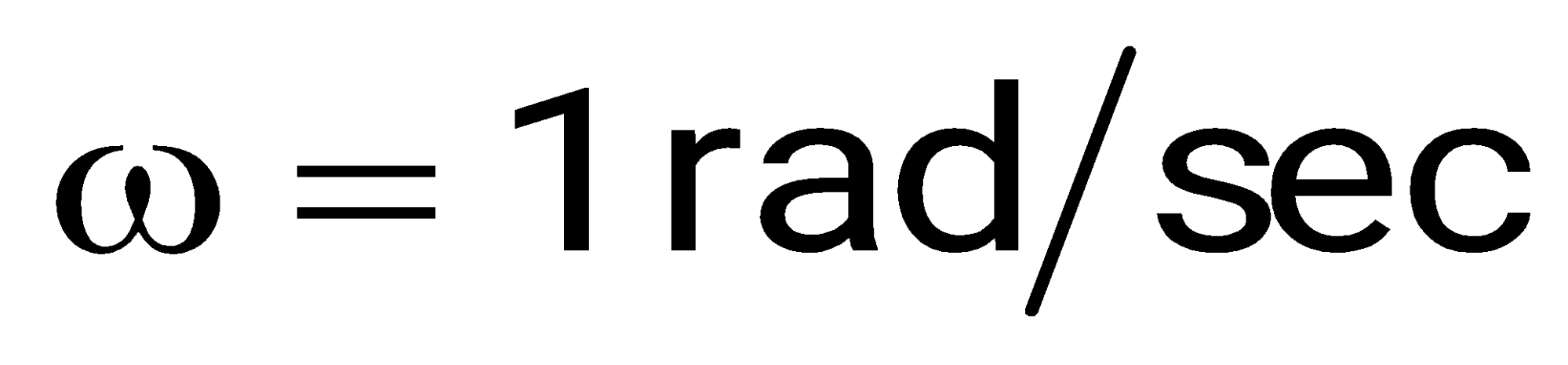

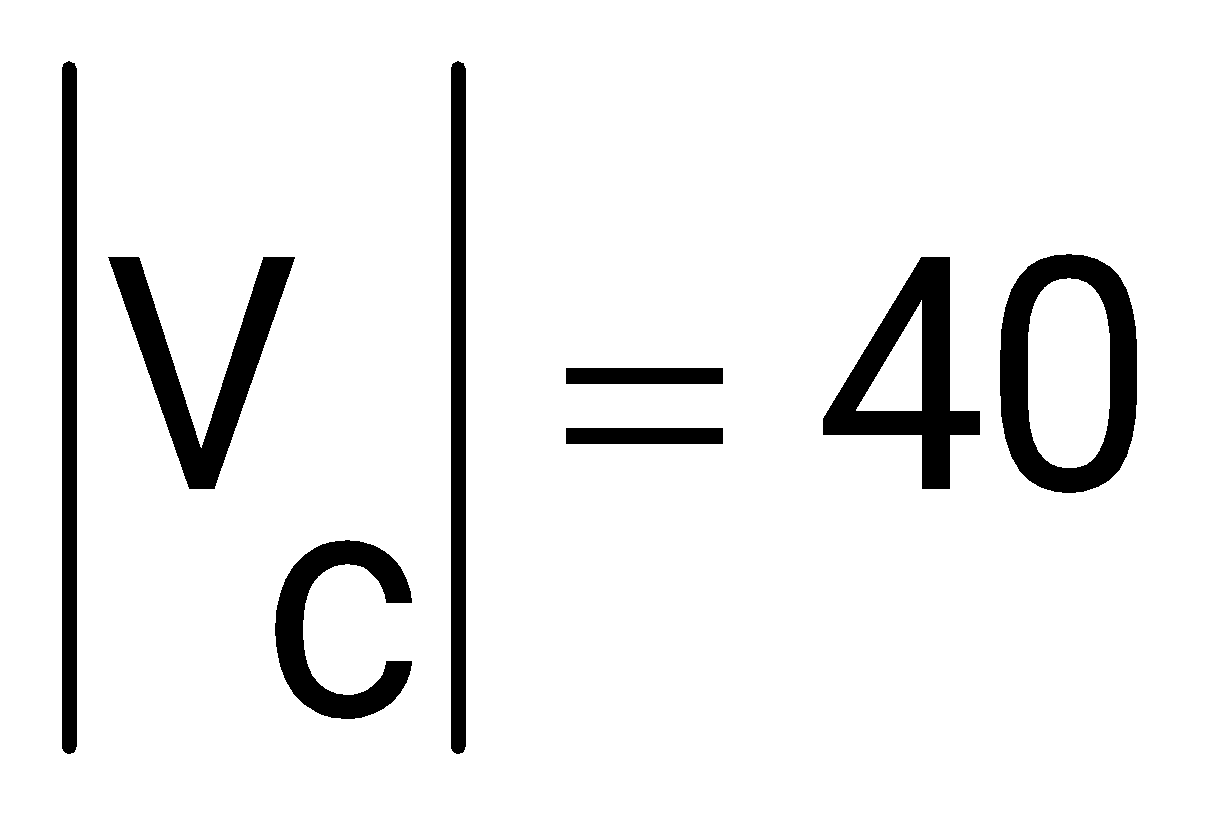

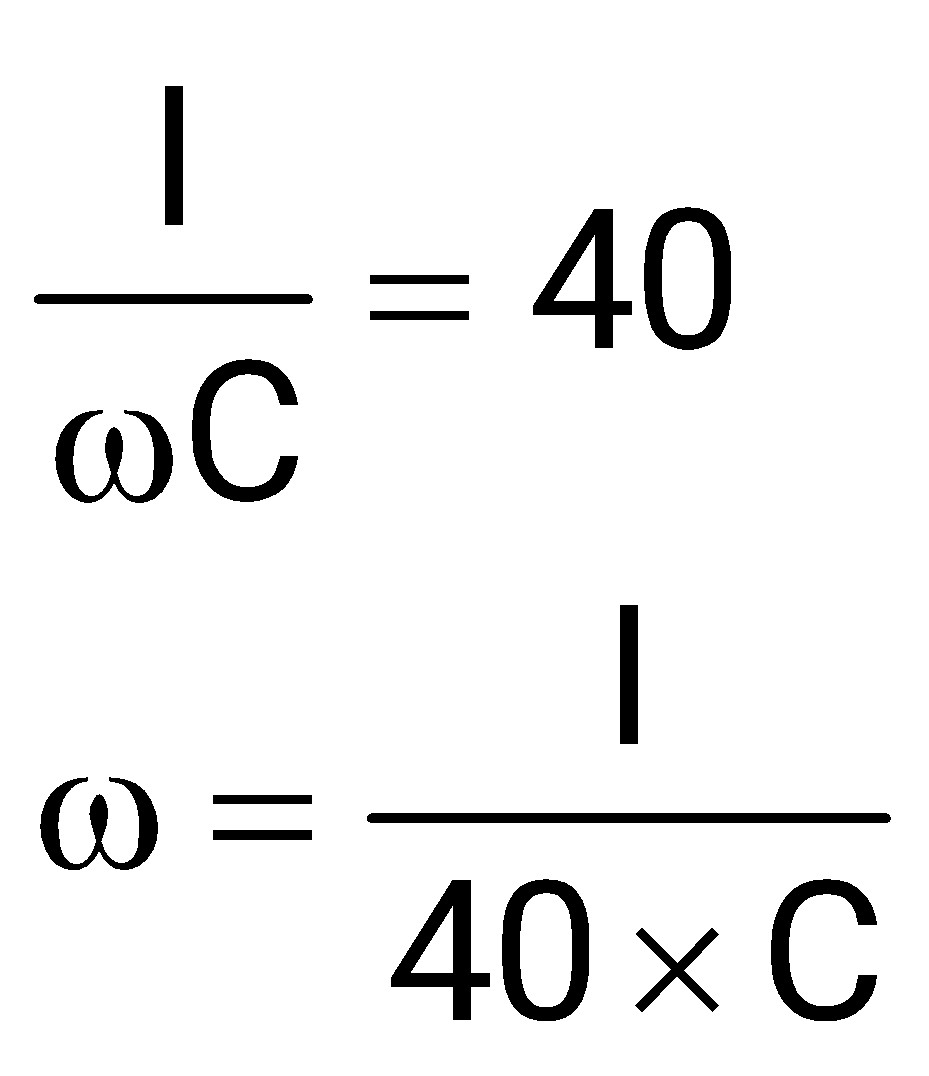

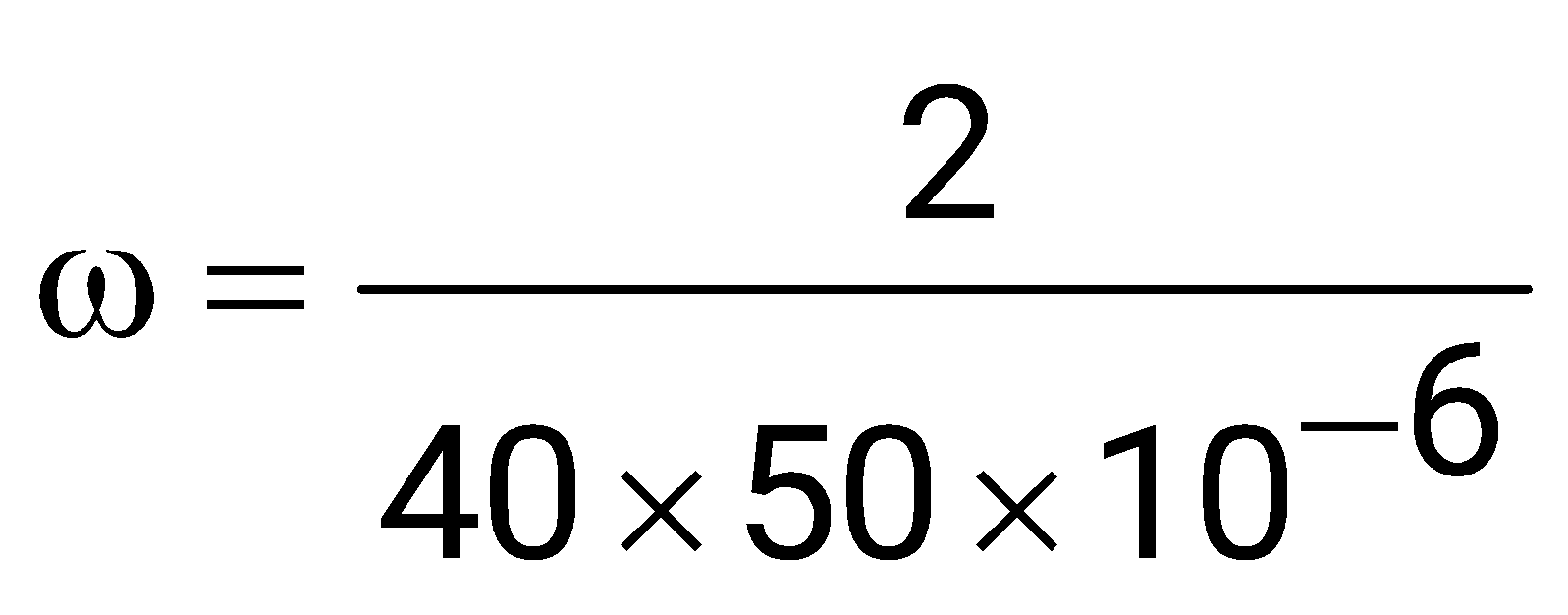

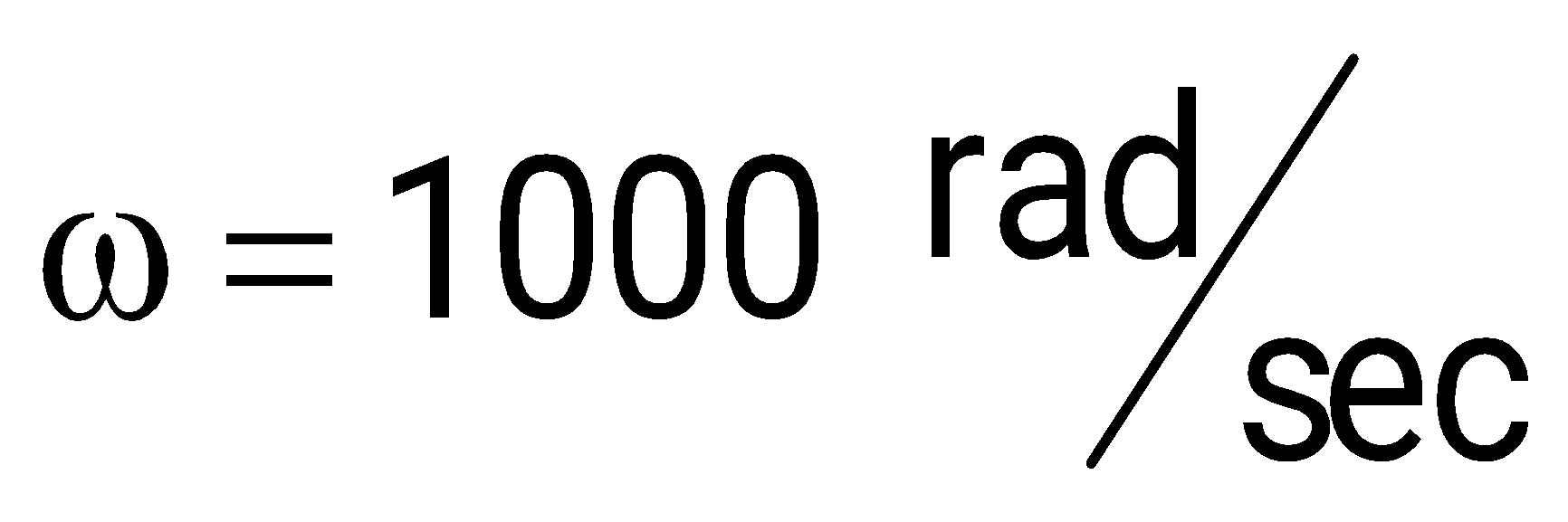

The voltage v(t) across the terminals a and b as shown in the figure, is a sinusoidal voltage having a frequency . When the inductor current i(t) is in phase with the voltage v(t), the magnitude of the impedance Z (in ) seen between the terminals a and is _______ (up to 2 decimal places).

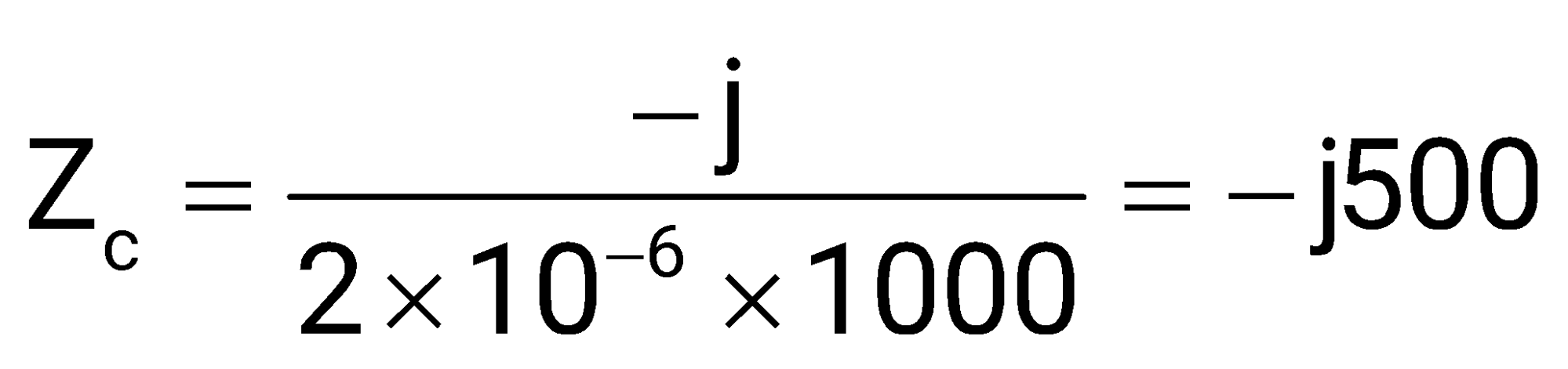

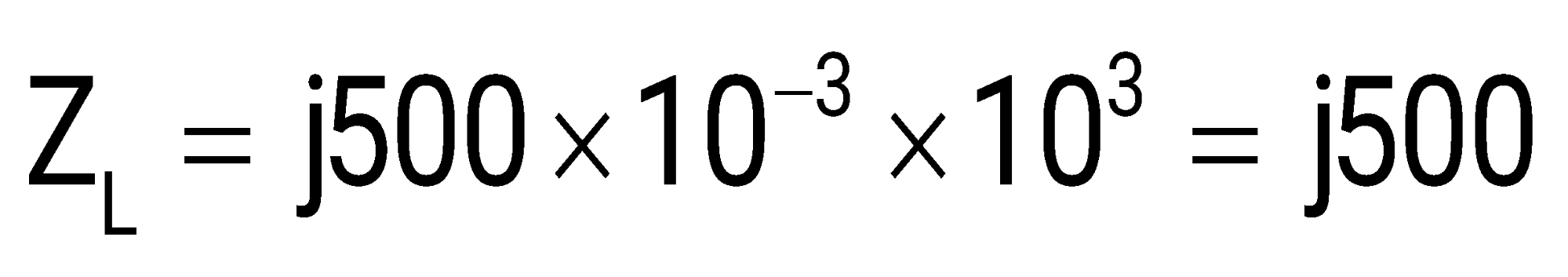

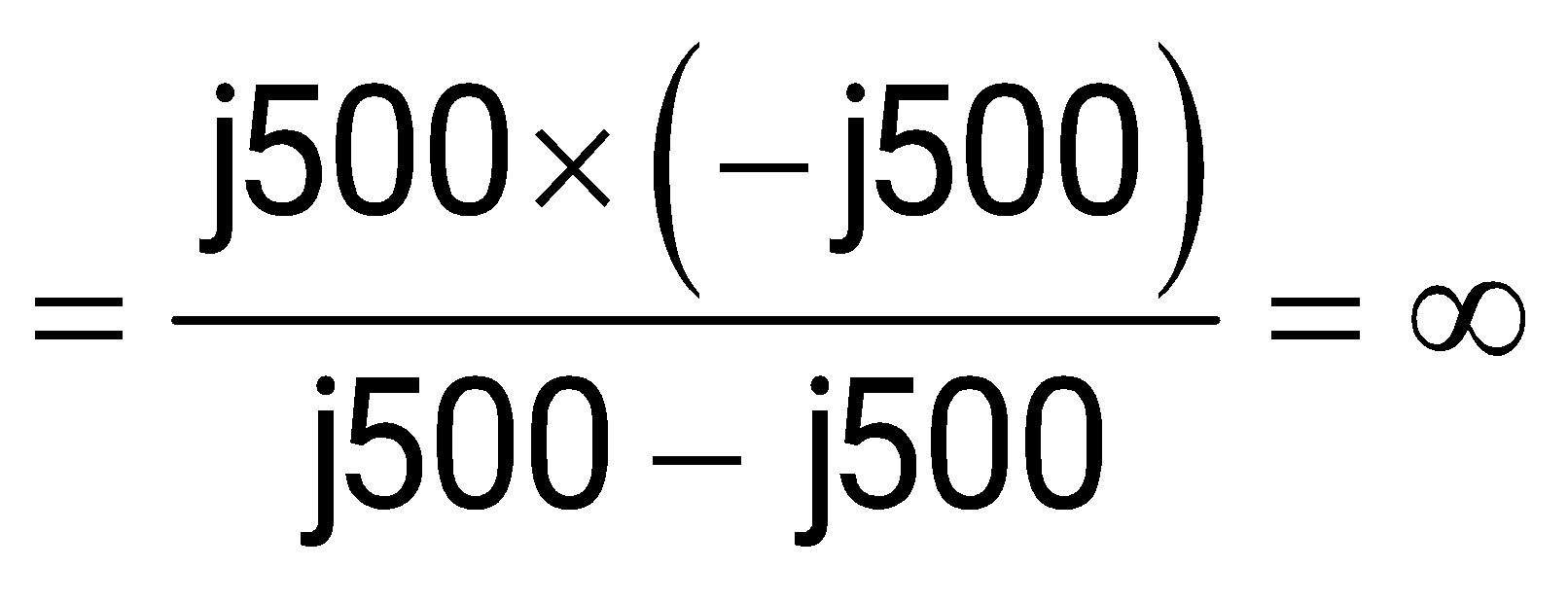

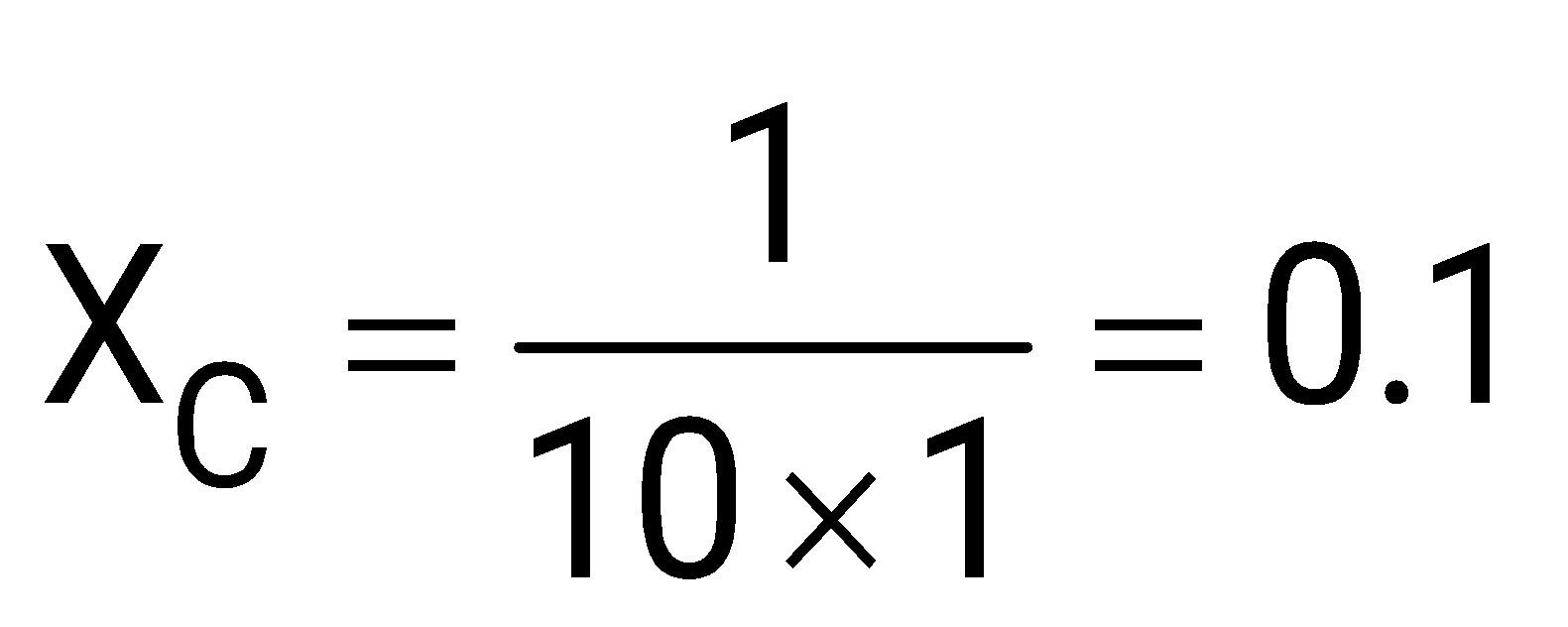

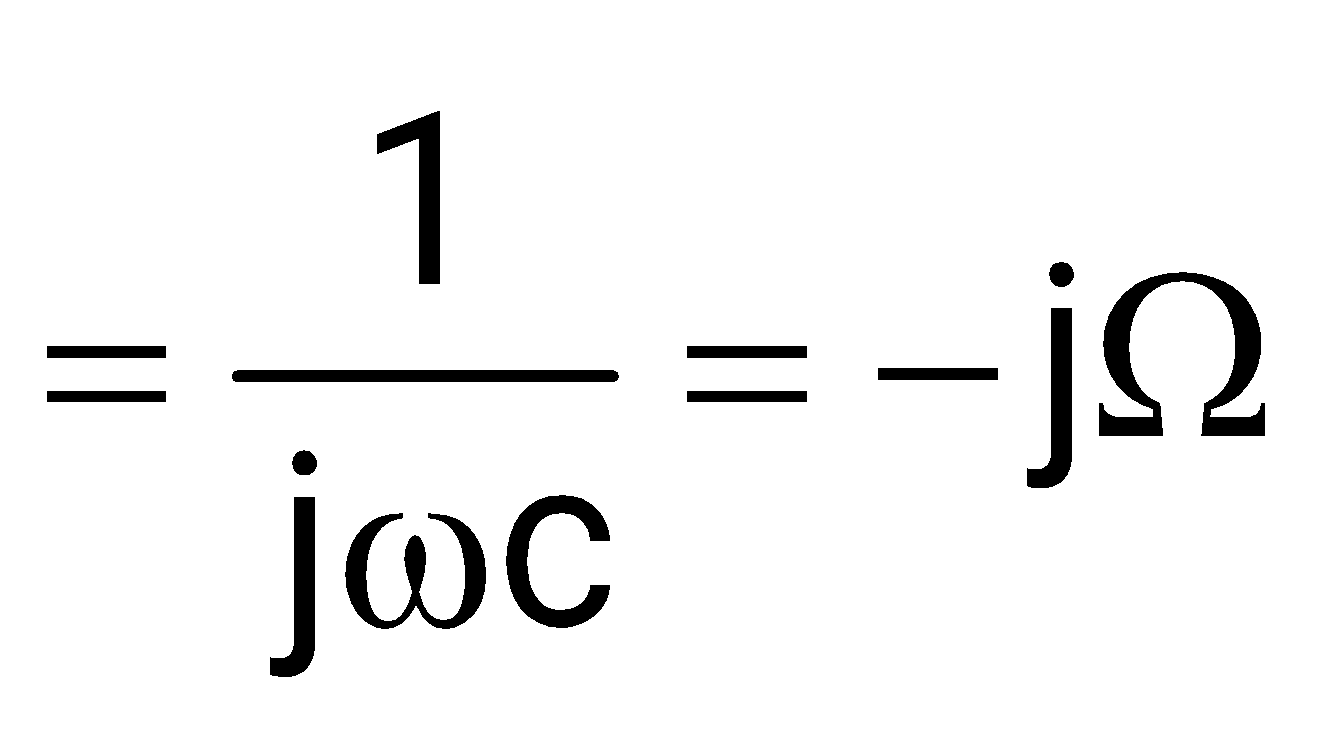

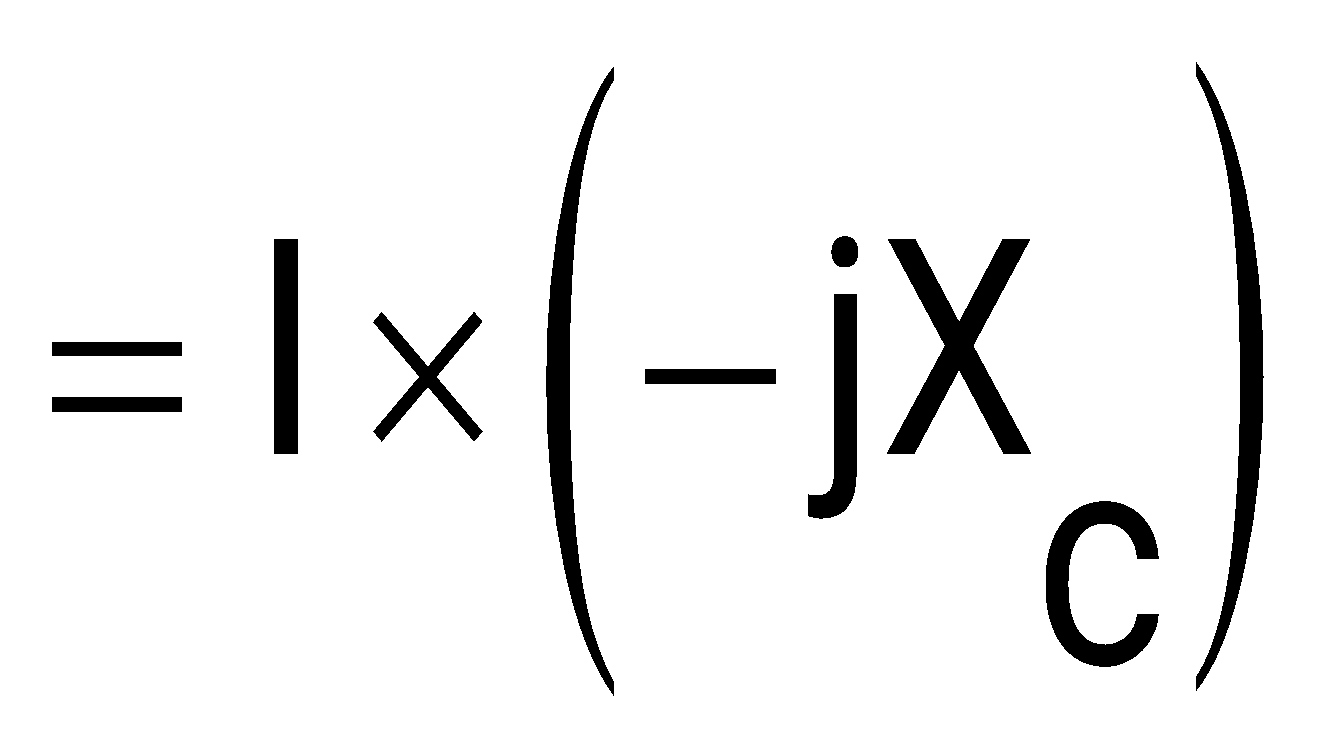

Reactance of capacitor

Parallel combination of R & C

Total impedance

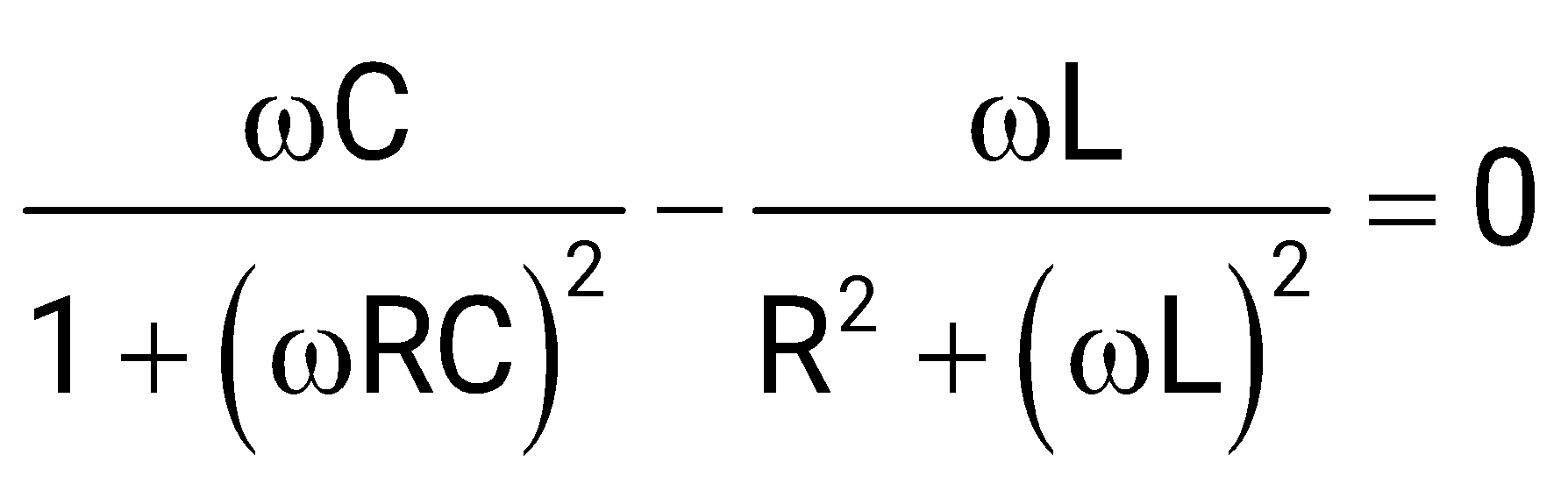

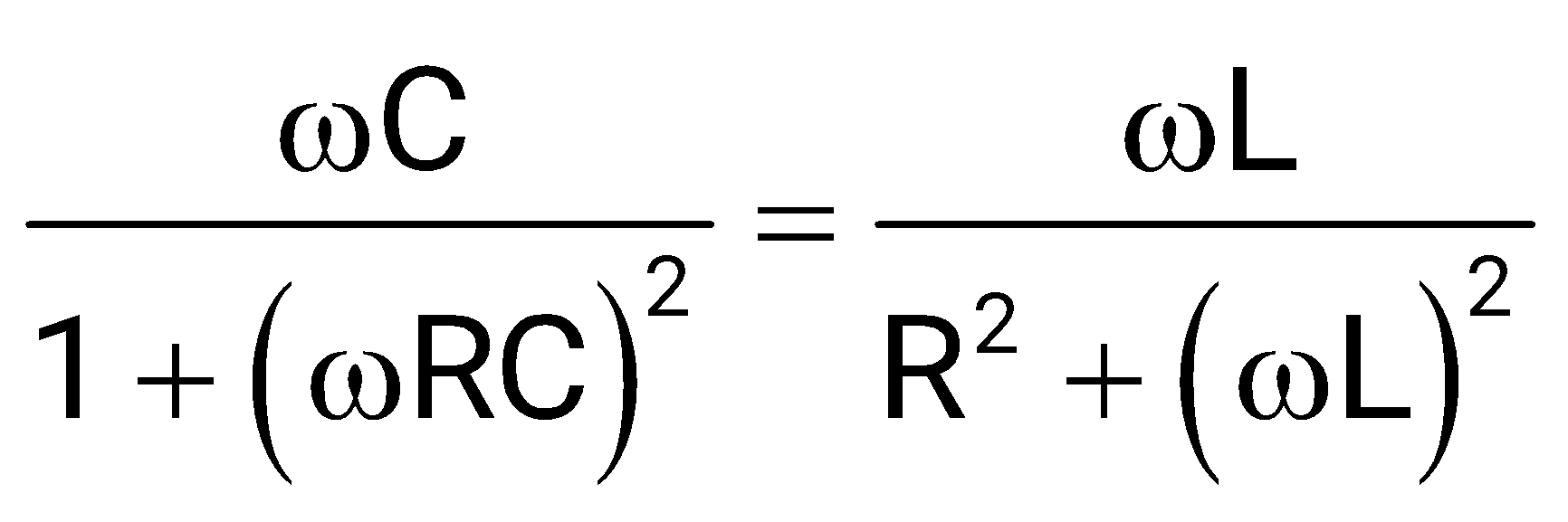

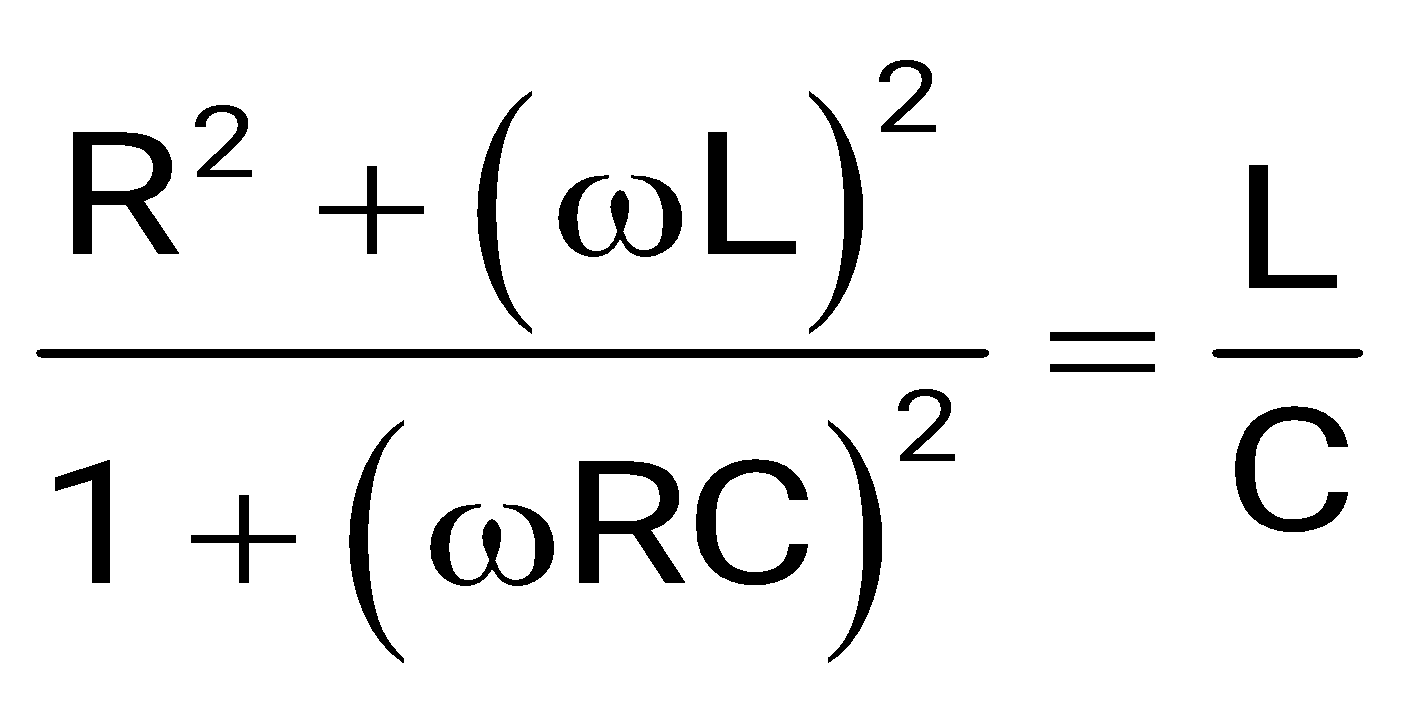

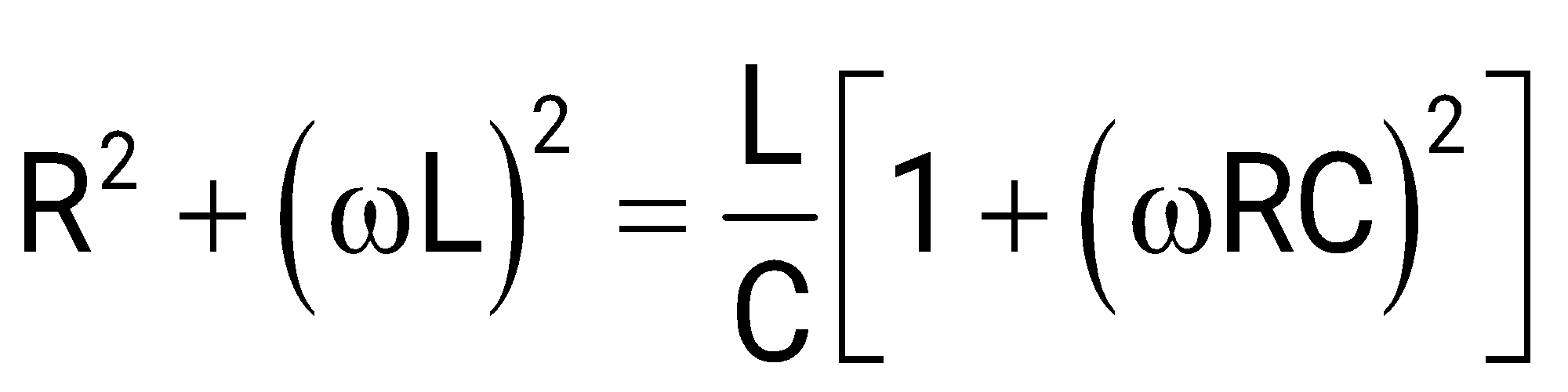

Since current & voltage have same phase. Imaginary part of impedance should be zero

Hence,

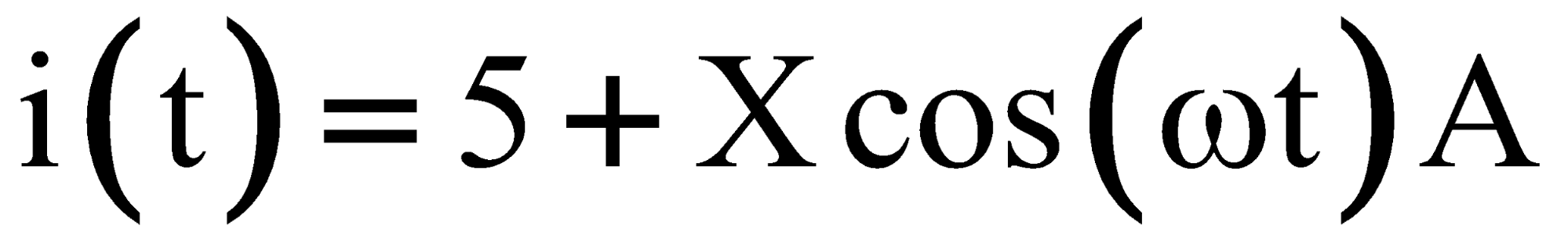

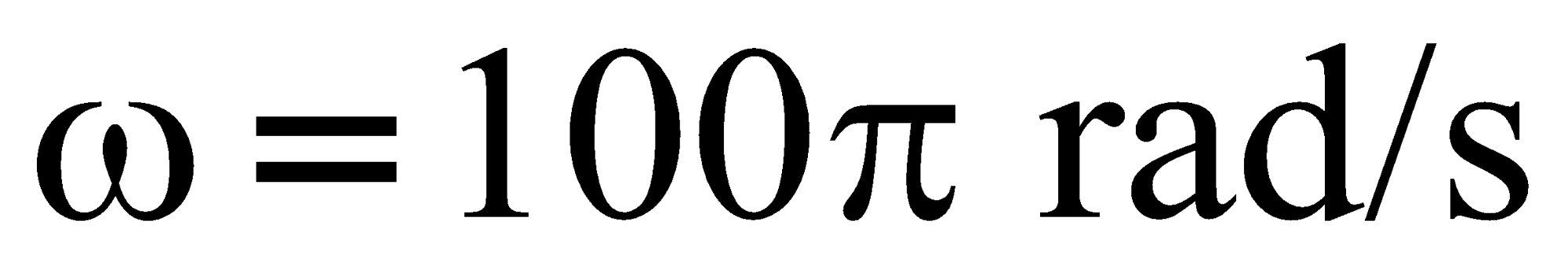

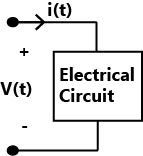

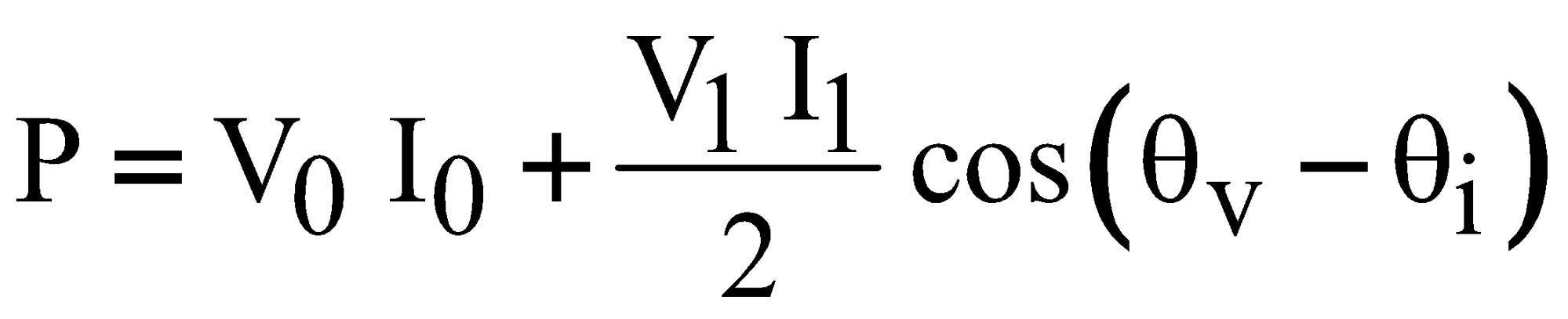

The voltage across the circuit in the figure, and the current through it are given by the following expressions:

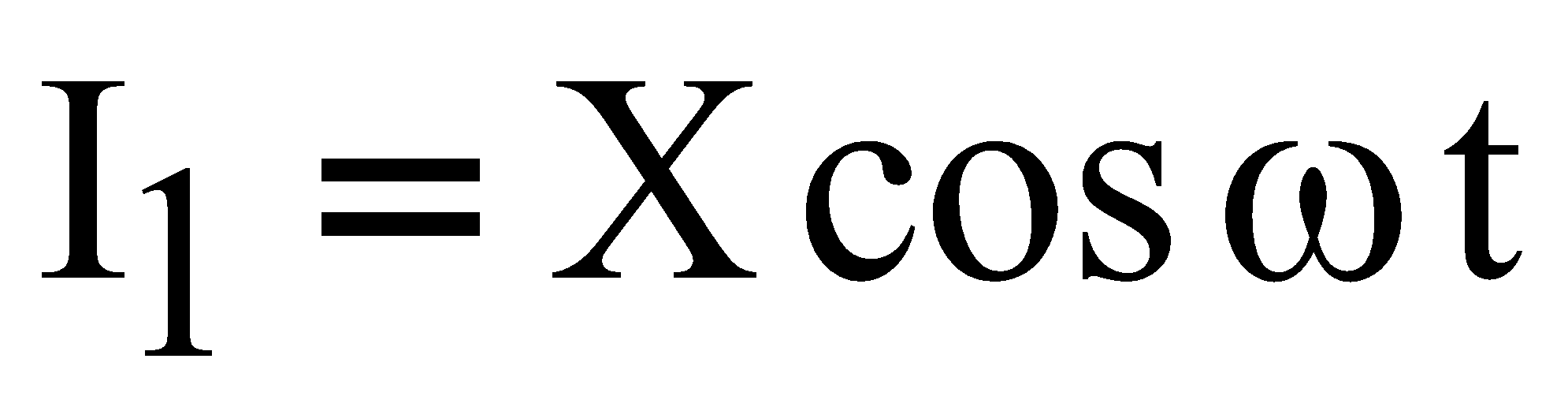

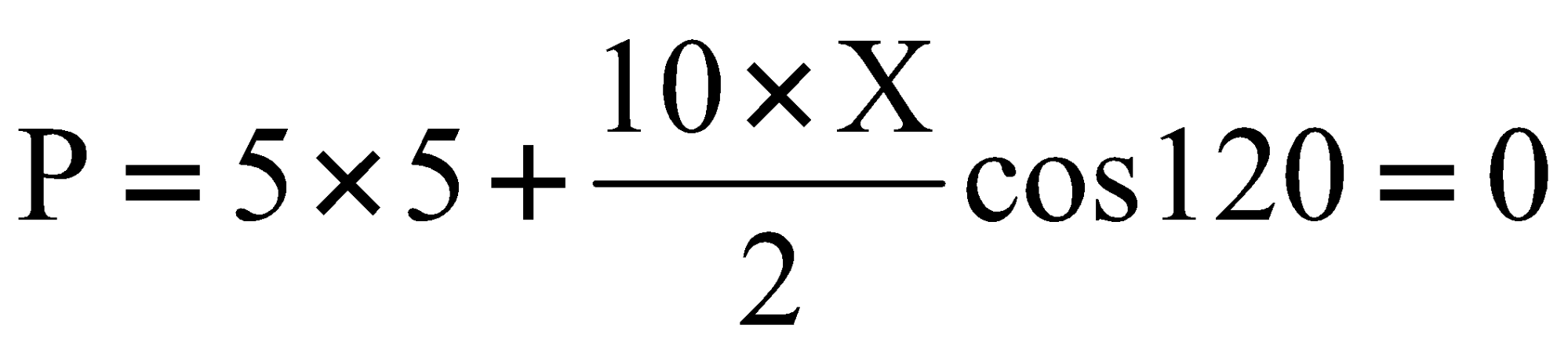

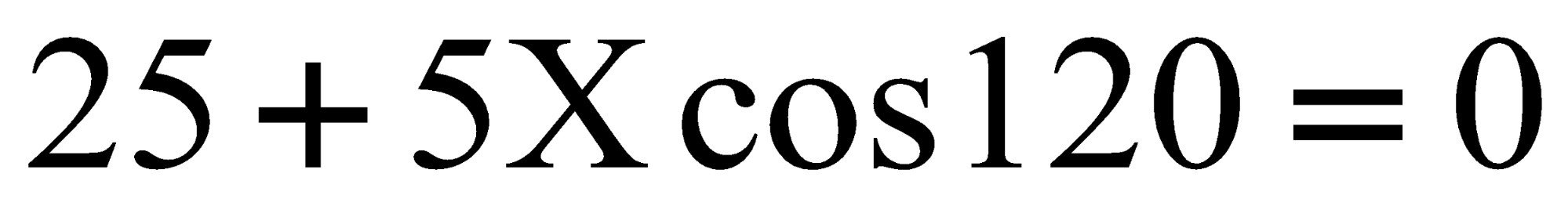

Where , If the average power delivered to the circuit is zero then the value of X (in Ampere) is ________ (up to 2 decimal places).

For calculation of power, same frequency terms must be used in both voltage & current.

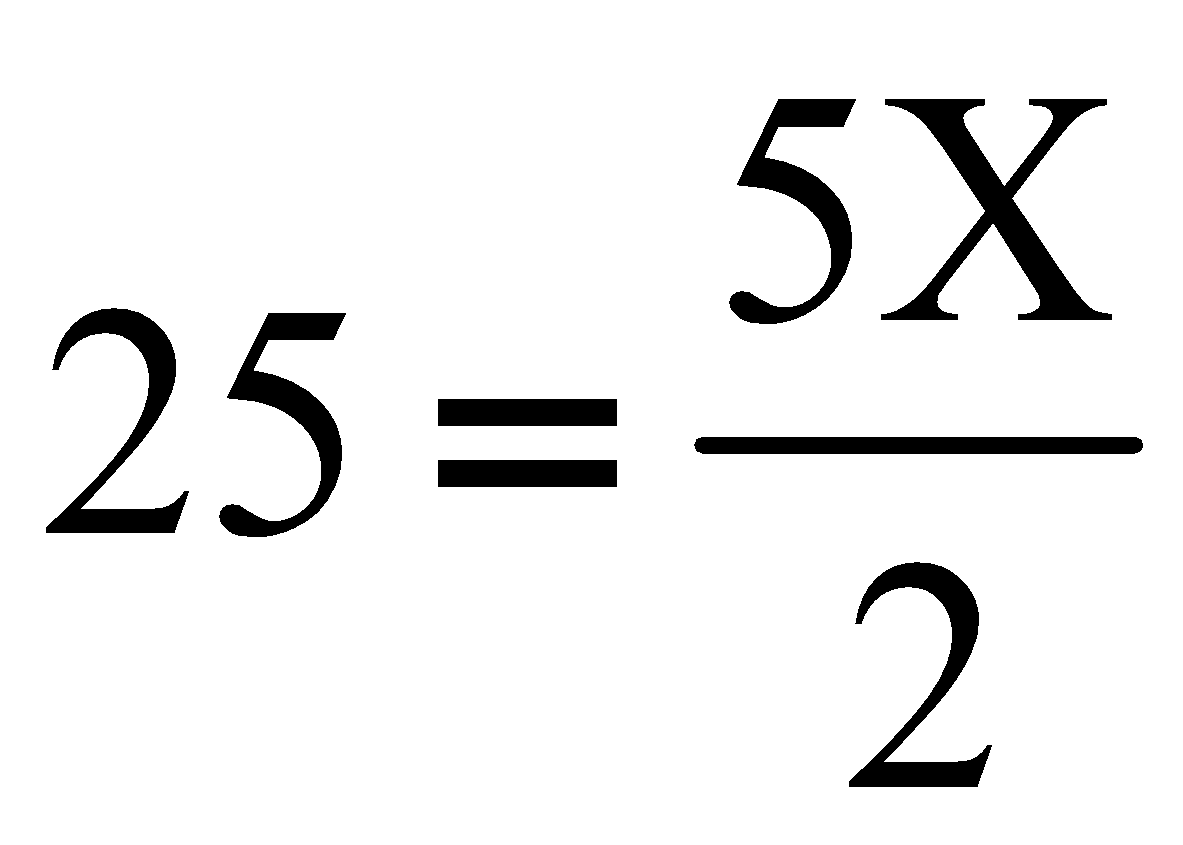

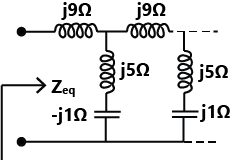

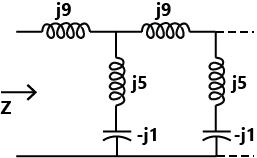

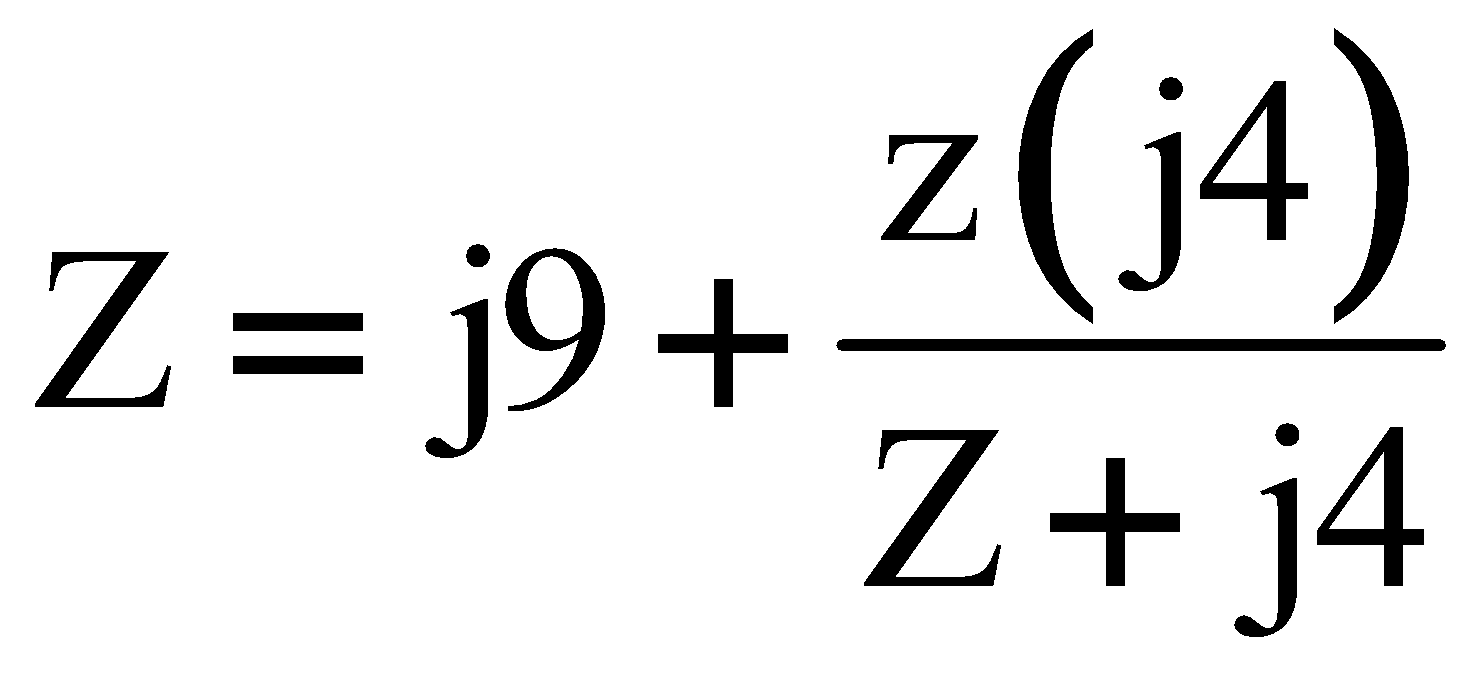

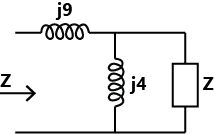

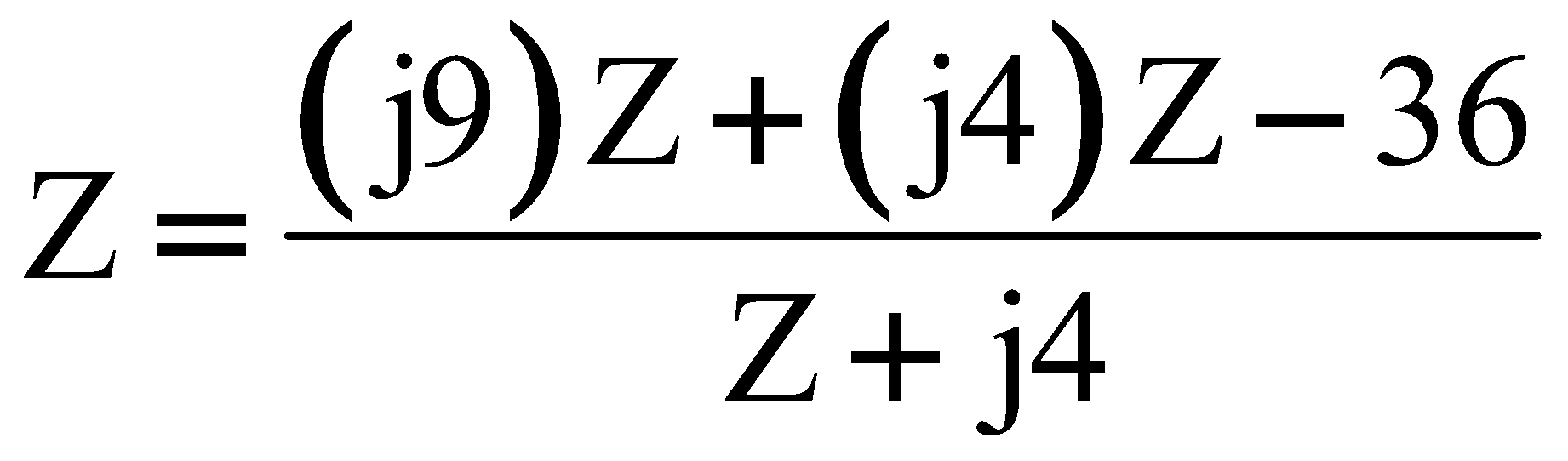

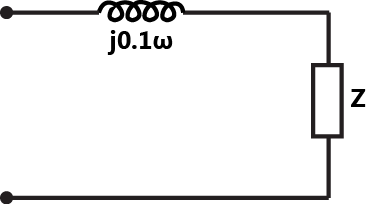

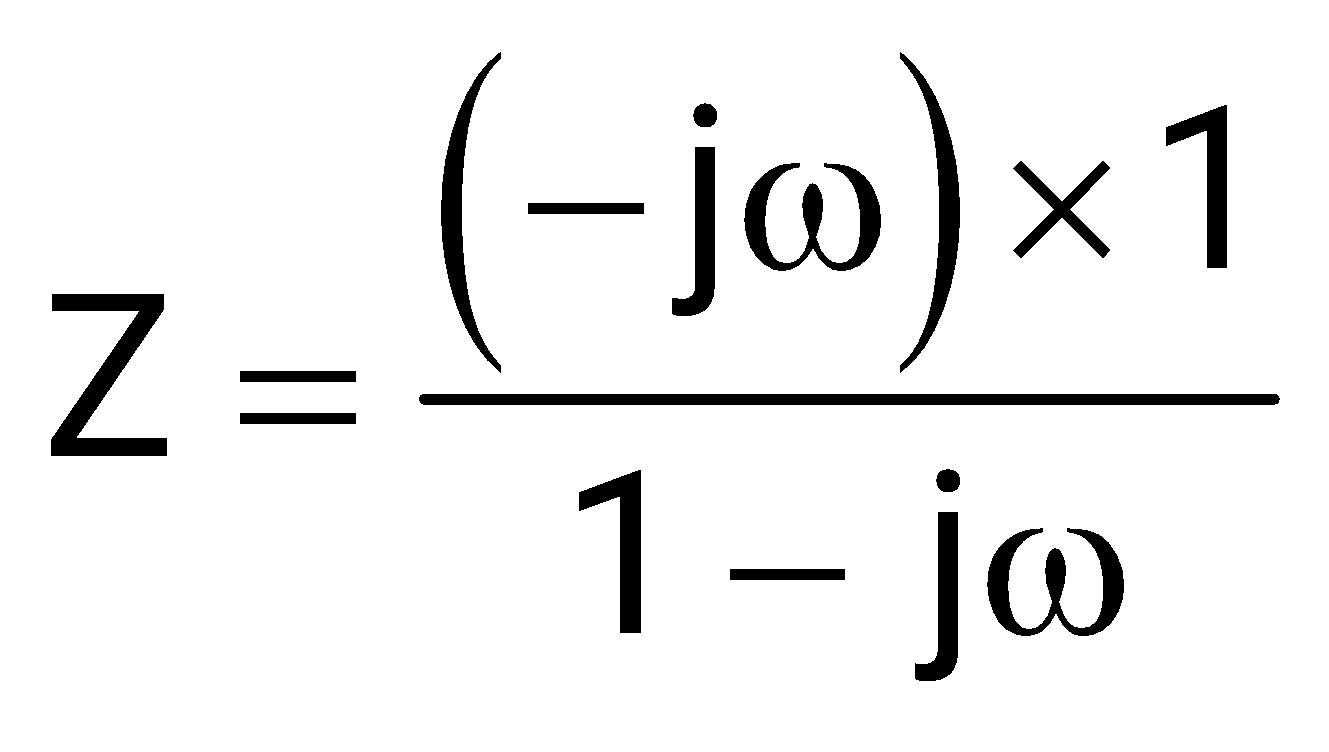

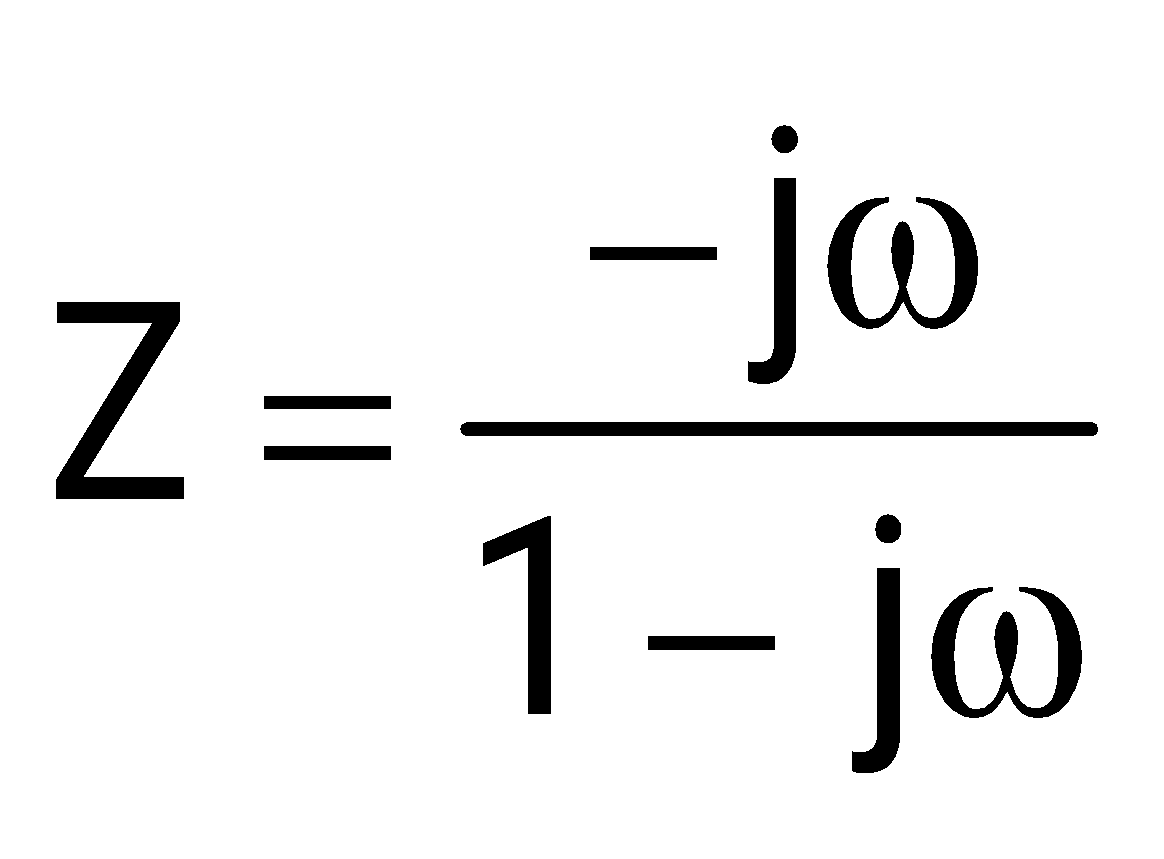

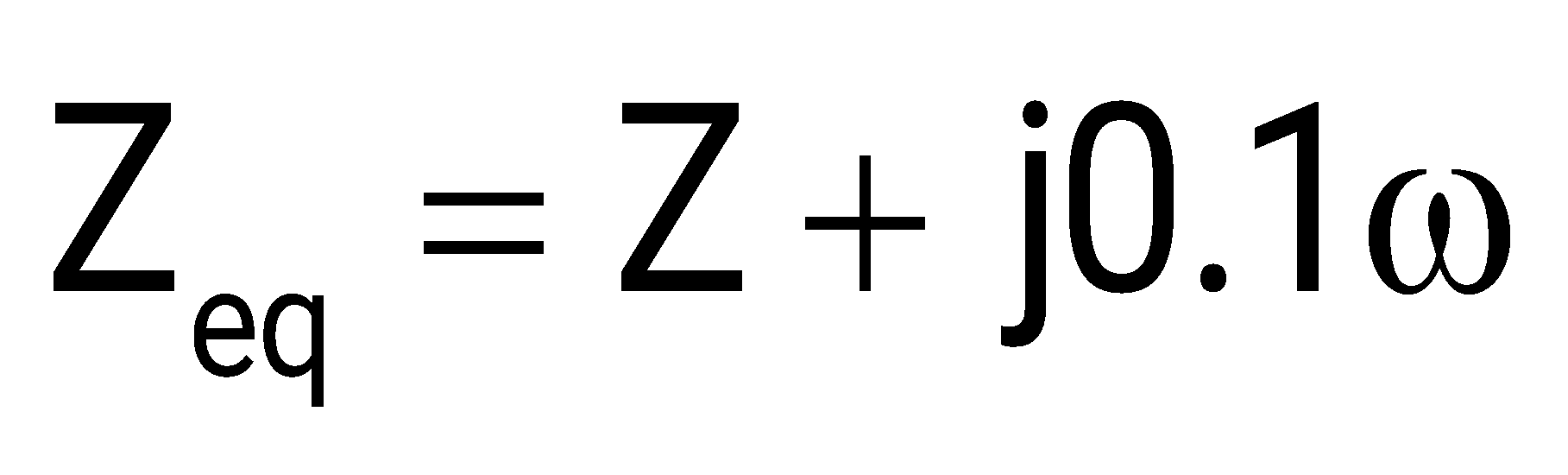

The equivalent impedance for the infinite ladder circuit shown in the figure is

Assume equivalent impedance = Z

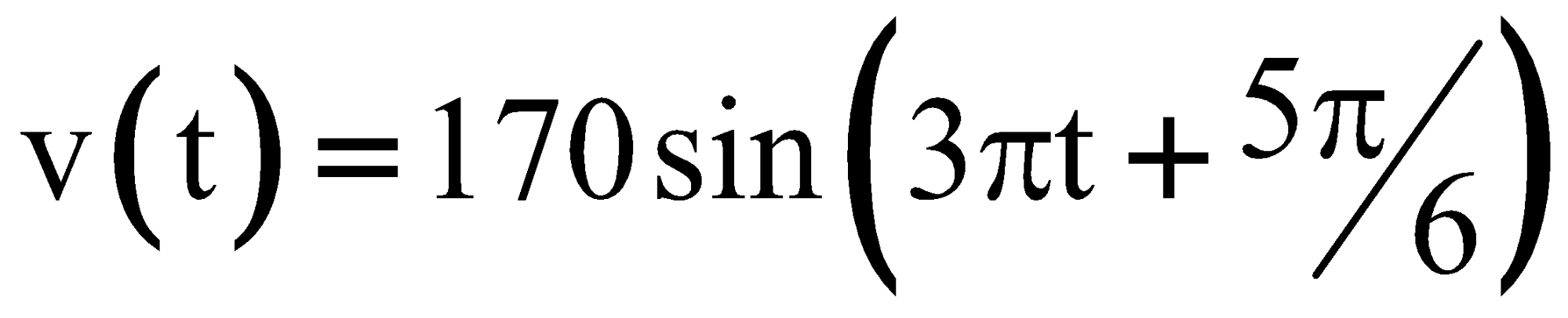

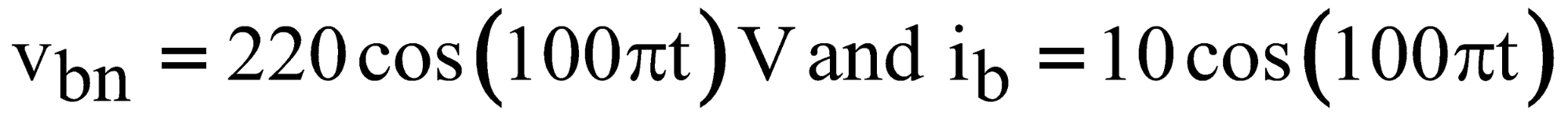

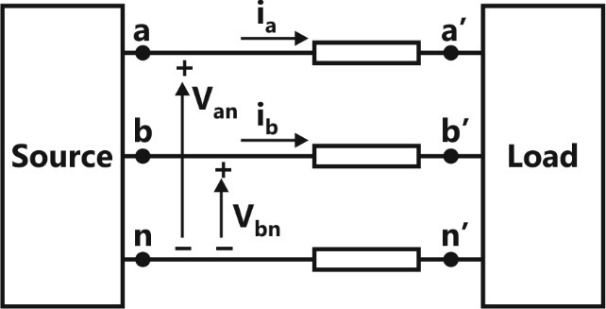

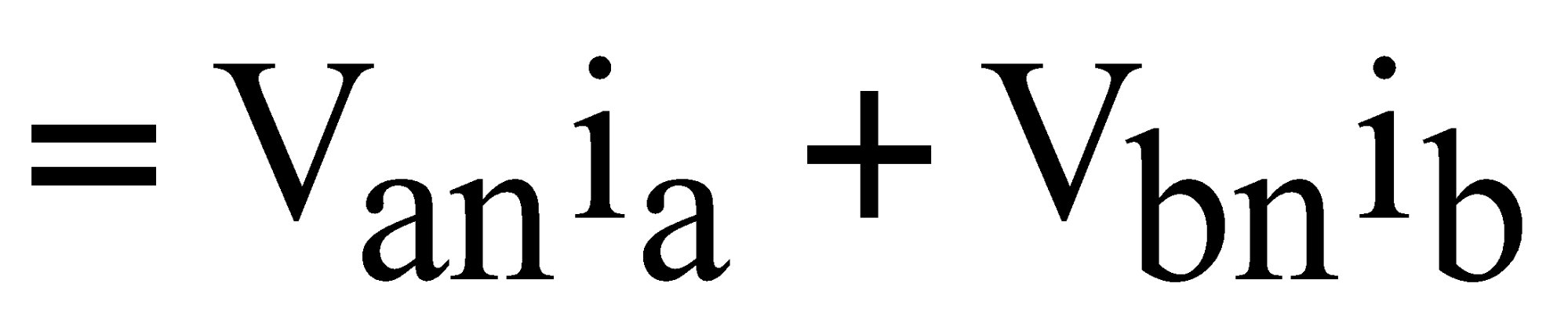

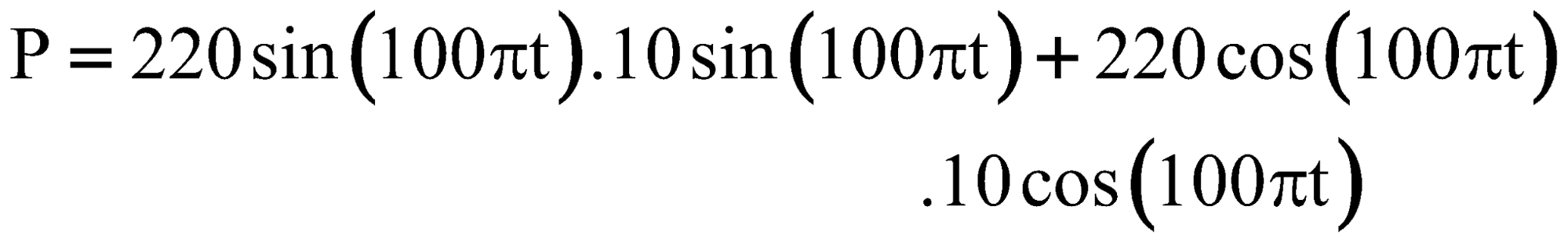

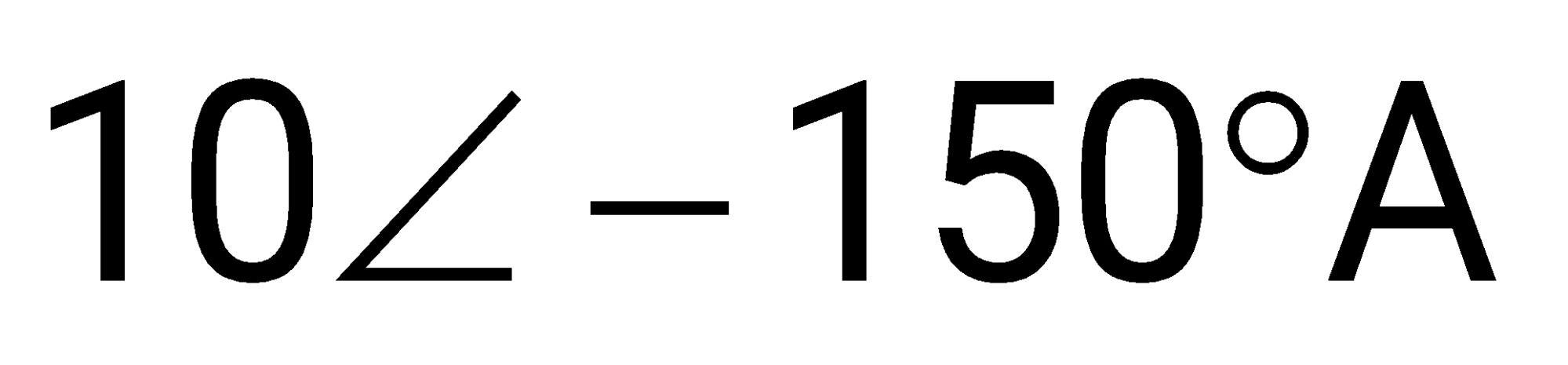

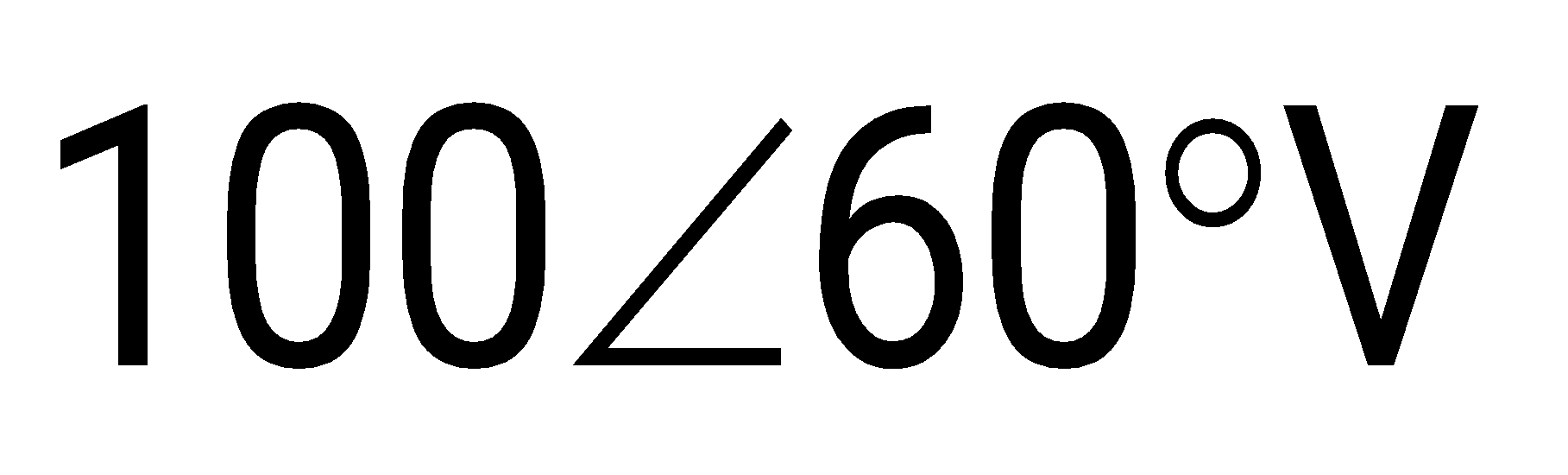

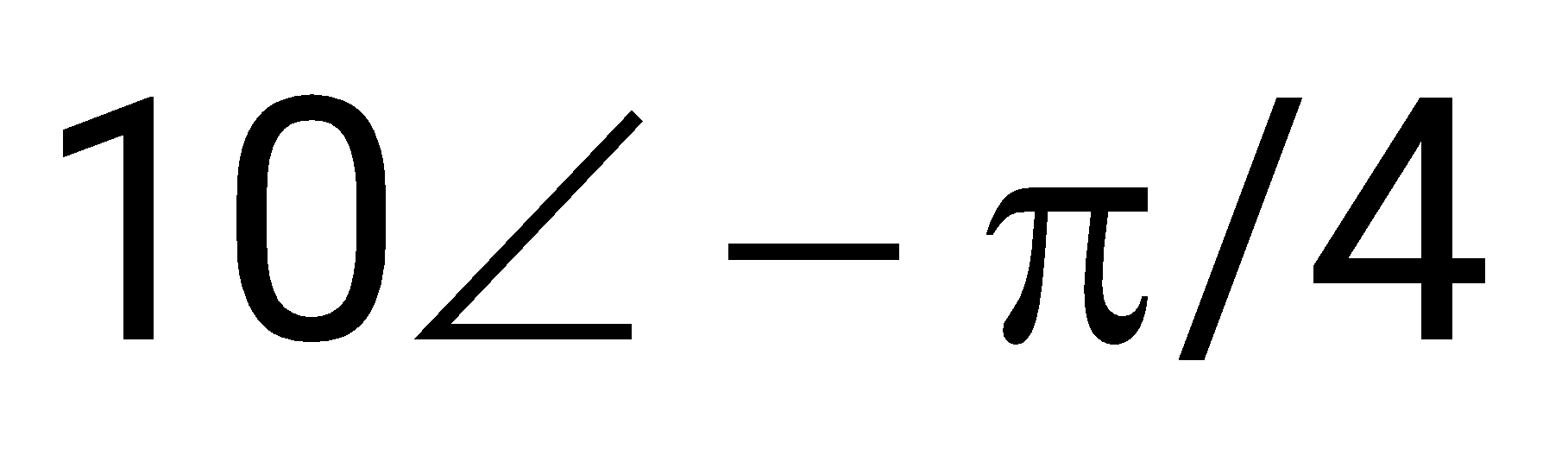

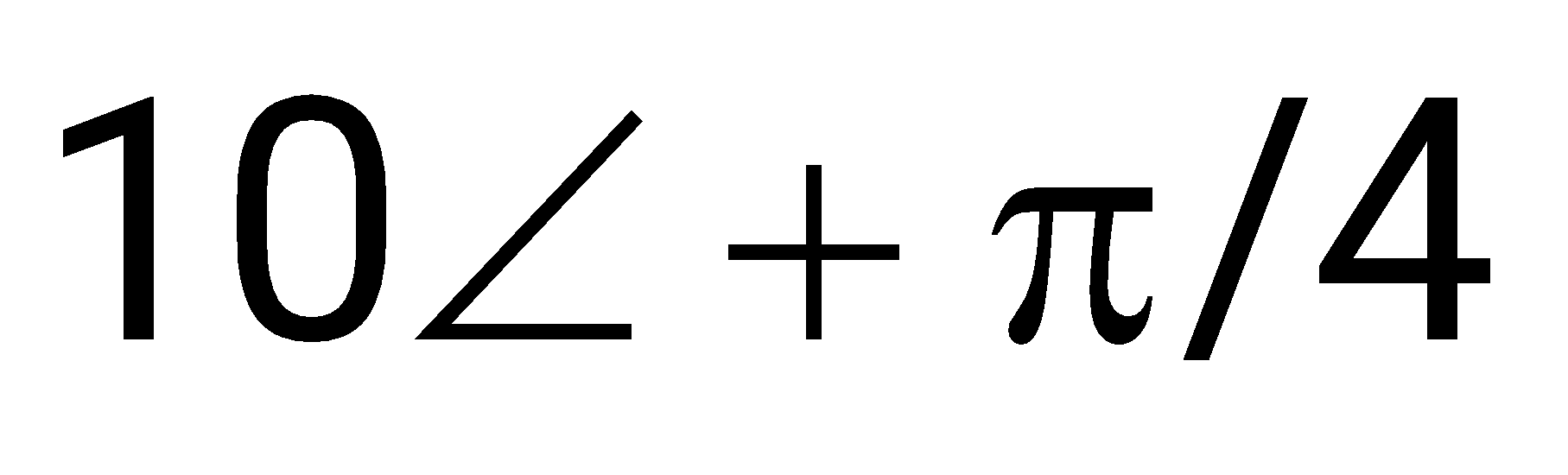

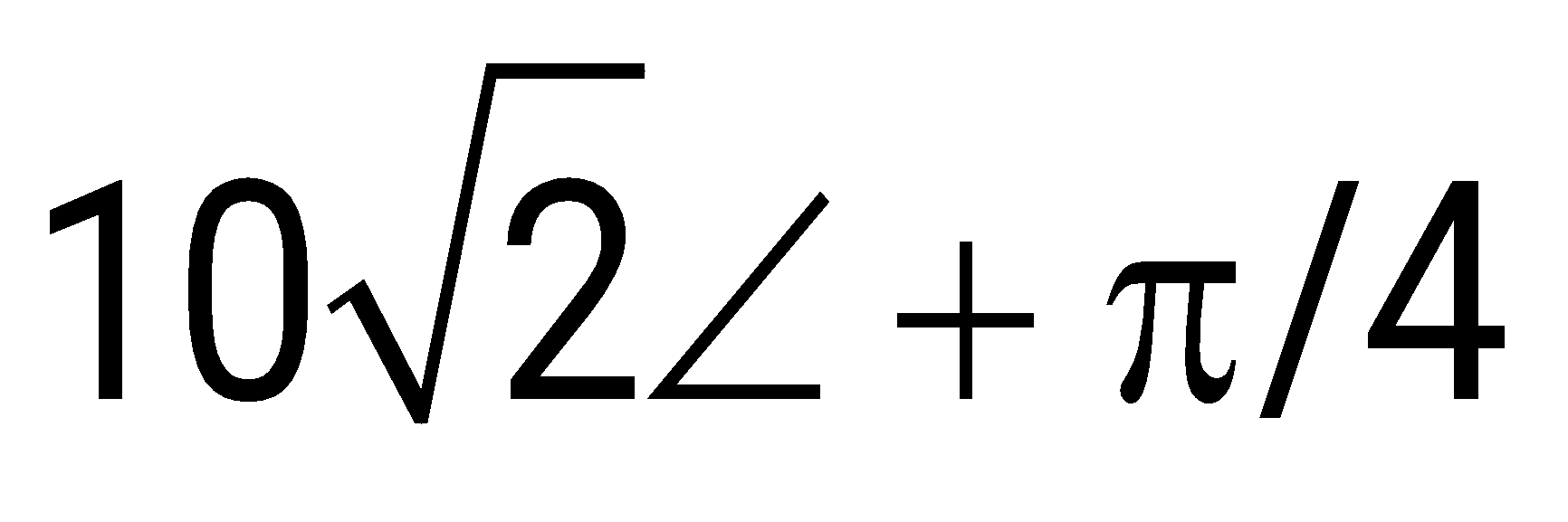

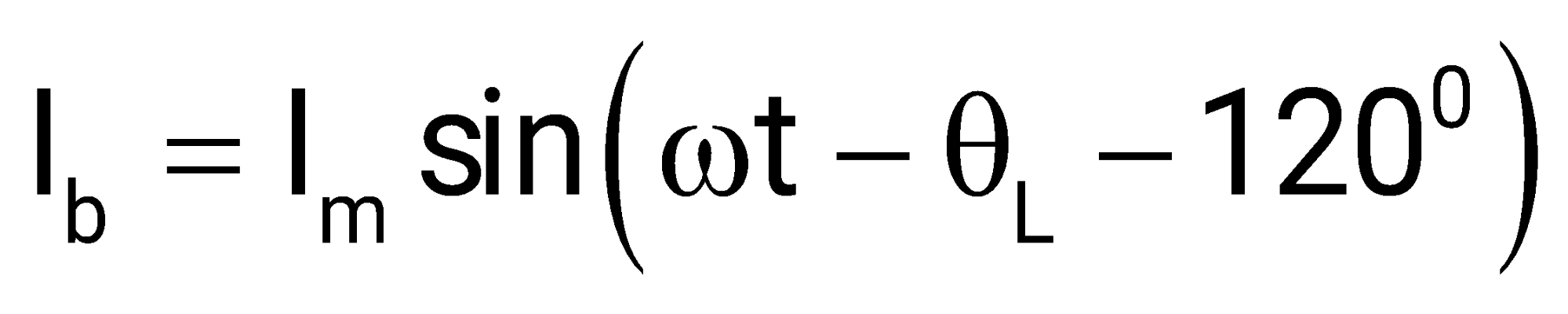

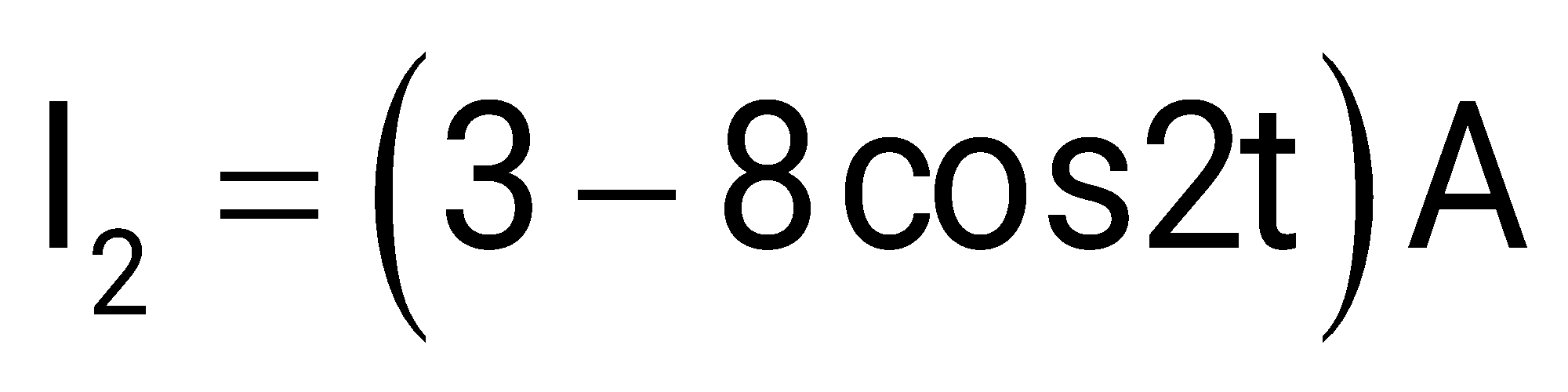

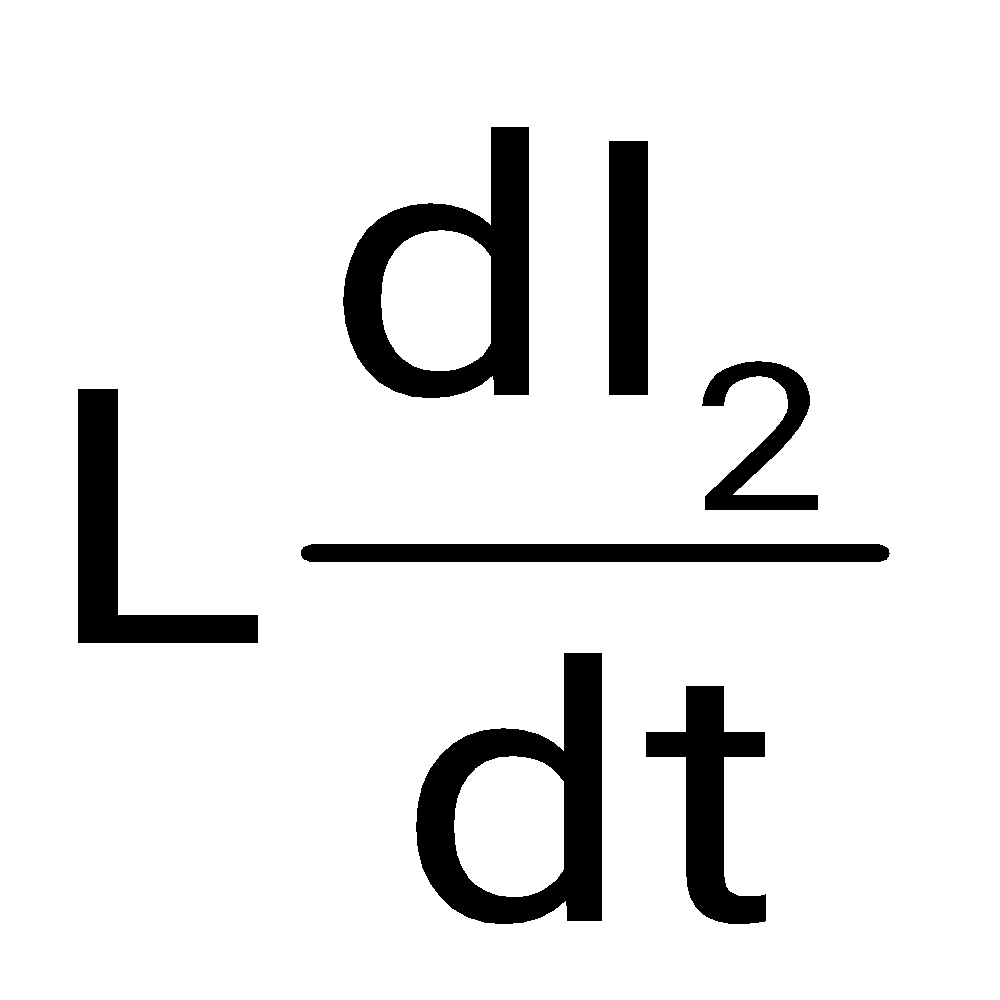

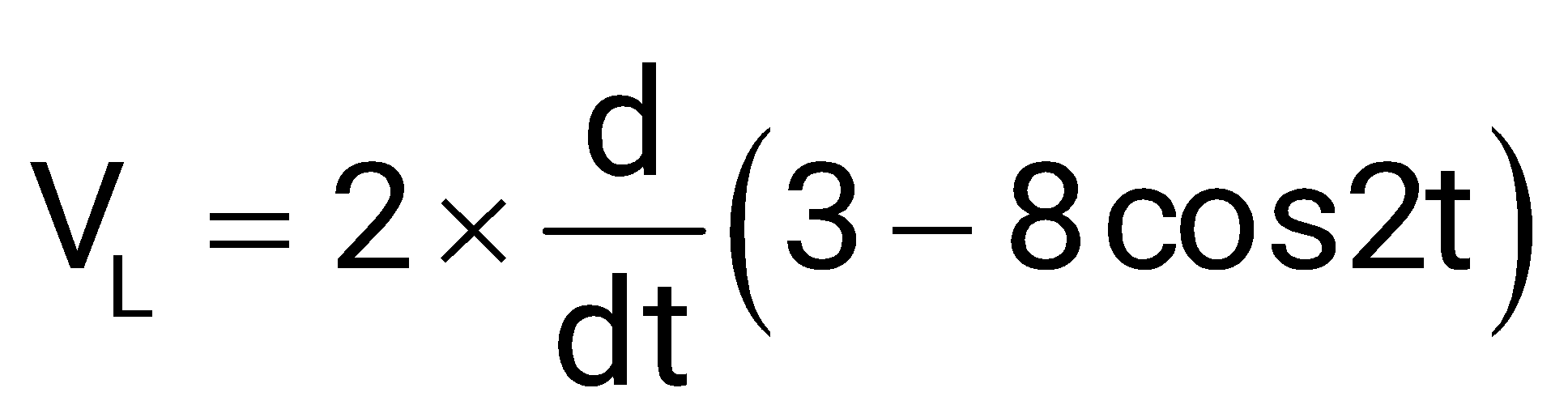

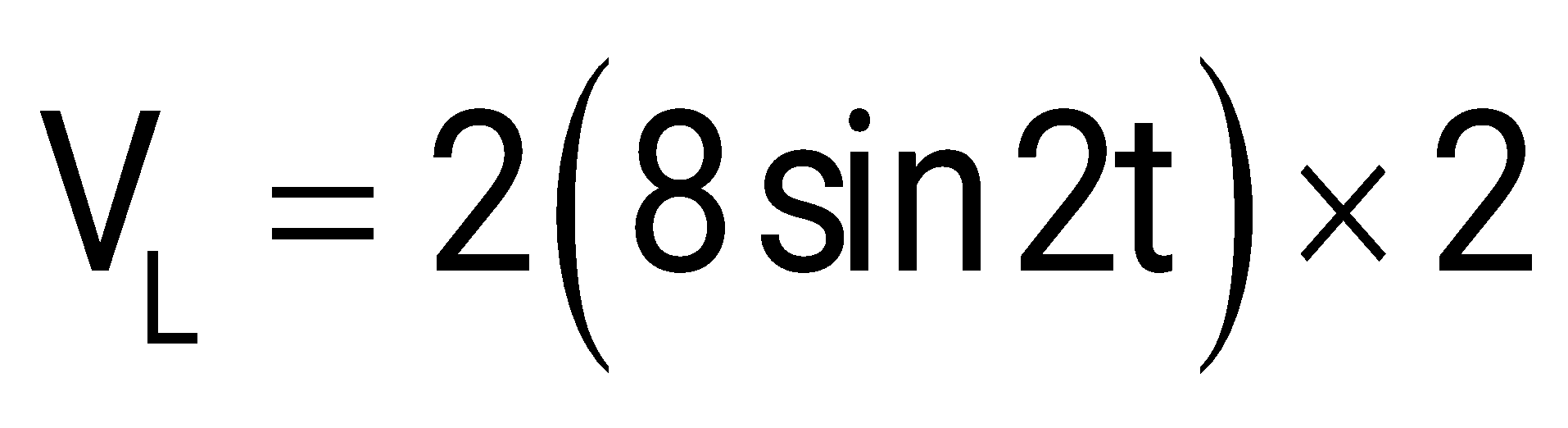

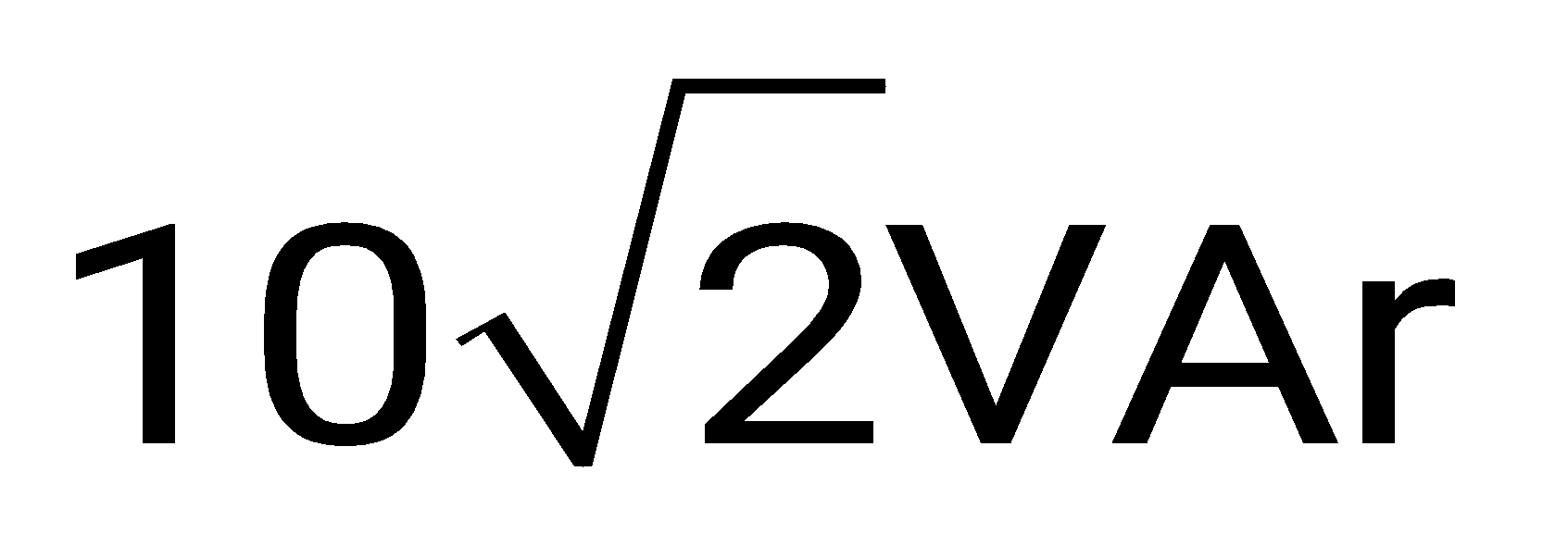

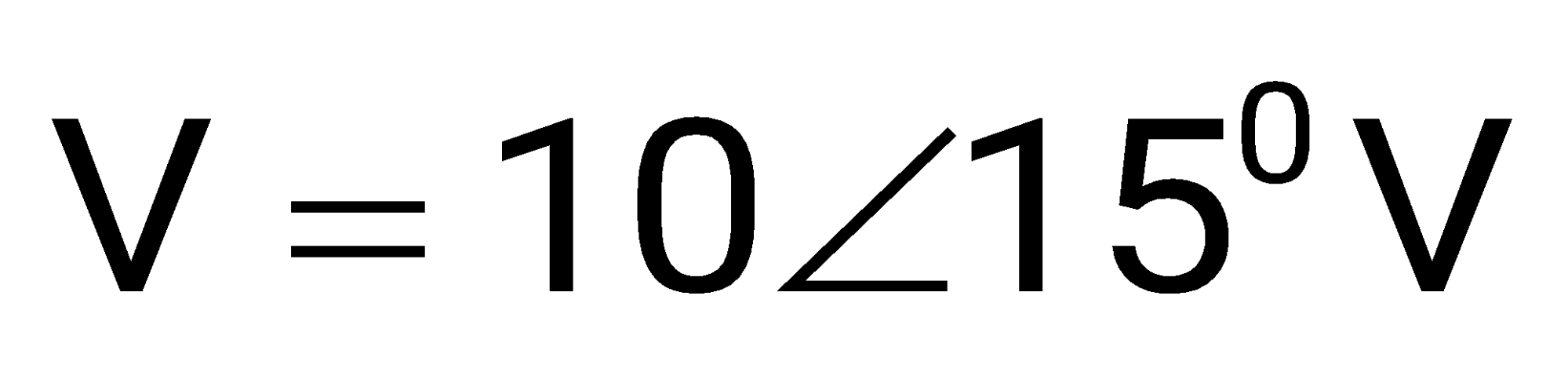

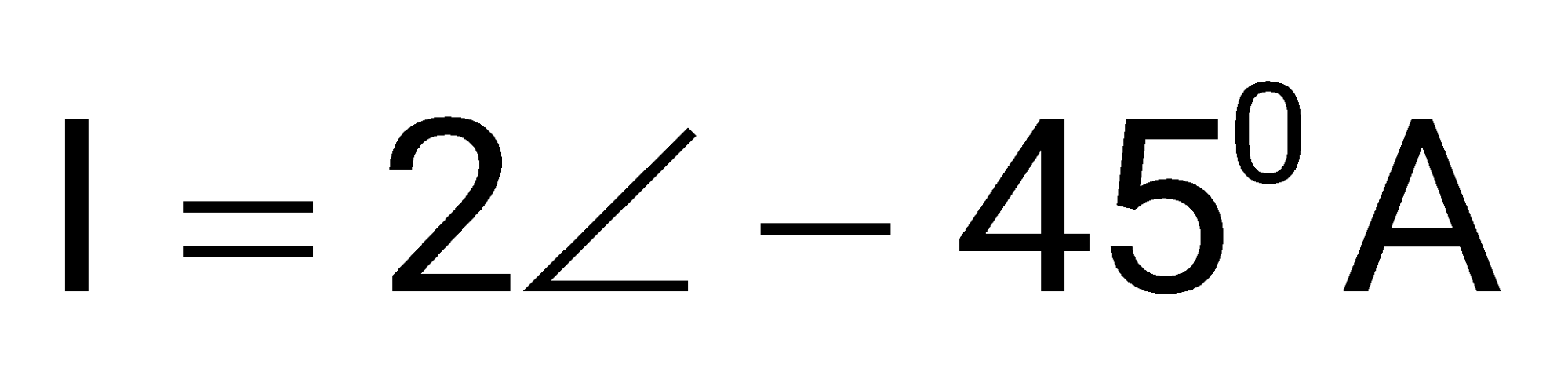

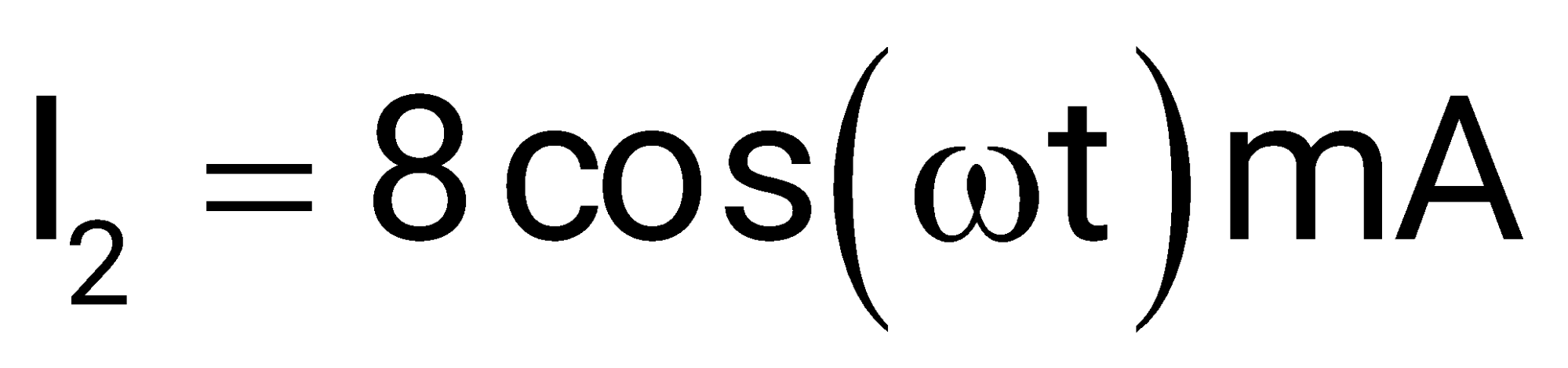

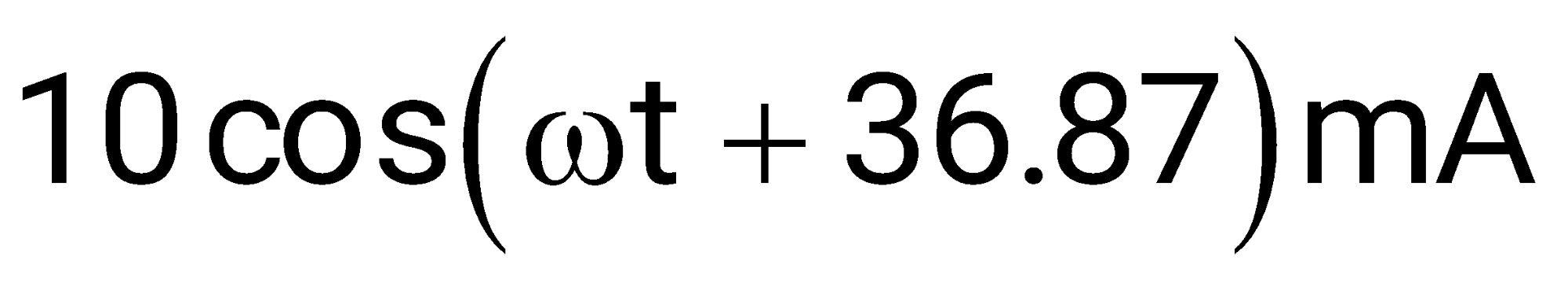

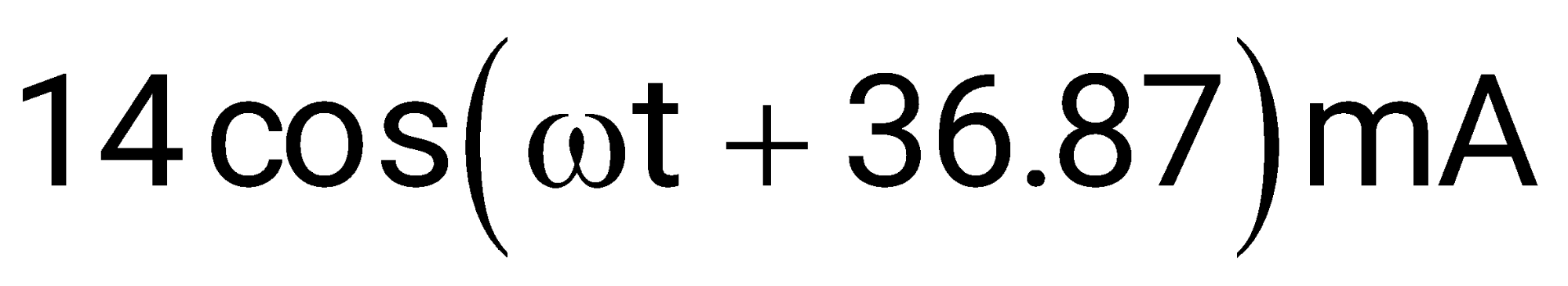

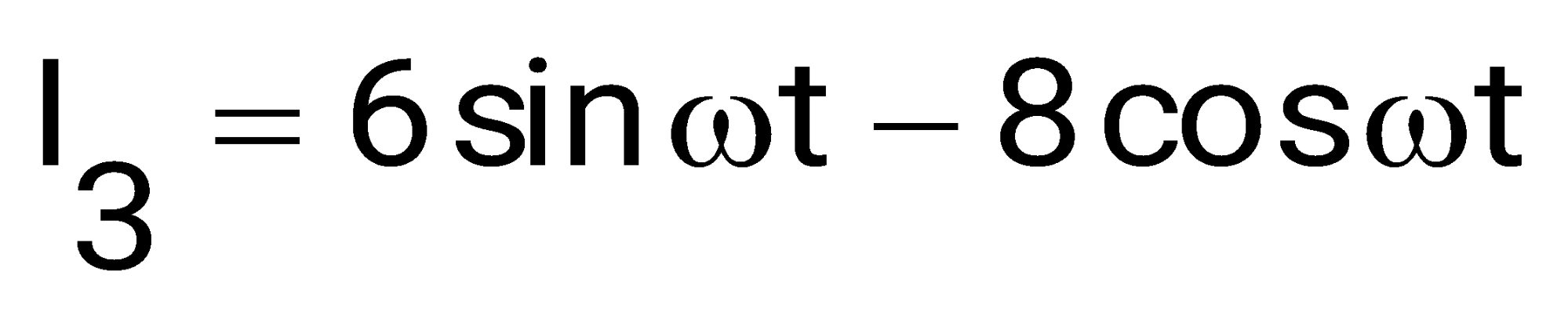

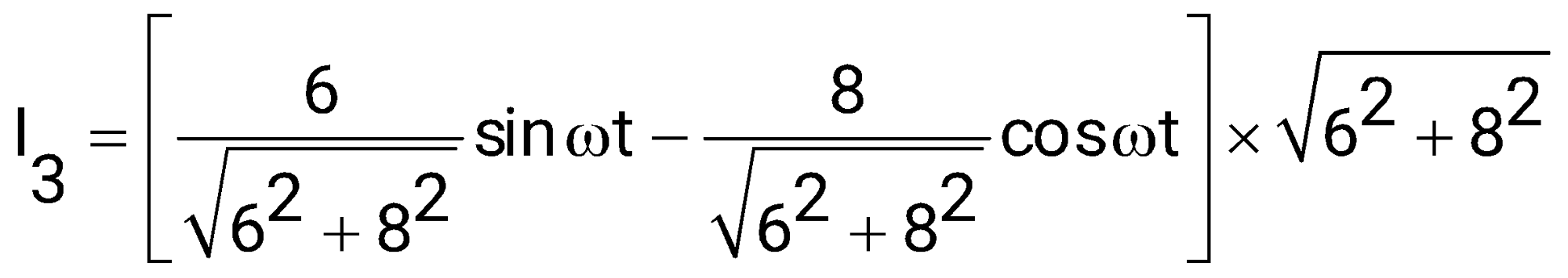

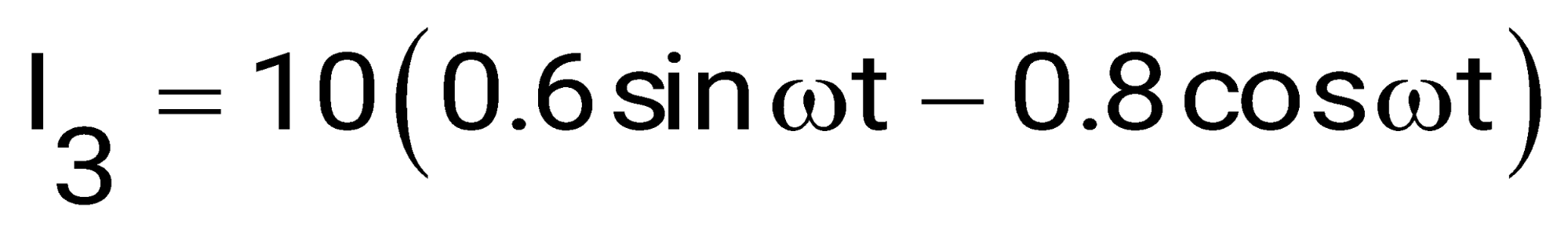

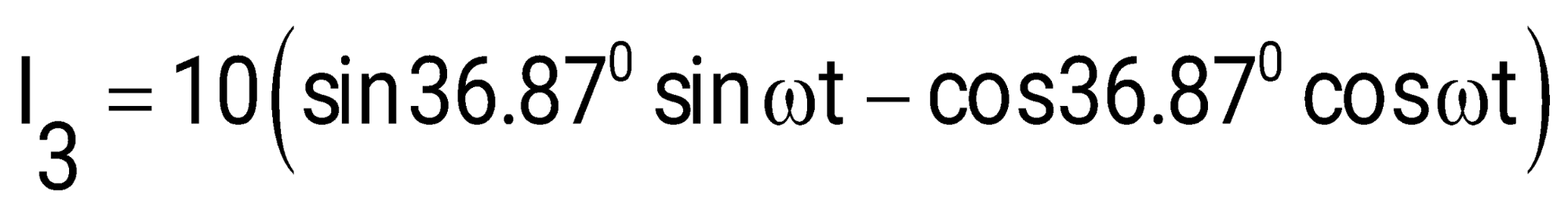

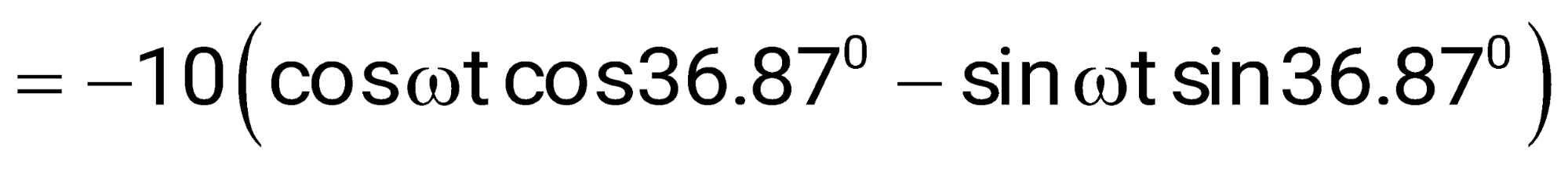

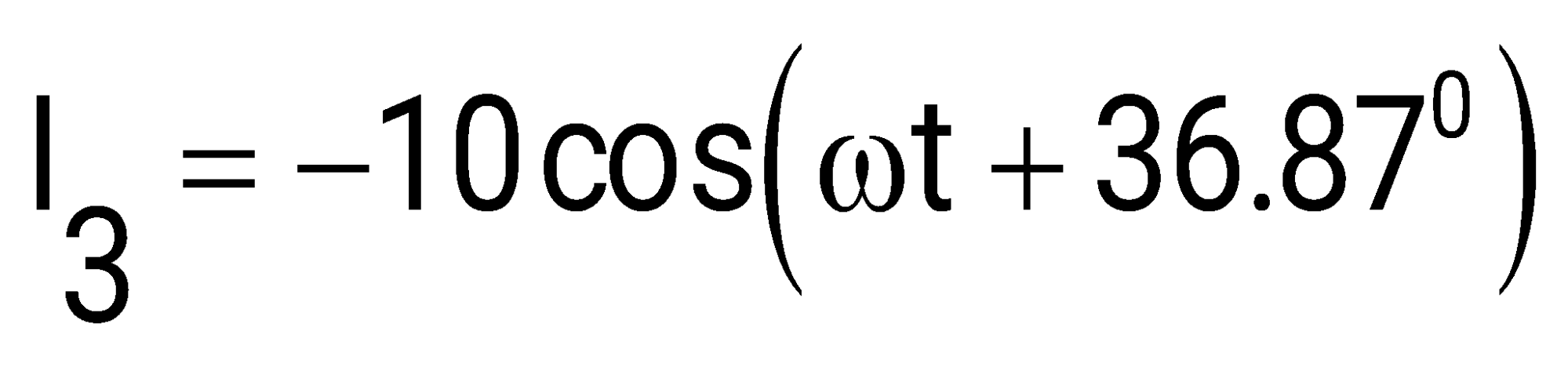

A source is supplying a load through a 2-phase, 3-wire transmission system as shown in figure below. The instantaneous voltage and current in phase-a are V and A, respectively. Similarly for phase-b, the instantaneous voltage and current are A, respectively.

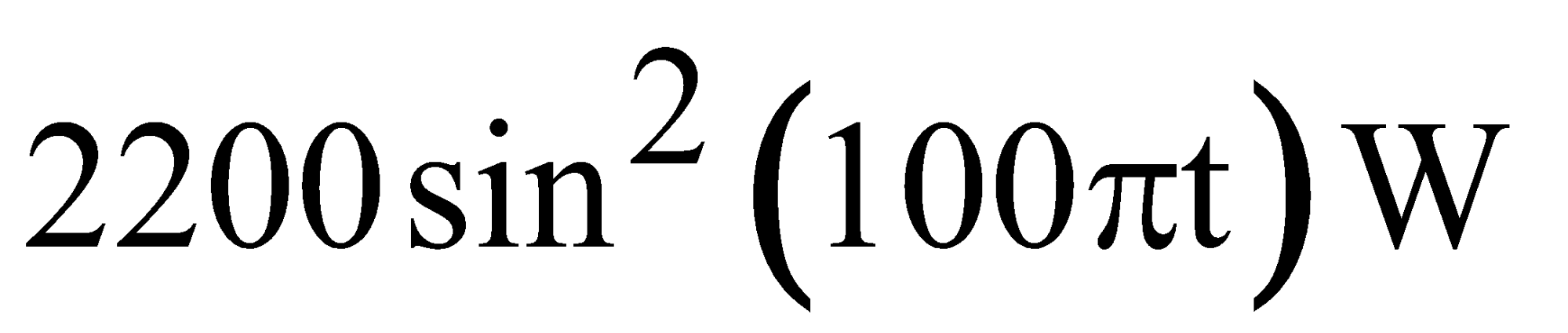

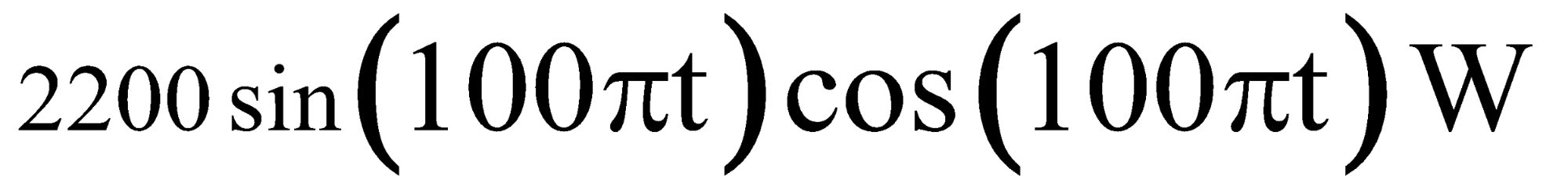

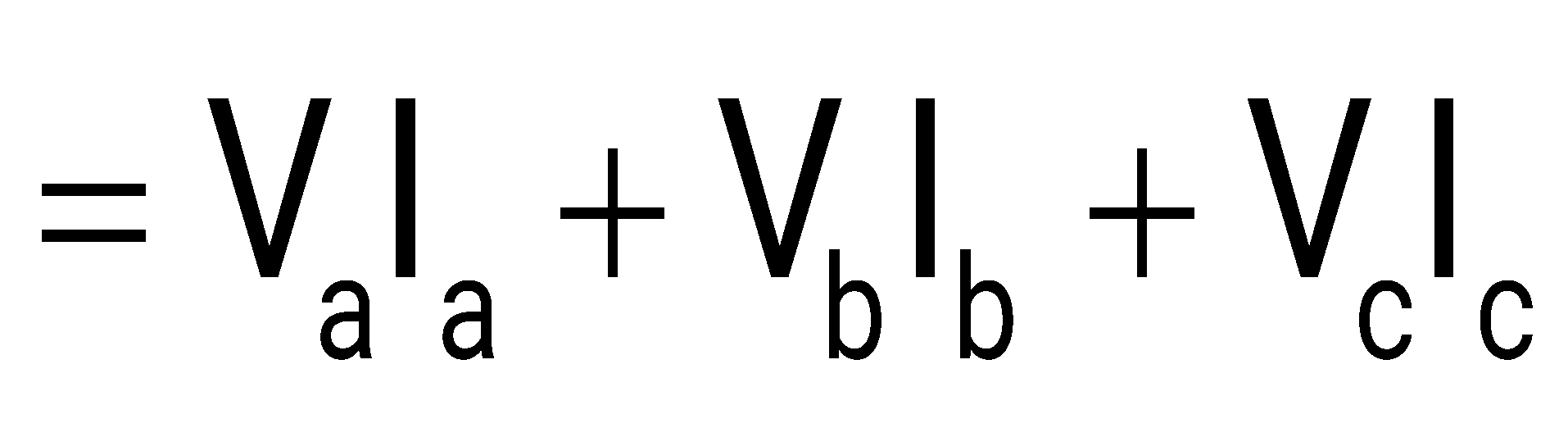

The total instantaneous power flowing from the source to the load is

Total instantaneous power

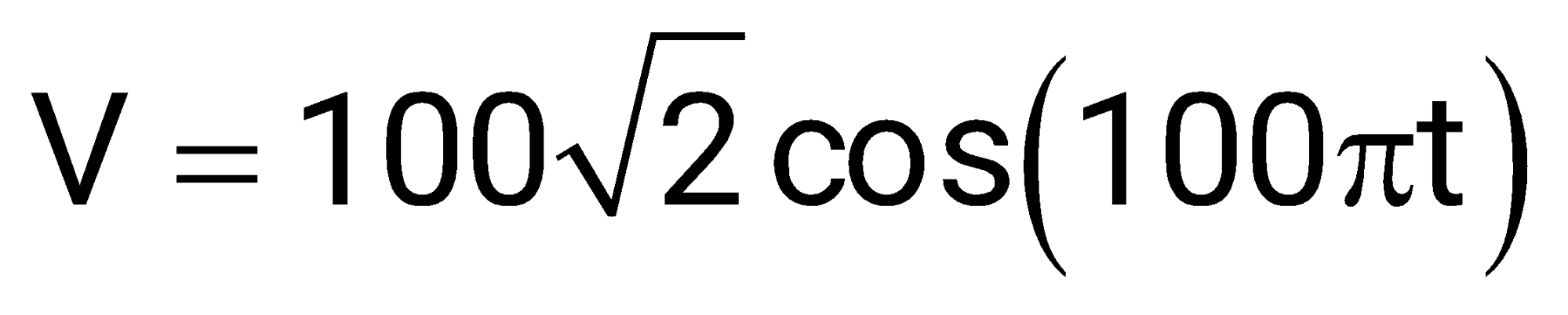

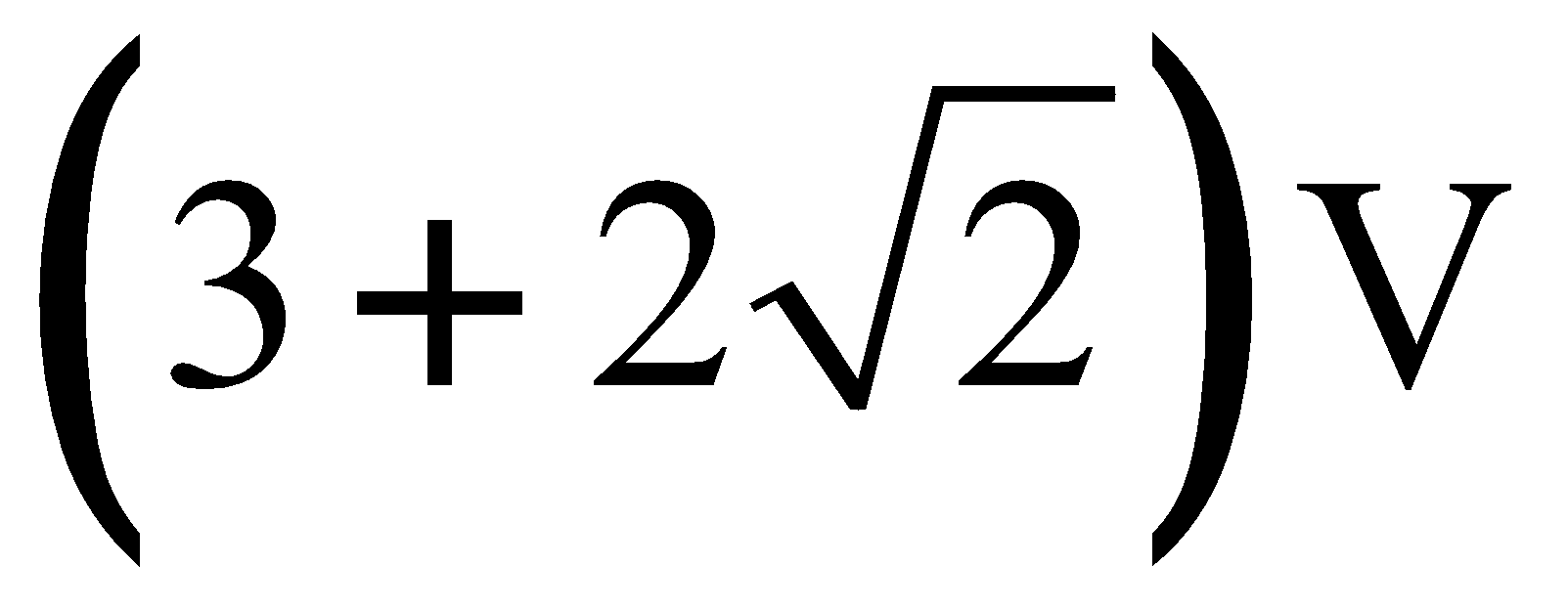

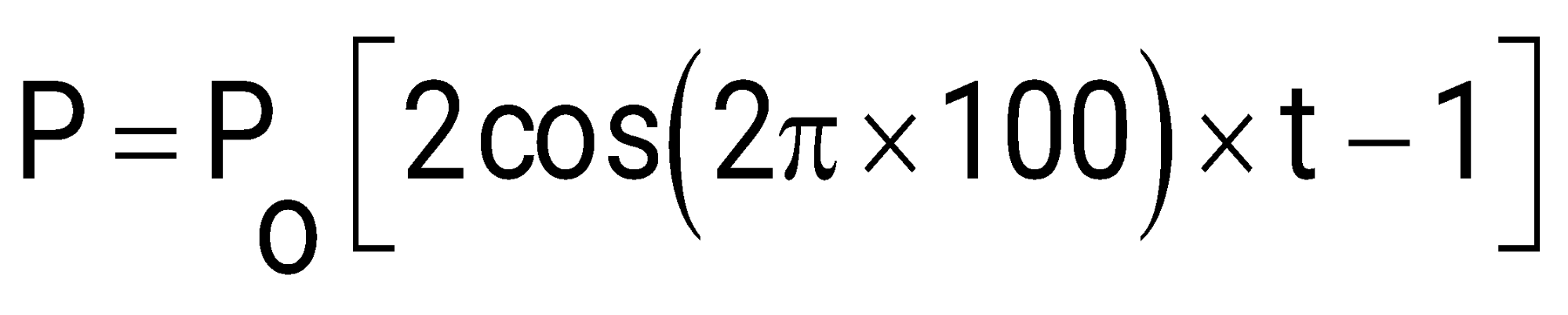

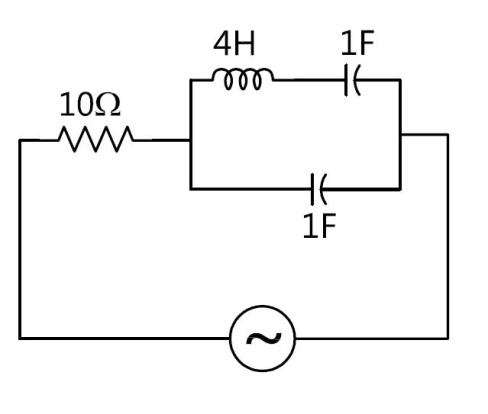

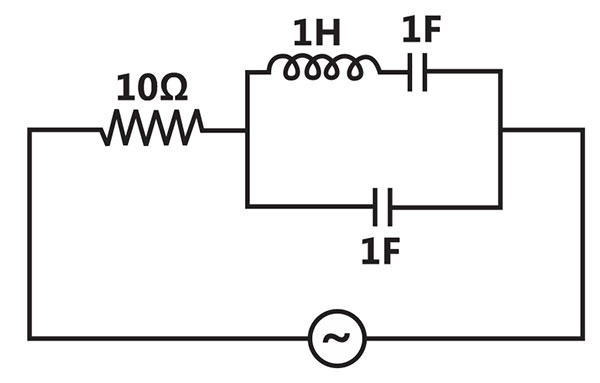

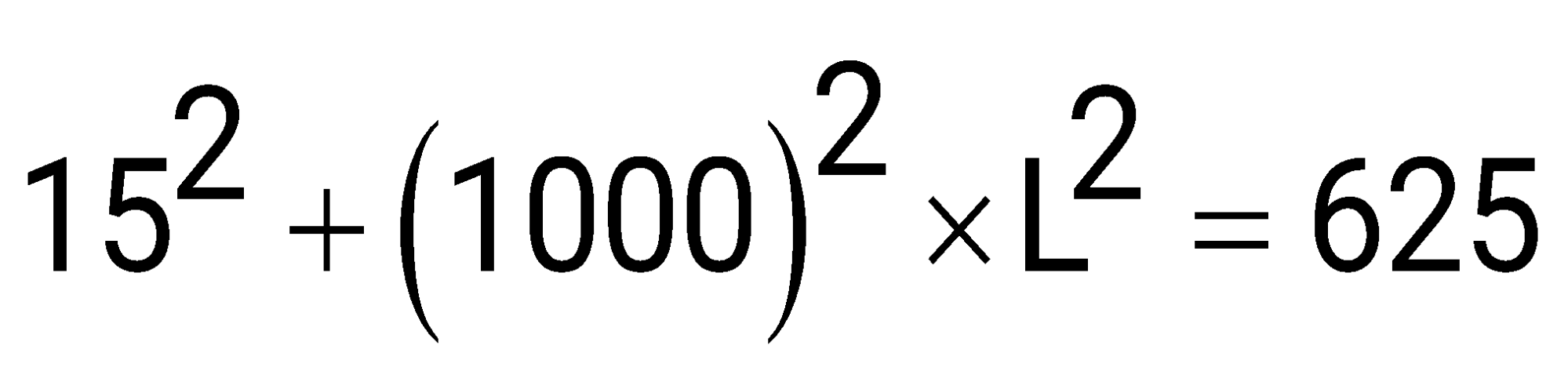

In the circuit shown below, the supply voltage is volts. The peak value of the steady state current through the resistor, in amperes, is _________________.

The given system is shown below with two parallel LC branches marked as A and B.

In branch A:

Resulting parallel combination

In branch B:

Resultant parallel combination

Hence, both branches A and B will act as Open Circuit.

Now, equivalent circuit will be:

Peak value of current through

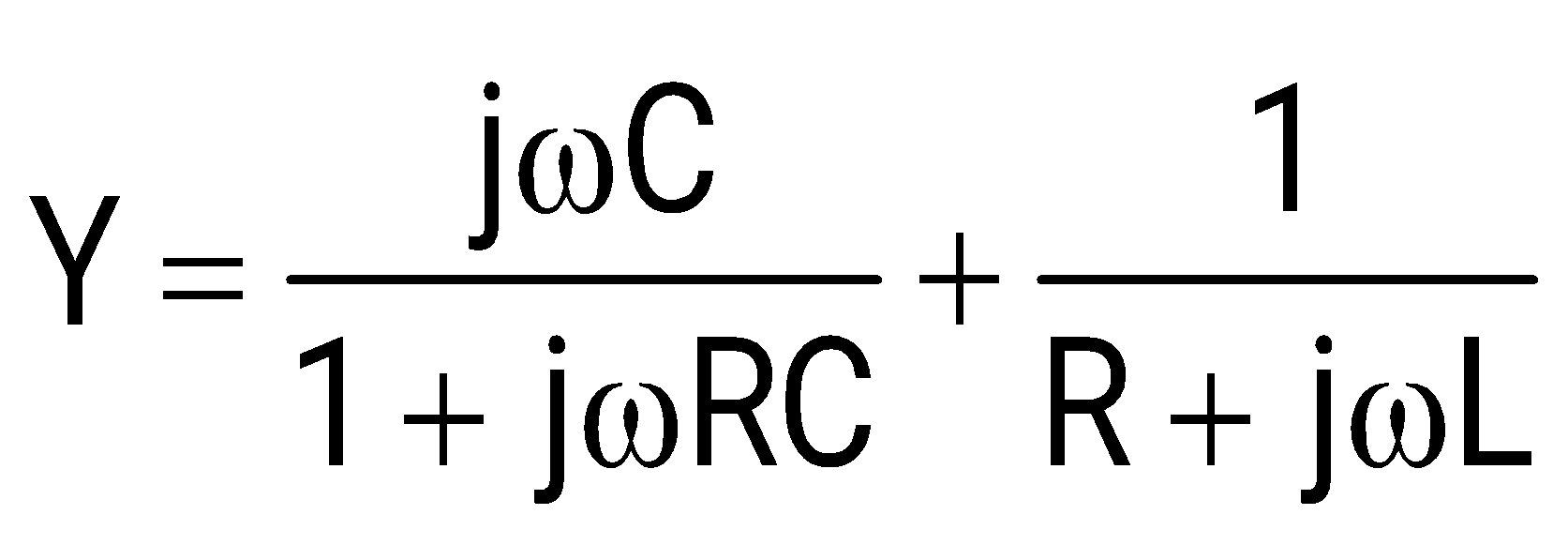

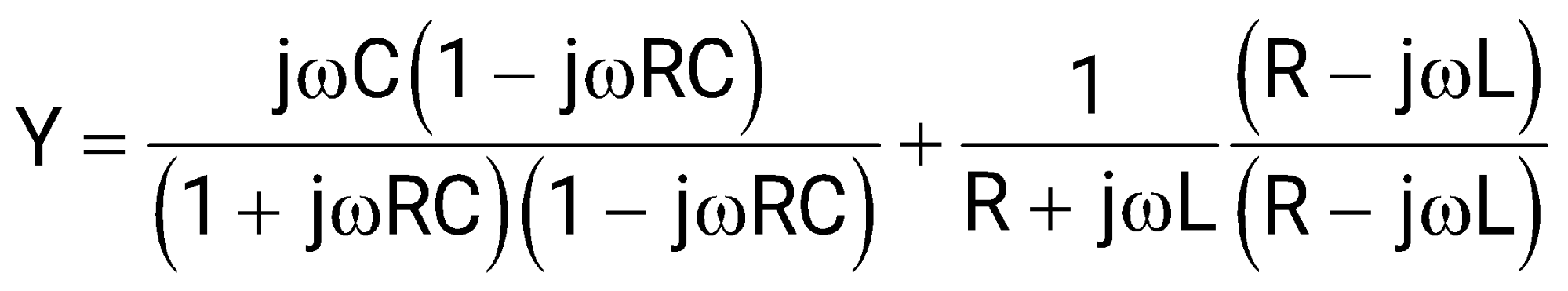

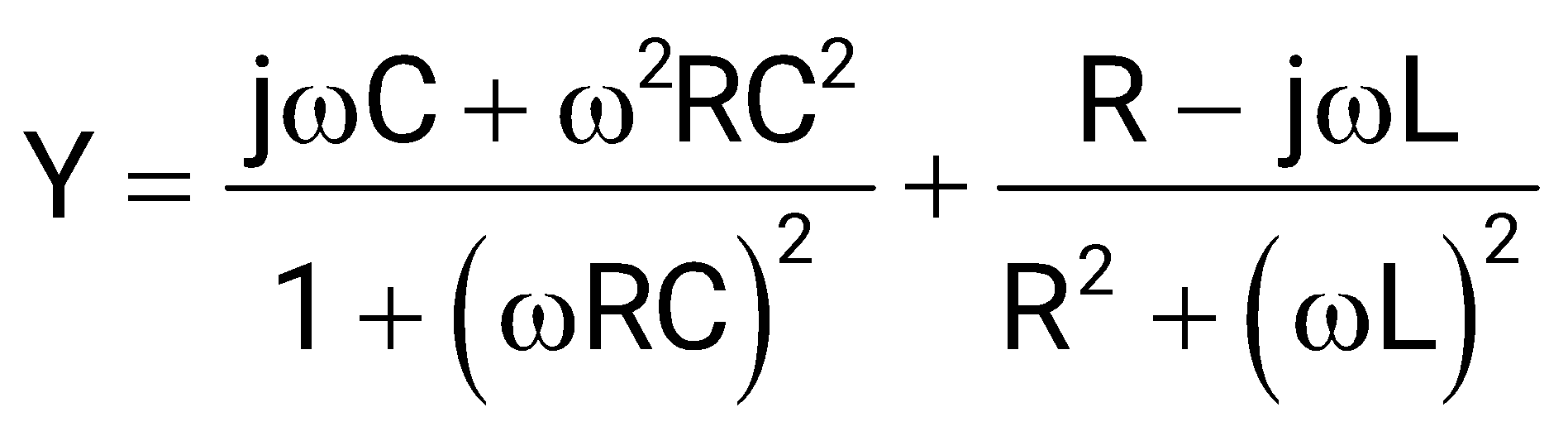

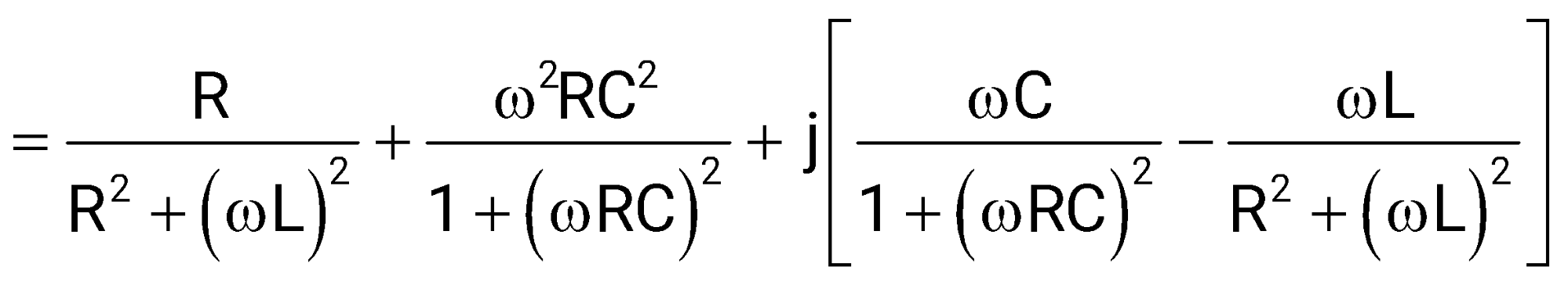

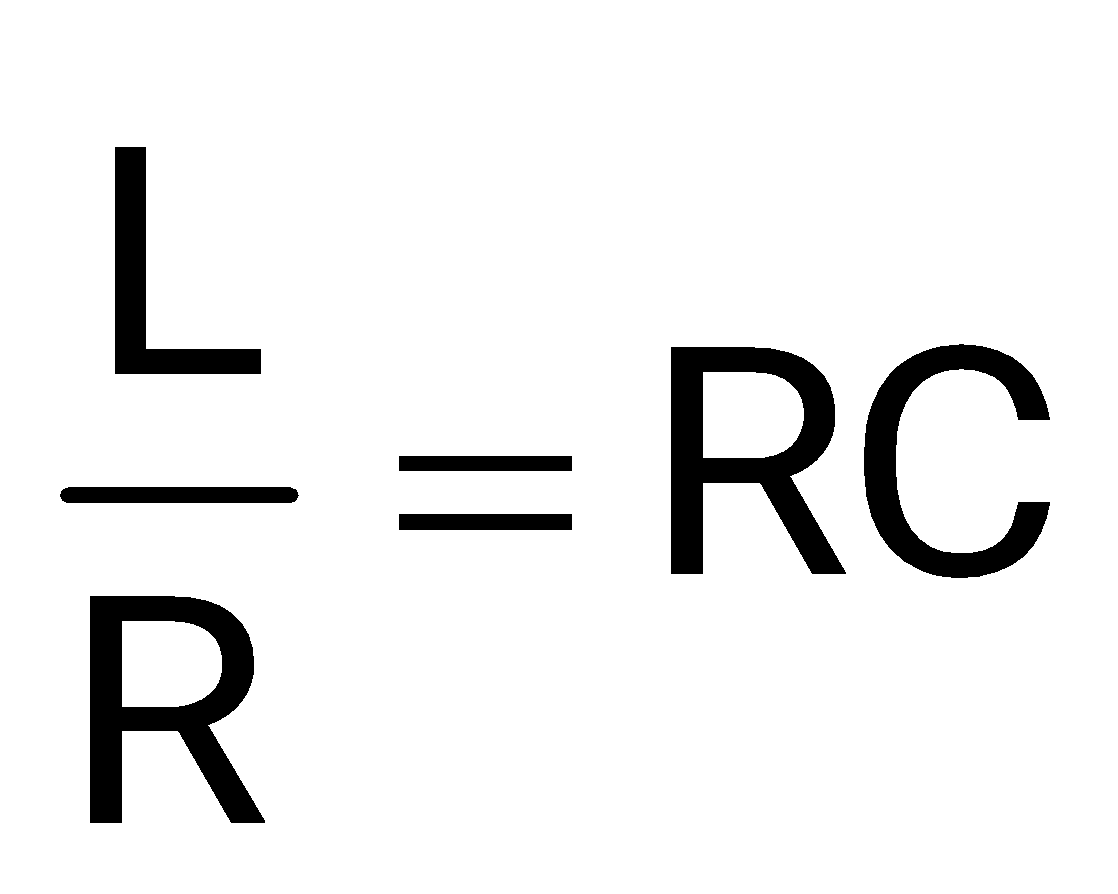

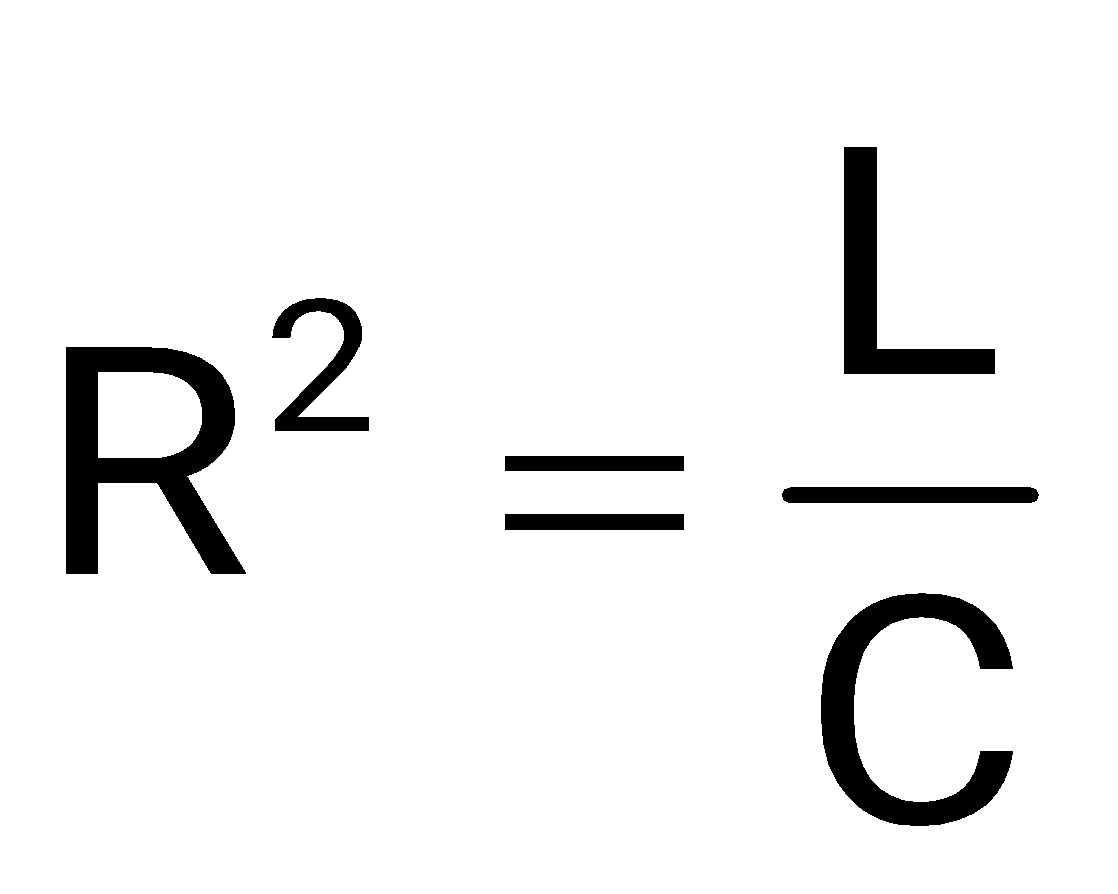

The circuit below is excited by a sinusoidal source. The value of R, in , for which the admittance of the circuit becomes a pure conductance at all frequencies is _____________.

For admittance to have only conductance, imaginary part of admittance should be zero.

For resonance at all frequency is variable, so,

Note: For the circuit to be independent of frequency the time constant of both branches should be equal.

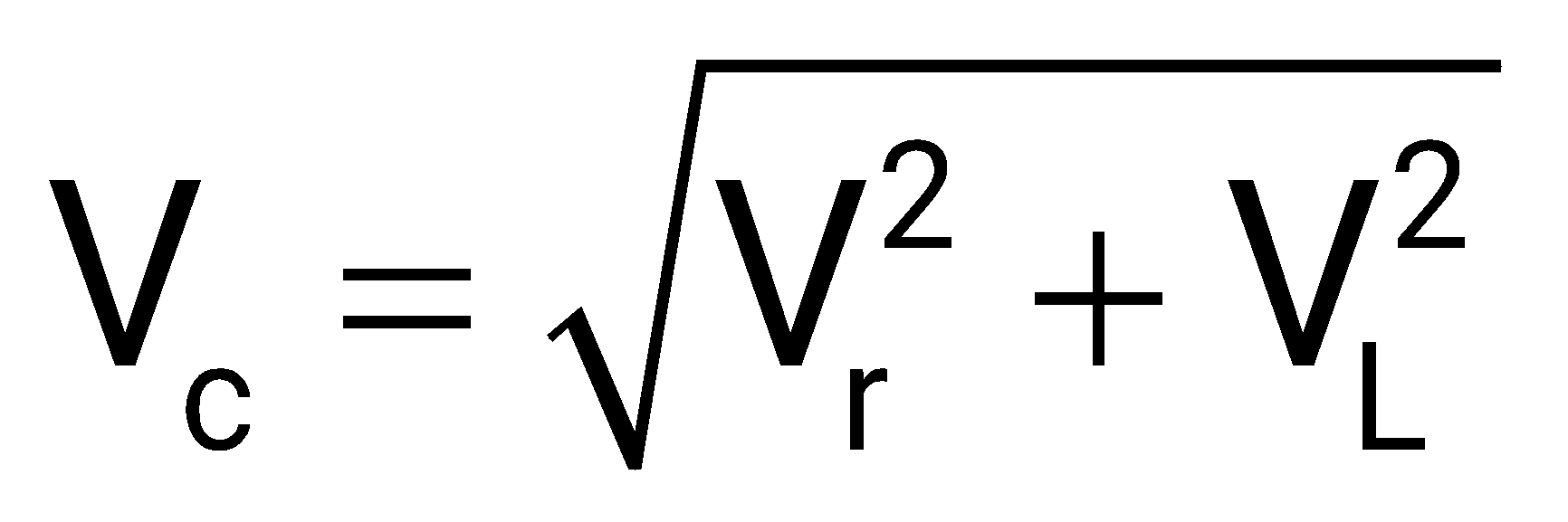

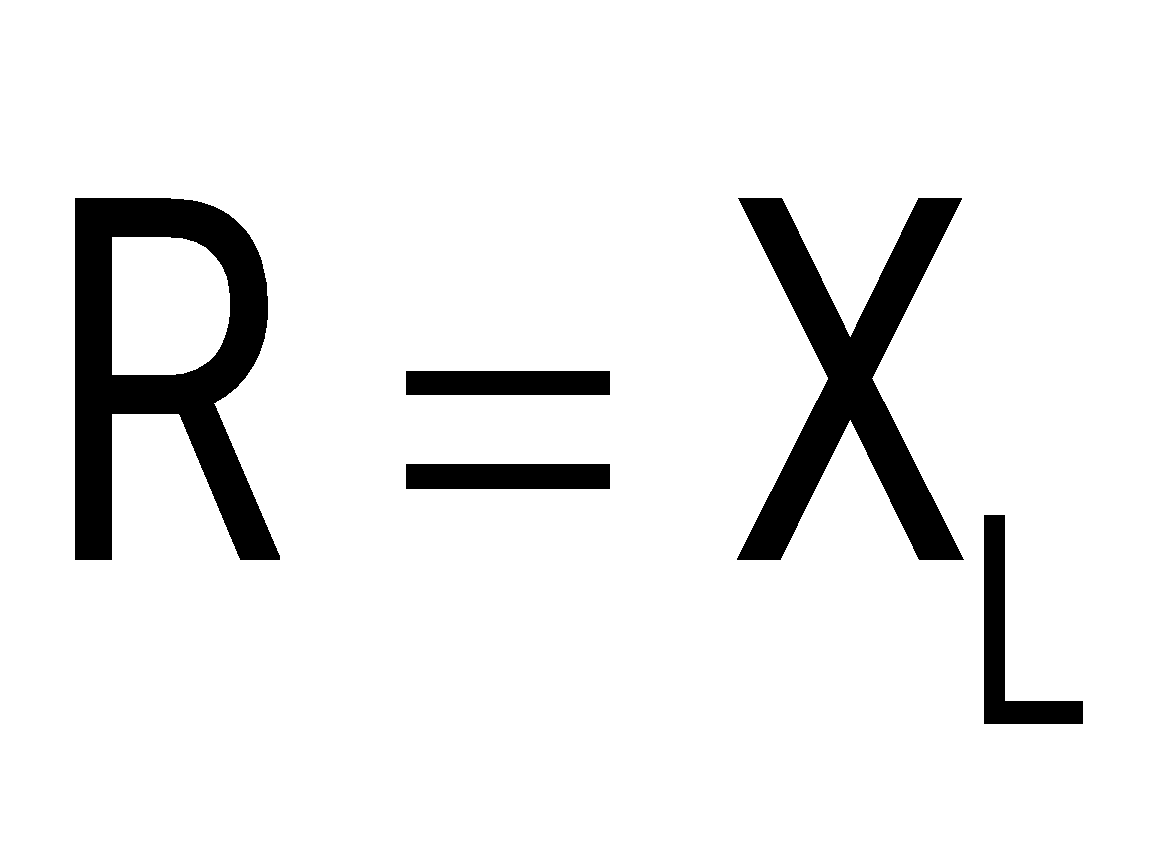

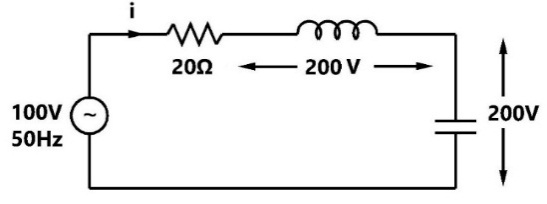

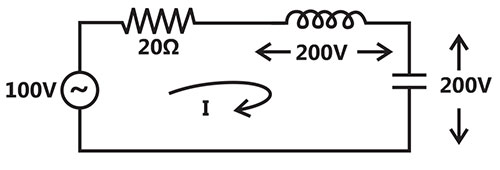

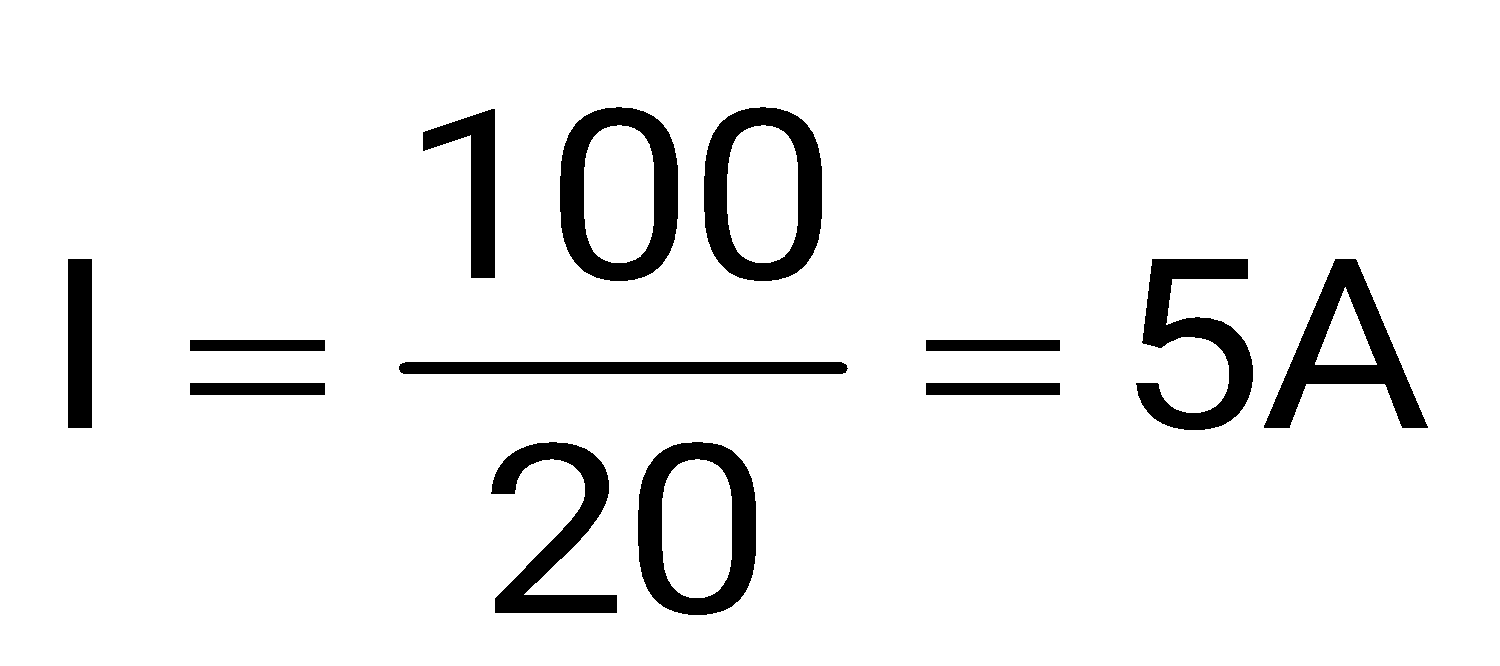

A resistance and a coil connected in series and supplied from a phase, 100V, 50Hz ac source as shown in the figure below. The rms values of possible voltages across the resistance and coil respectively, in volts are

`

Let,

is the voltage across resistance of coil

is the voltage across inductance of coil

Since,

Option A:

Given,

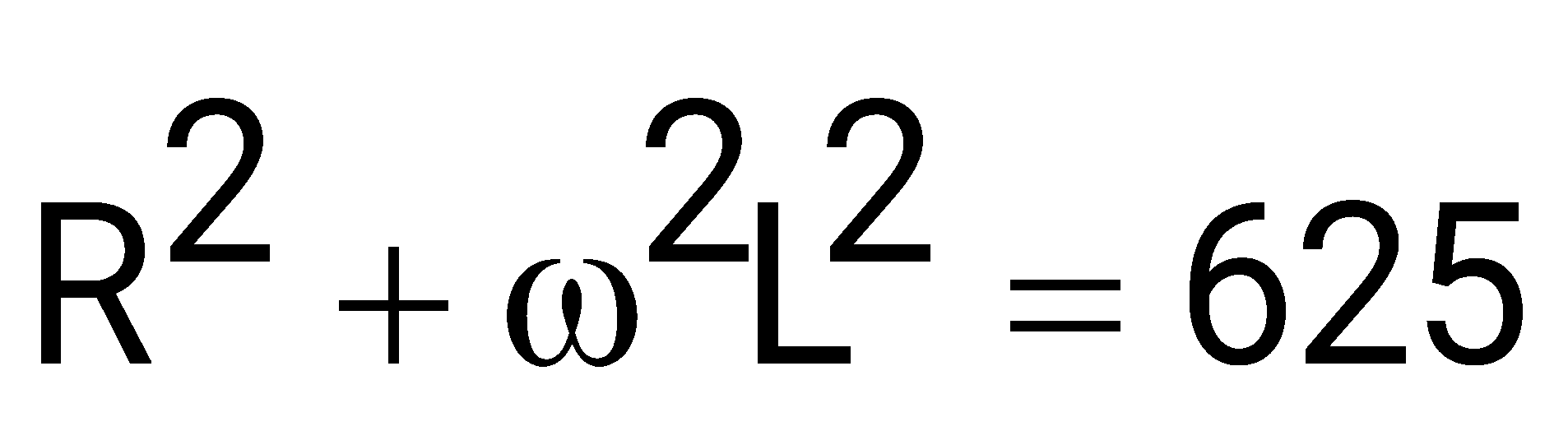

…………….(1)

Applying KVL in loop,

………….…(2)

Putting the values of in equation (2)

Putting this value in equation (1)

This means voltage across inductance = 0

This is not possible and hence option is incorrect.

Option B,

Not possible so option B is also wrong.

Option C:

Putting these values in eq (2)

Voltage across resistance can’t be negative so option C is also wrong.

Option D:

Putting in eqn (2)

This is only possible when coil is ideal but in question coil is not ideal, so this is also wrong.

Note: There is something wrong in the question and marks to all were given in this question by the GATE committee.

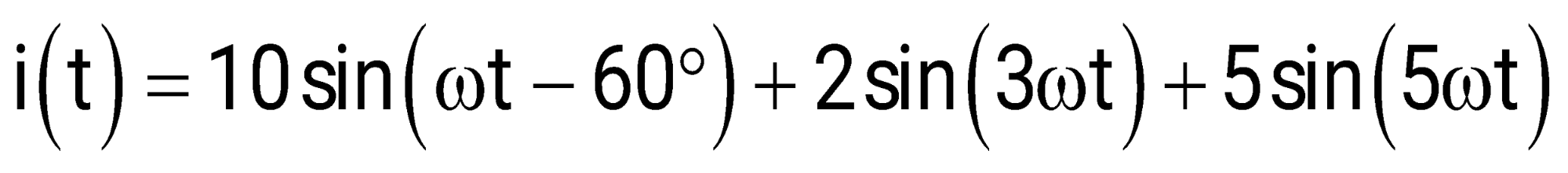

The voltage (V) and current ((A) across a load are as follows.

.

.

The average power consumed by the load, in W, is_____________.

Current have several frequency components but voltage has only one frequency component. Average power will be due to only same frequency components.

W

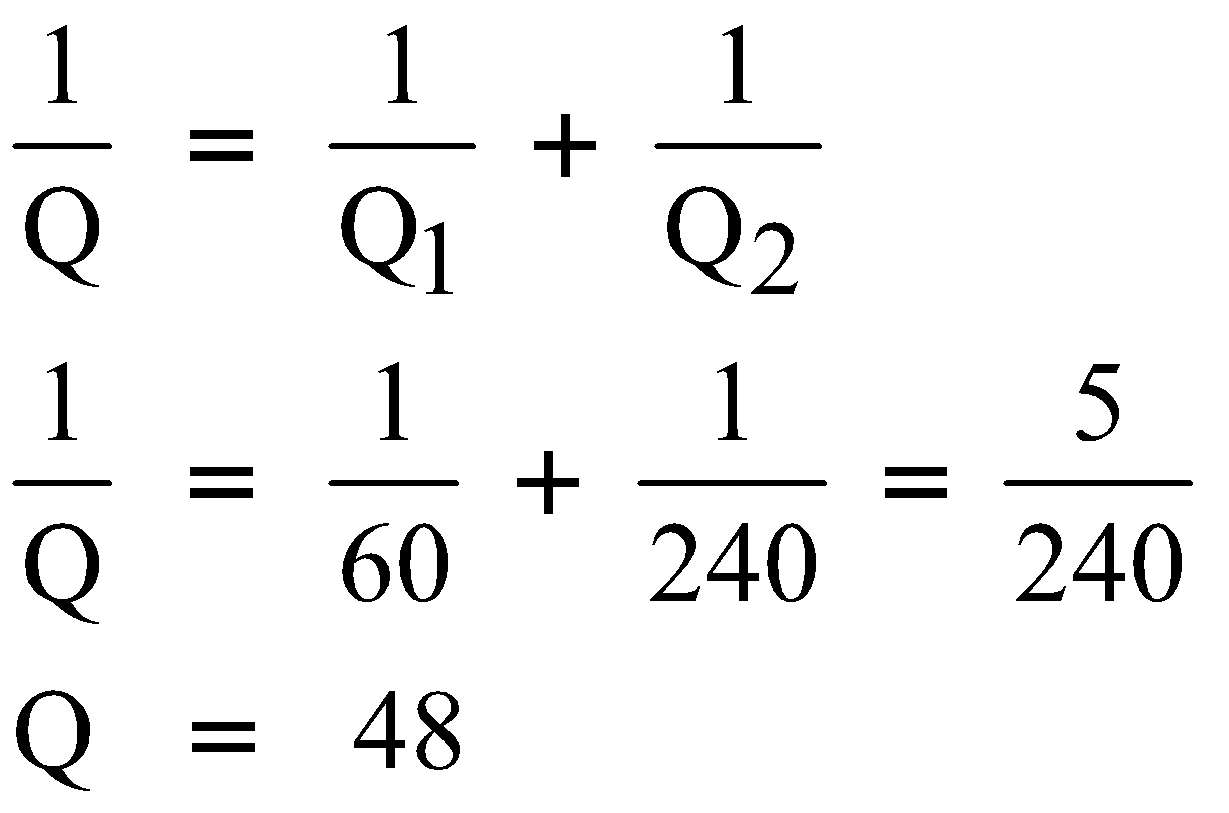

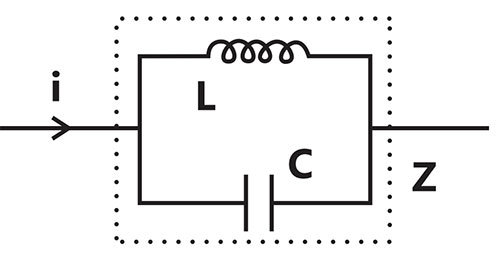

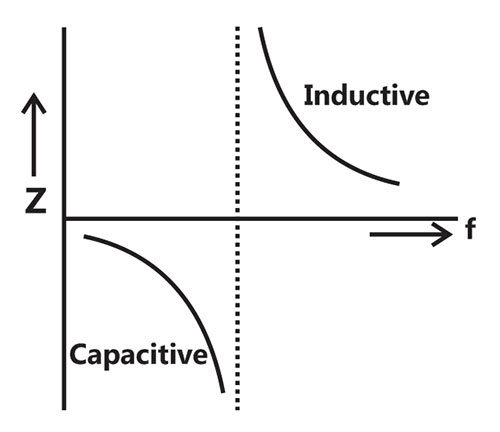

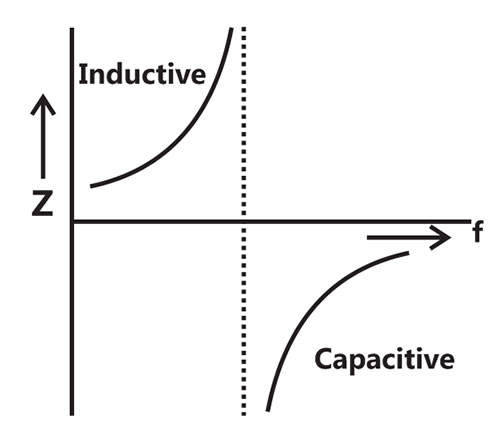

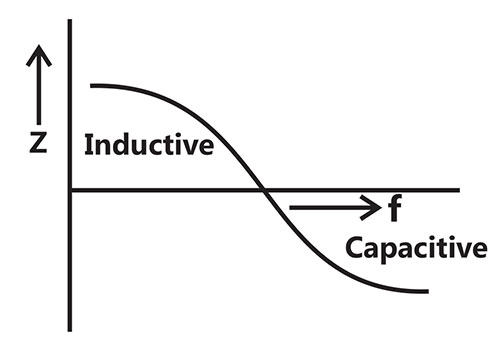

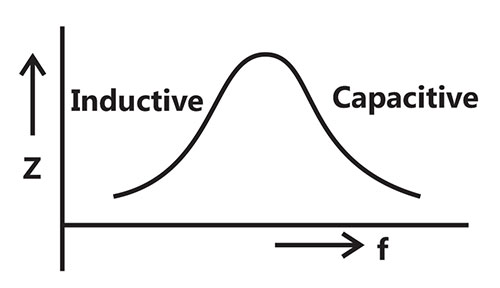

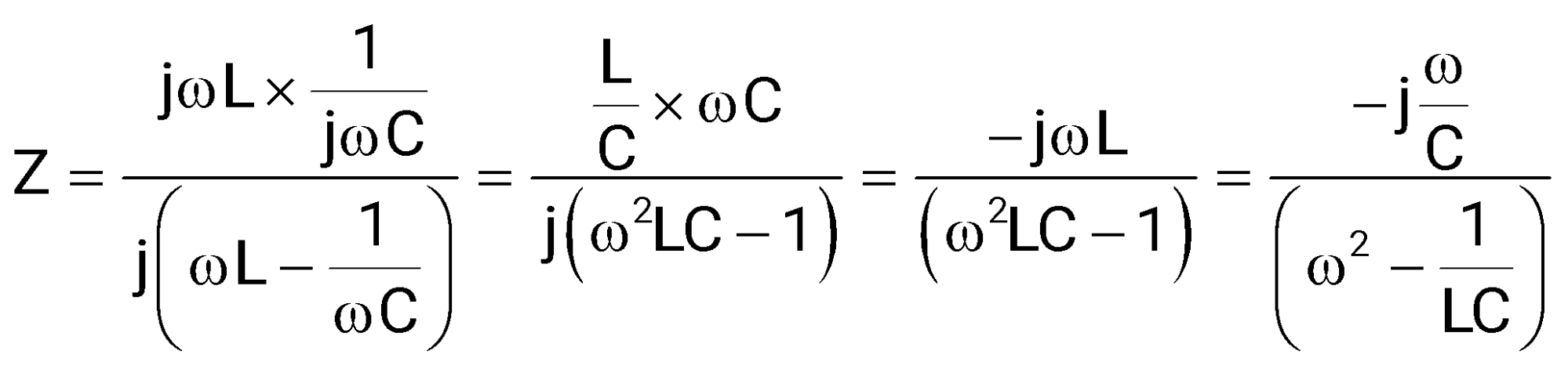

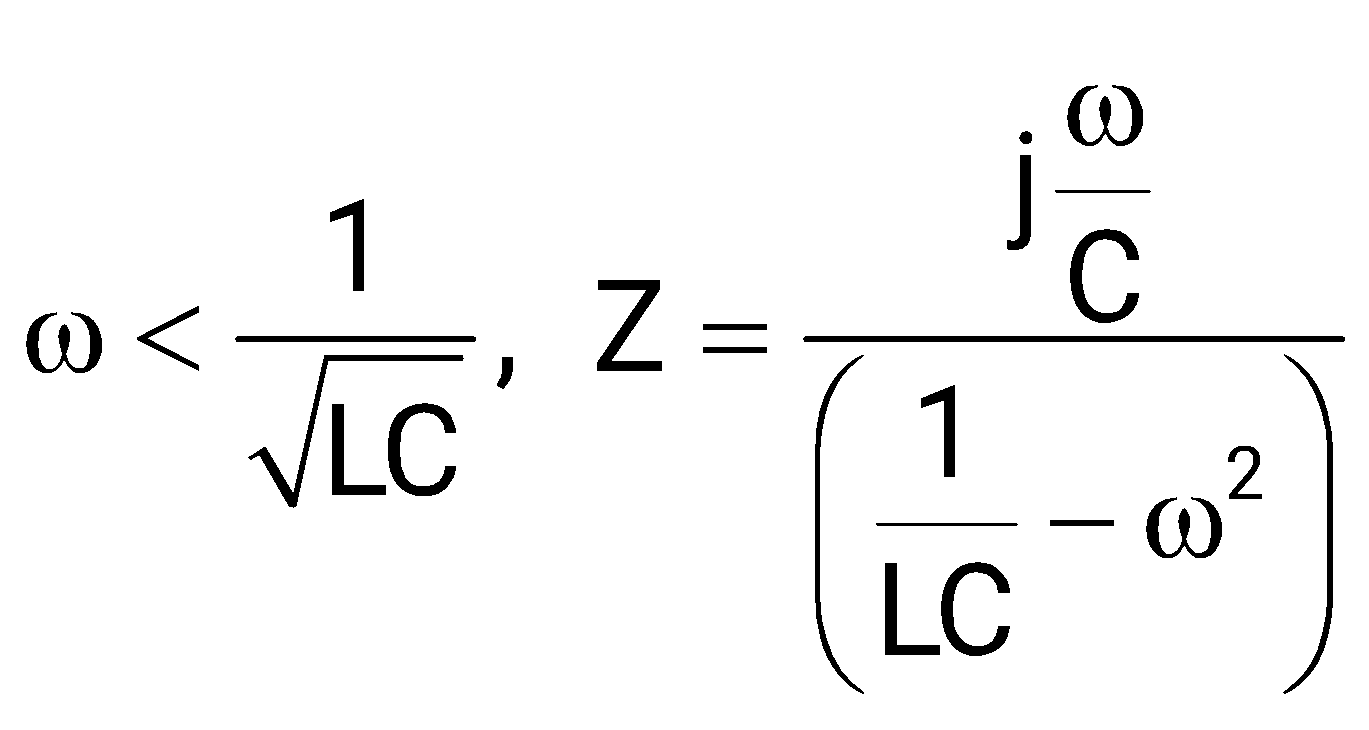

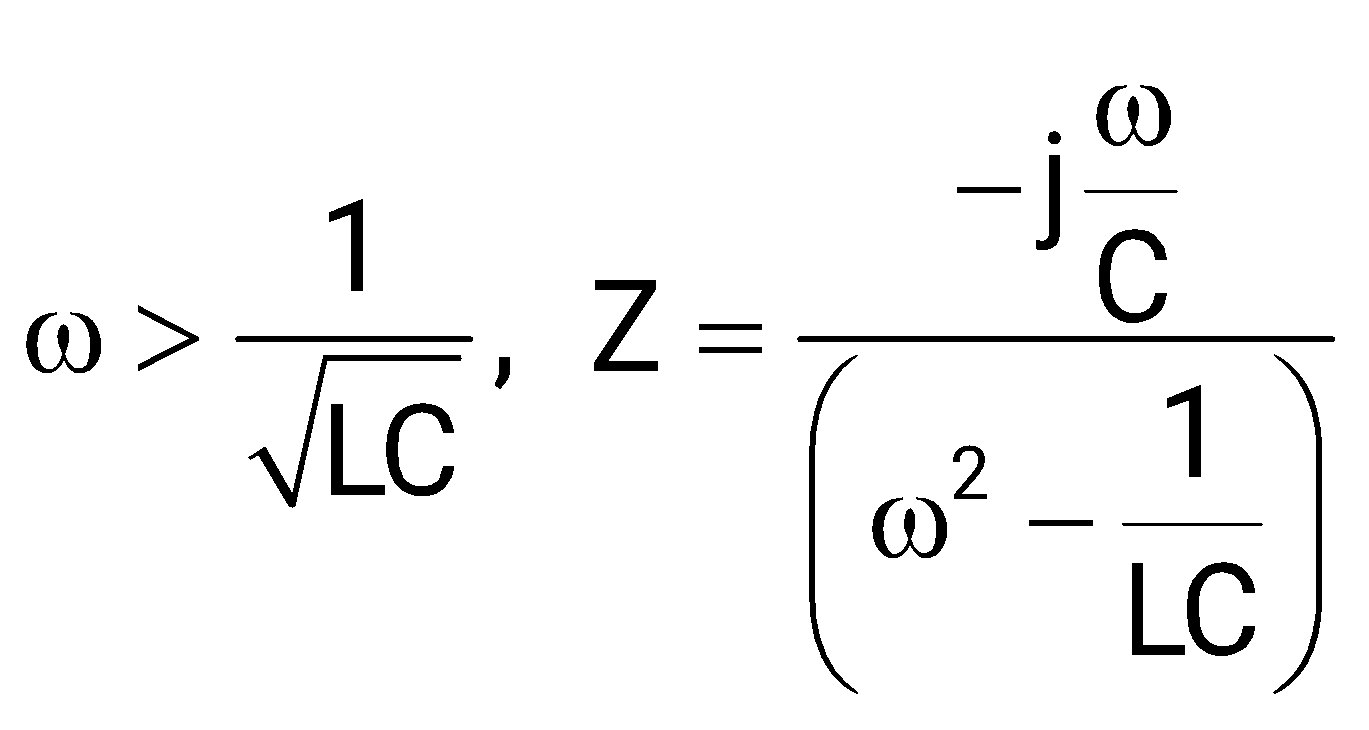

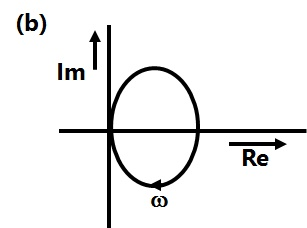

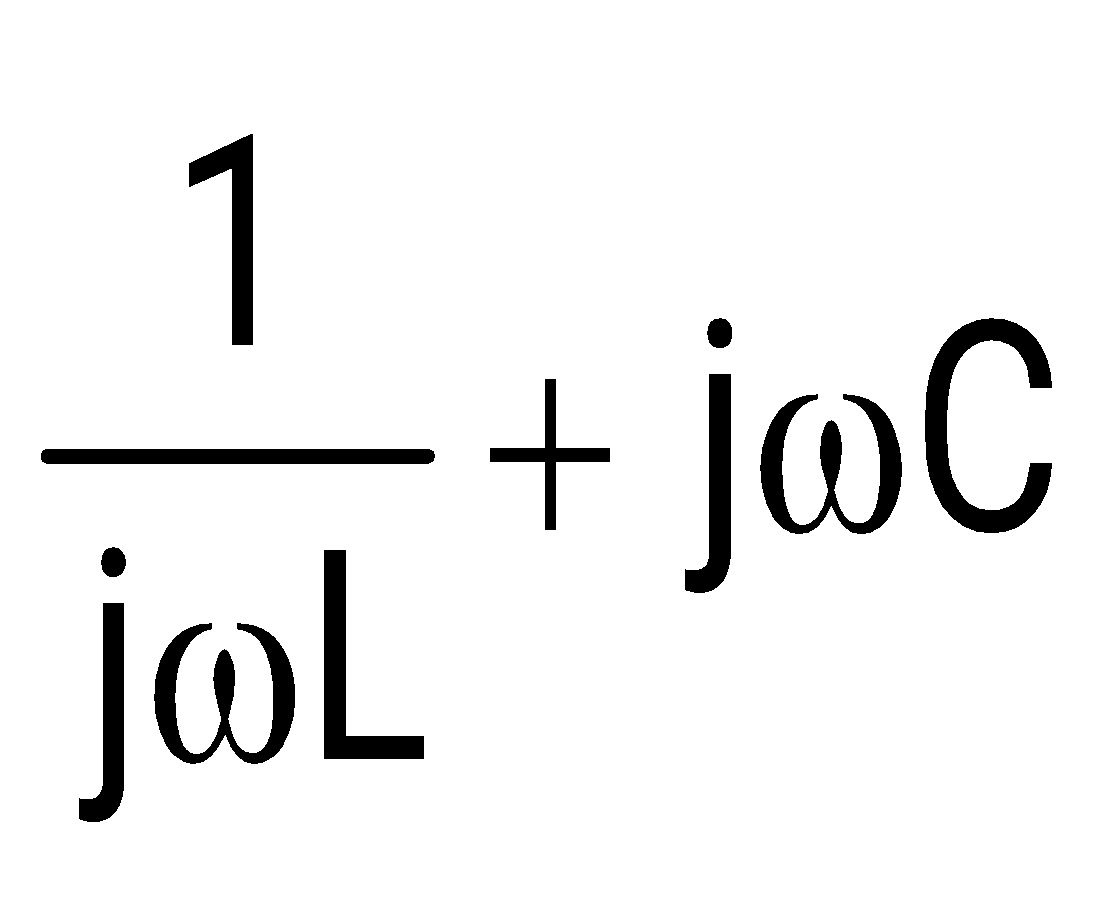

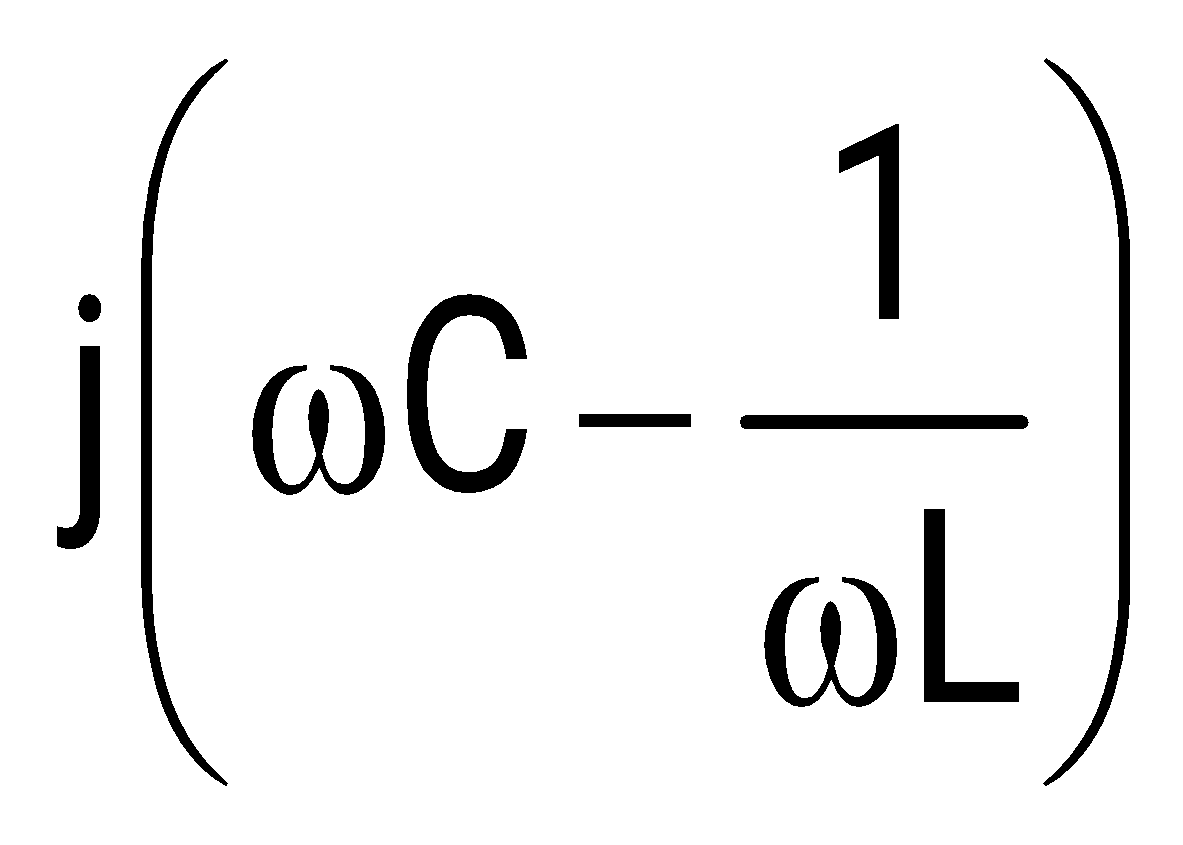

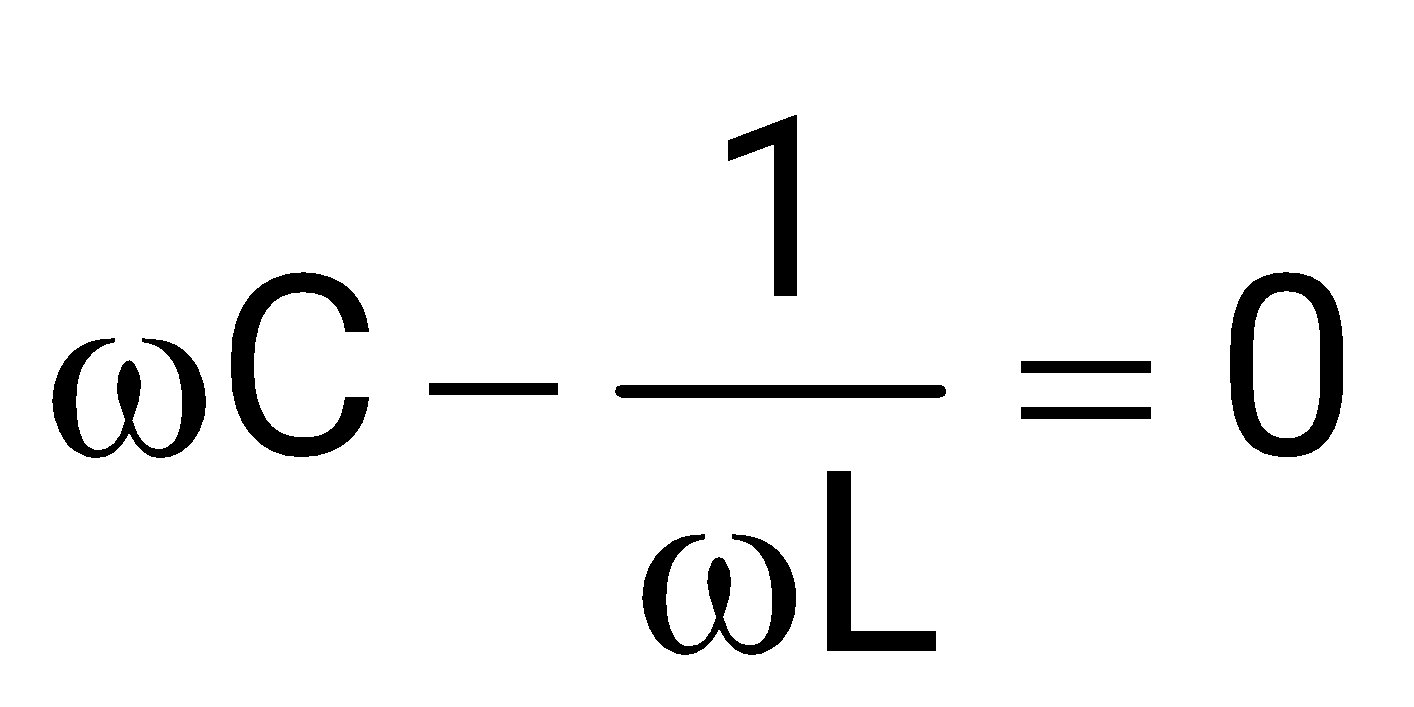

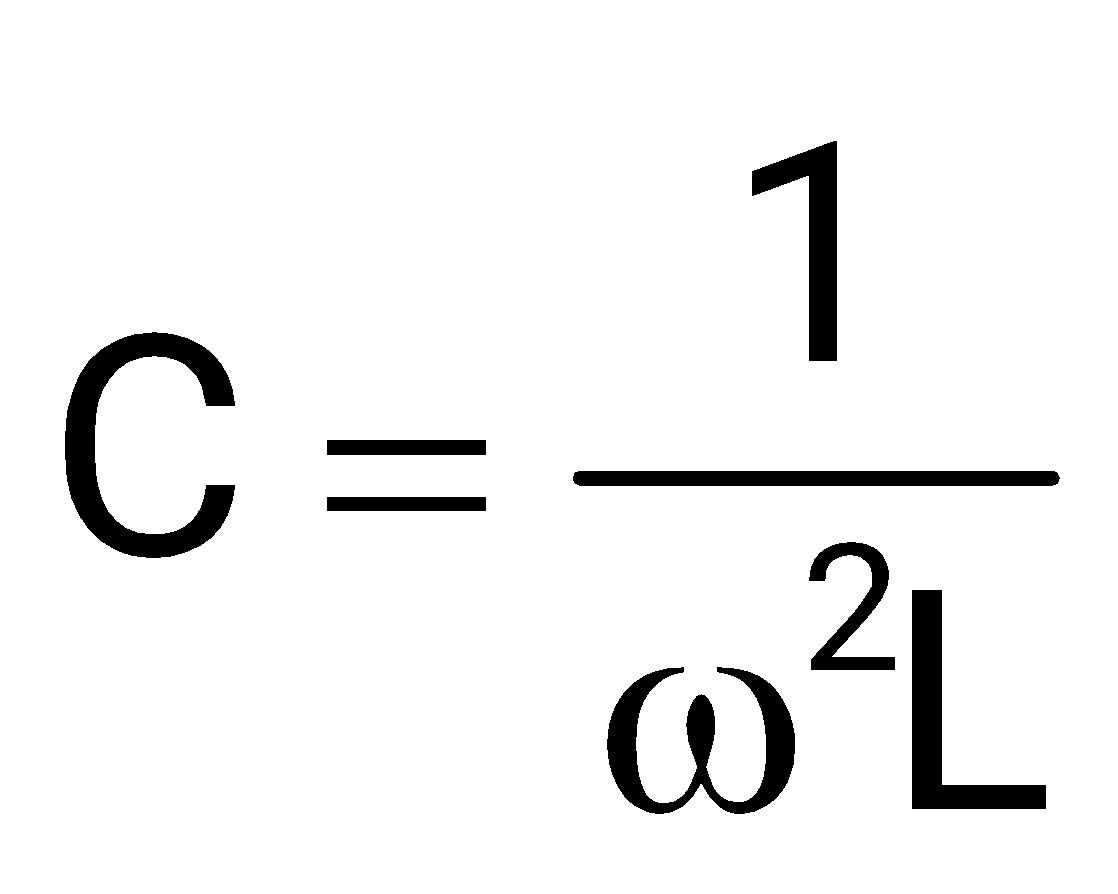

An inductor is connected in parallel with a capacitor as shown in the figure.

As the frequency of current i is increased, the impedance (Z) of the network varies as

Equivalent Impedance of Parallel RC circuit shown below is,

When (inductive)

When (capacitive)

At , impedance goes to infinity as the net admittance goes to zero. Hence, the plot of impedance versus frequency is shown below,

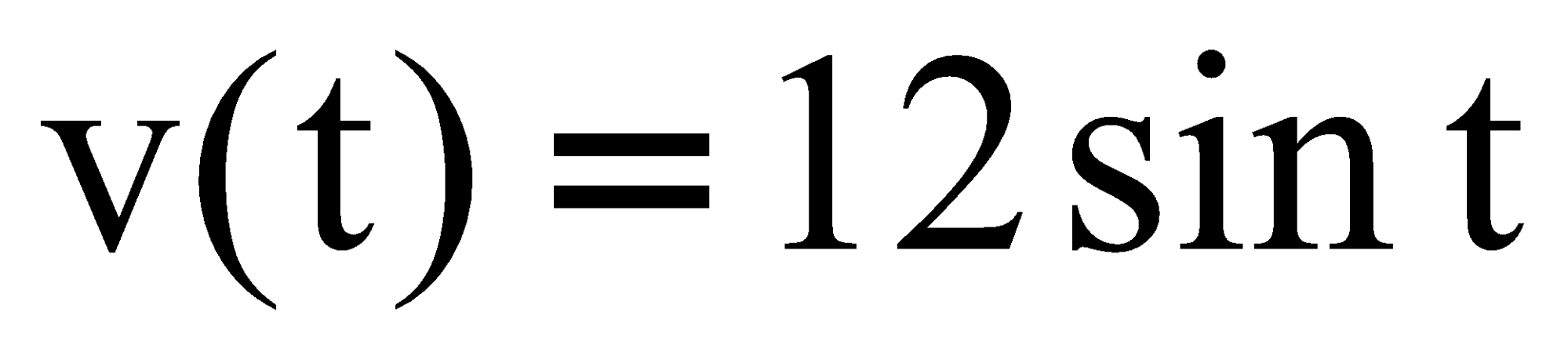

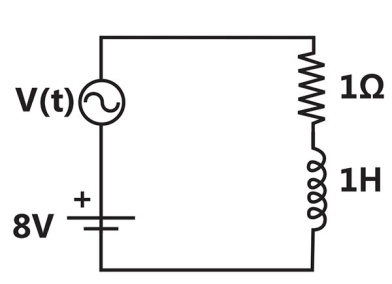

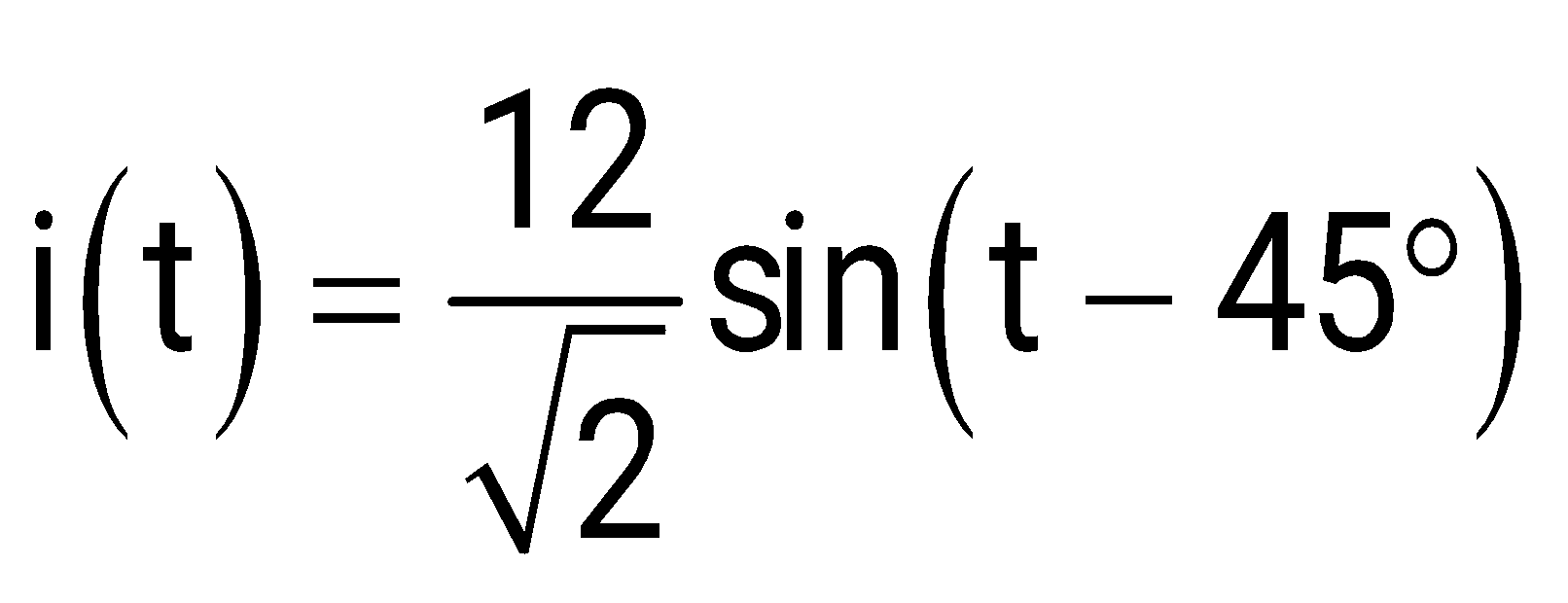

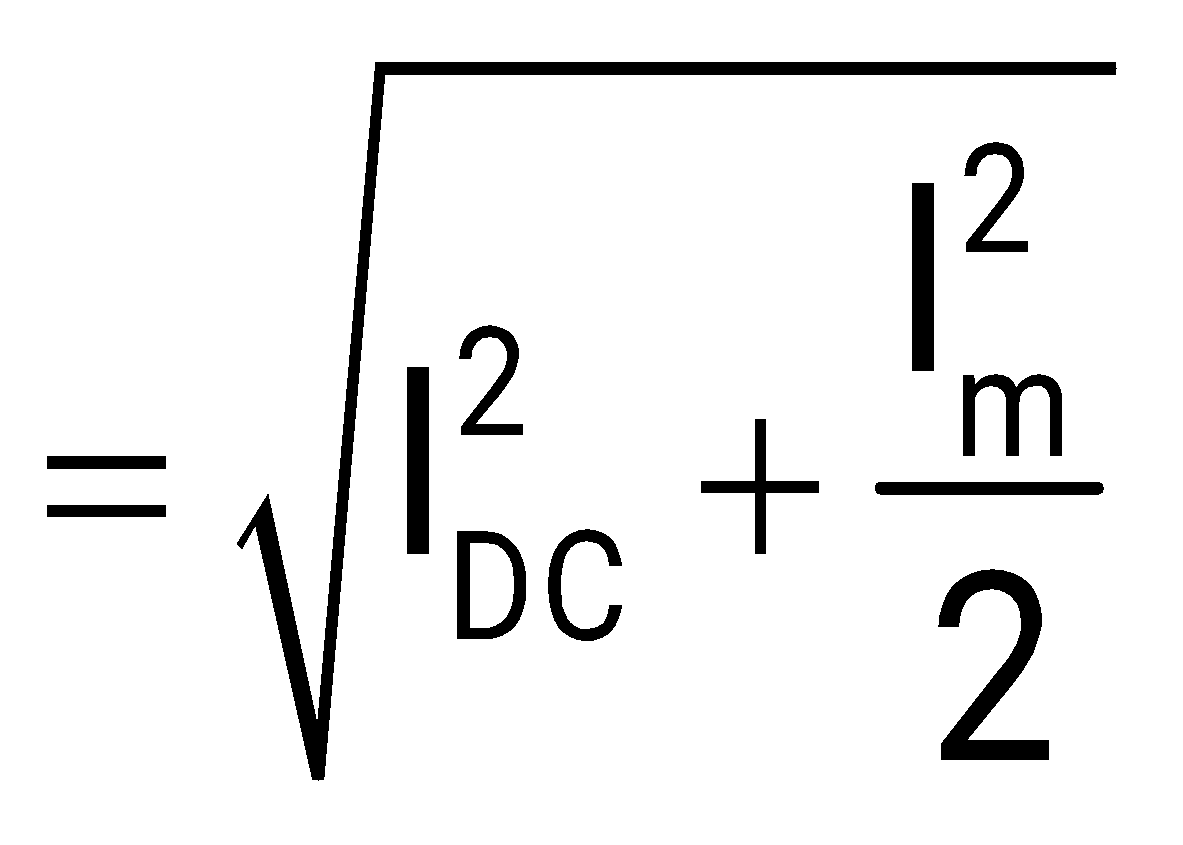

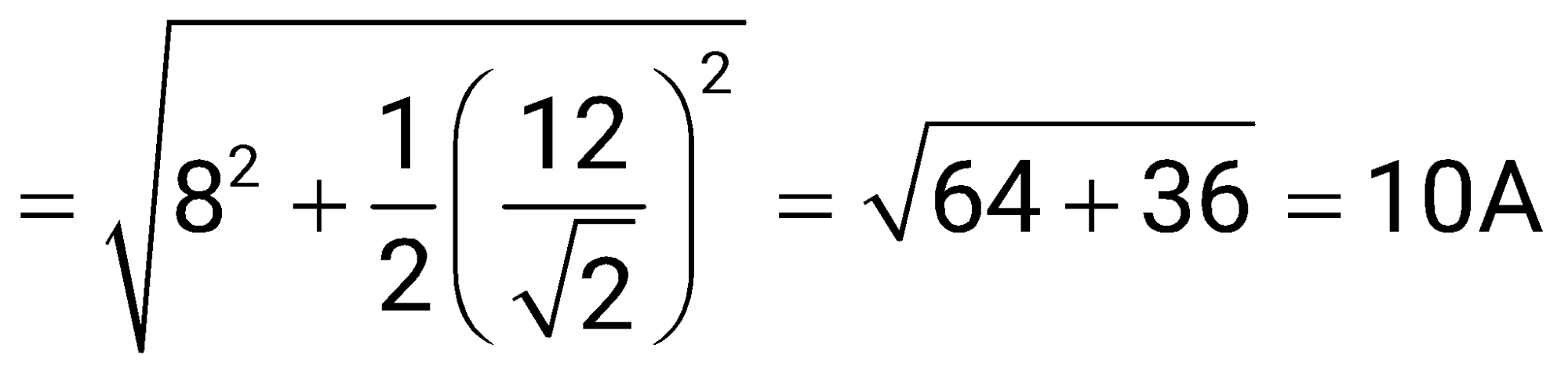

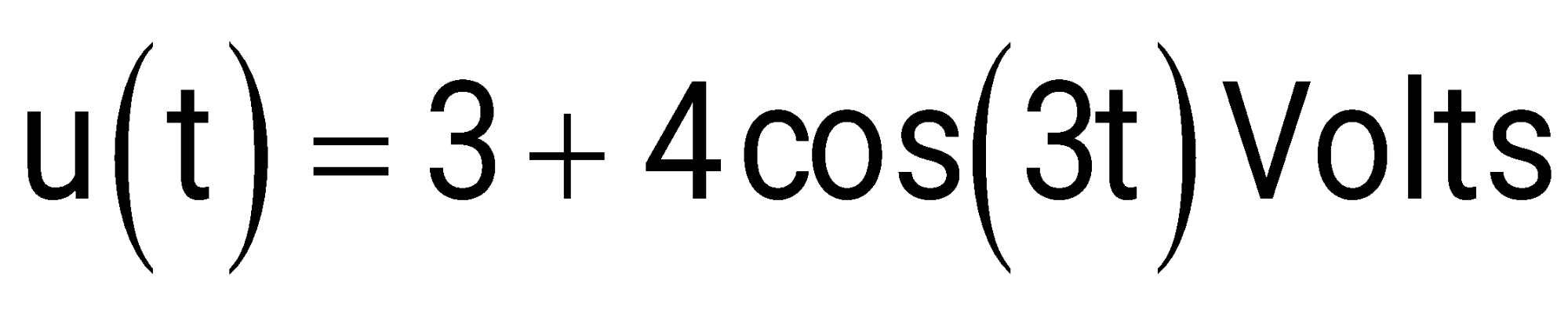

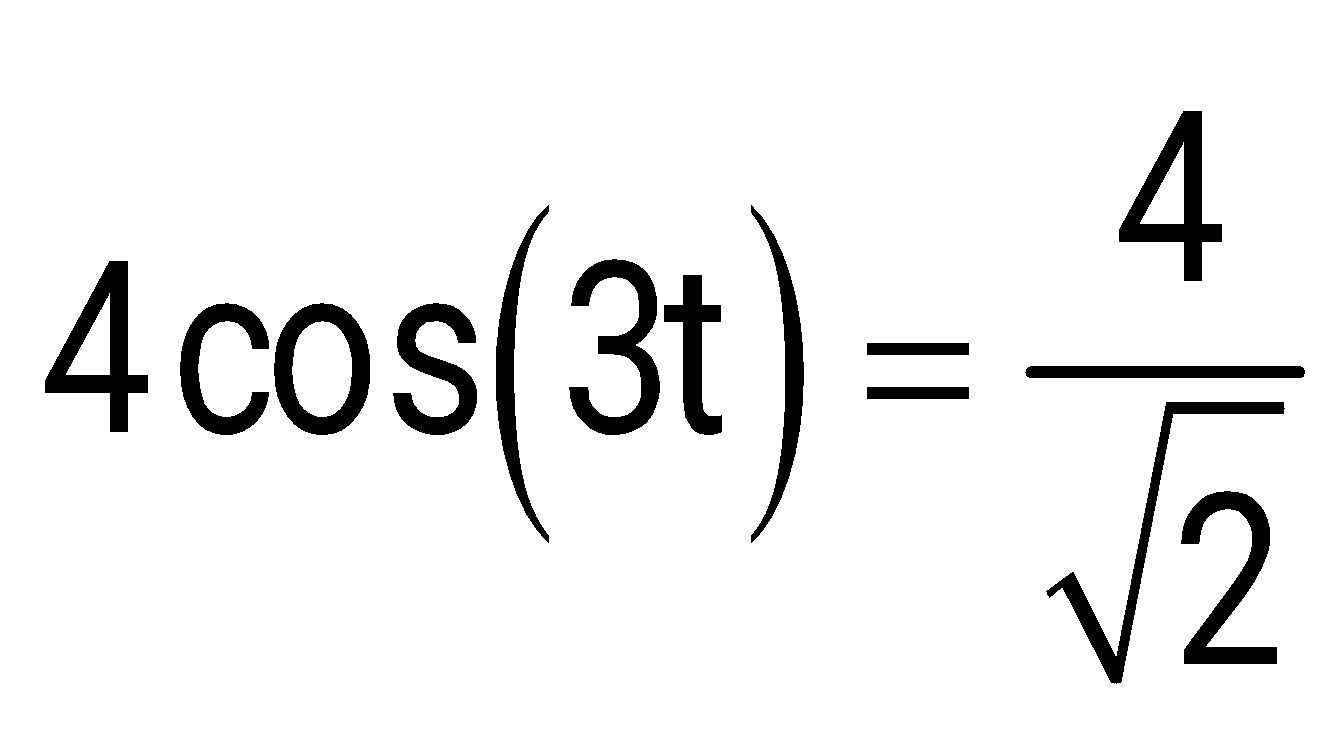

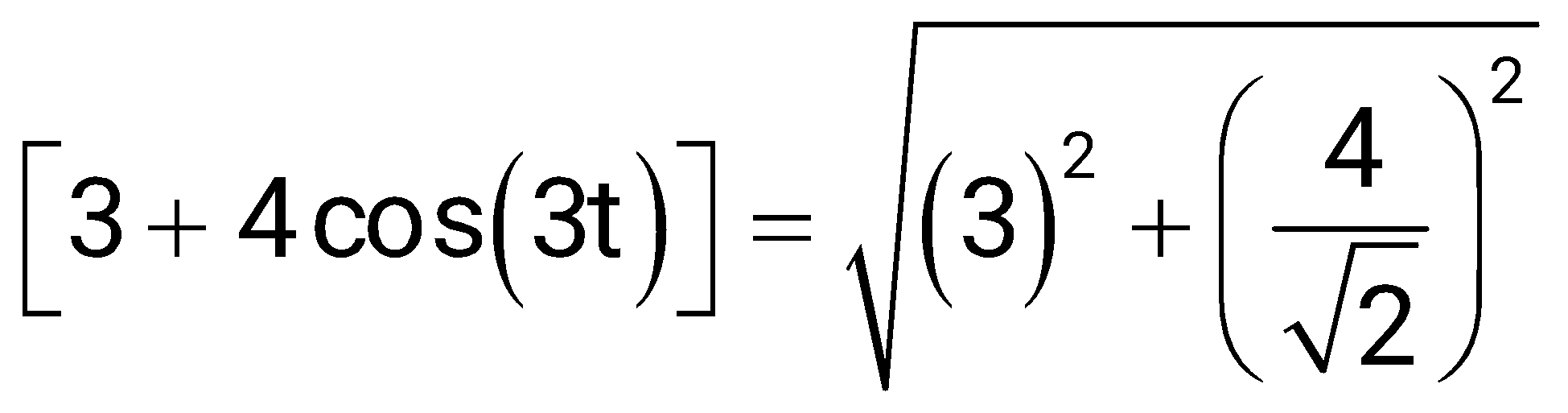

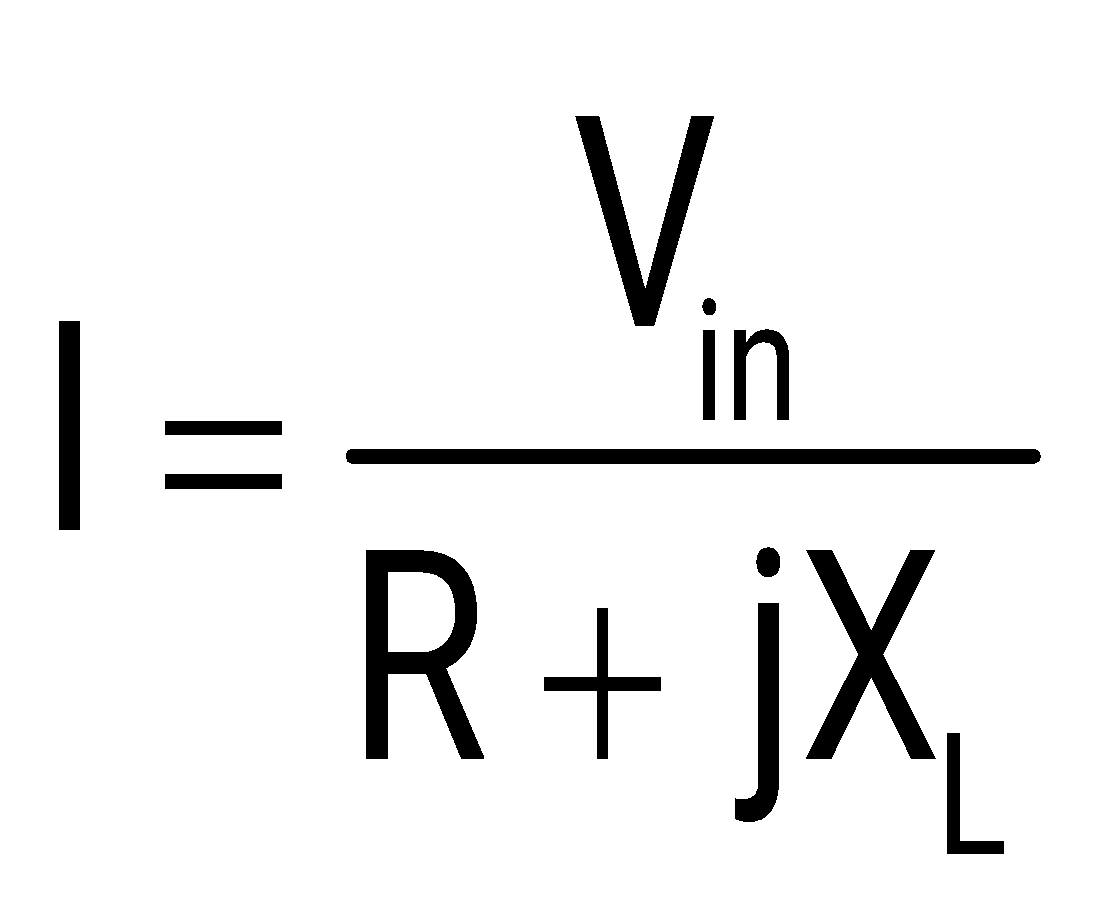

The circuit shown in the figure has two sources connected in series. The instantaneous voltage of the AC source (in Volt) is given by . If the circuit is in steady state, then the RMS value of the current (in Ampere) flowing in the circuit is

This problem can be solved by superposition principle.

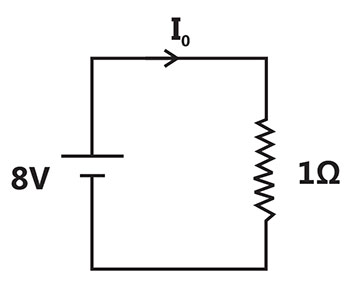

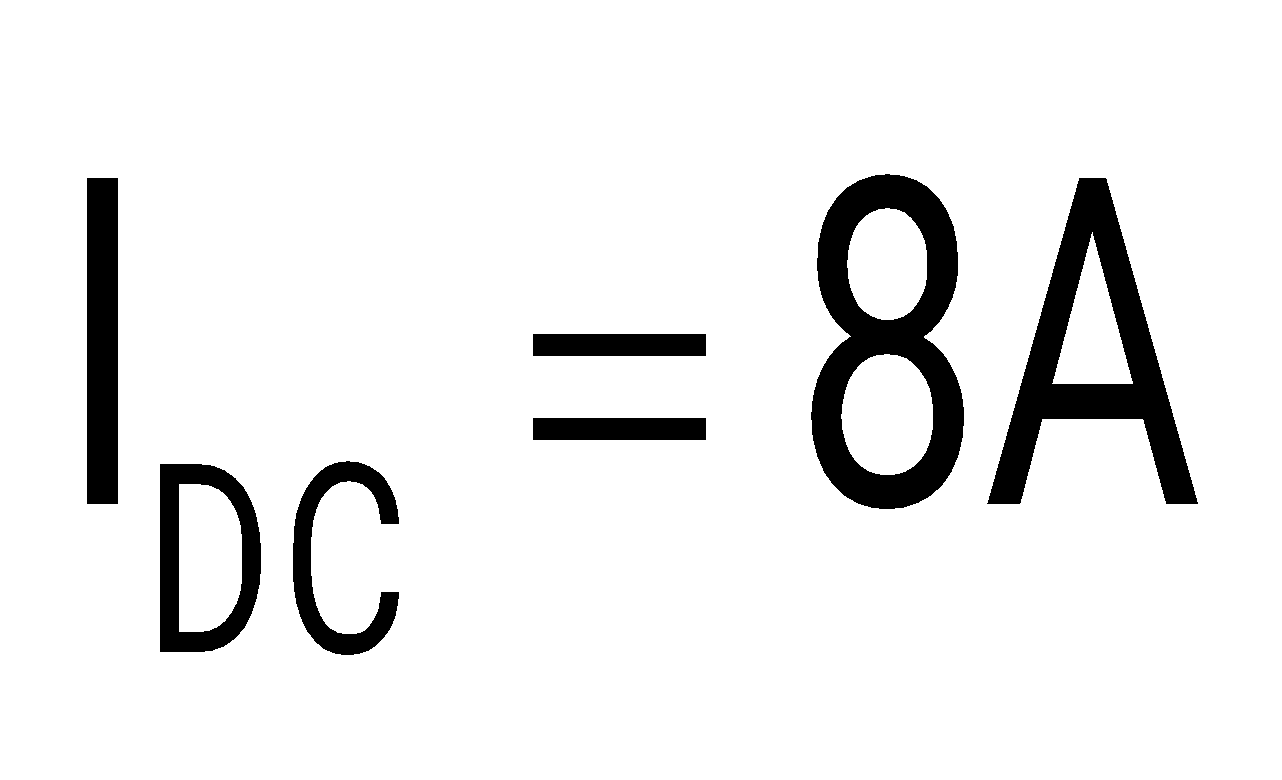

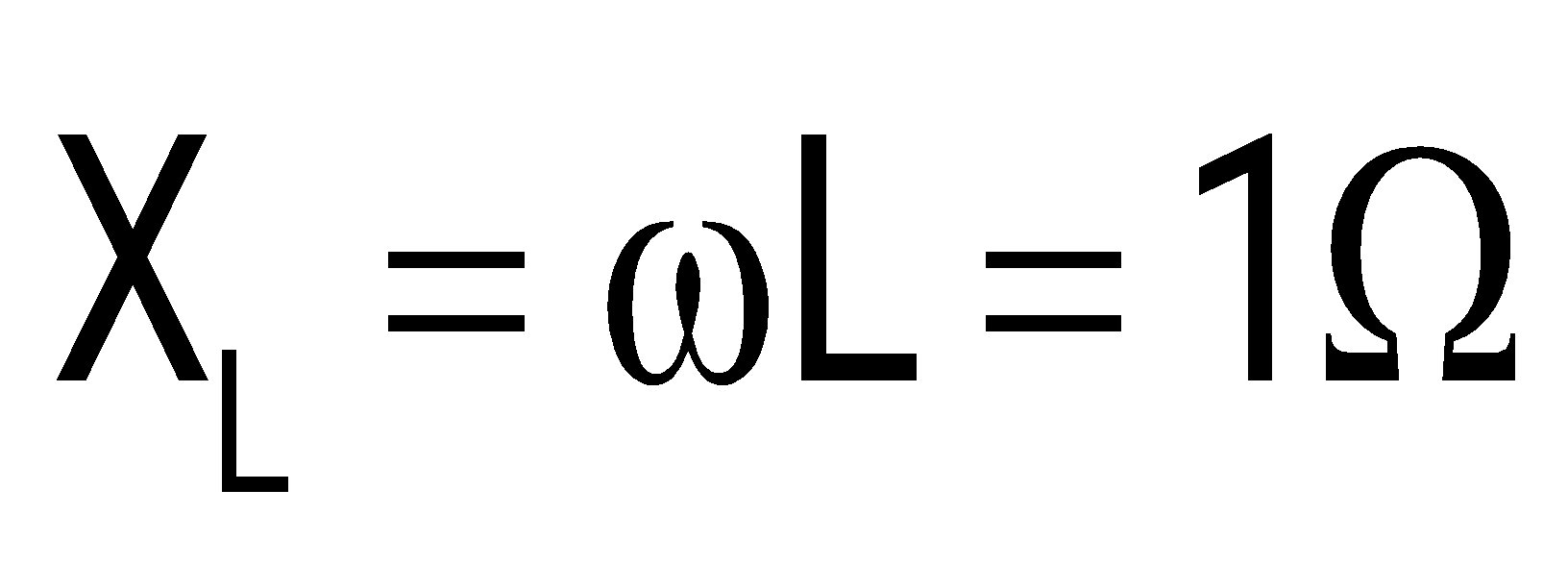

Solving with DC source alone by short circuiting the AC source:

In steady state, inductor is short – circuited,

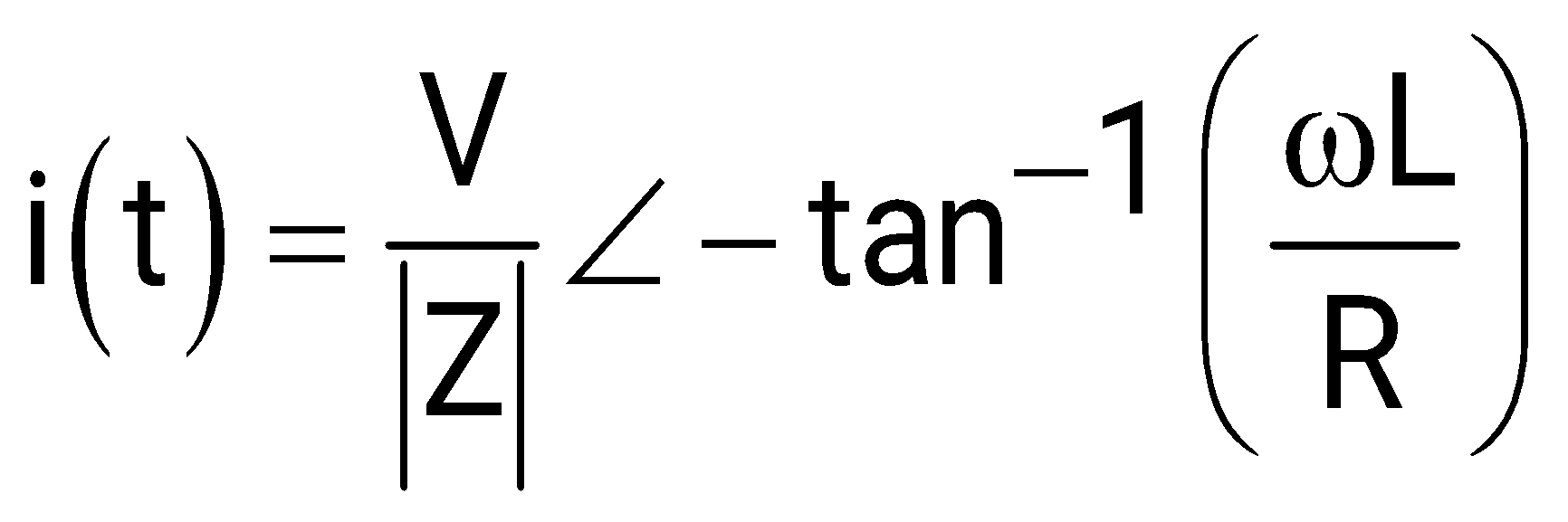

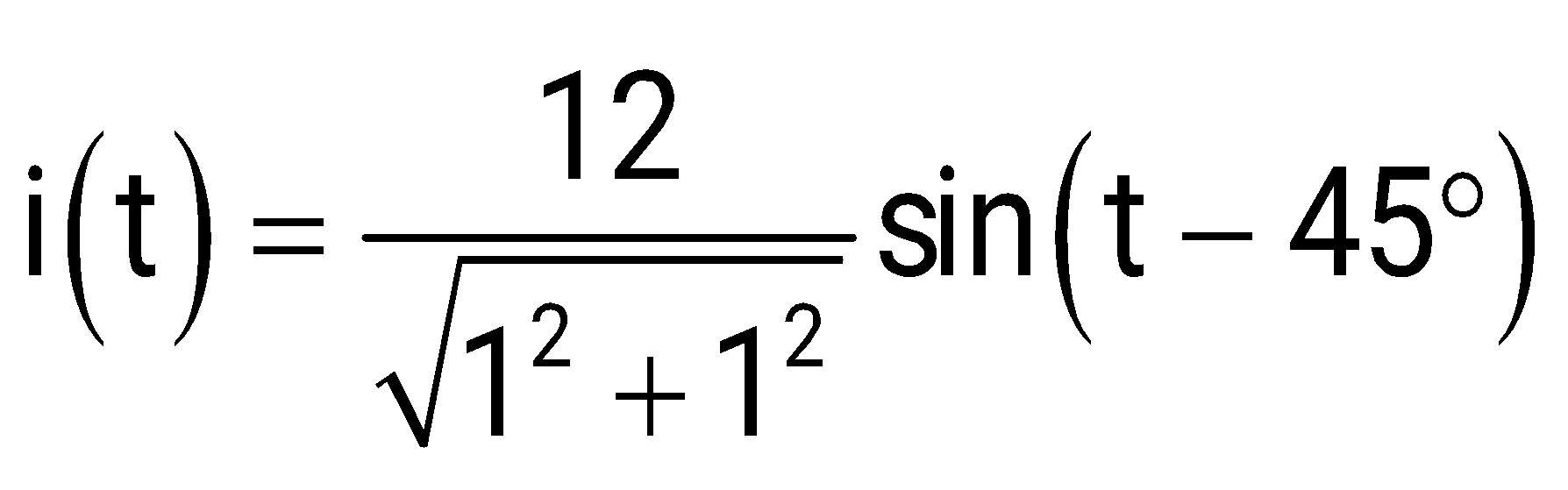

Solving with AC source alone by short circuiting the DC Source:

=1,

v(t) = 12 sin t

By superposition theorem,

RMS value of i(t)

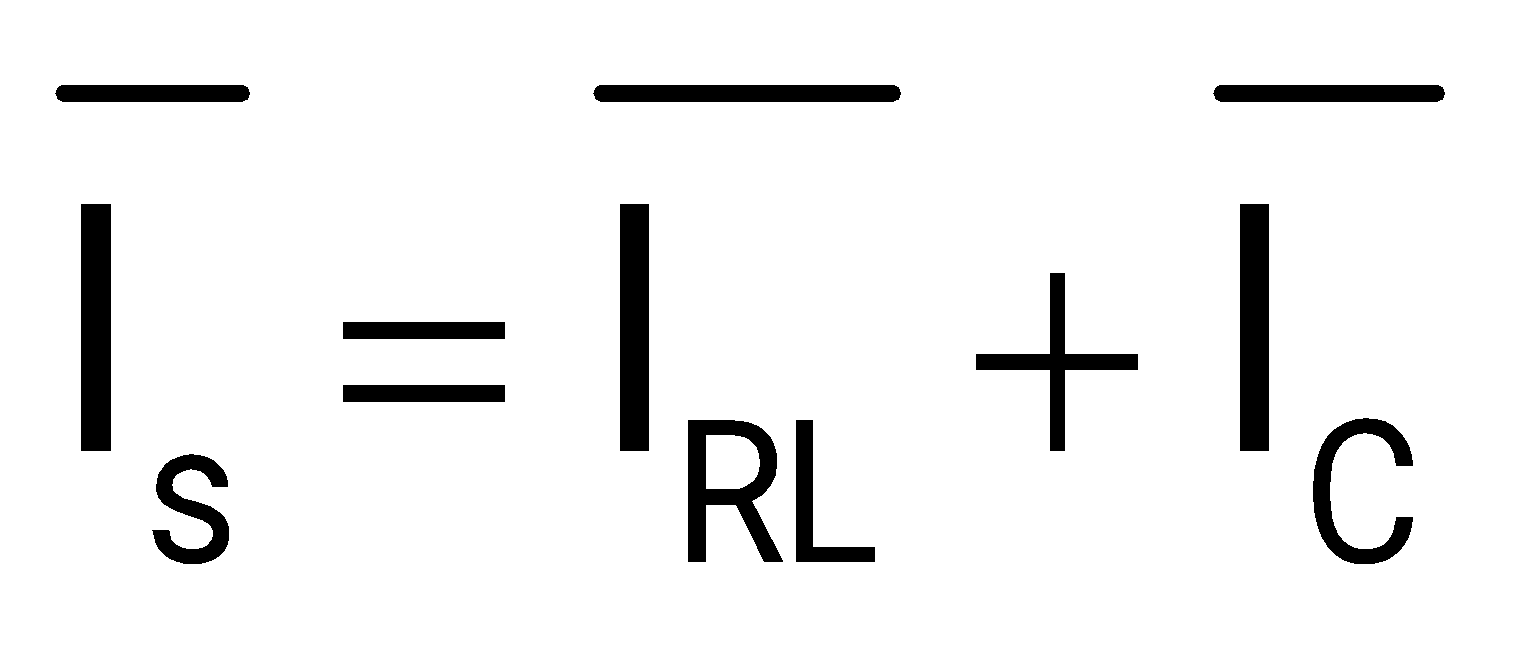

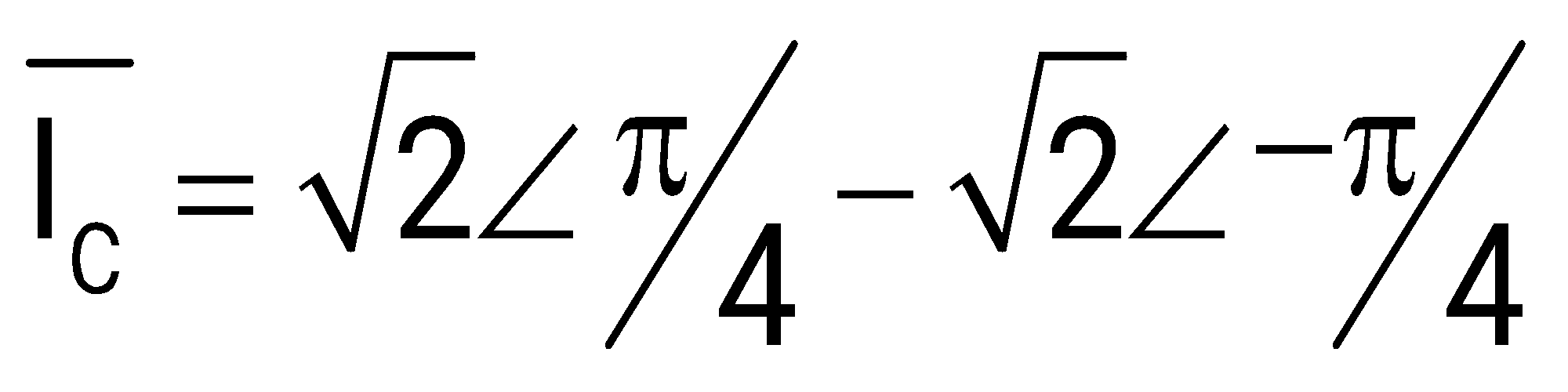

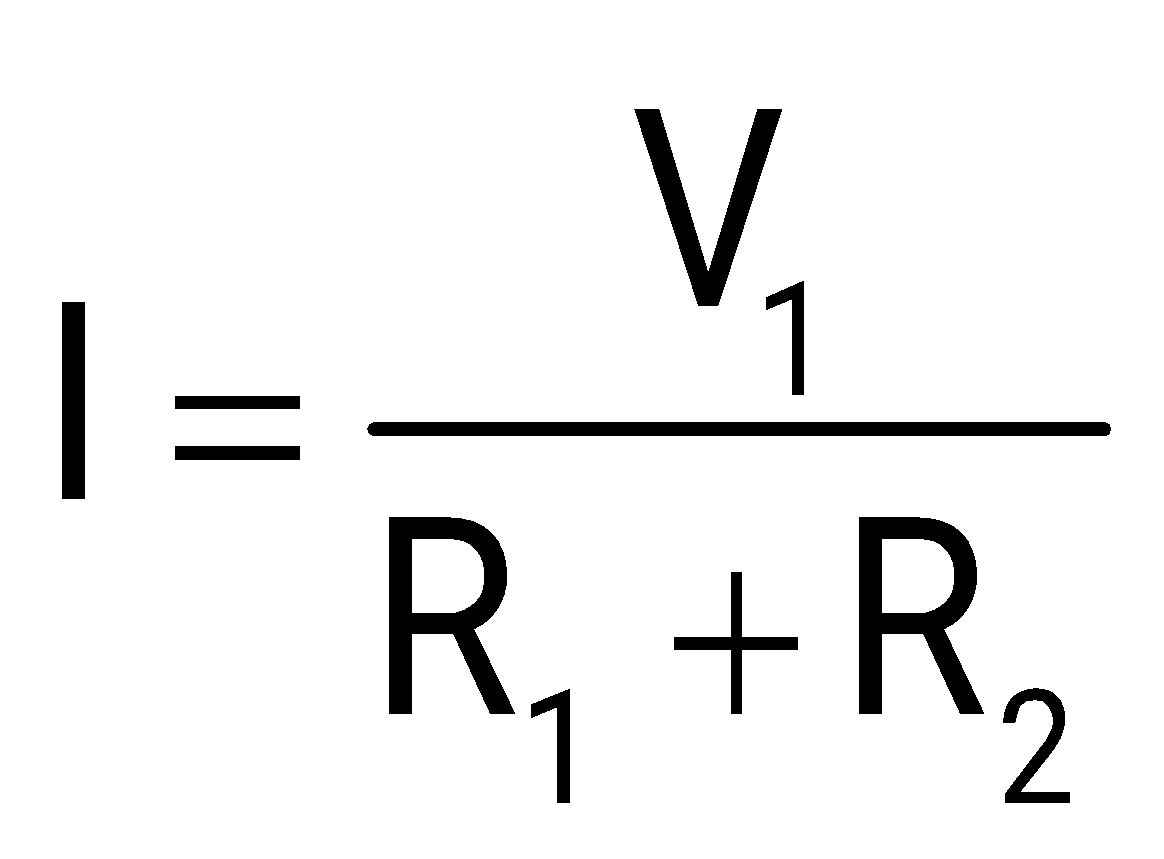

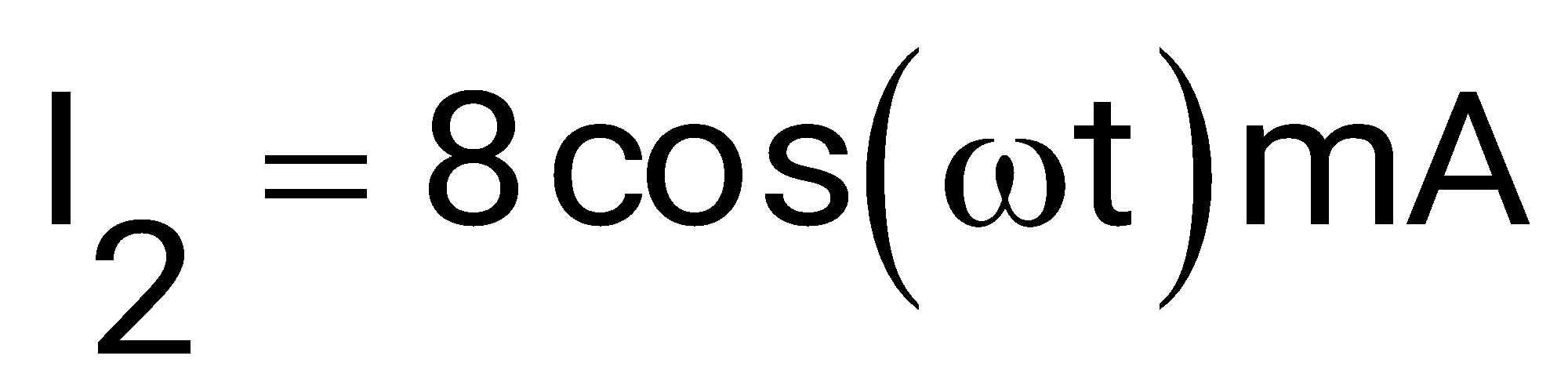

In the given network. , ,

The phasor current i (in Ampere) is

The currents in various branches of the circuit is shown,

By KVL,

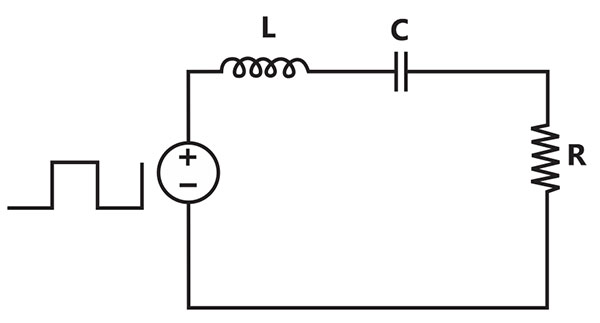

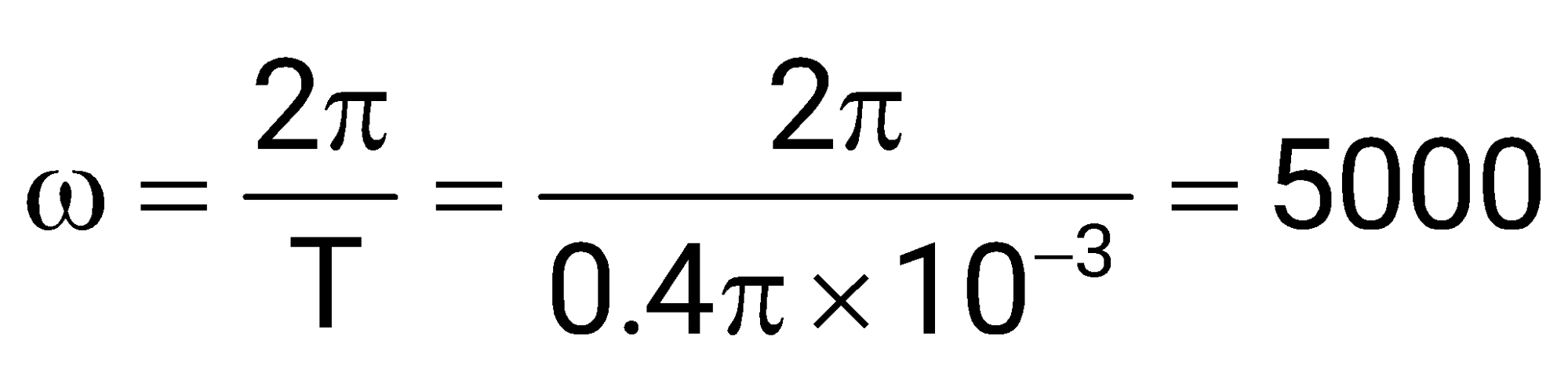

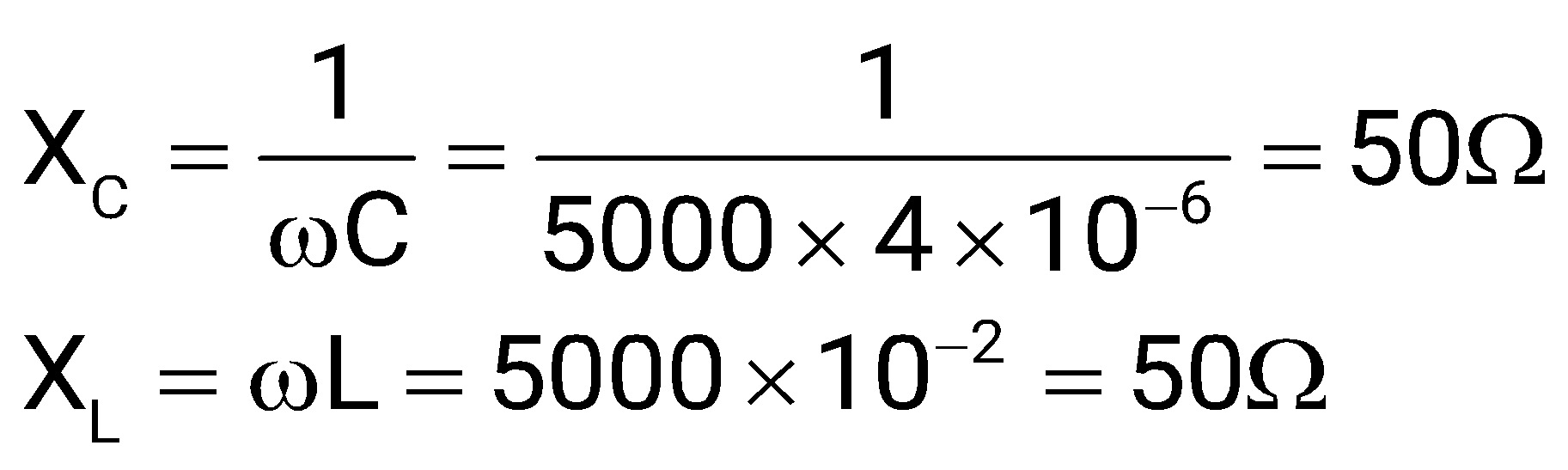

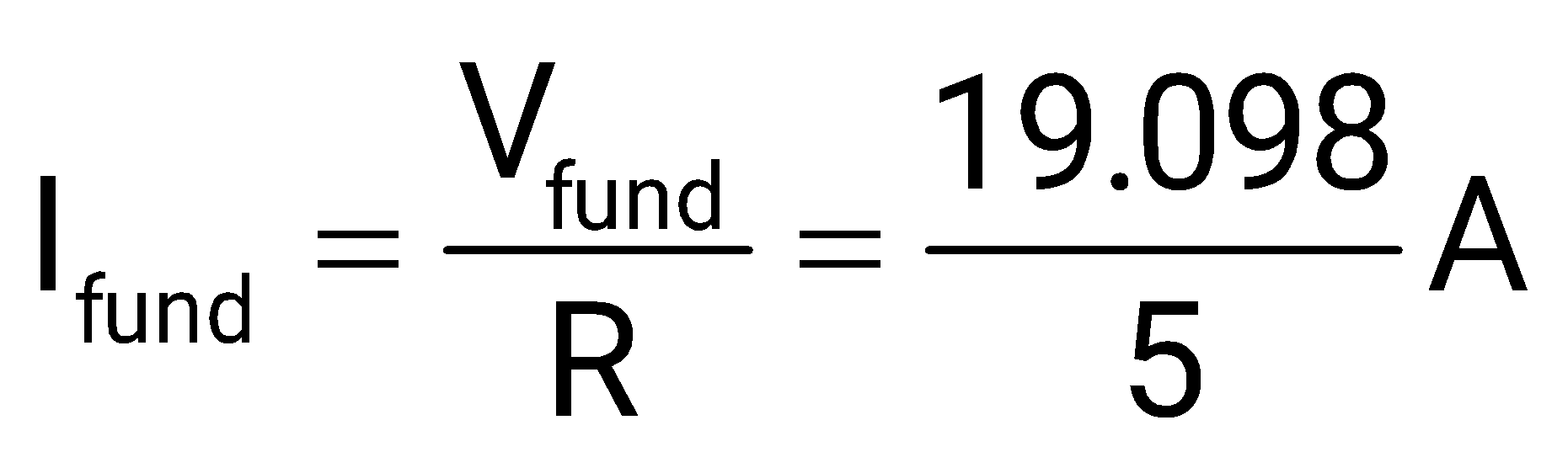

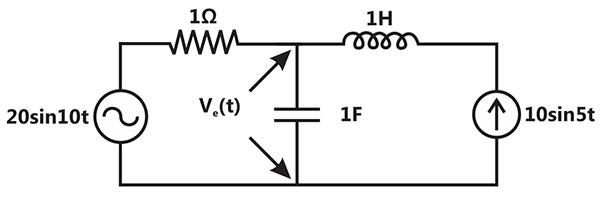

A symmetrical square wave of 50% duty cycle has amplitude of ±15V and time period of . This square wave is applied across a series RLC circuit with L=10mH and . The amplitude of the 5000 rad/s component of the capacitor voltage (in volt) is ____________.

Assuming the supply voltage is represented by V (peak)

Fourier series of square wave:

ms

rad/sec

So, we are interested in fundamental.

Since , circuit is in resonance. Hence, fundamental current can be obtained as,

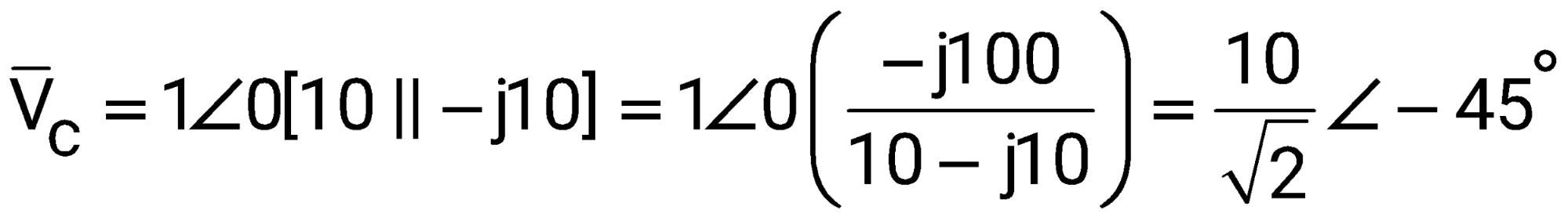

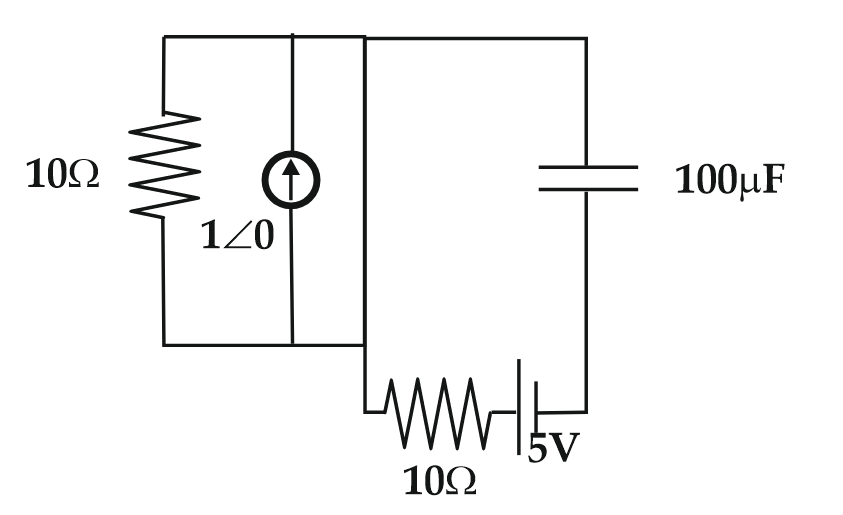

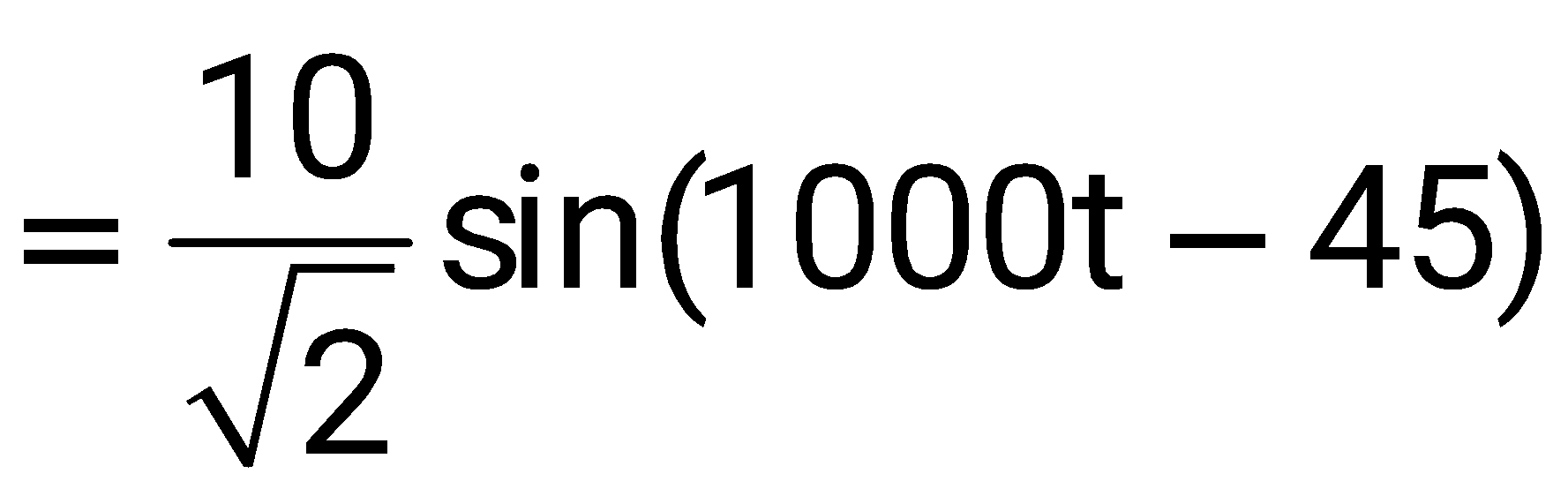

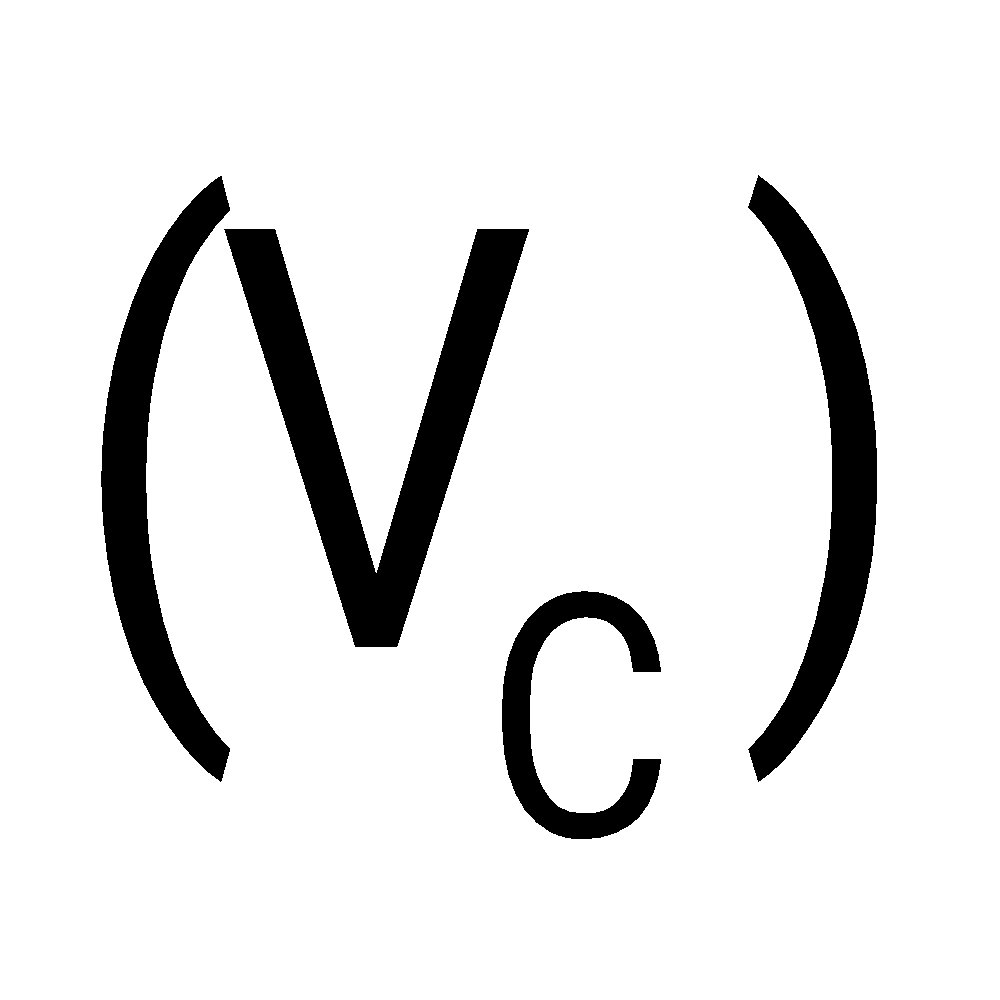

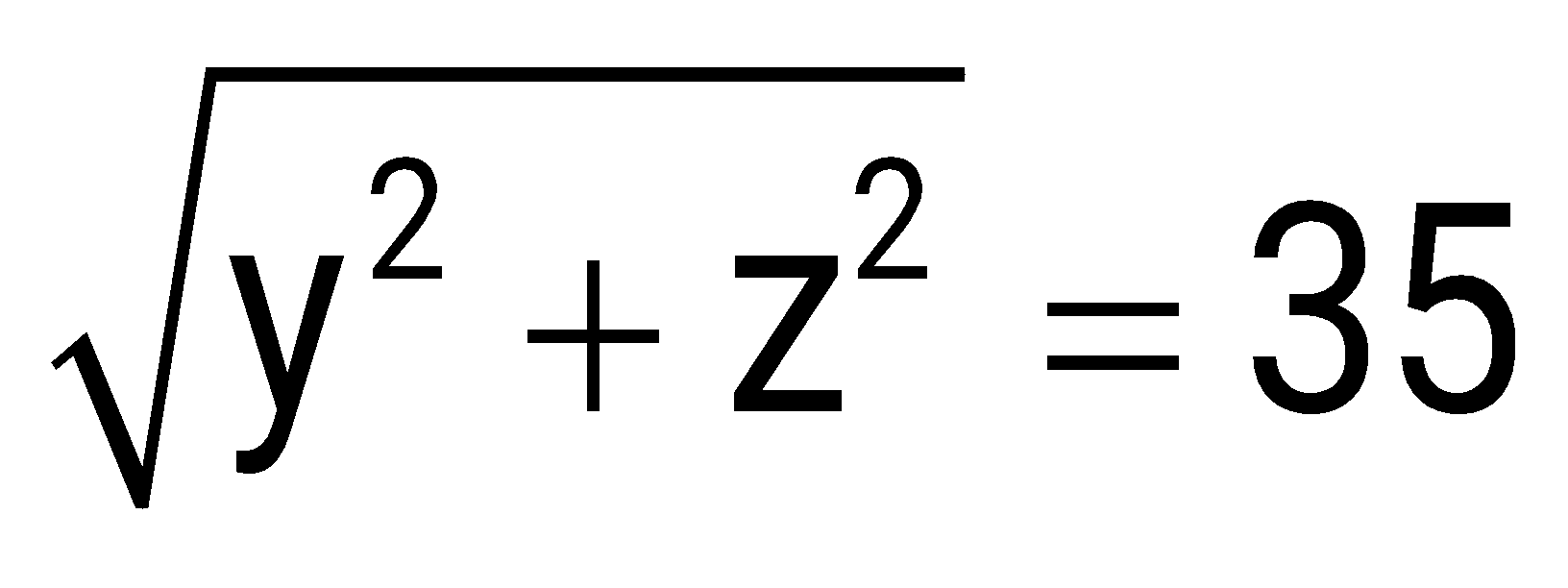

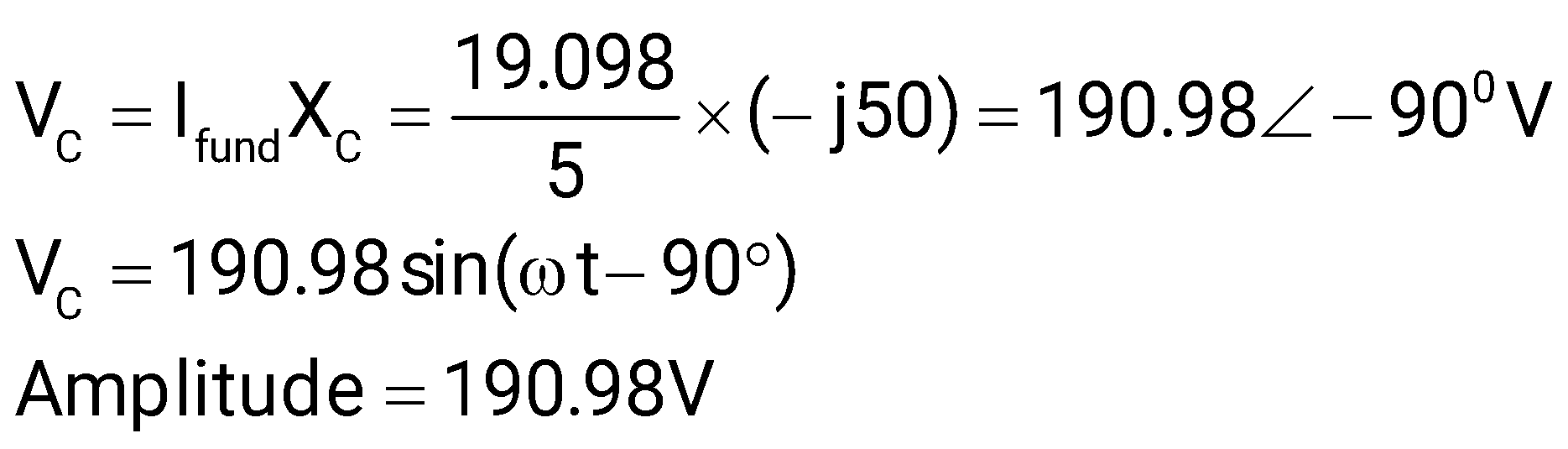

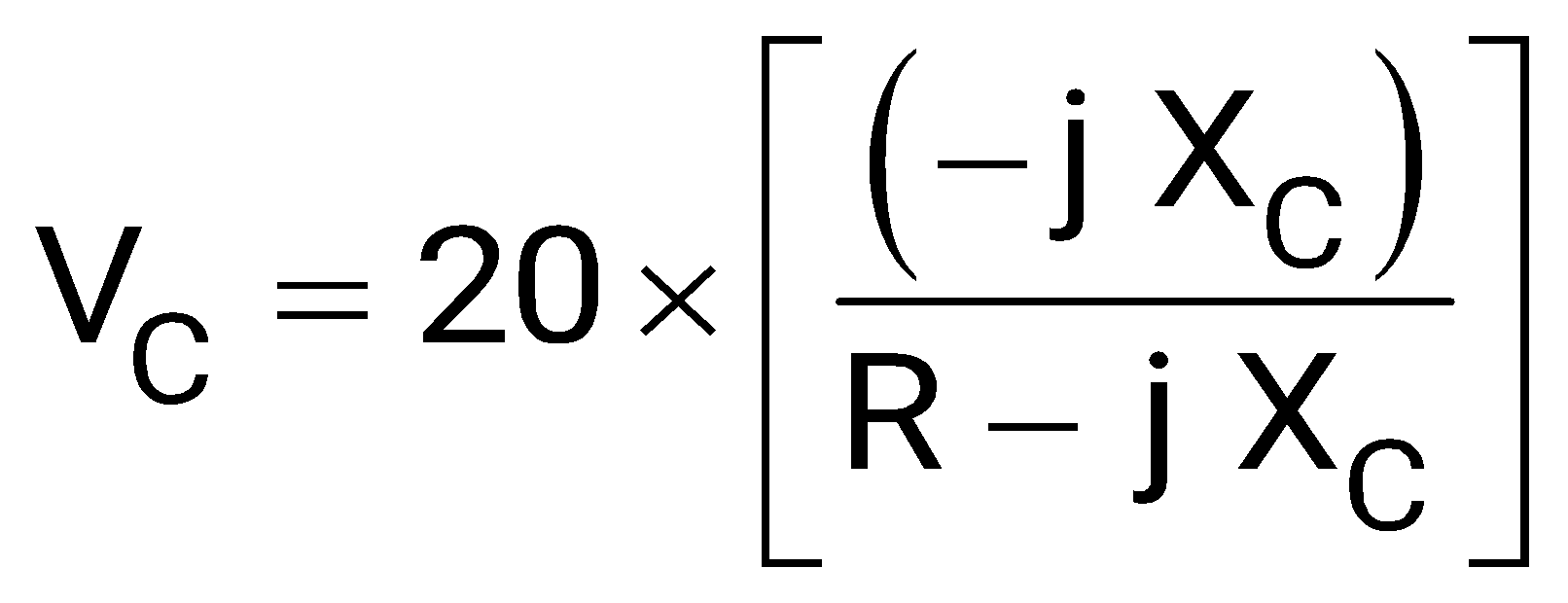

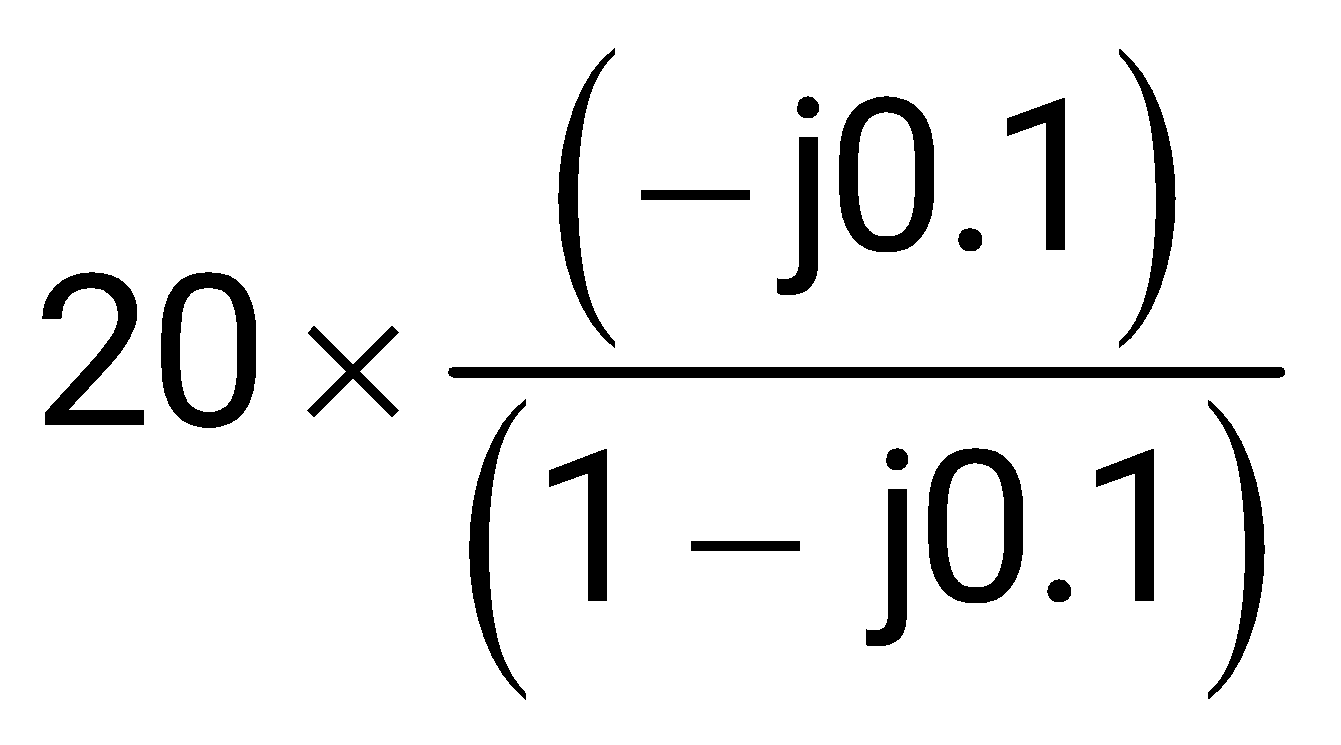

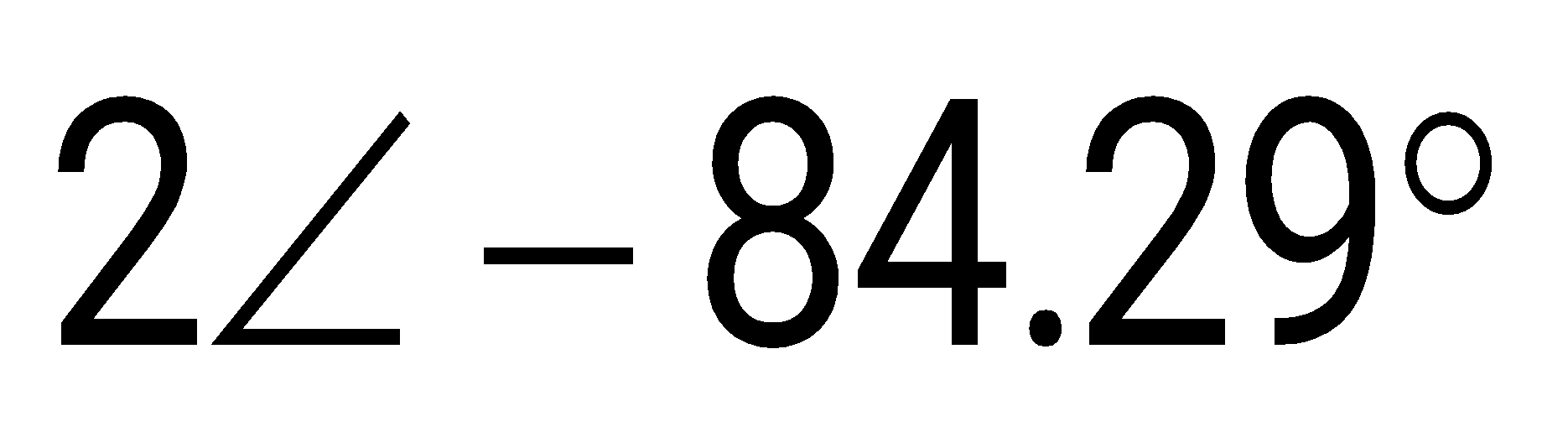

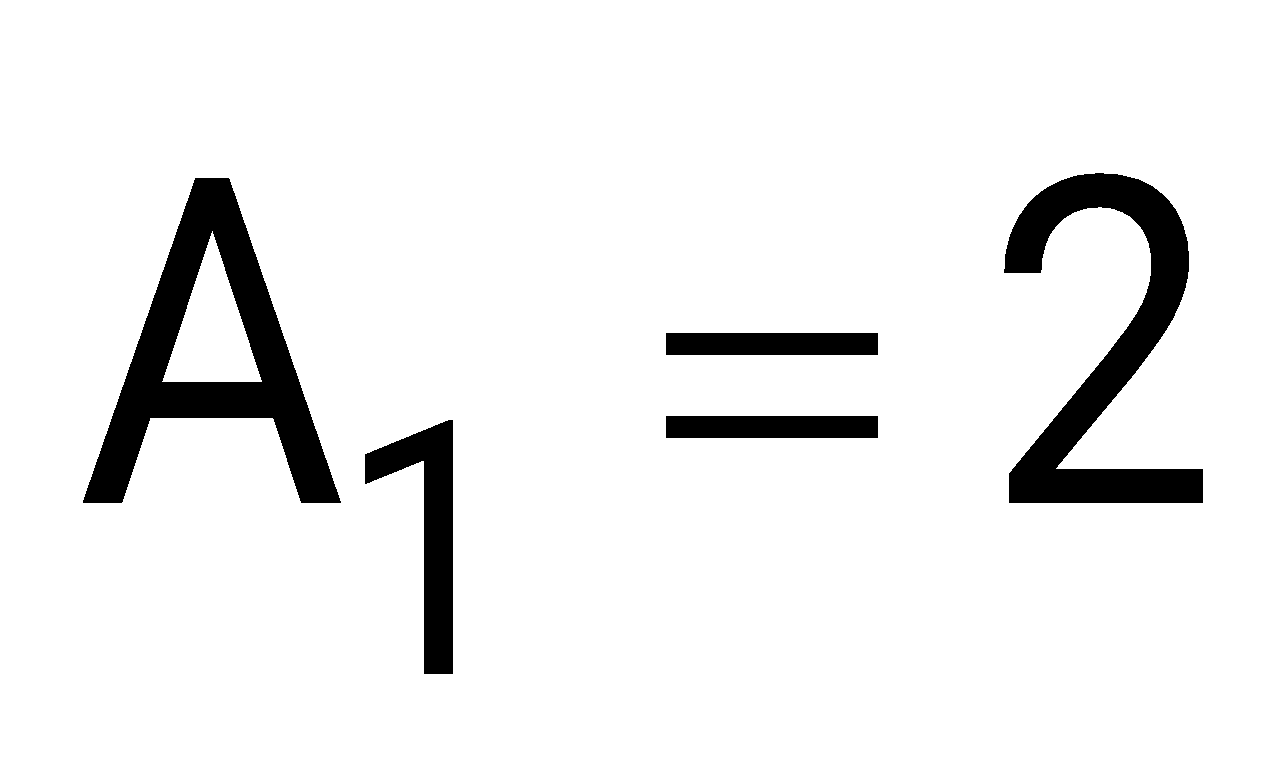

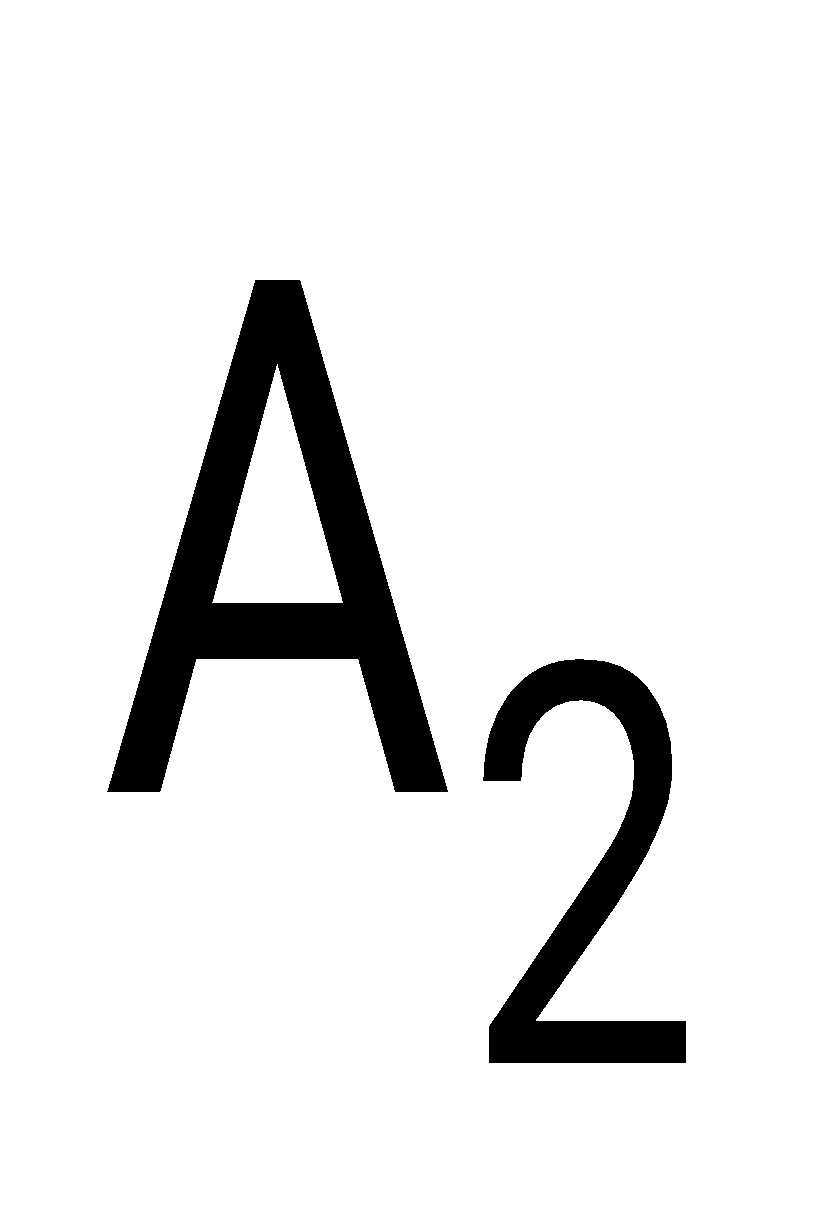

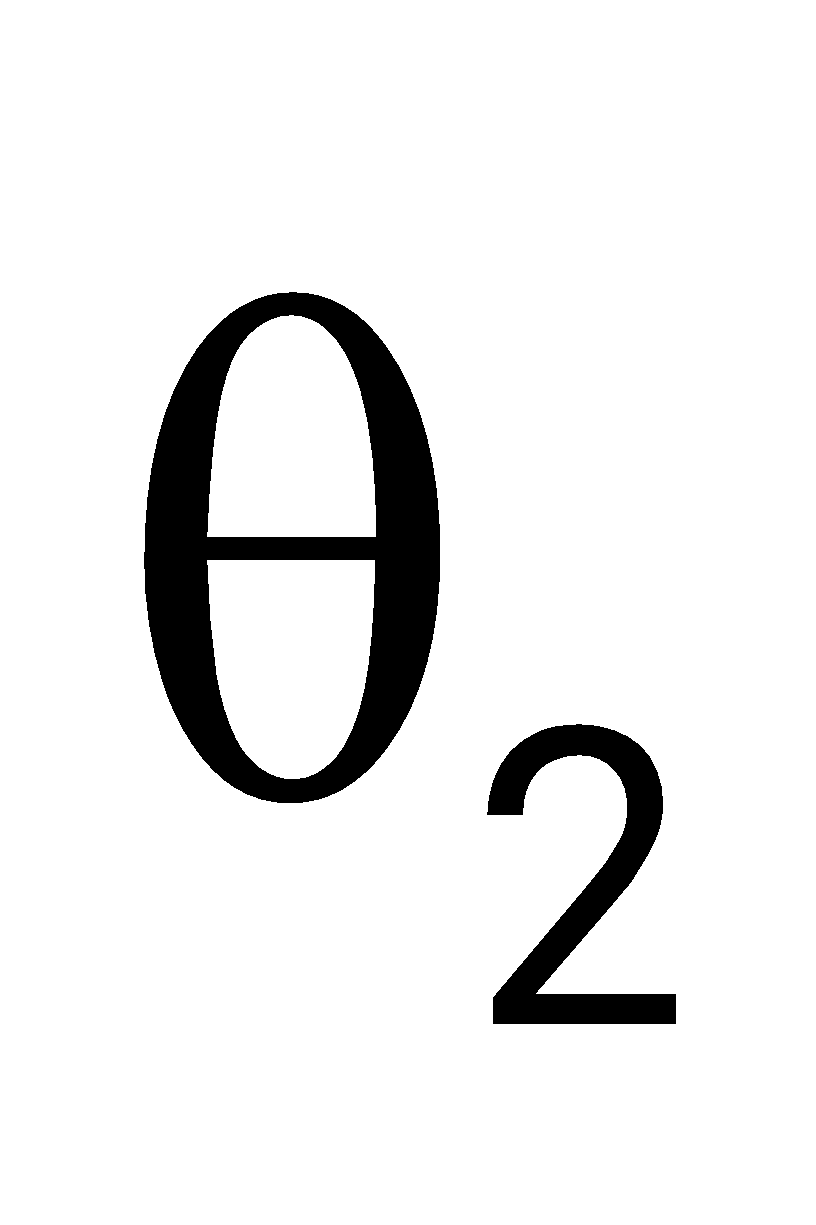

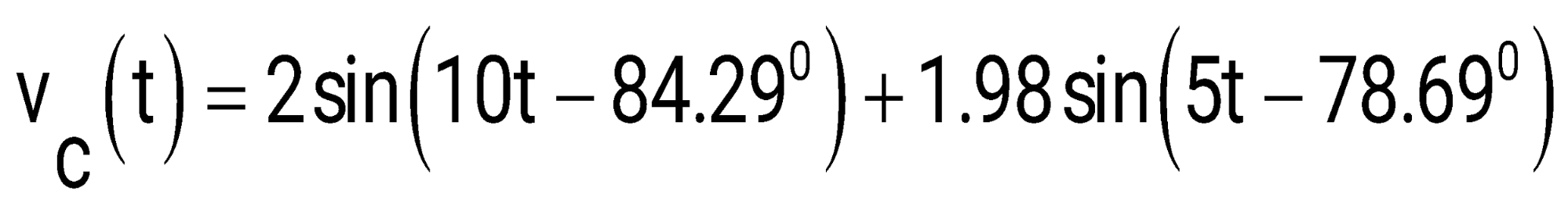

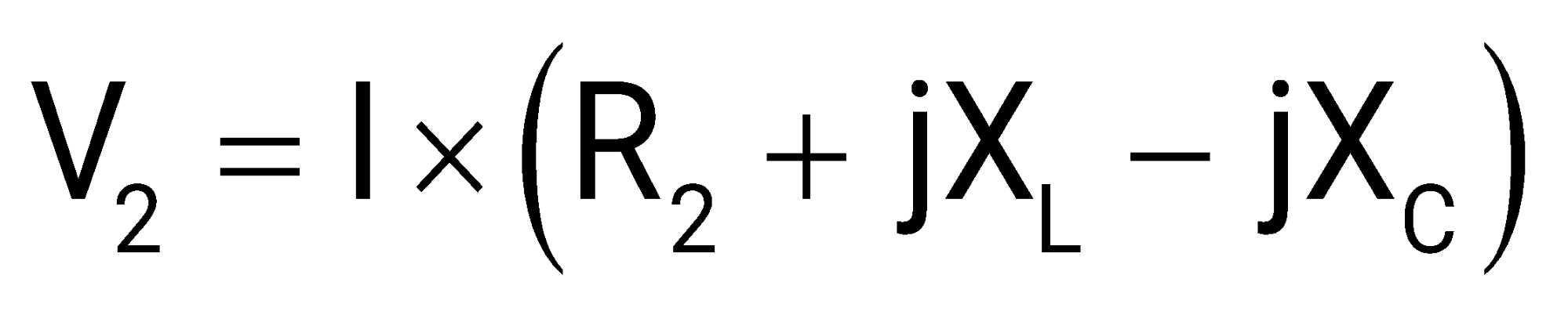

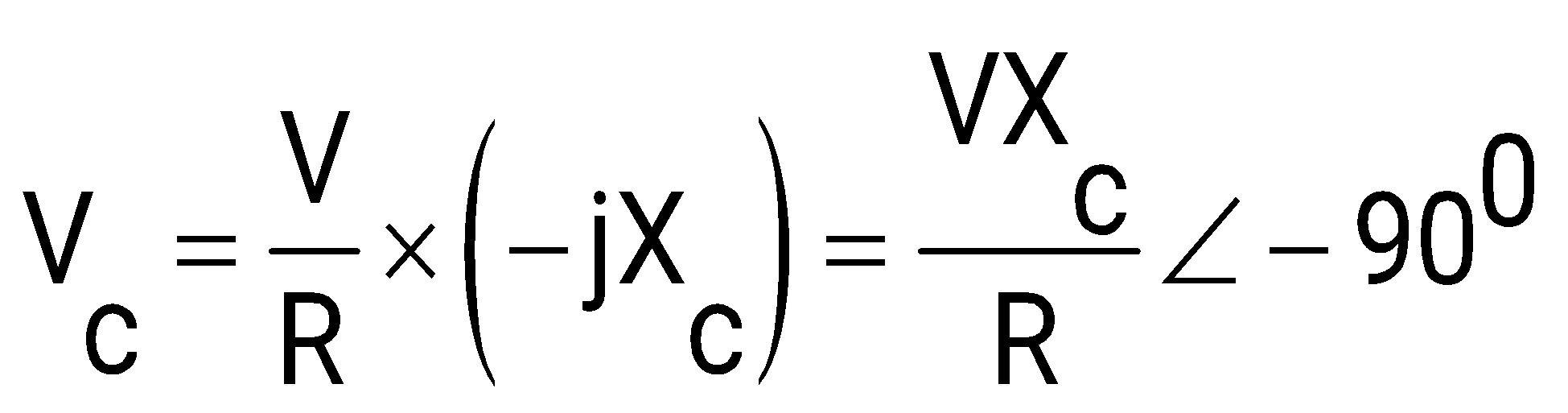

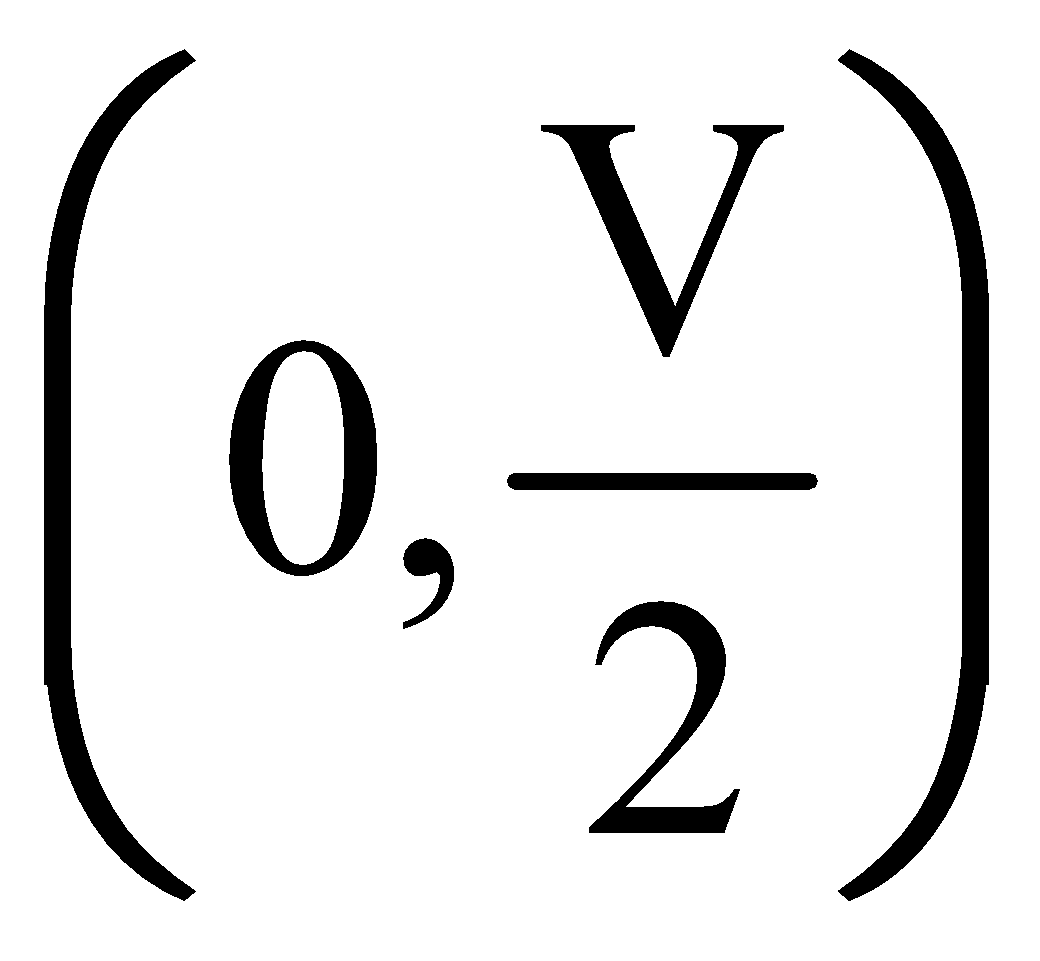

The voltage across the capacitor, as shown in the figure, is expressed as +

The values of and respectively, are

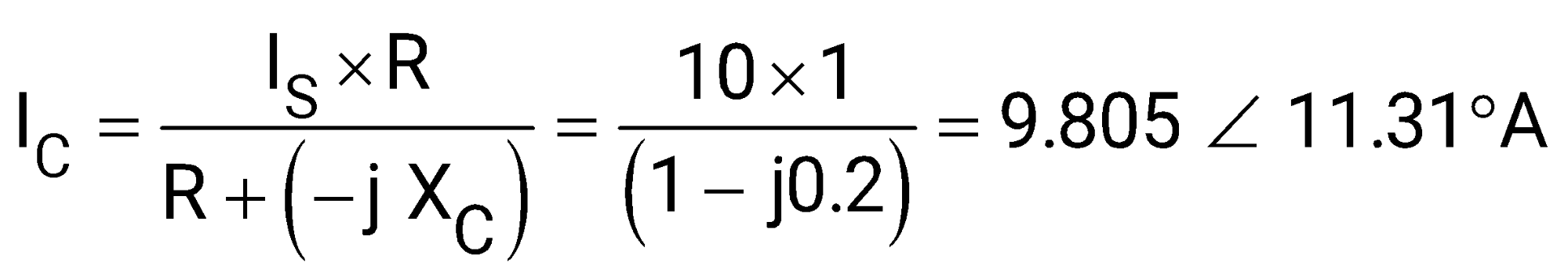

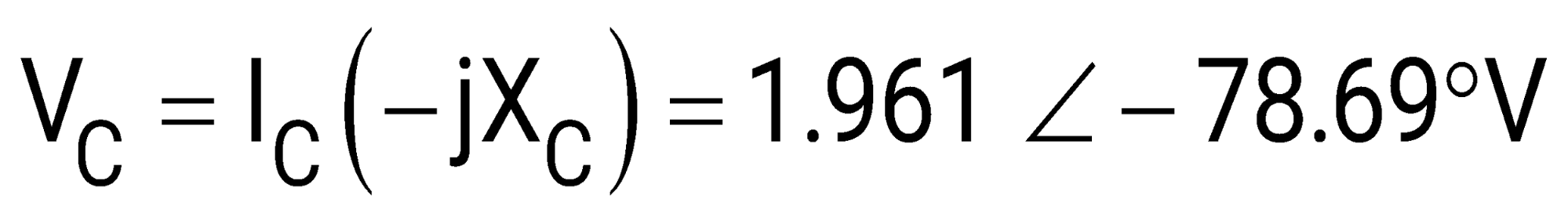

Using super position theorem,

First, open circuit current source

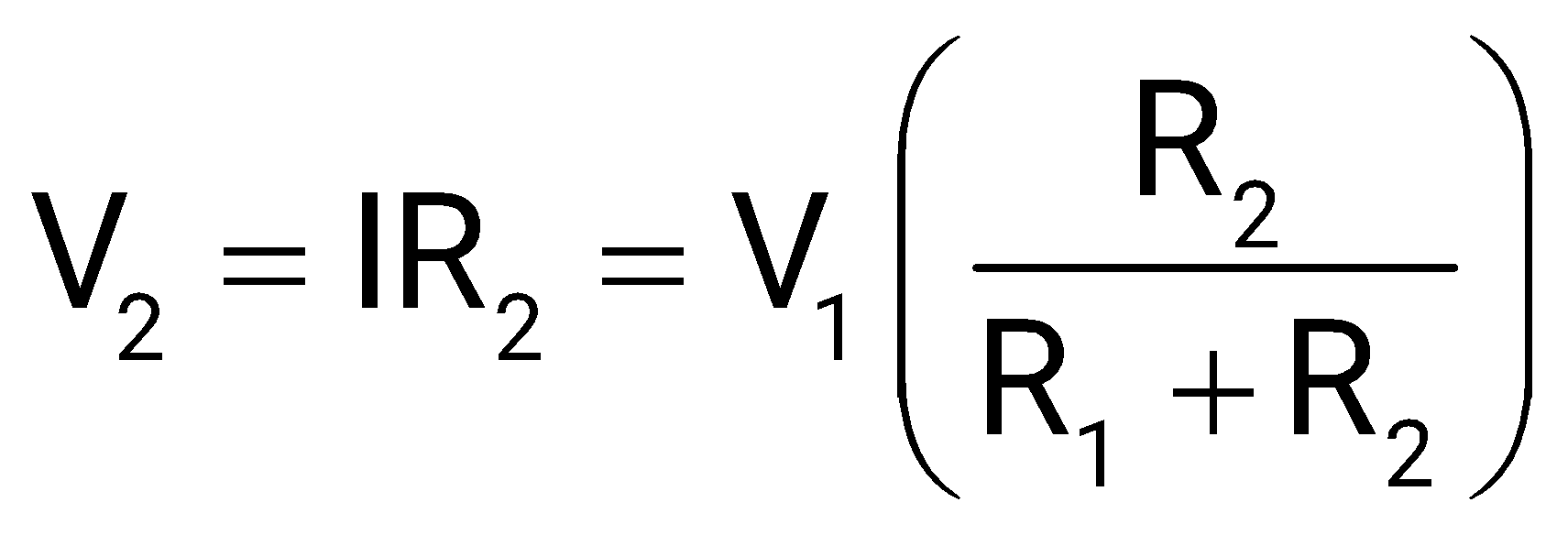

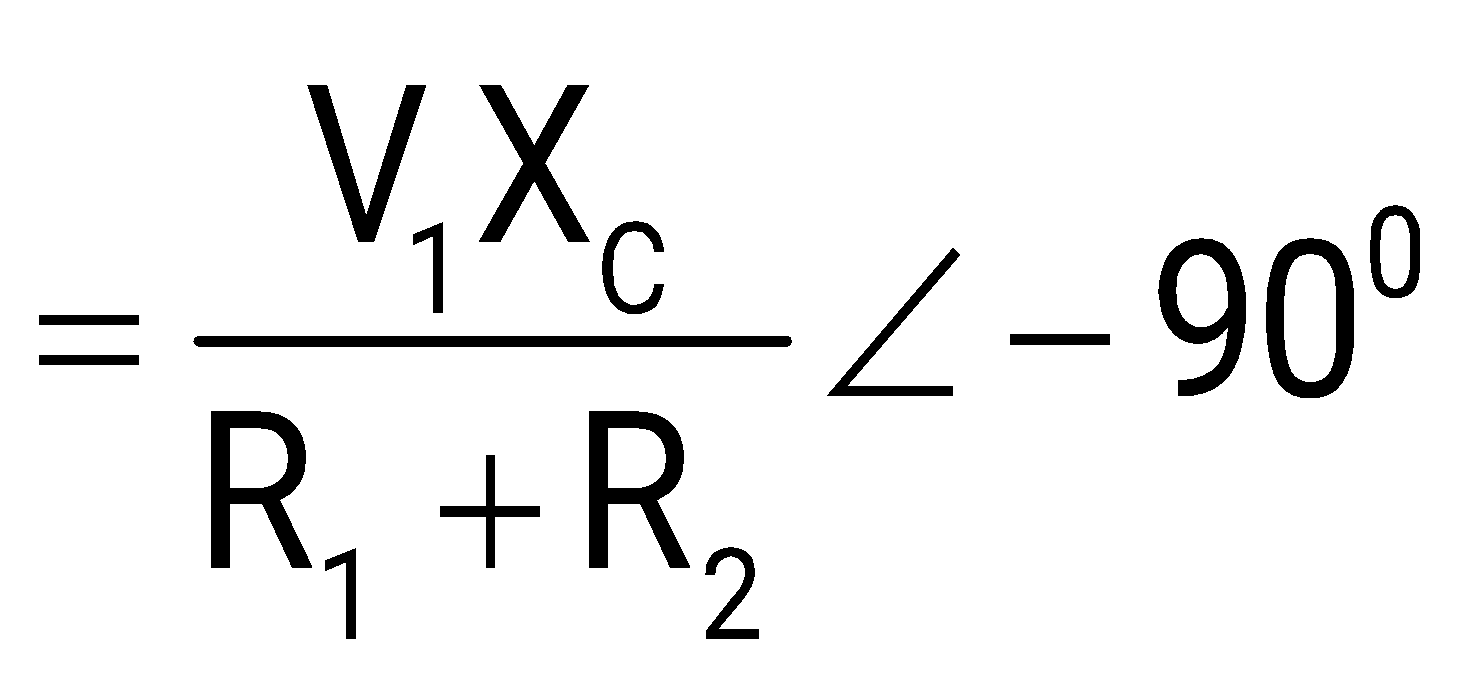

By Potential Division,

= =

Therefore, ;

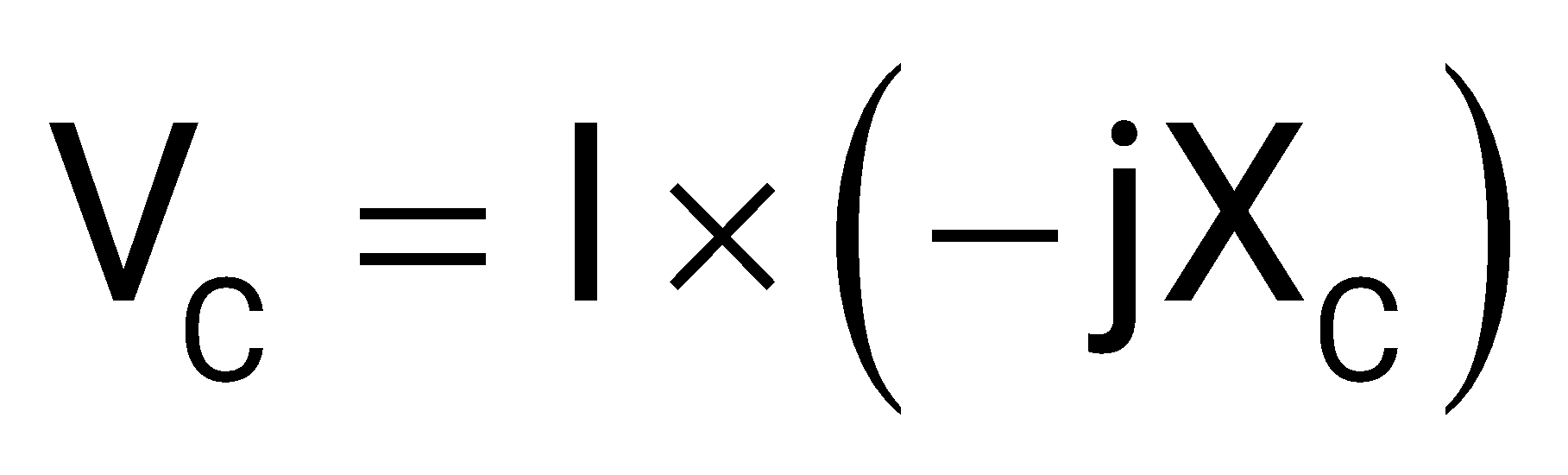

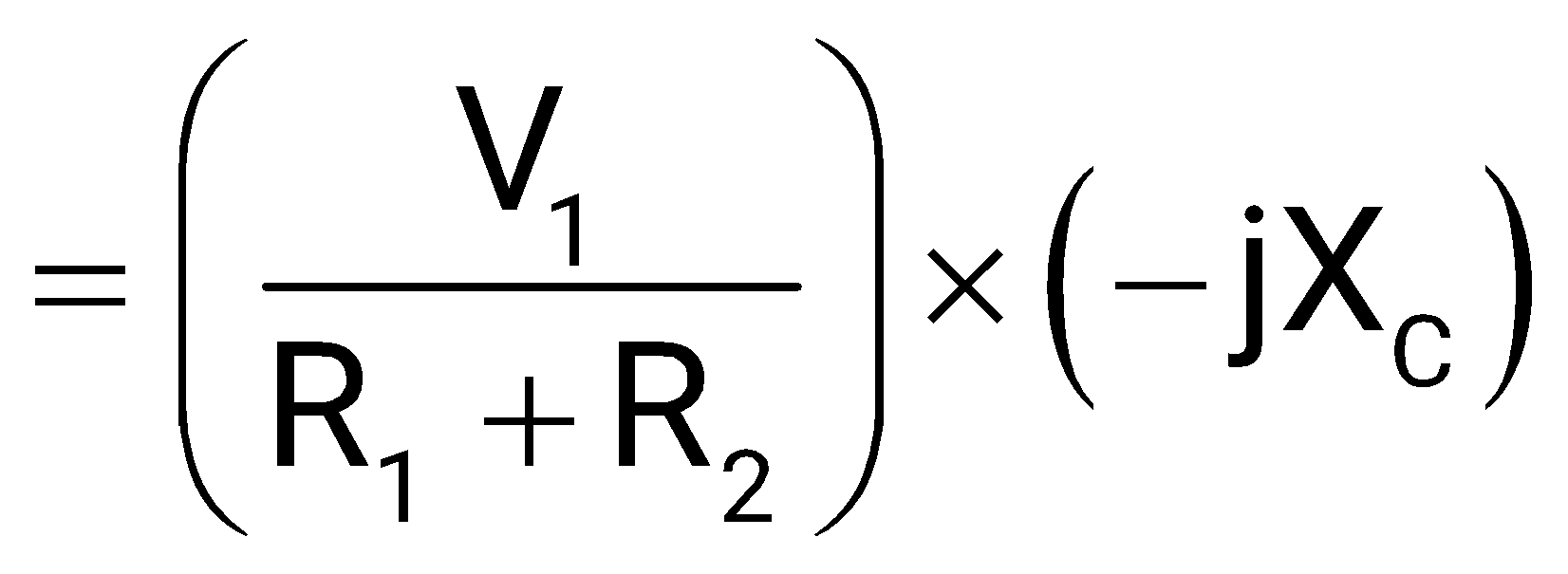

Now, short circuit voltage source

By Current Division,

Hence, =1.98 , = 78.69°

Thus, the capacitor voltage is given by,

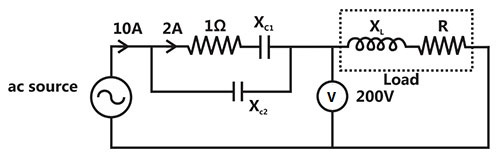

The total power dissipated in the circuit, shown in the figure, is 1kW. The voltmeter, across the load, reads 200V. The value of is ____________

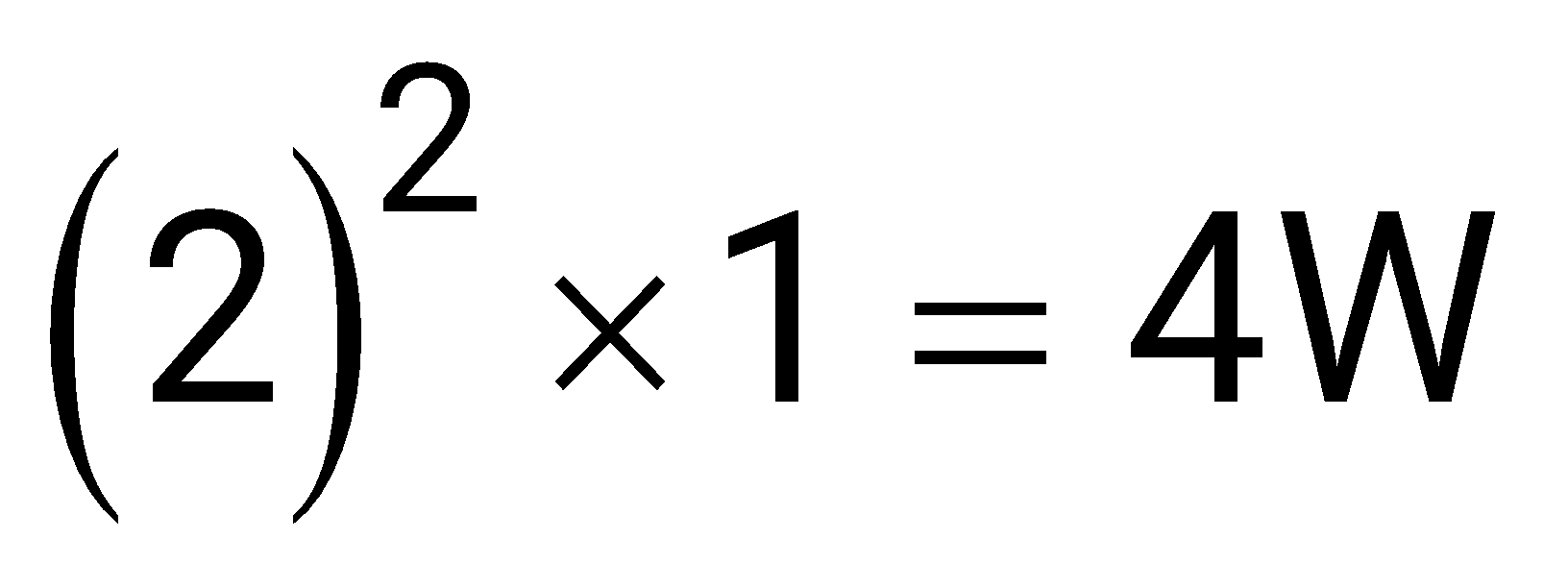

Power loss in 1Ω =

Real Power is only consumed in resistances. Hence,

Power loss in R = 1 kW – 4W = 996W

Assuming no current goes into voltmeter i.e. ideal voltmeter,

R = 9.96Ω

,

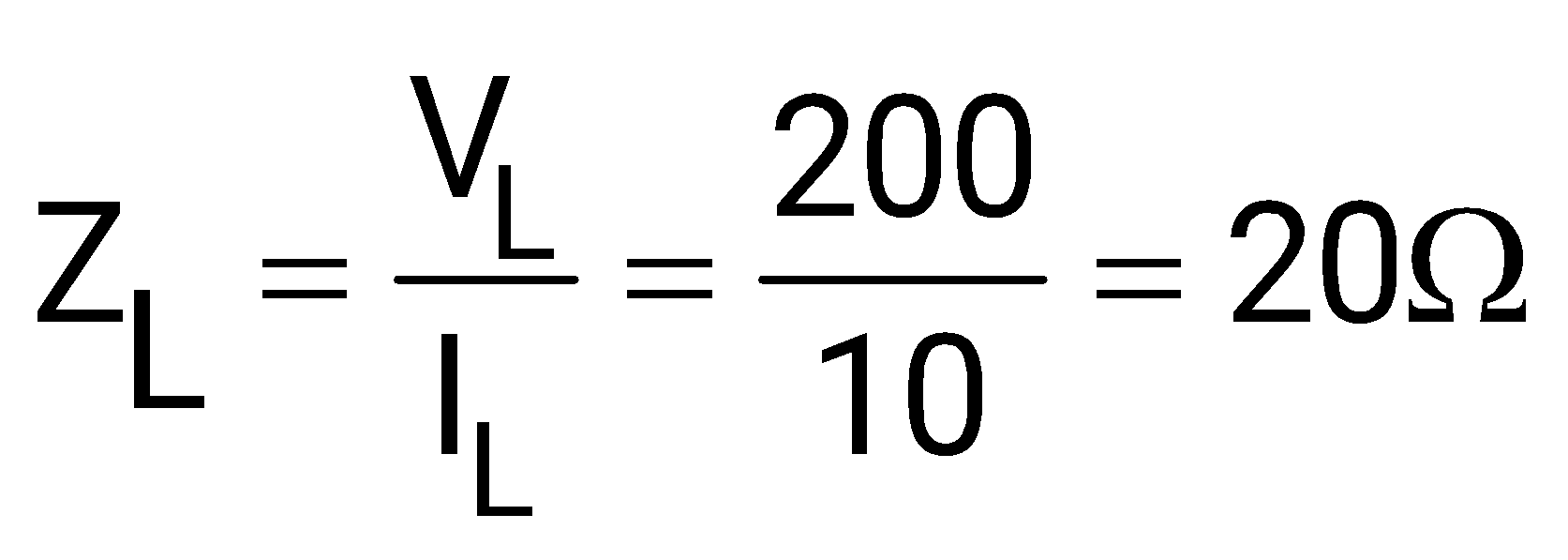

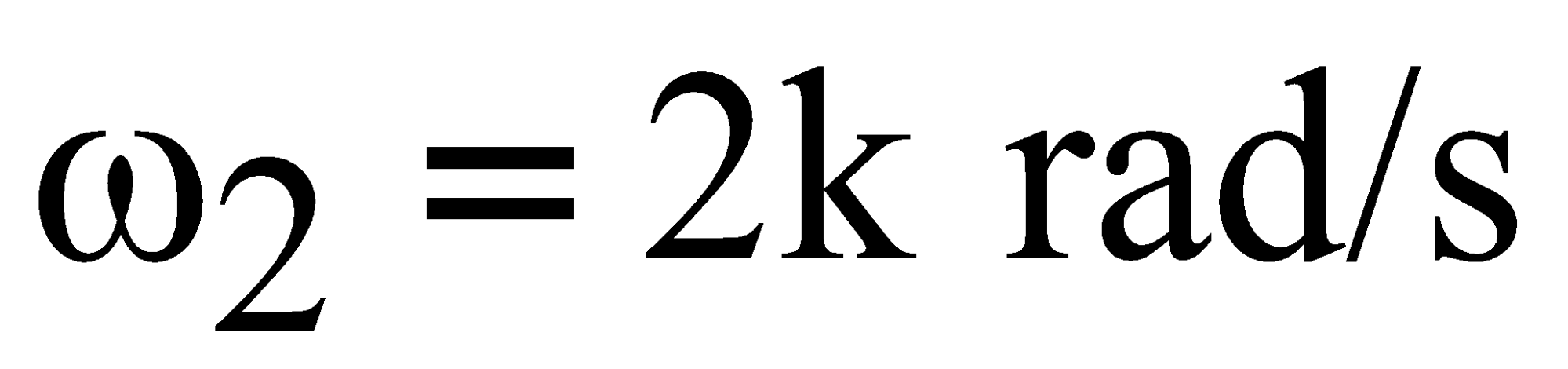

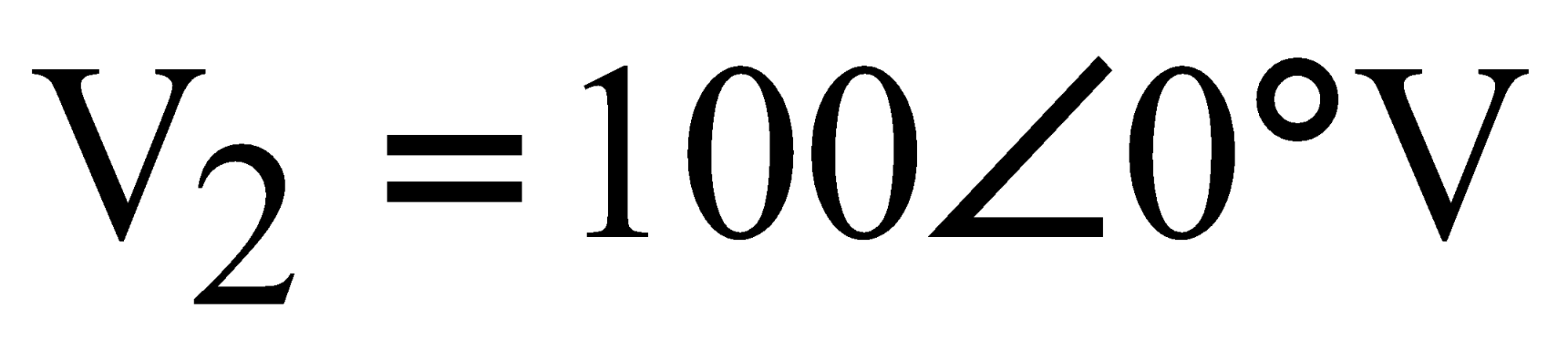

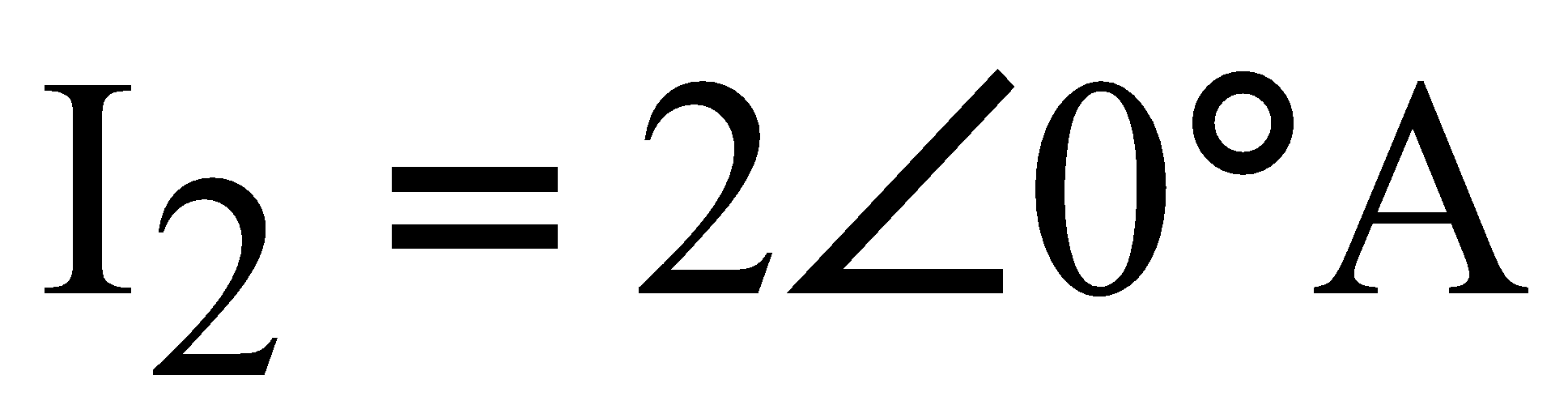

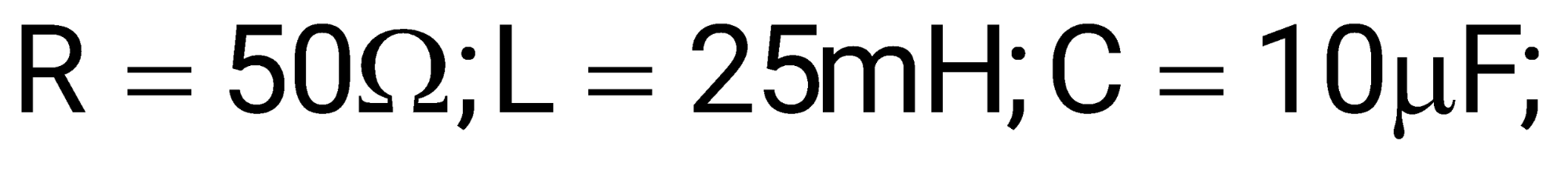

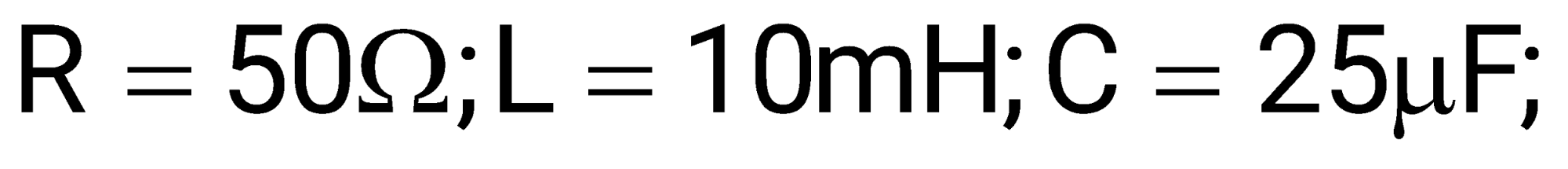

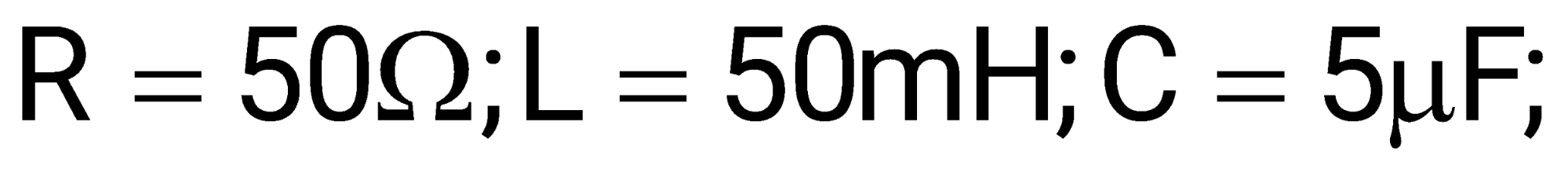

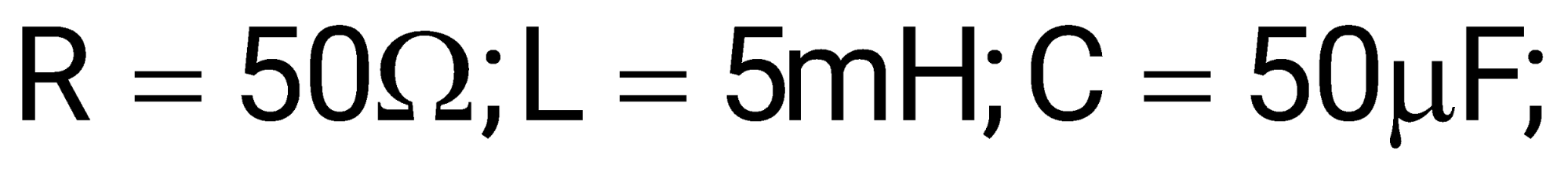

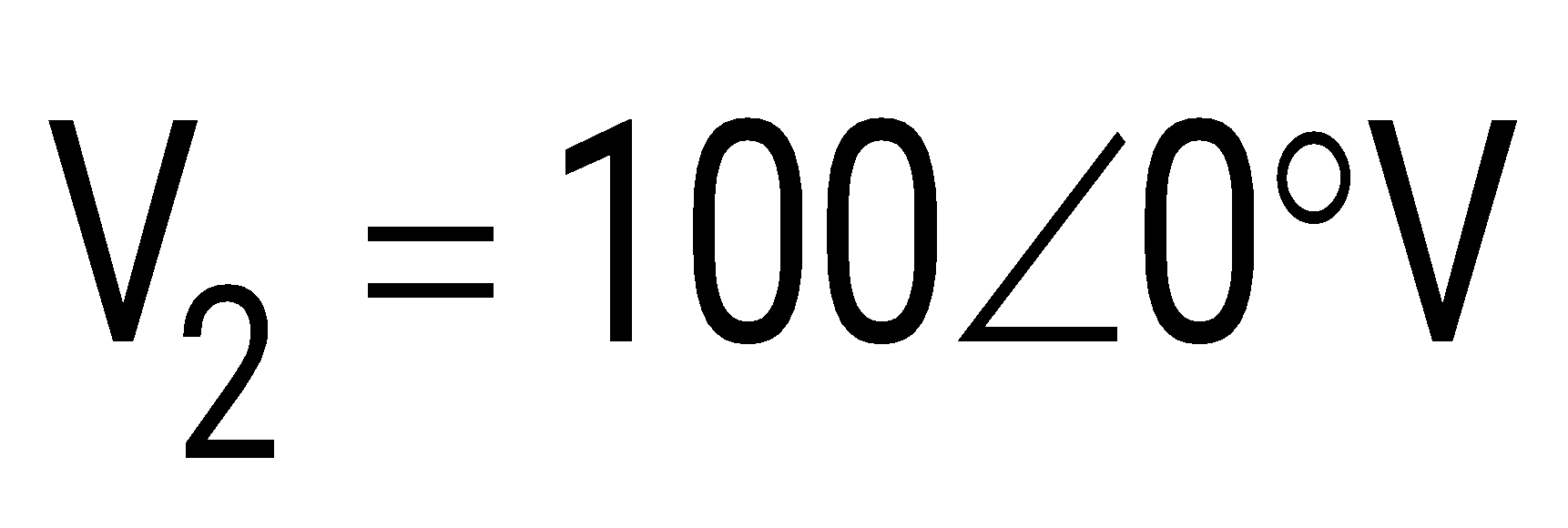

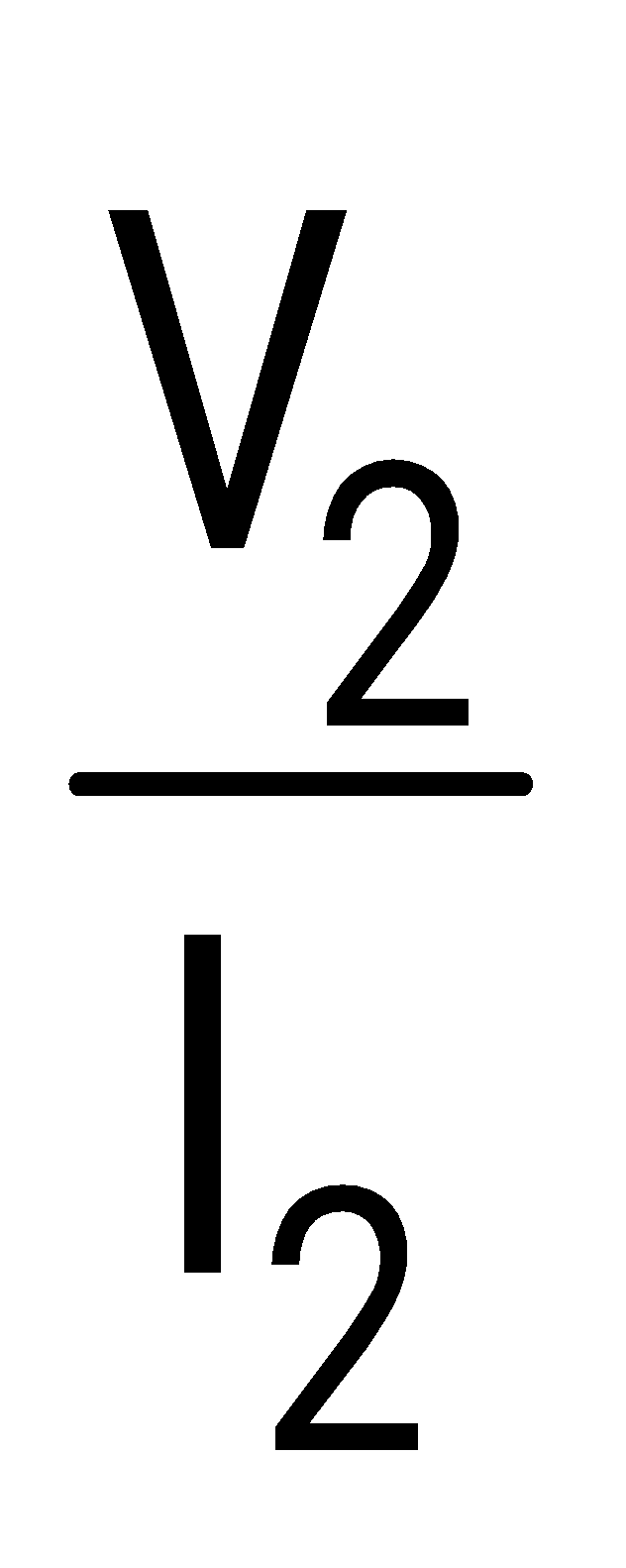

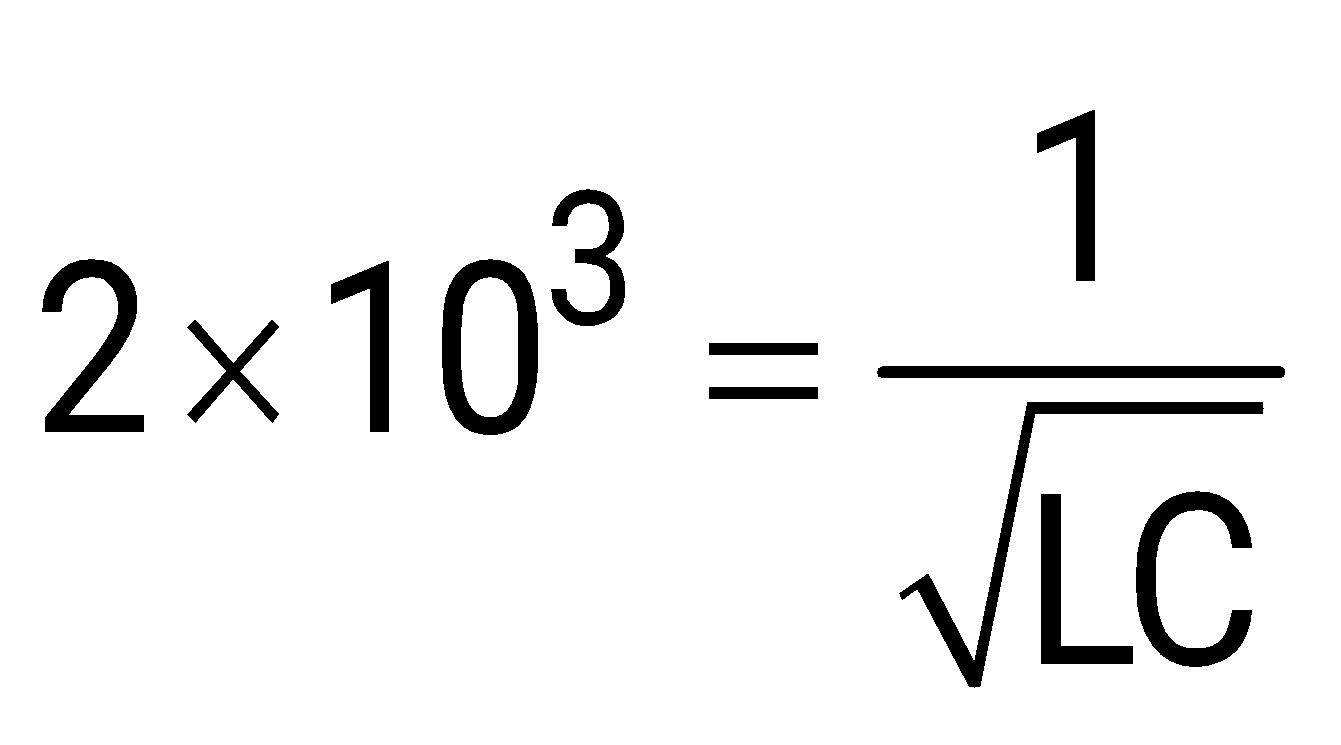

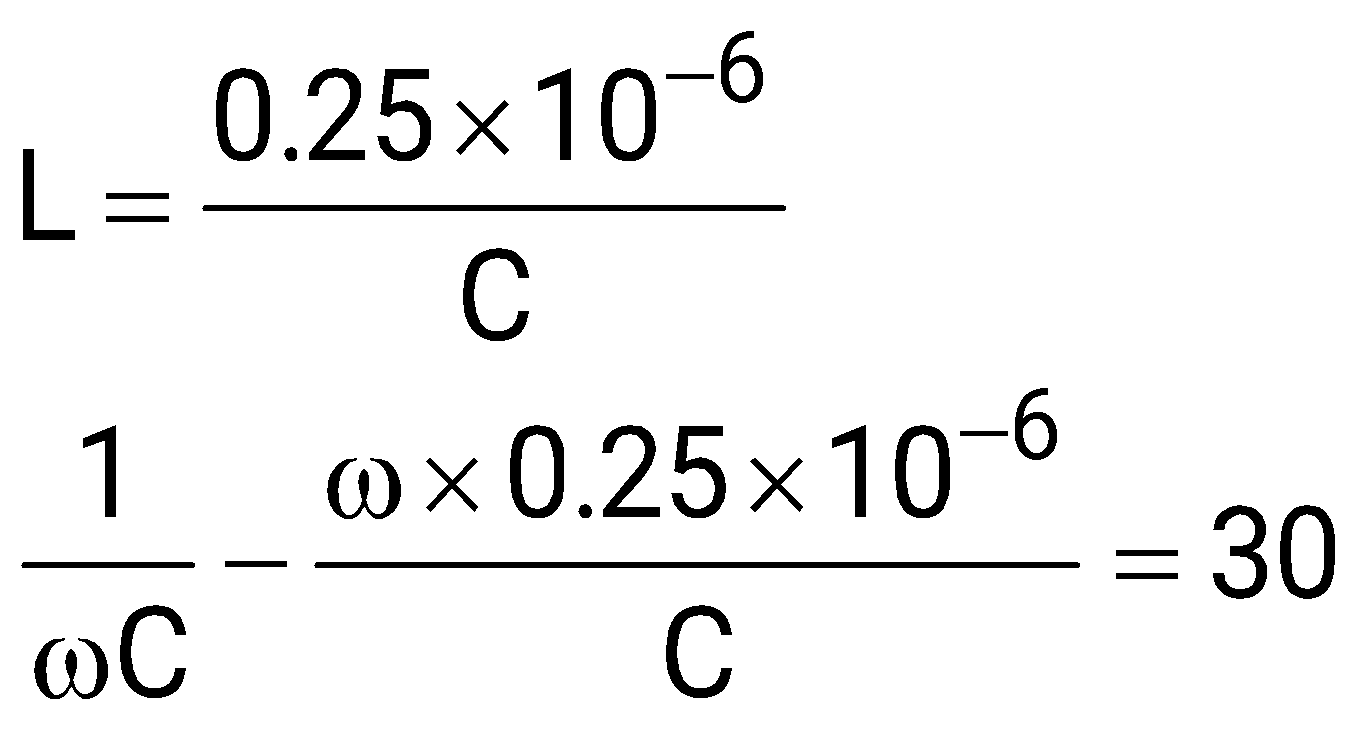

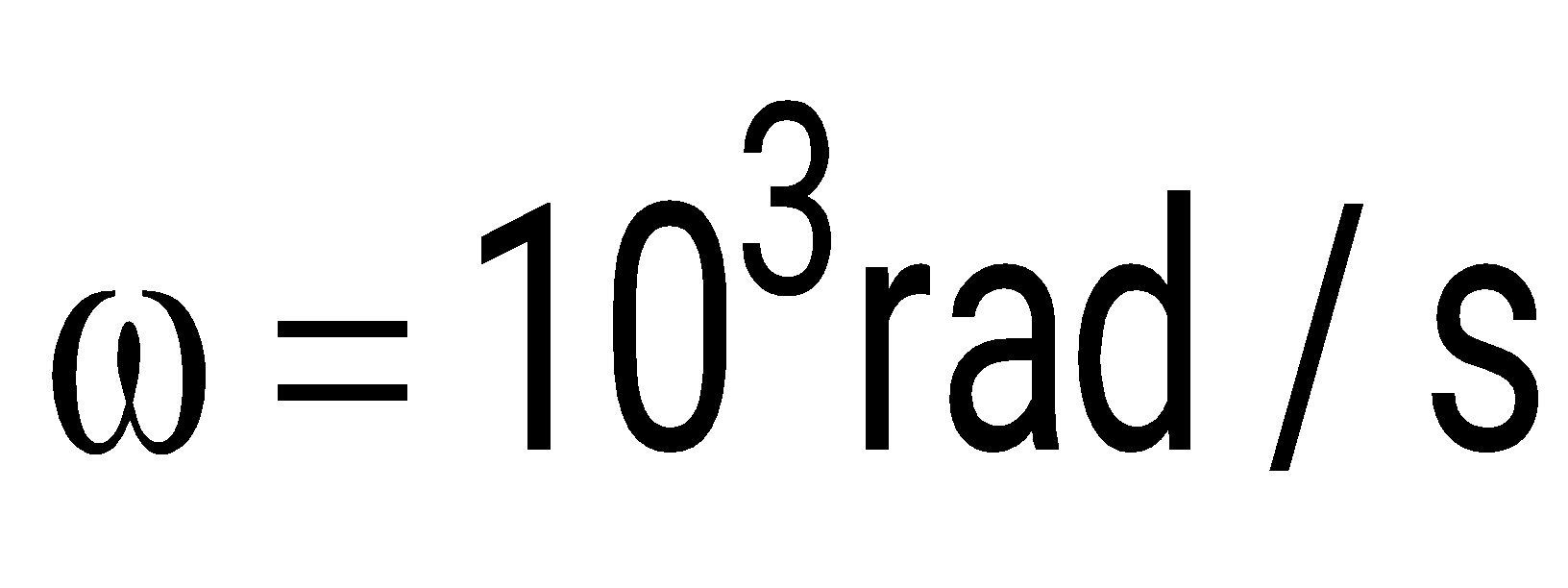

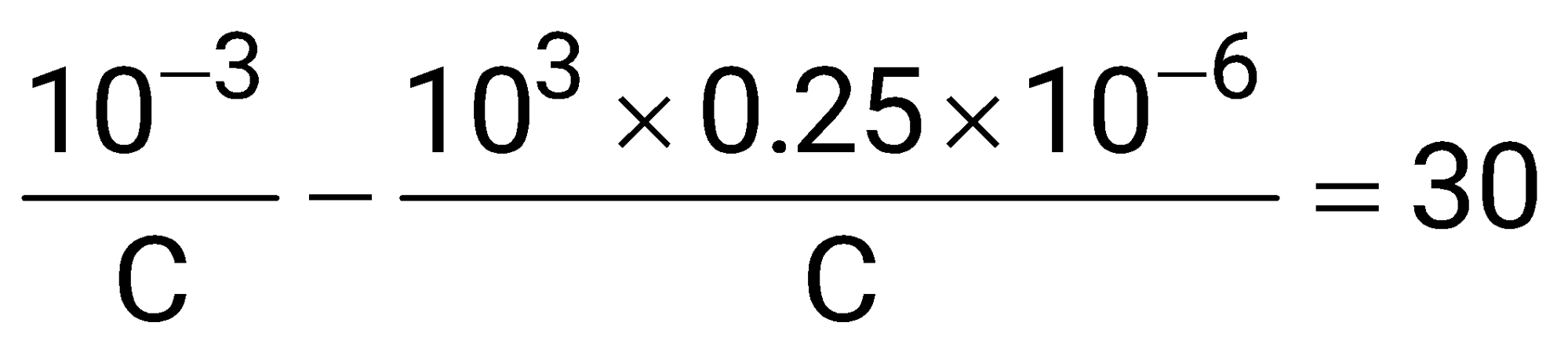

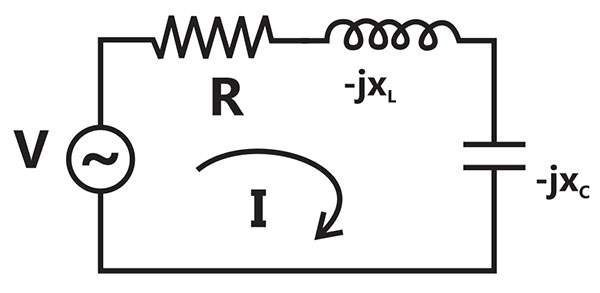

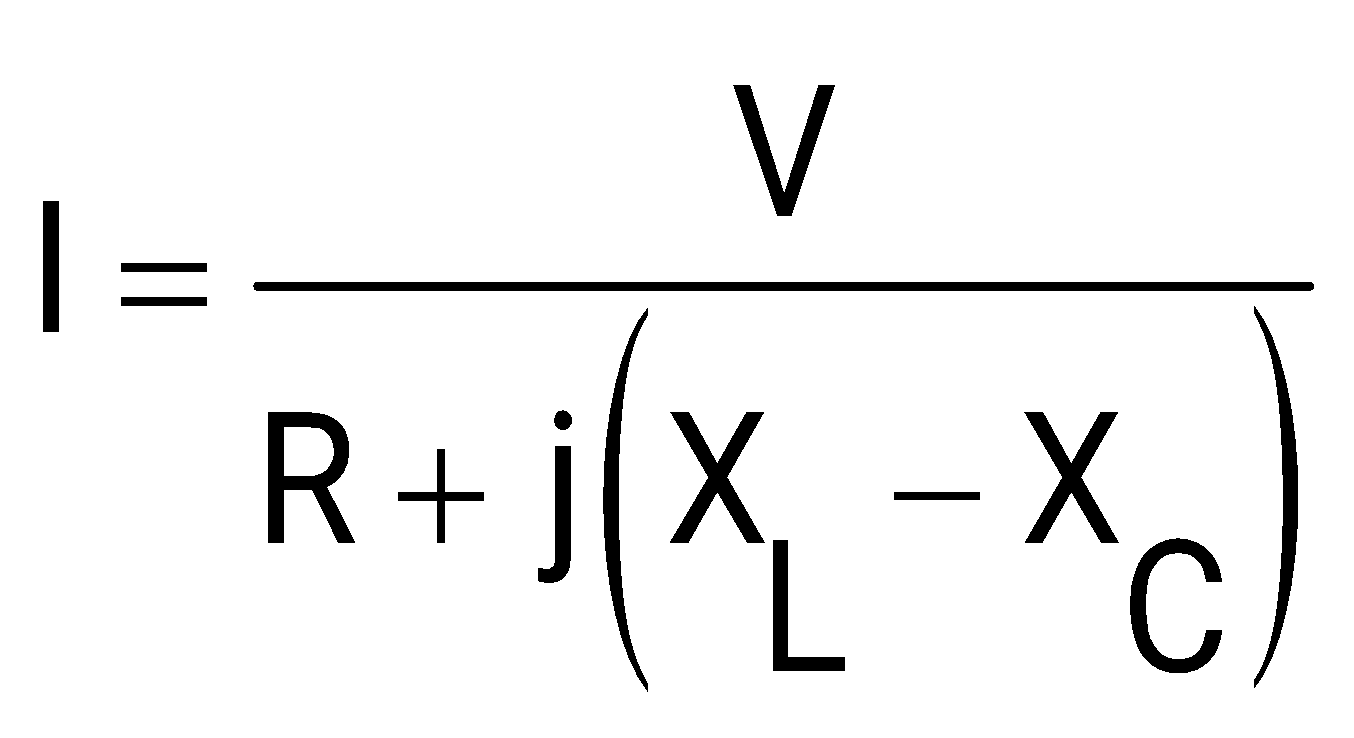

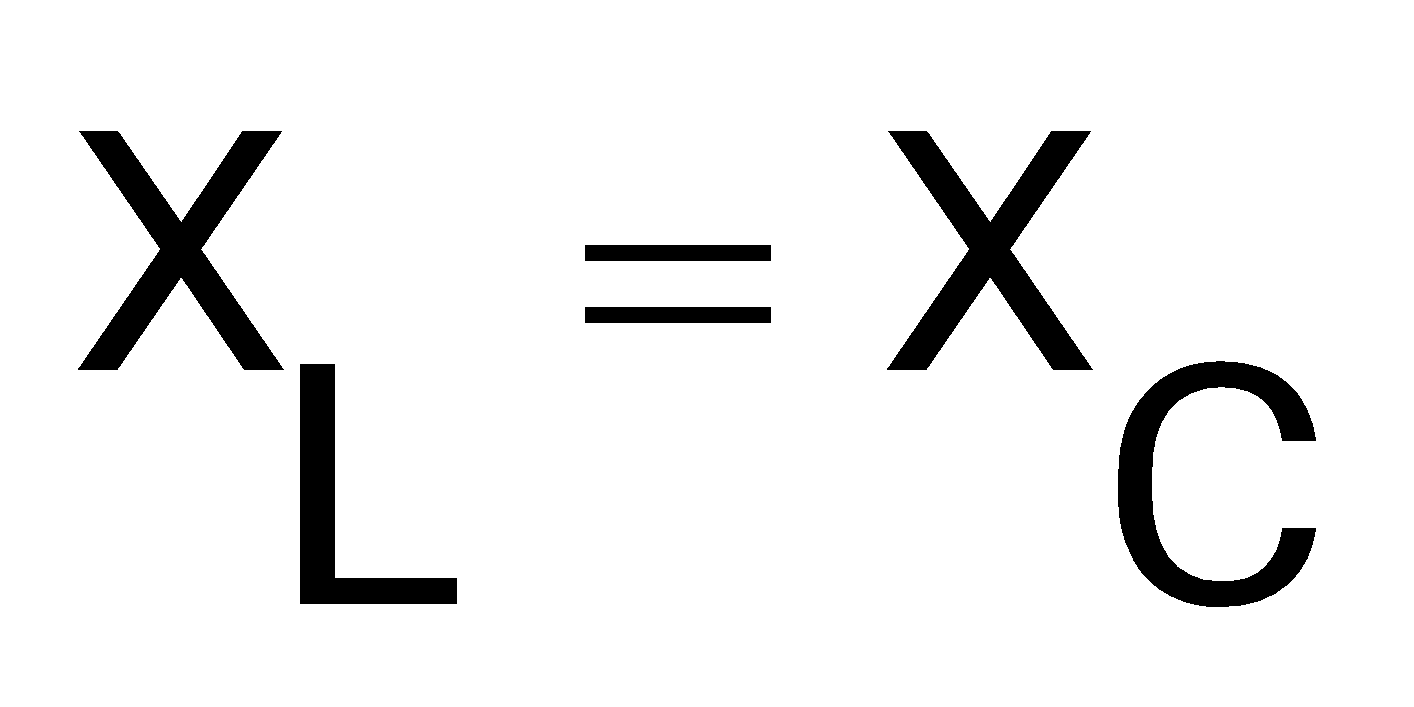

A series RLC circuit is observed at two frequencies. At , we note that source voltage results in a current . At , the source voltage results in a current . The closest values for R, L, C out of the following options are

Given, and

Since both the current & voltage are in phase, it is resonance condition. Under resonance condition,

Net Impedance, Z = R

R == 50 Ω

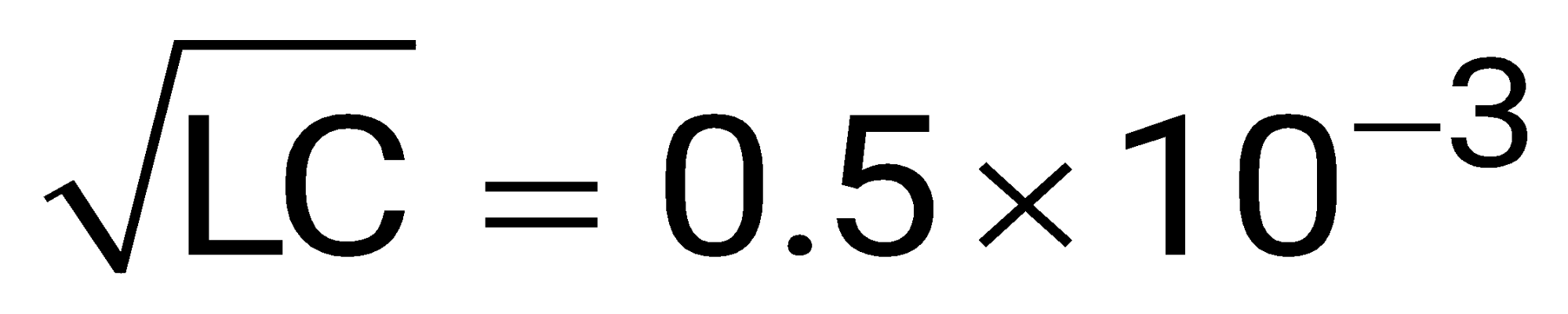

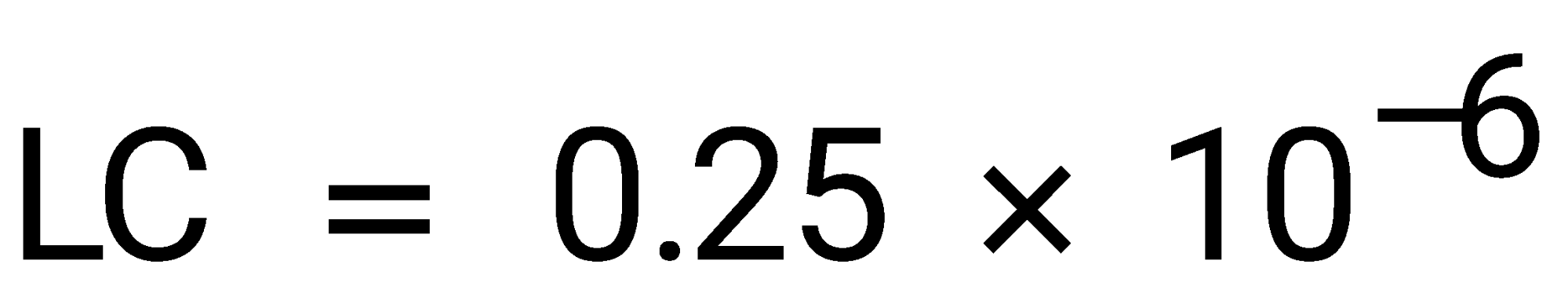

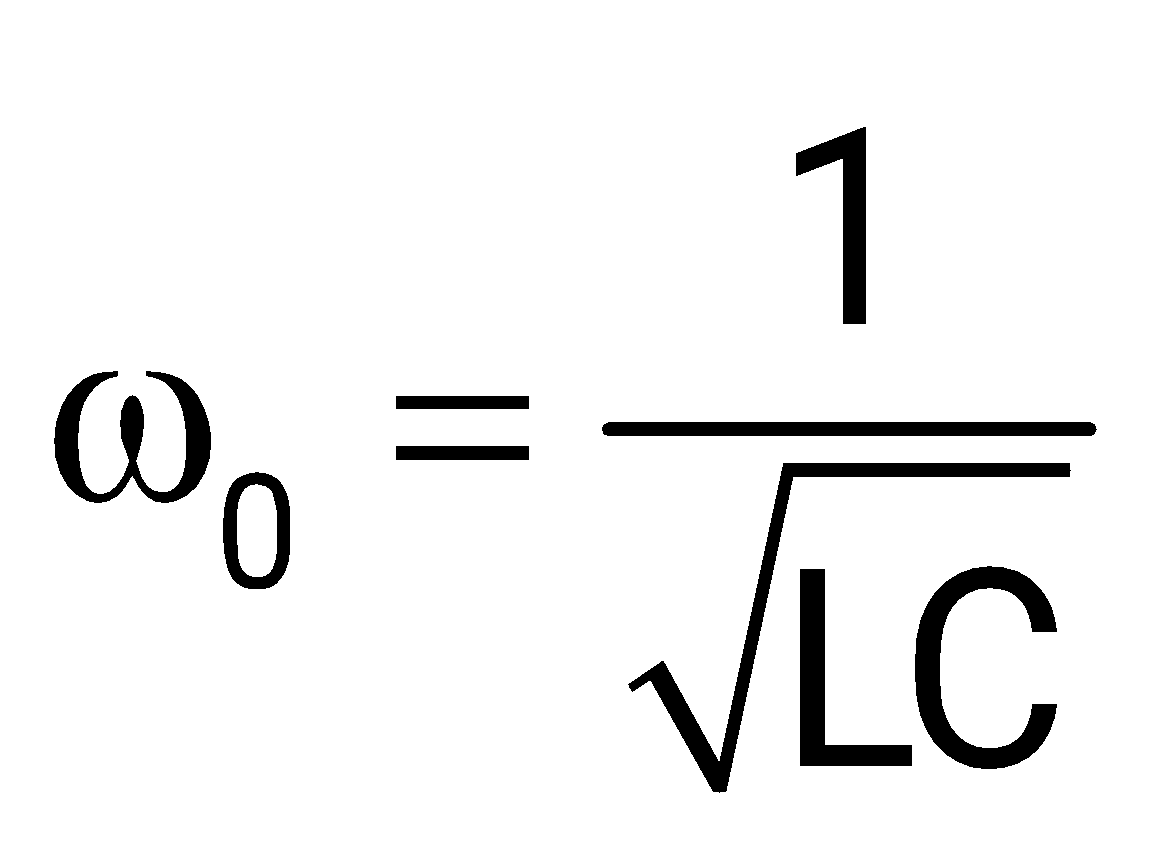

Resonance frequency, =

-----------(1)

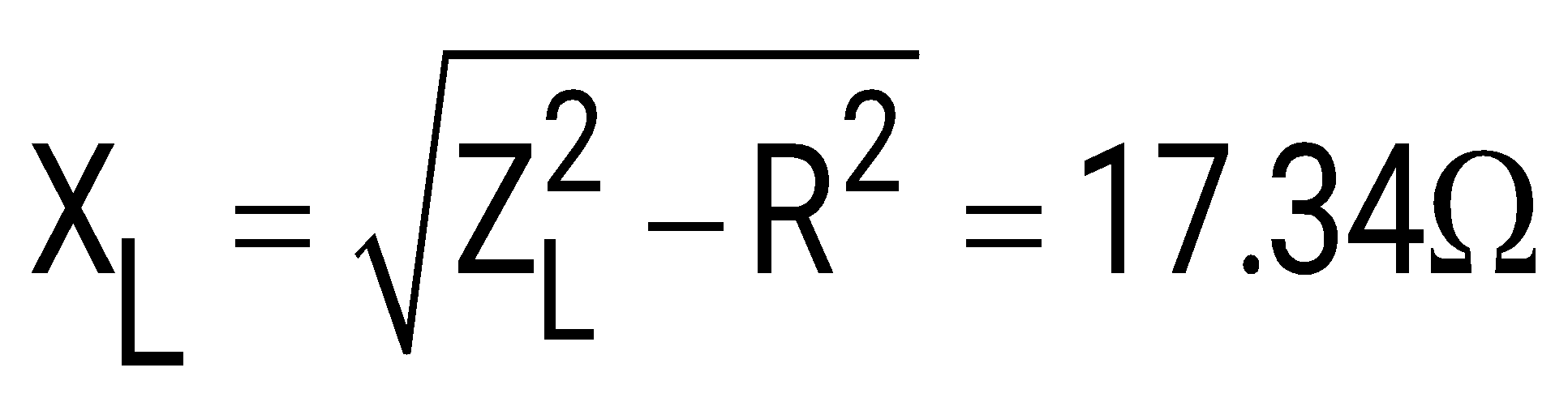

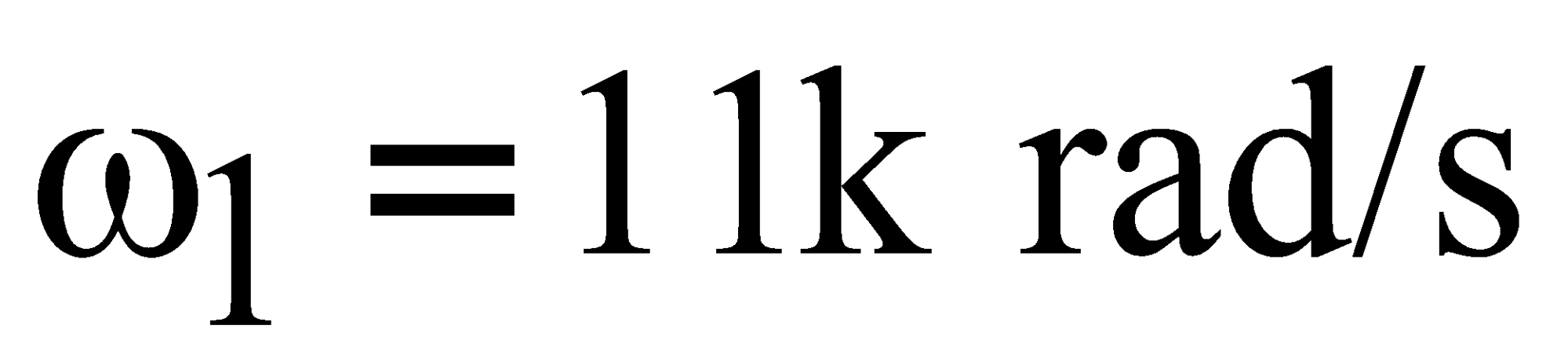

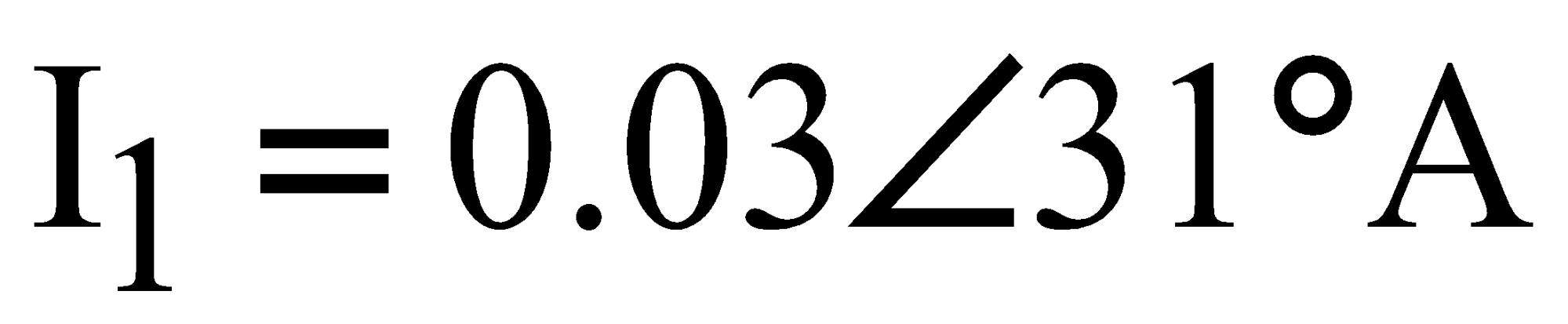

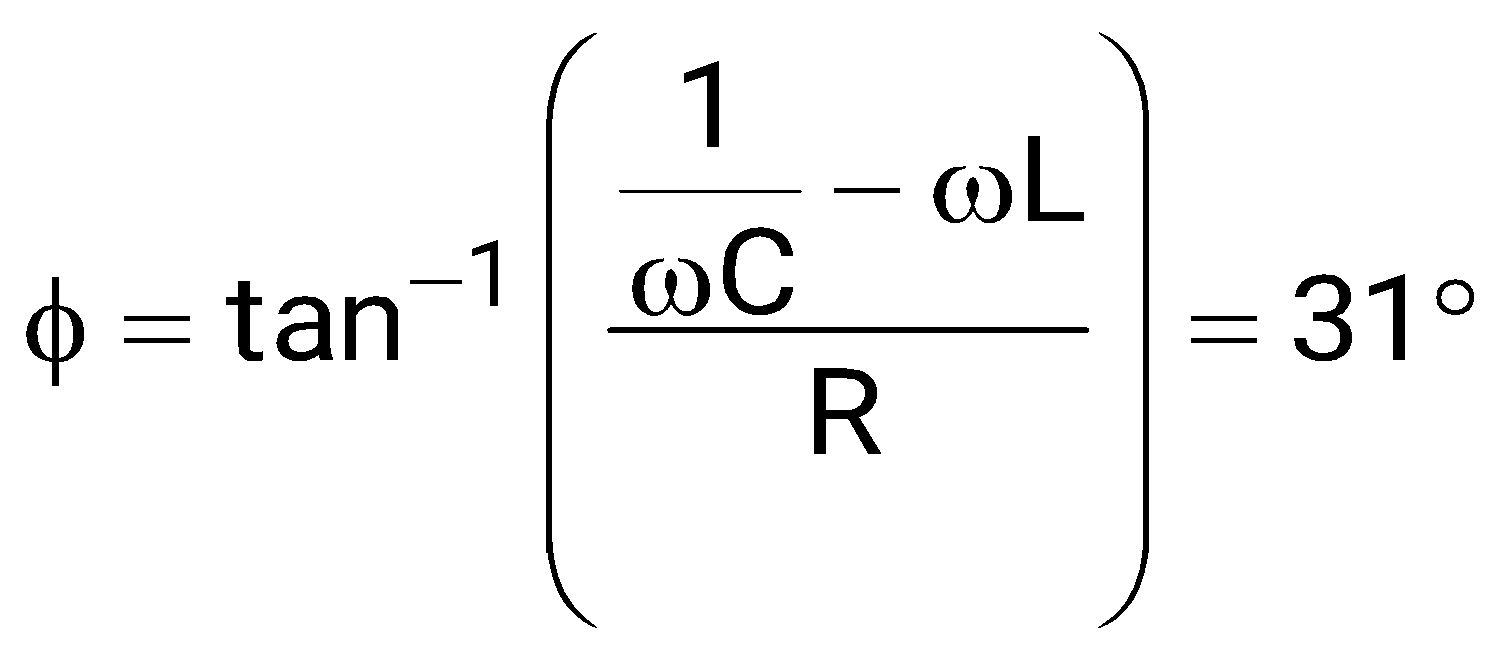

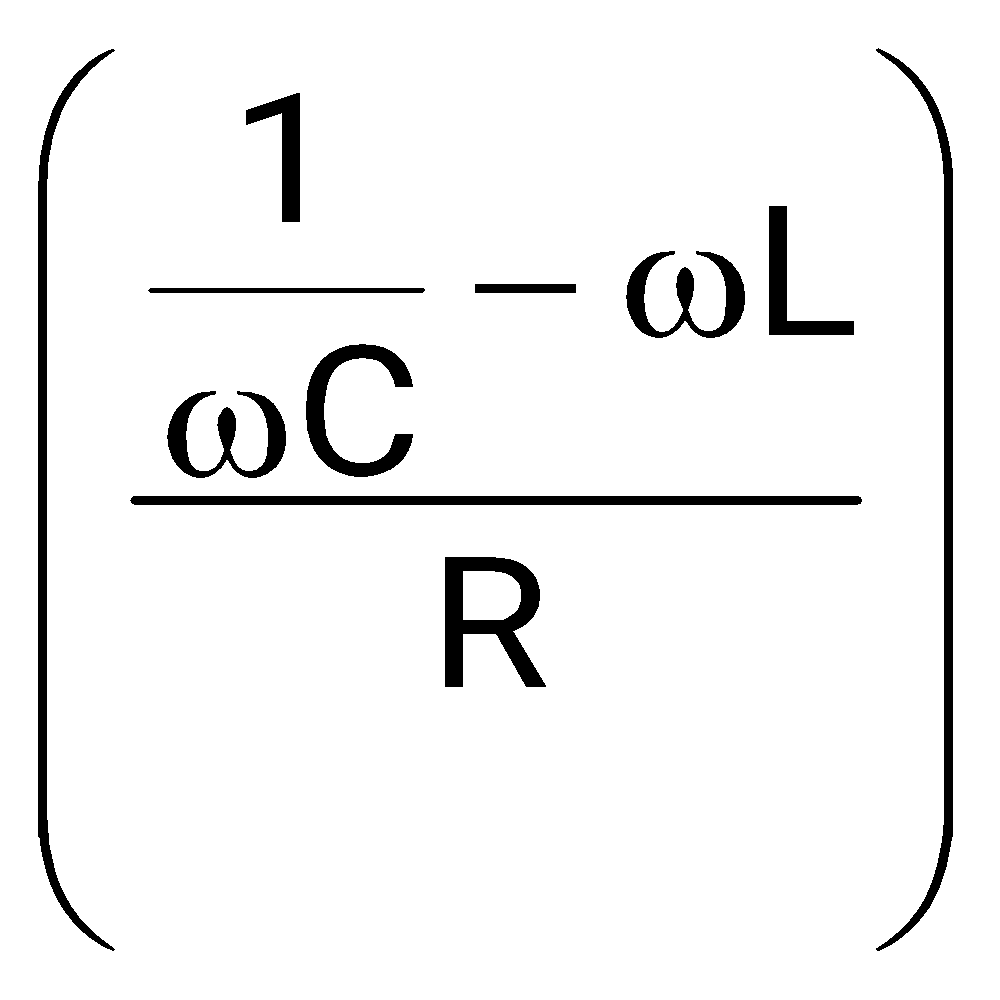

At = 1krad/s, current is leading by an angle of 31°

So, net impedance is capacitive.

= 0.6

= 50 × 0.6 = 30

From (1)

Since,

C = 25 μF

From (1), L = 10mH

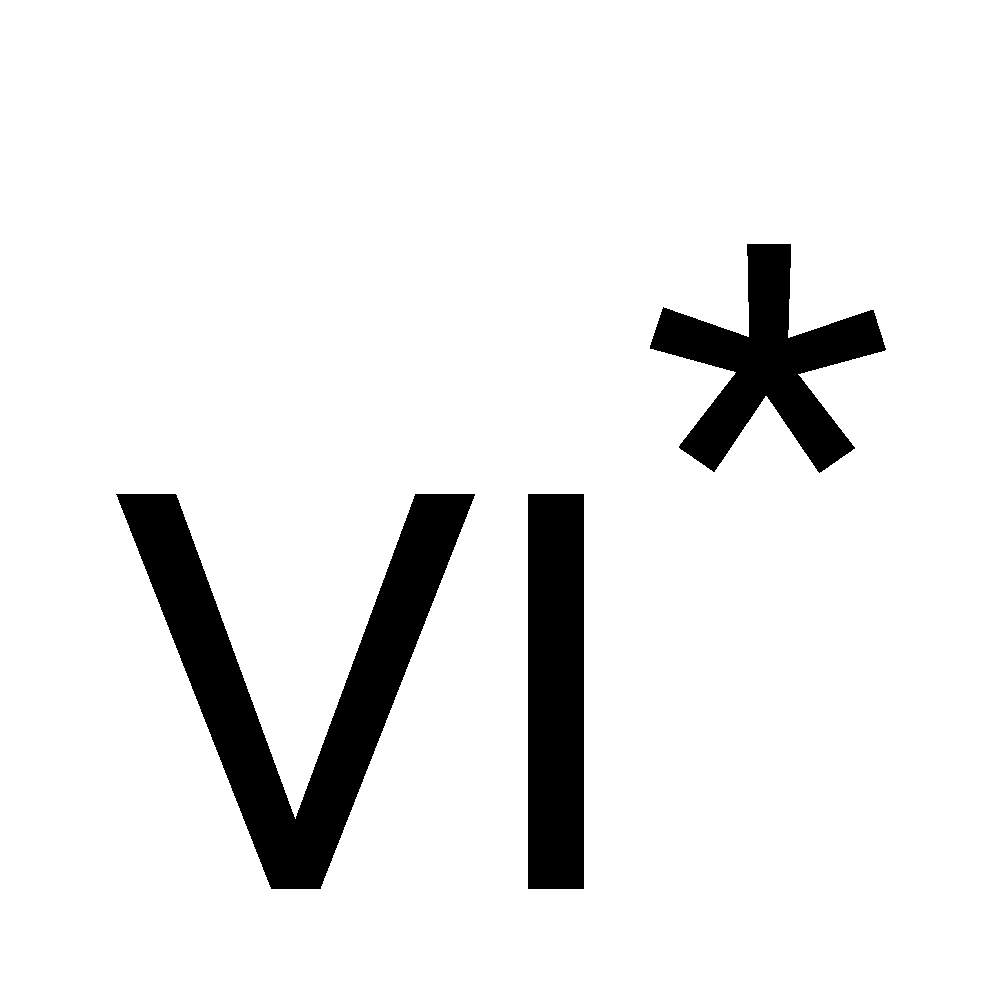

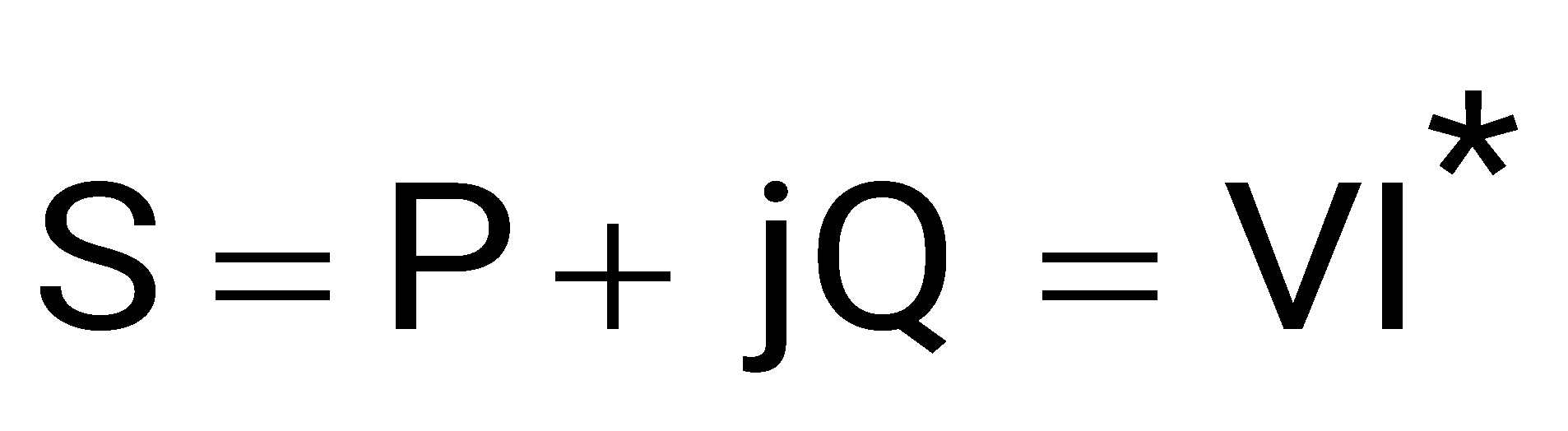

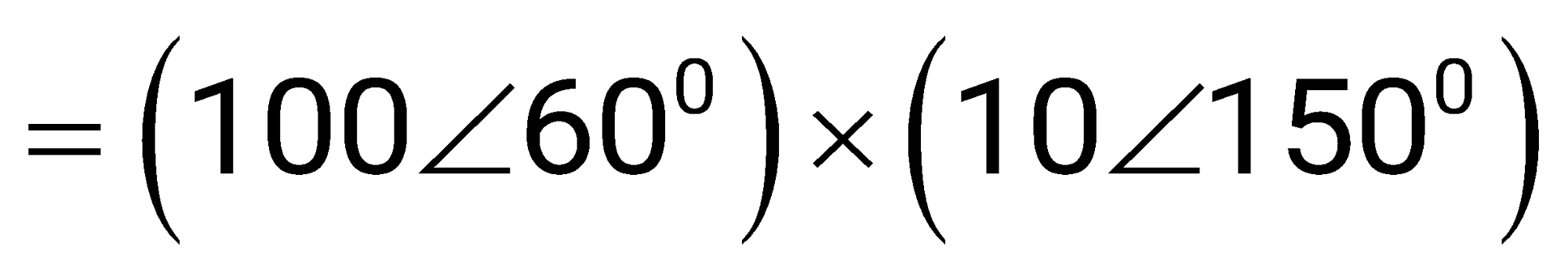

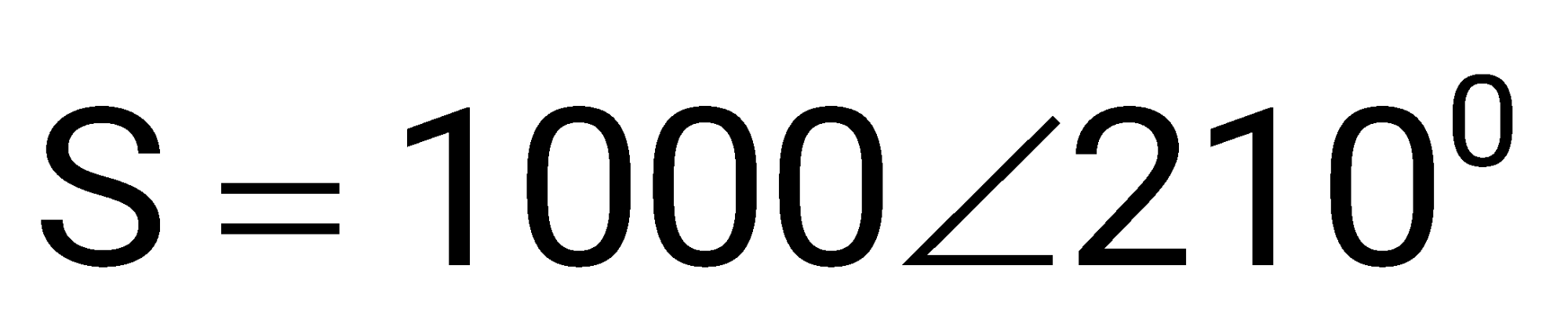

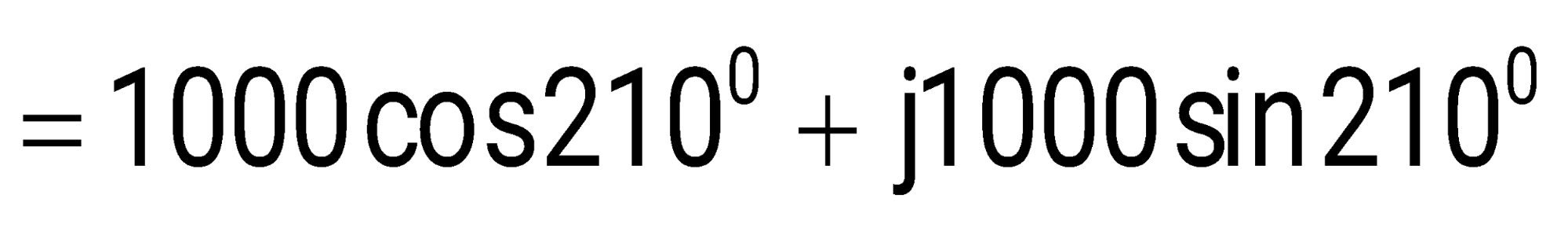

A single-phase load is supplied by a single –phase voltage source. If the current flowing from the Load to the source is and if the voltage at the load terminals is , then the

The configuration of the given system is shown below,

Since, the current is coming out of the positive terminal of load the load is said to be delivering power.

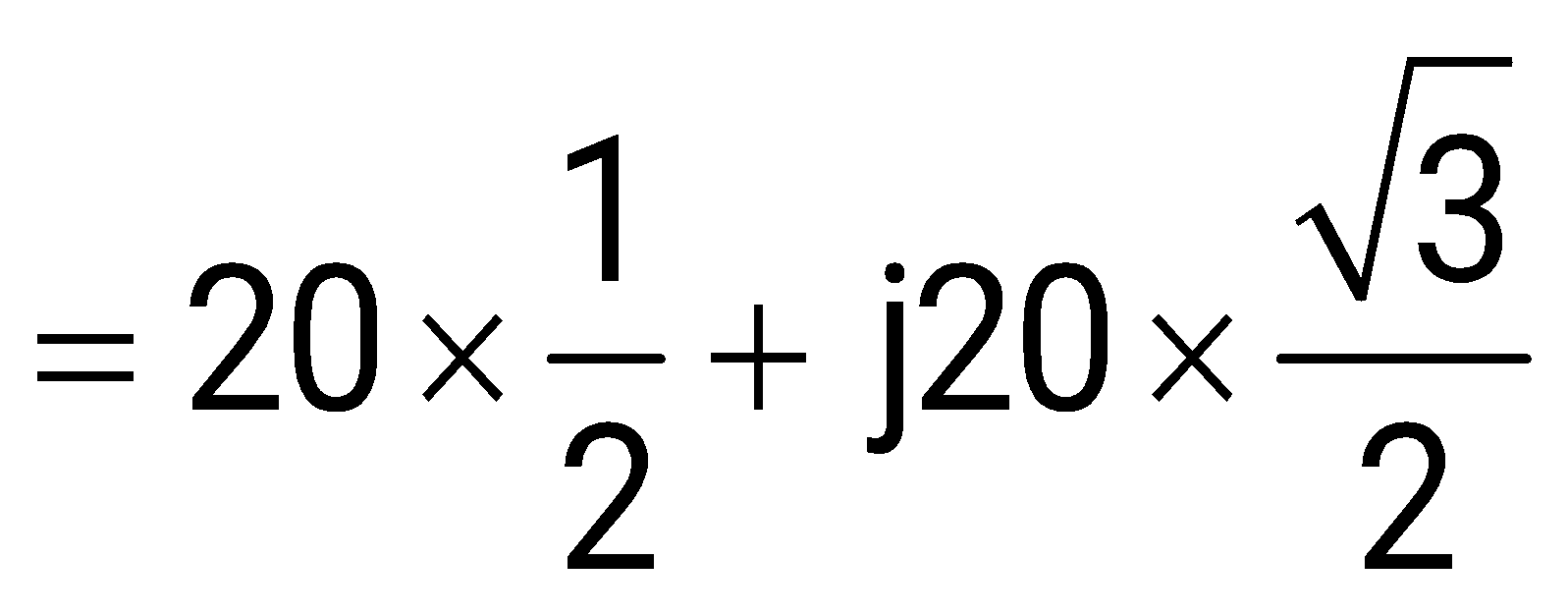

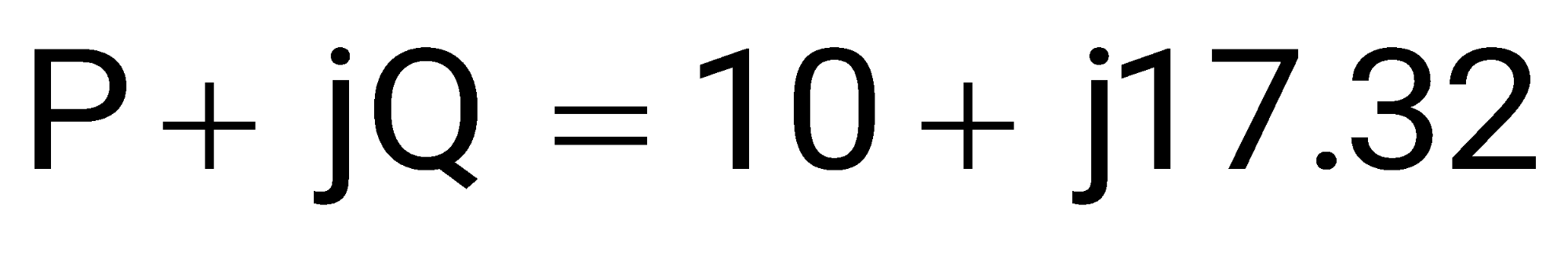

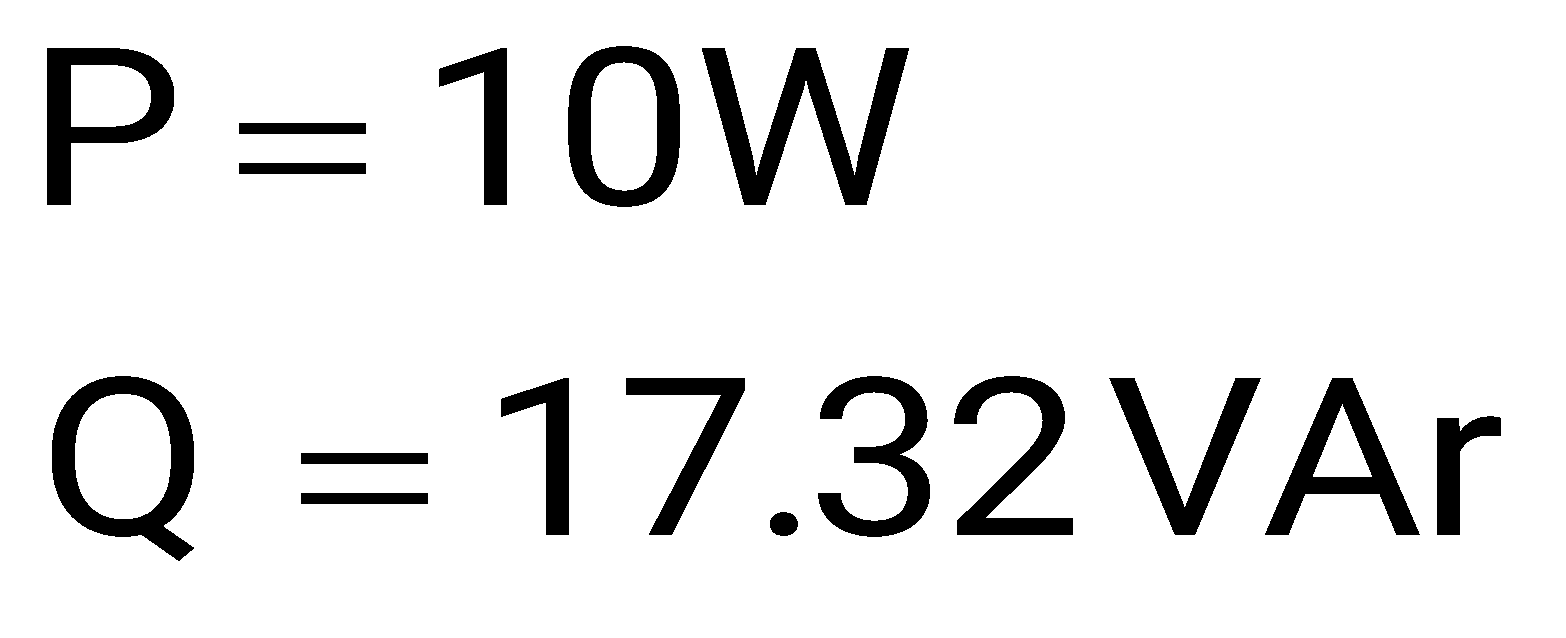

Complex power delivered by the load is =

Both P & Q are negative means load absorbs active power as well as reactive power from the source.

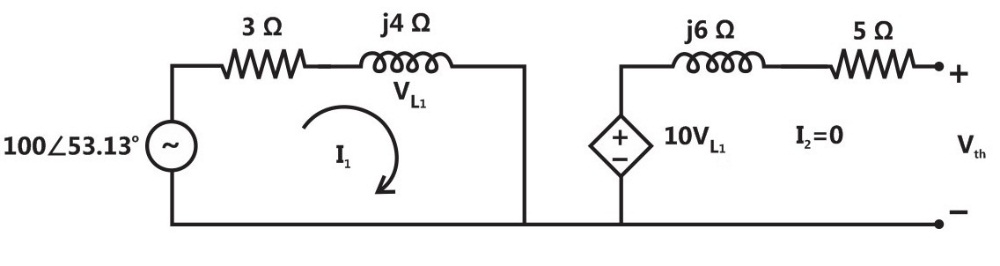

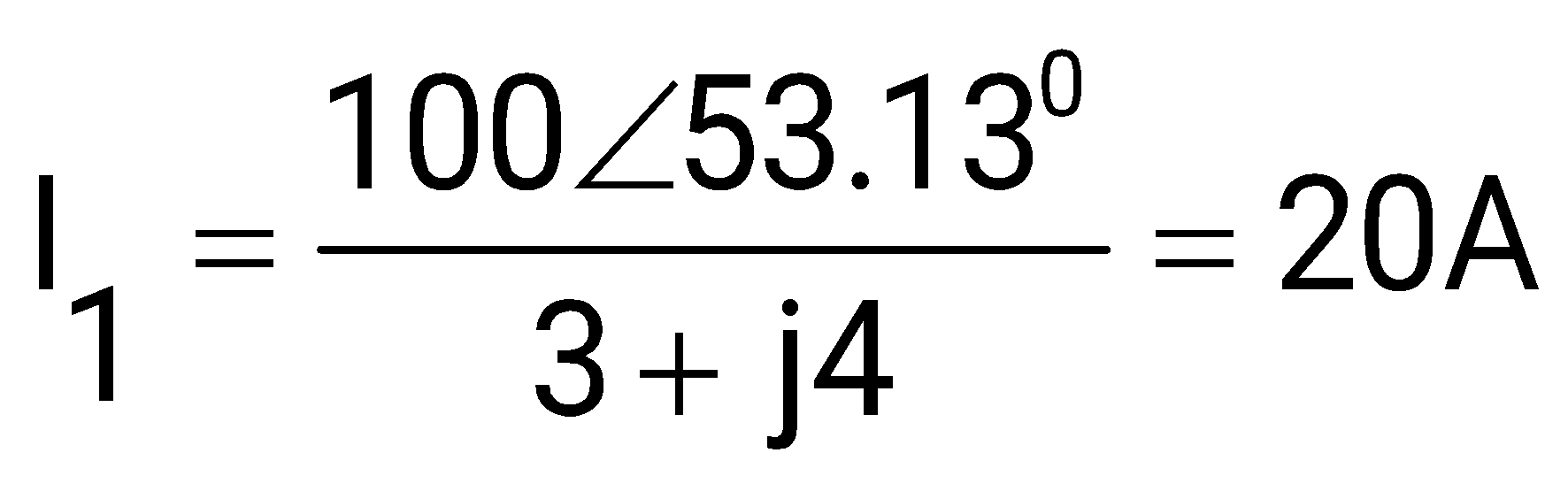

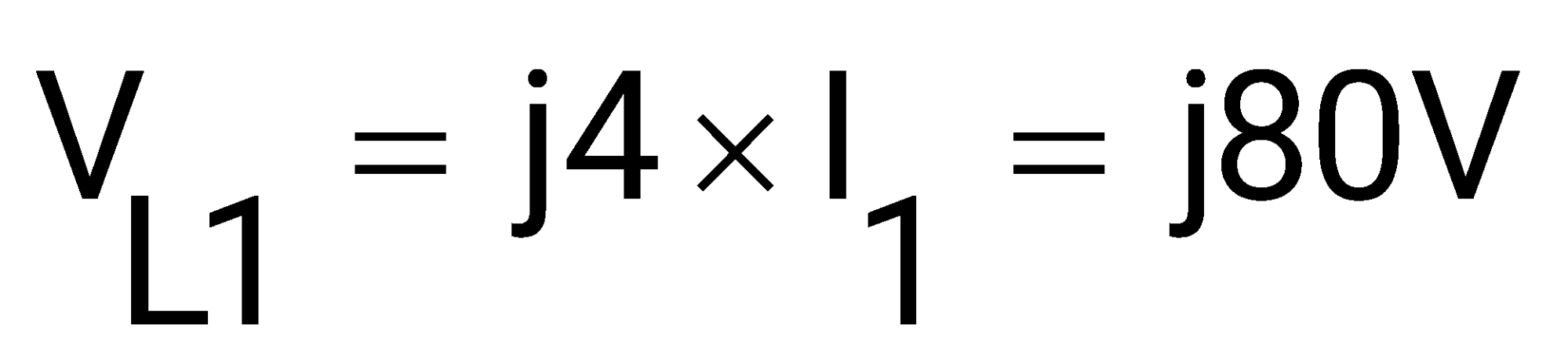

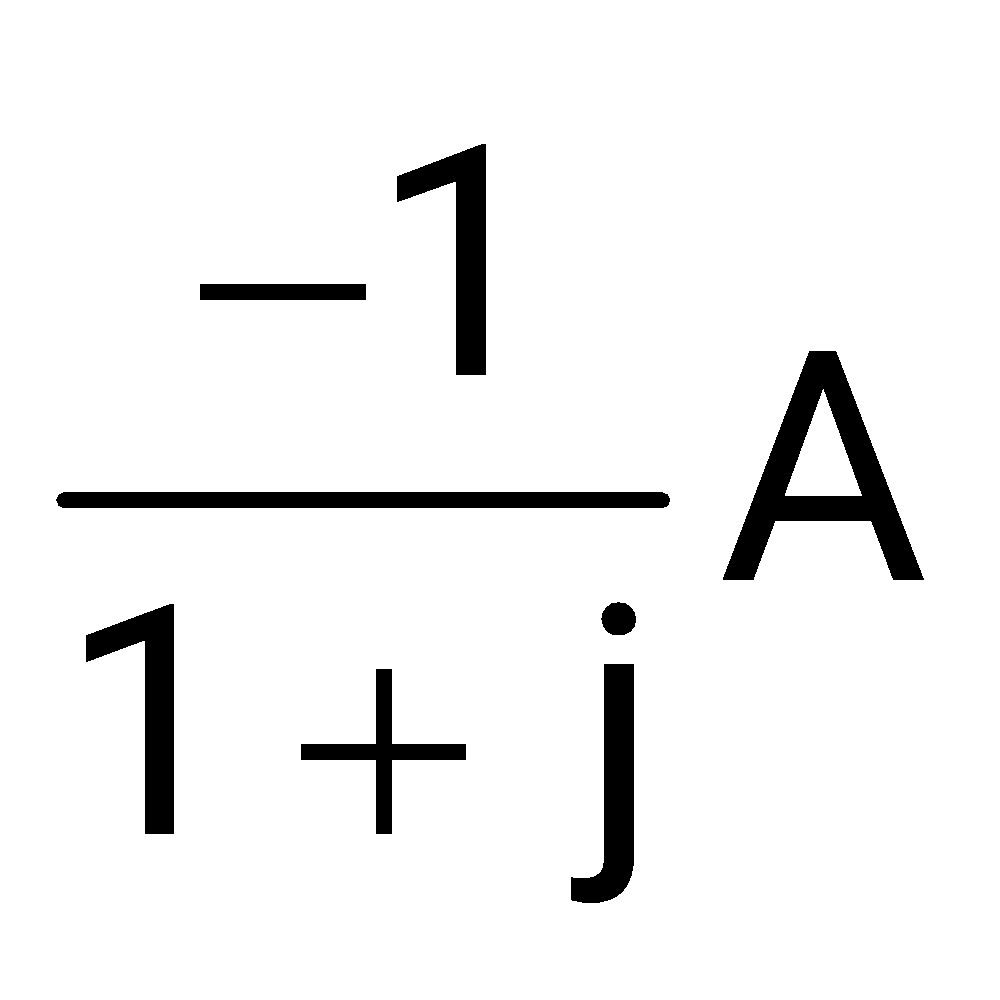

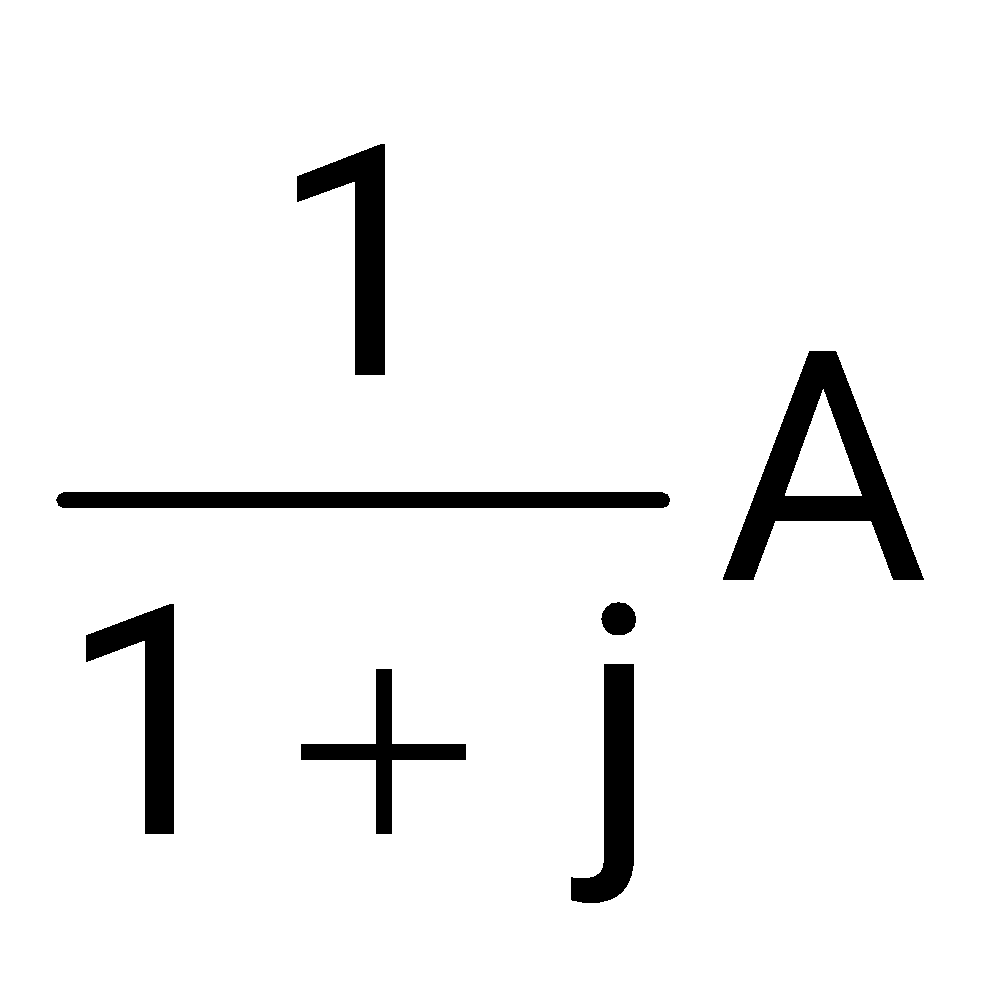

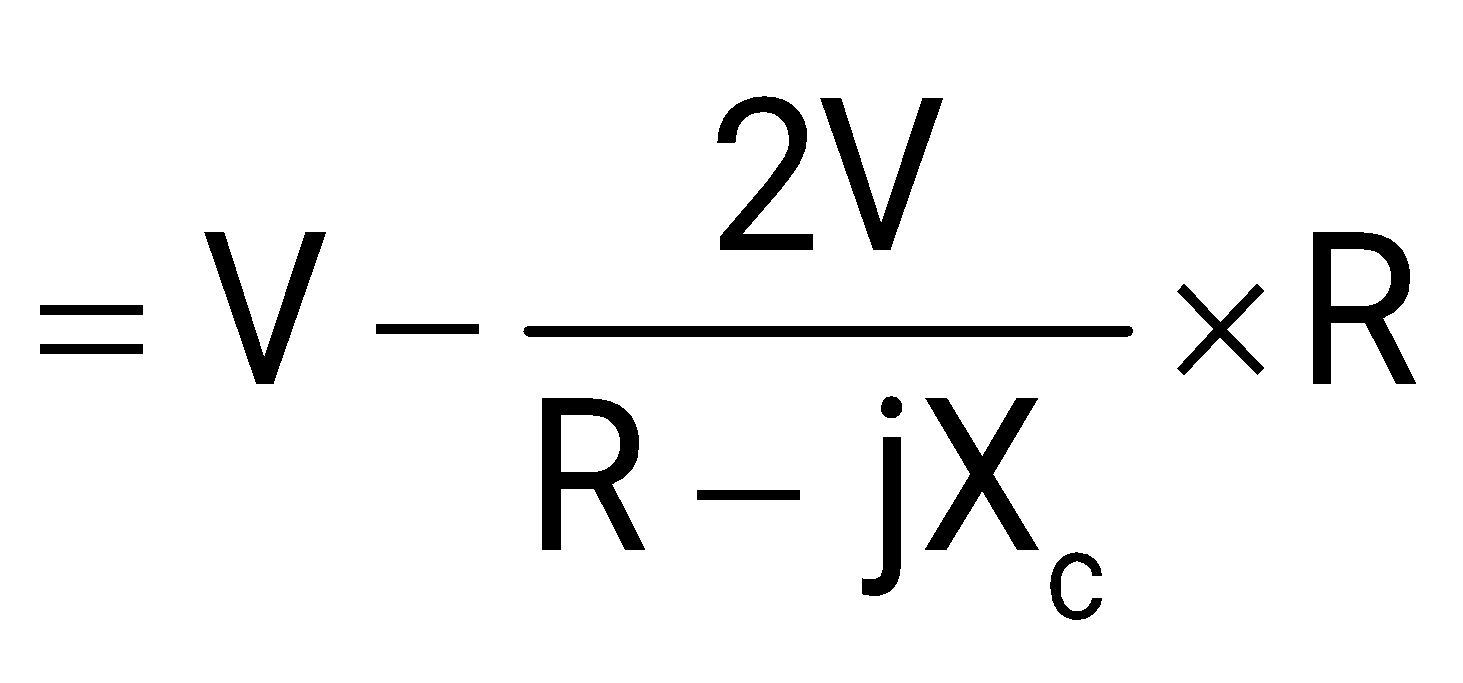

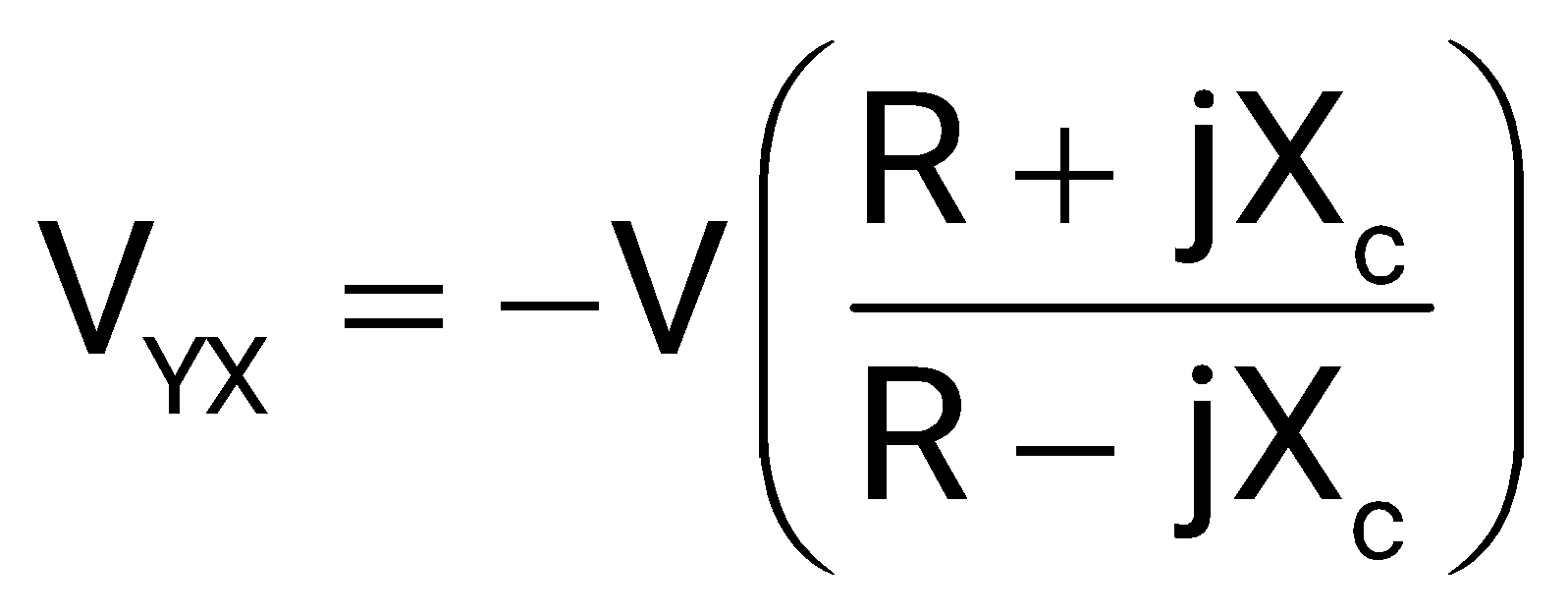

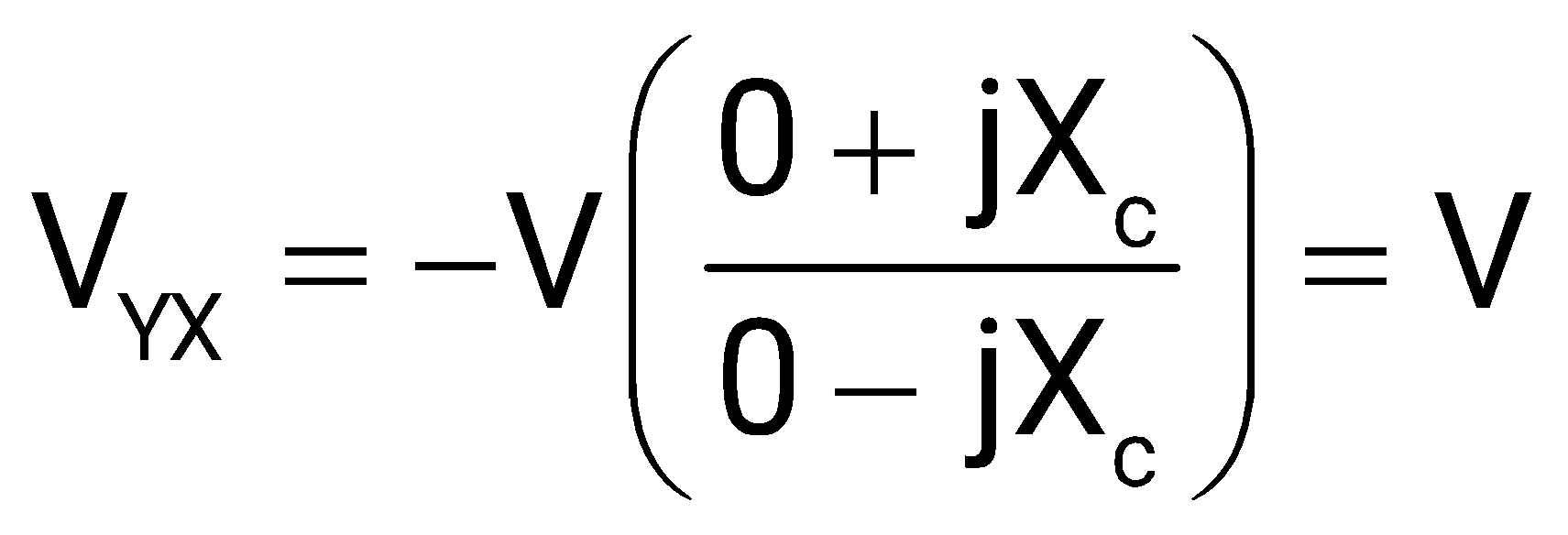

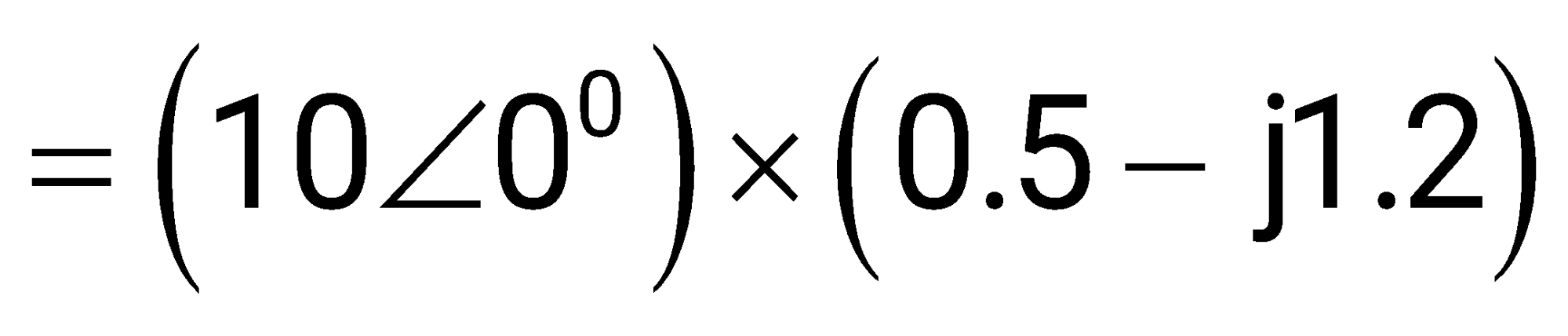

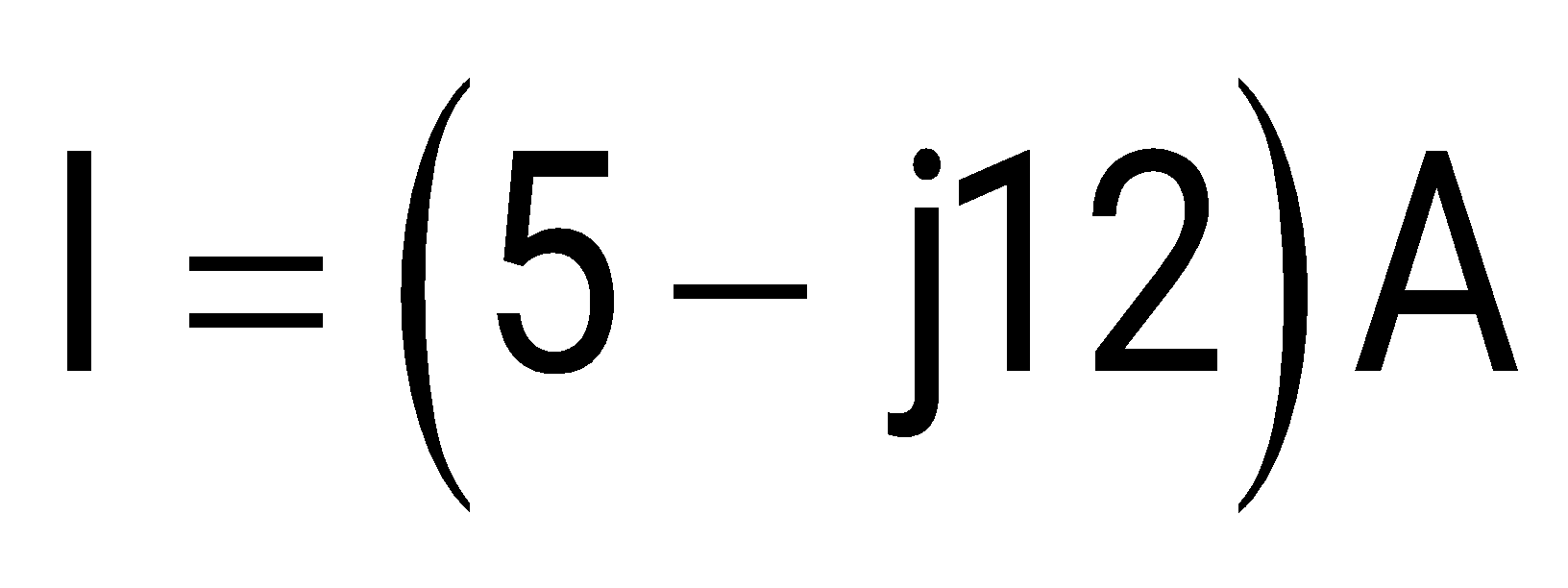

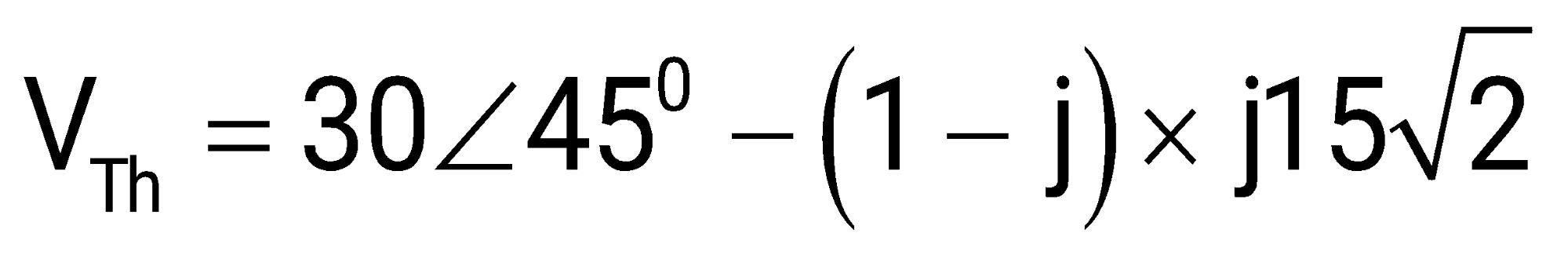

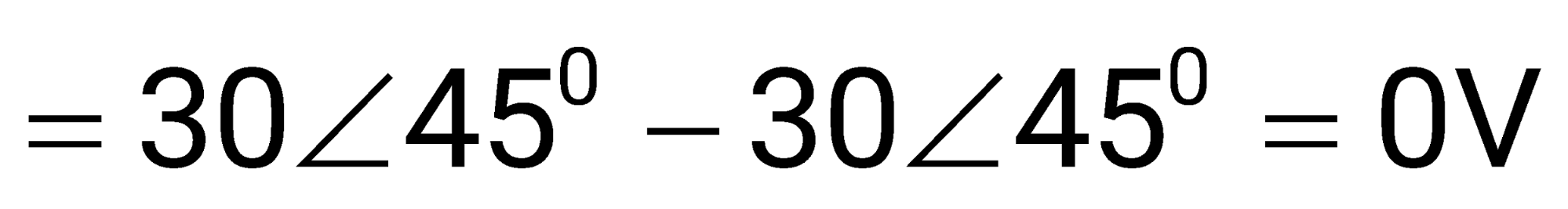

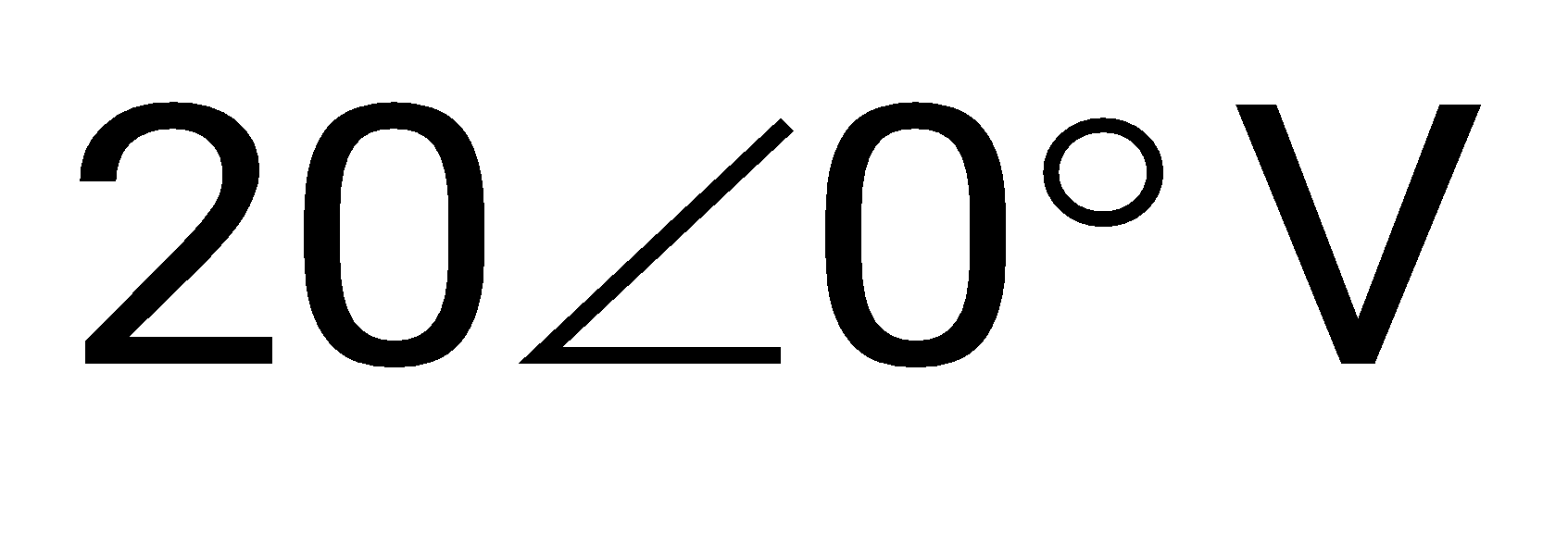

In the circuit shown below, if the source voltage then the Thevenin’s equivalent voltage in volts as seen by the load resistance is

For disconnect the load as shown below,

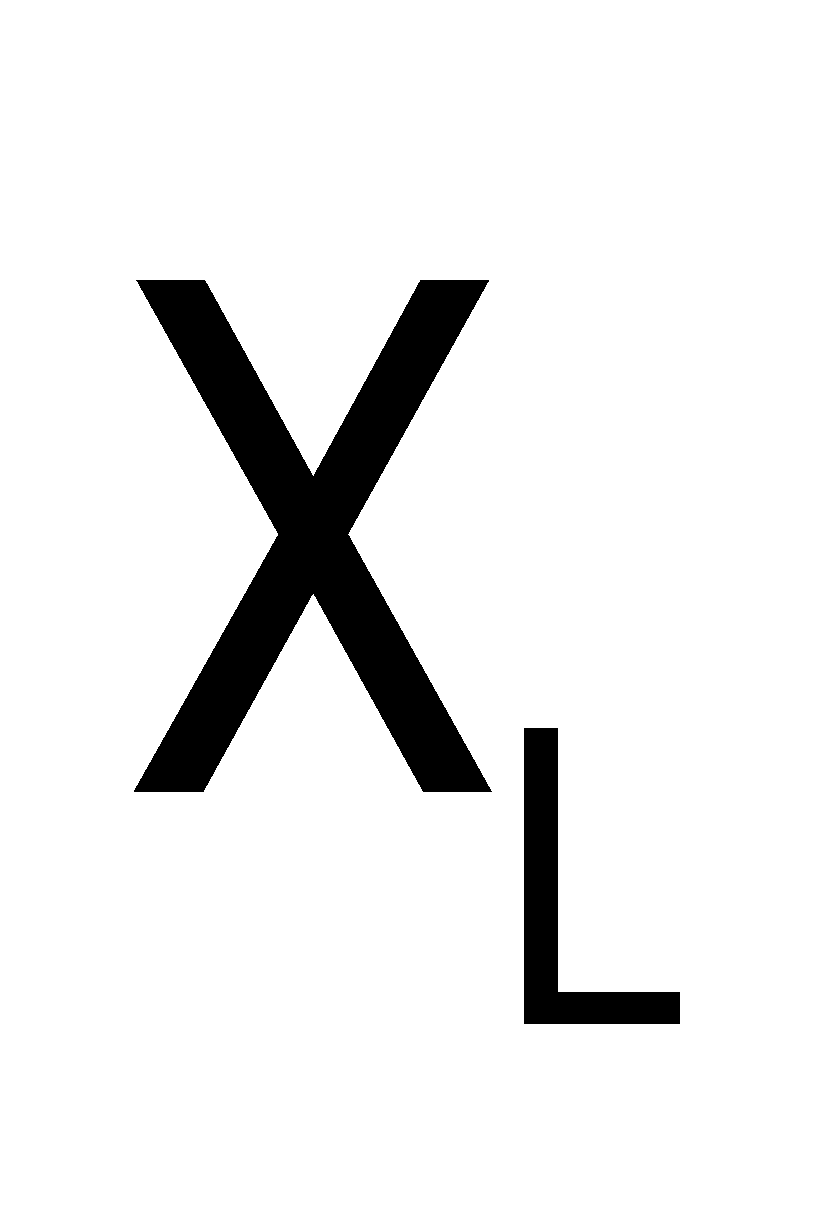

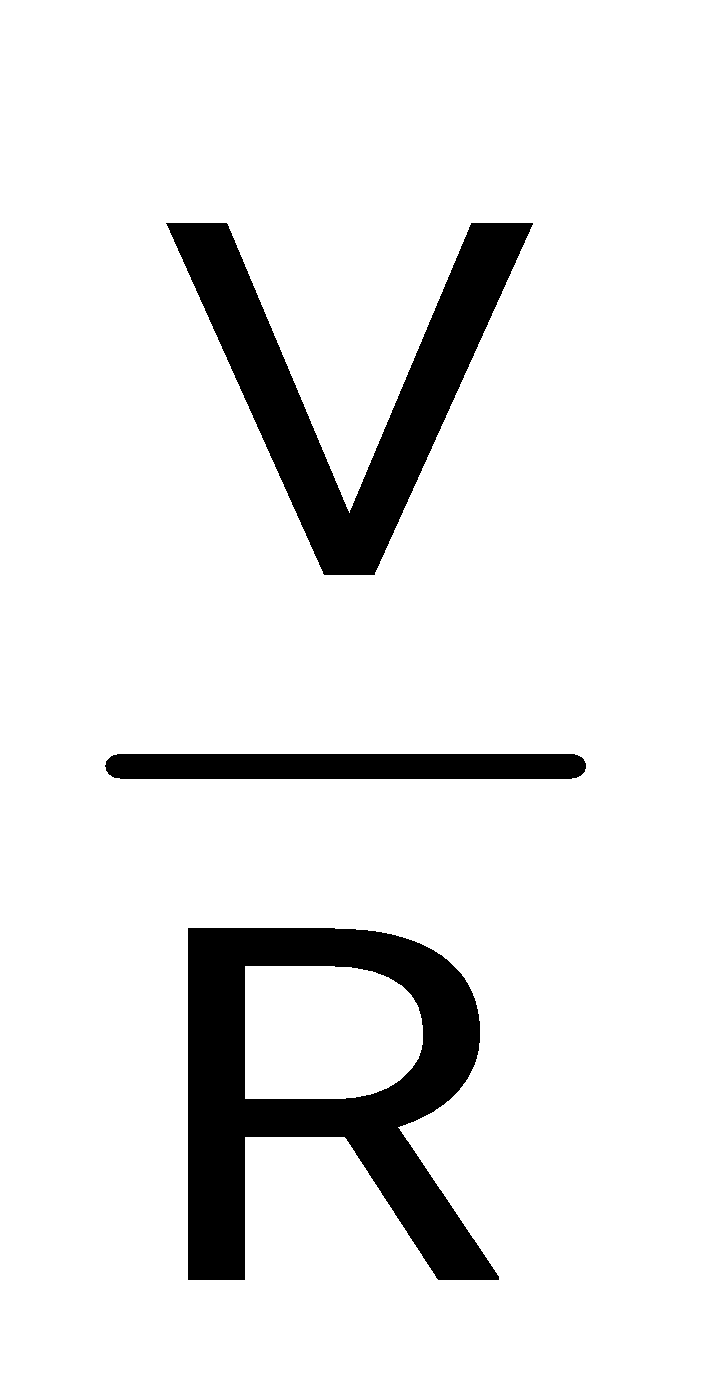

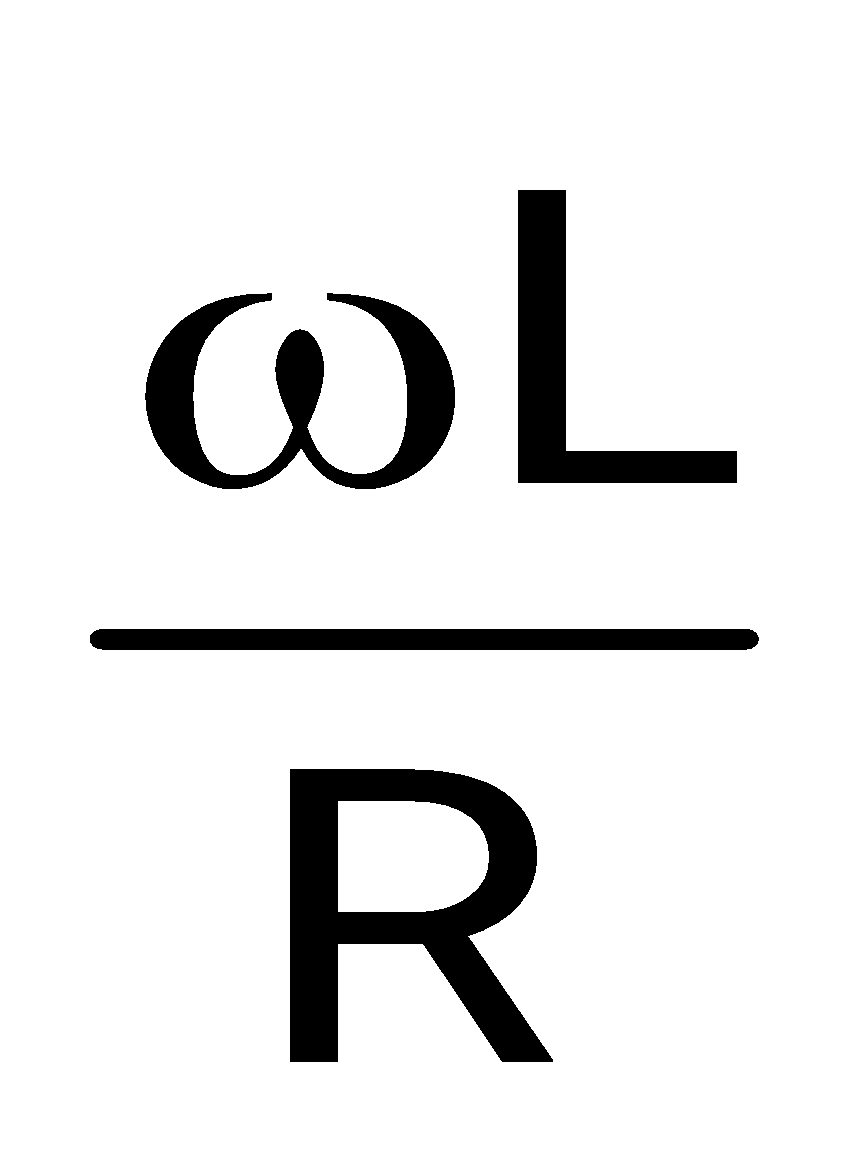

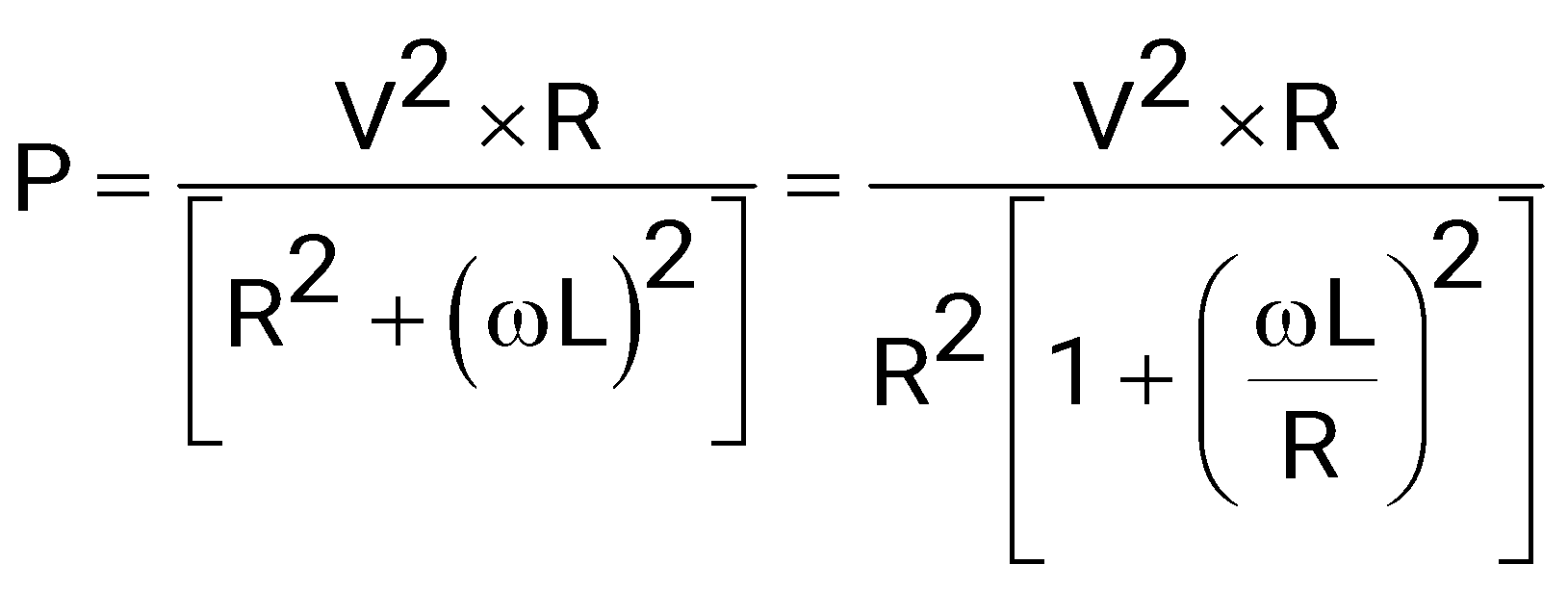

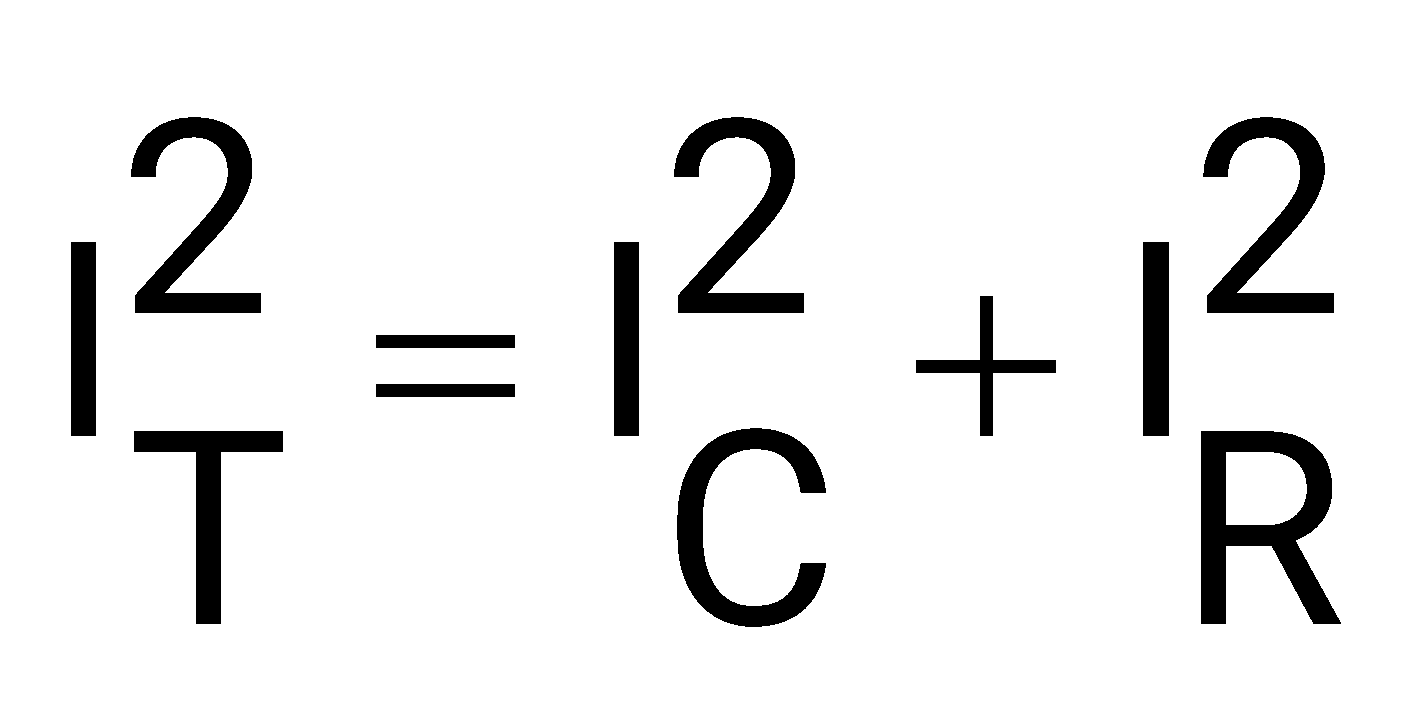

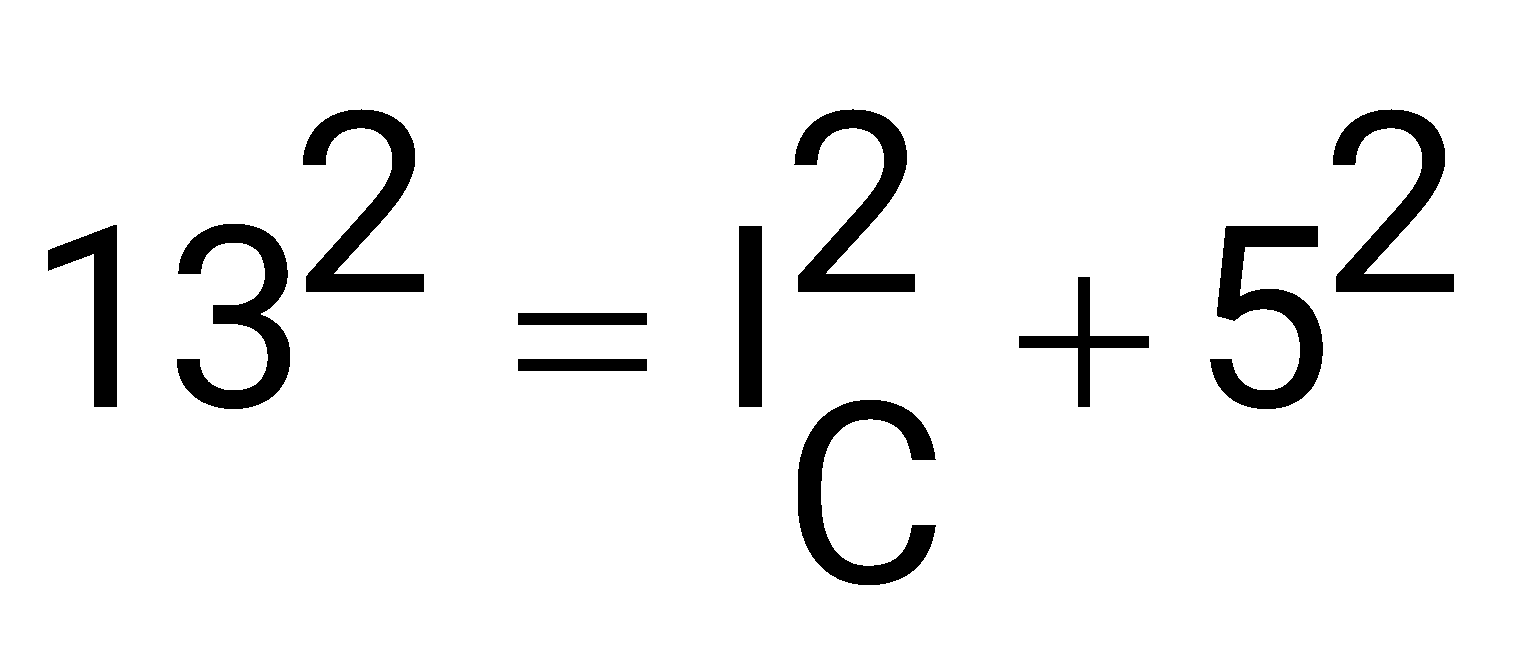

Two magnetically uncoupled inductive coils have Q factors and at the chosen operating frequency. Their respective resistances are and . When connected in series, their effective Q factor at the same operating frequency is

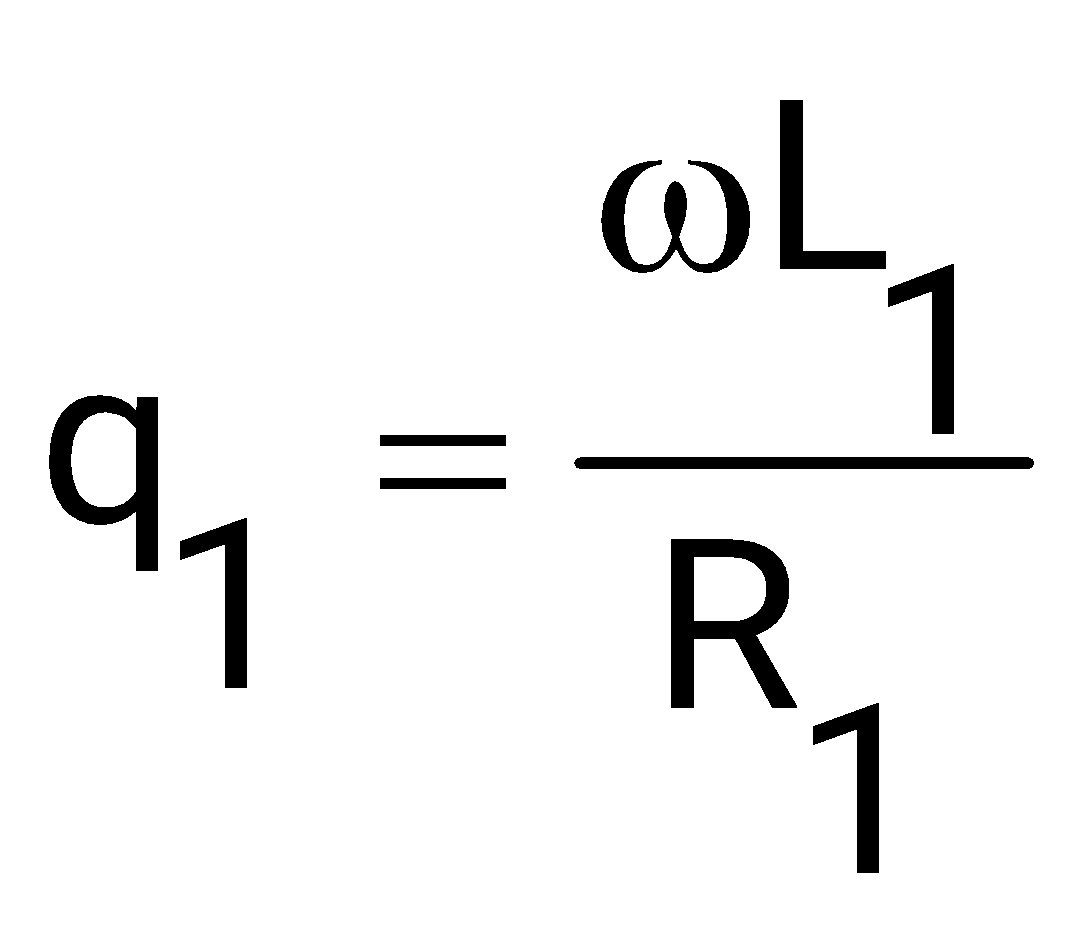

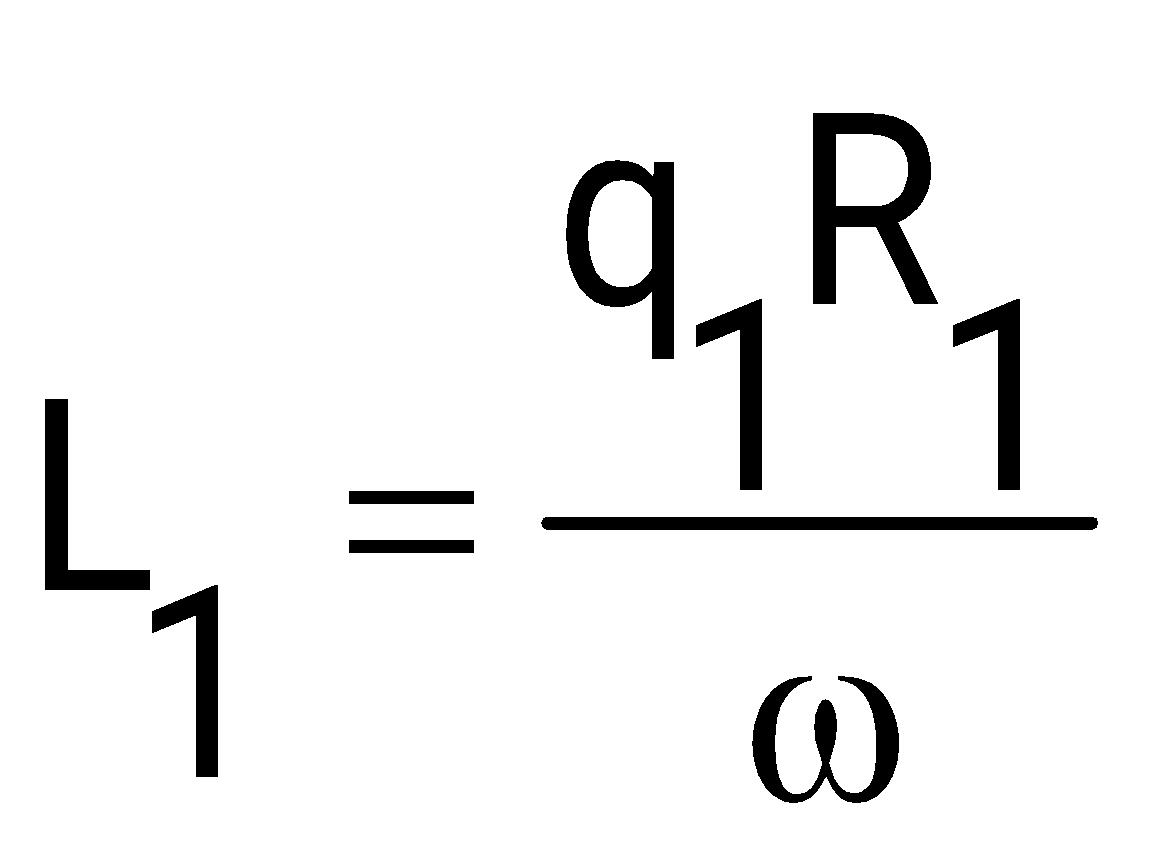

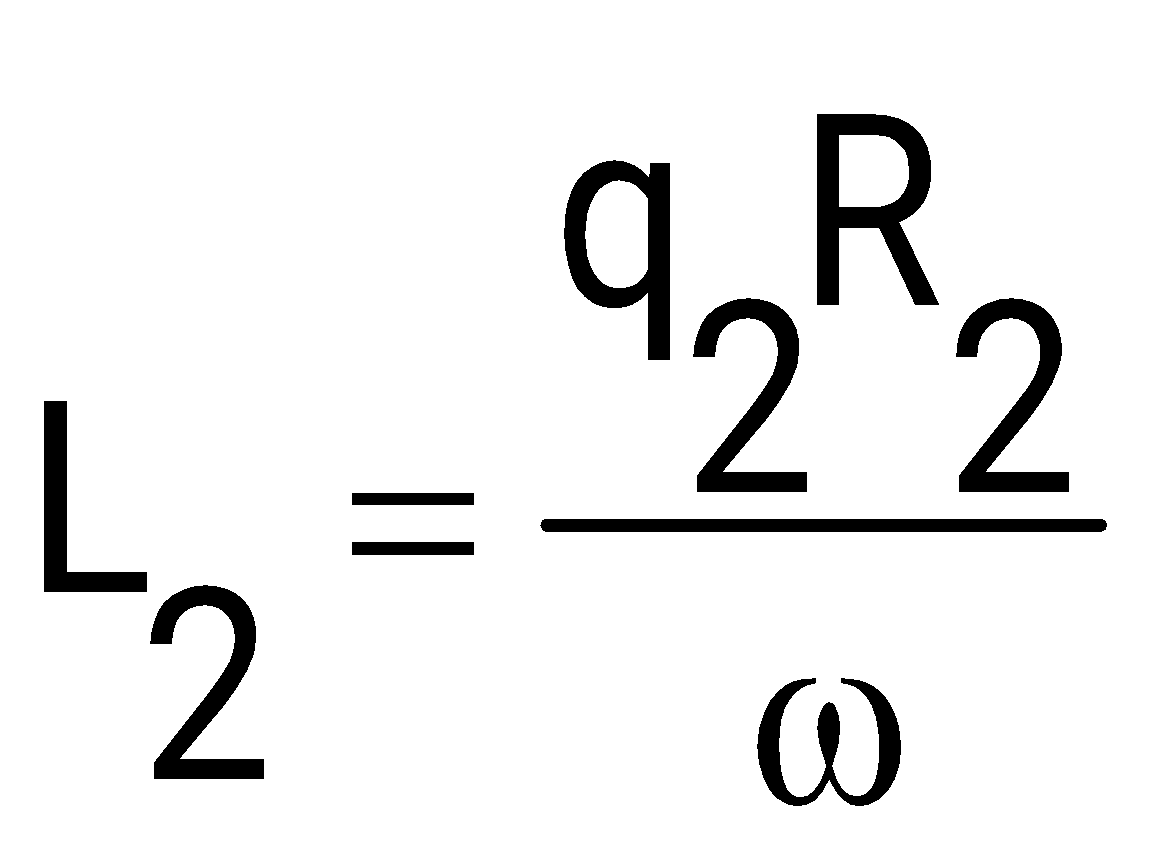

For Coil 1,

Similarly for Coil 2,

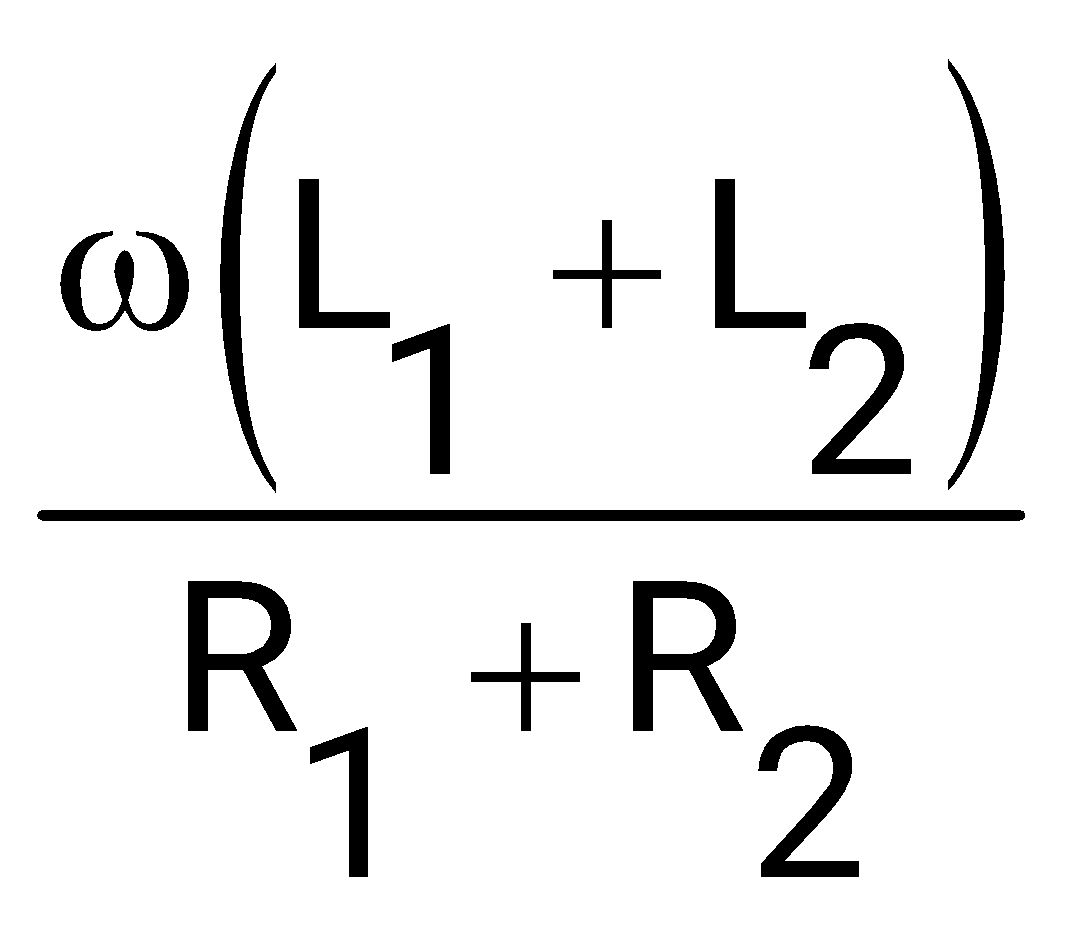

When connected in series,

Equivalent inductance =

Equivalent resistance =

quality factor =

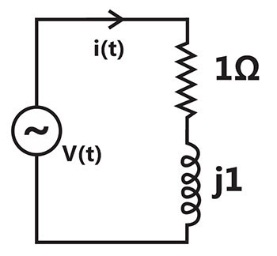

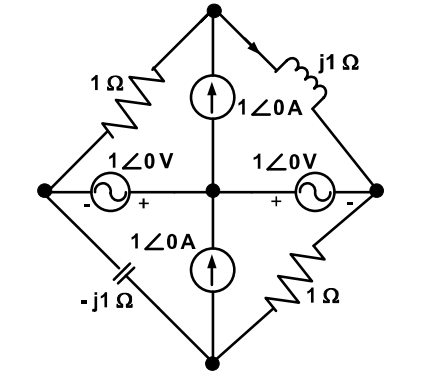

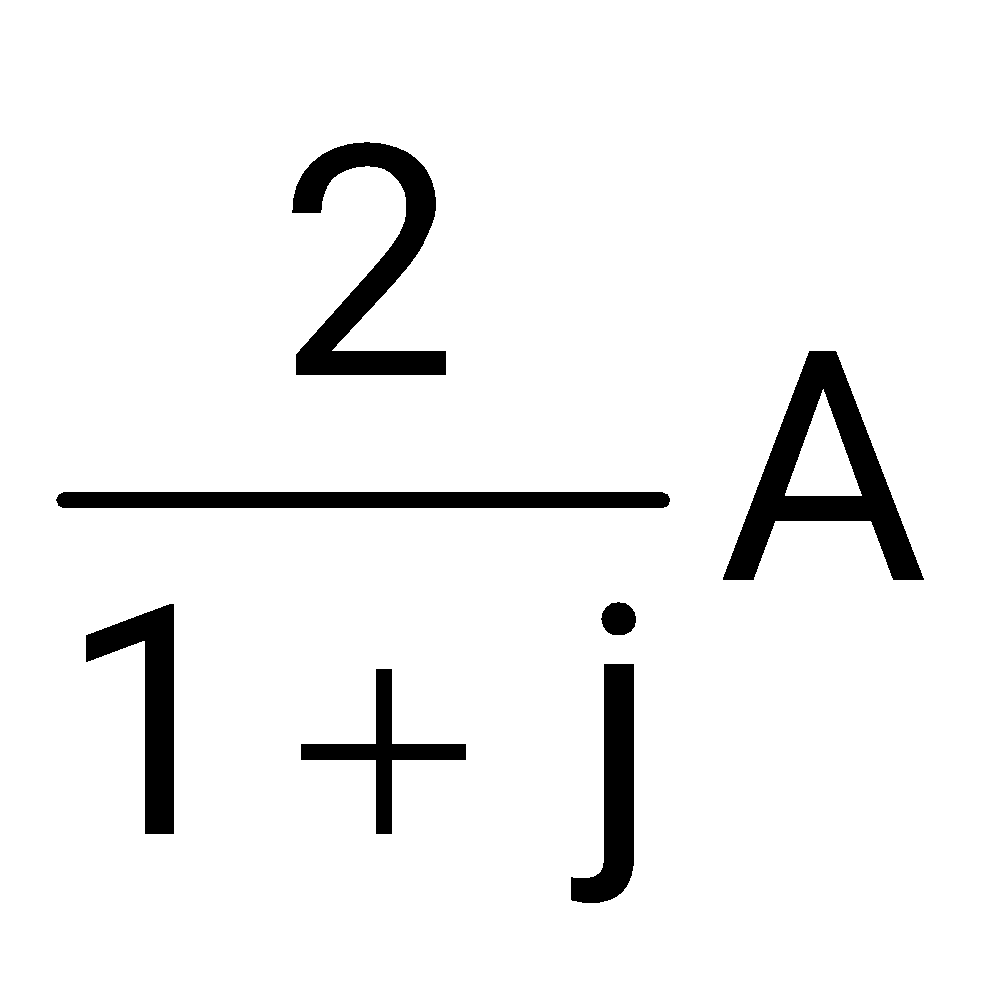

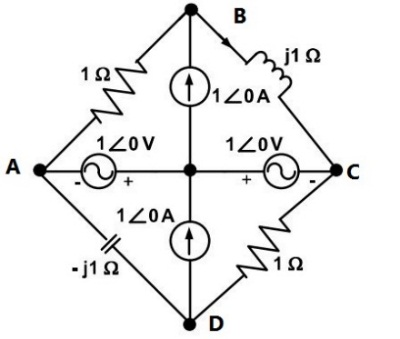

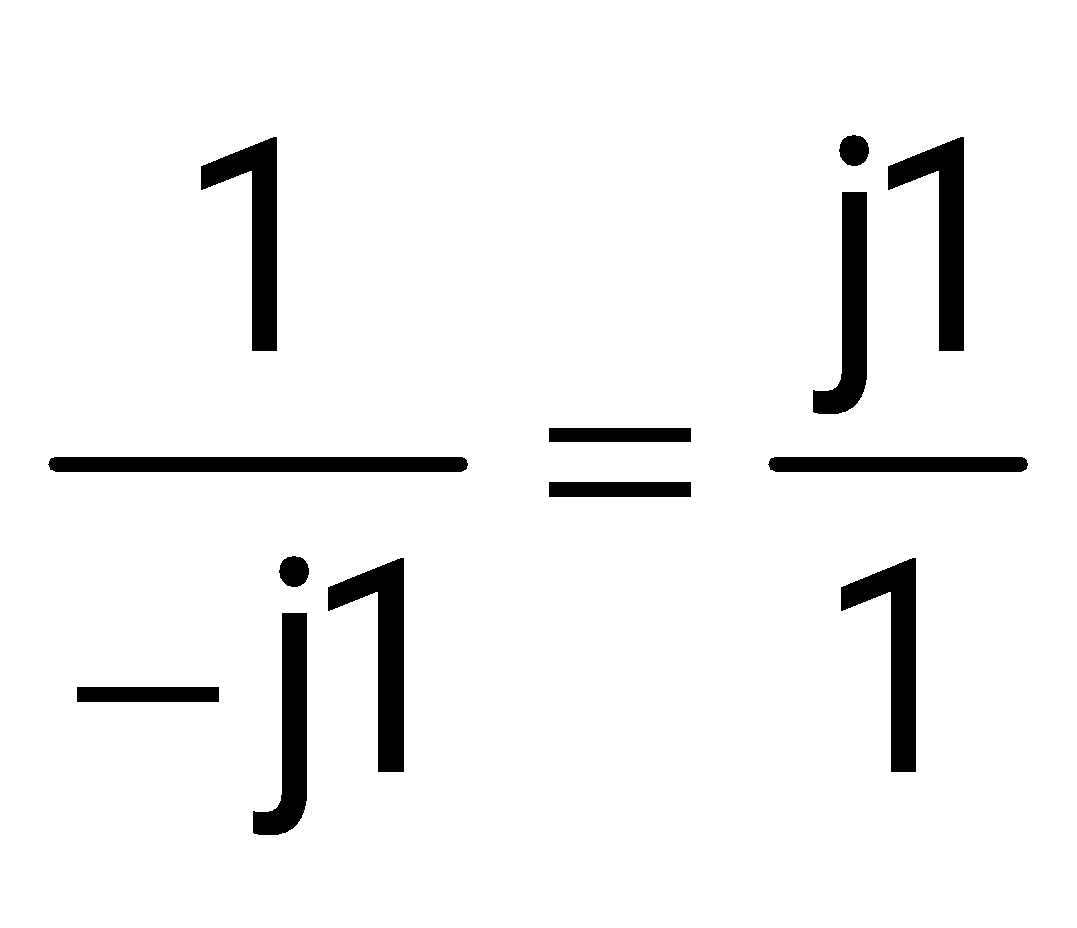

In the circuit shown below, the current through the inductor is

This implies that the bridge circuit is in balanced condition.

So points A & C will be at same potential.

Due to this 1Ω resistor and j1Ω are connected in parallel.

So applying current division rule at node B.

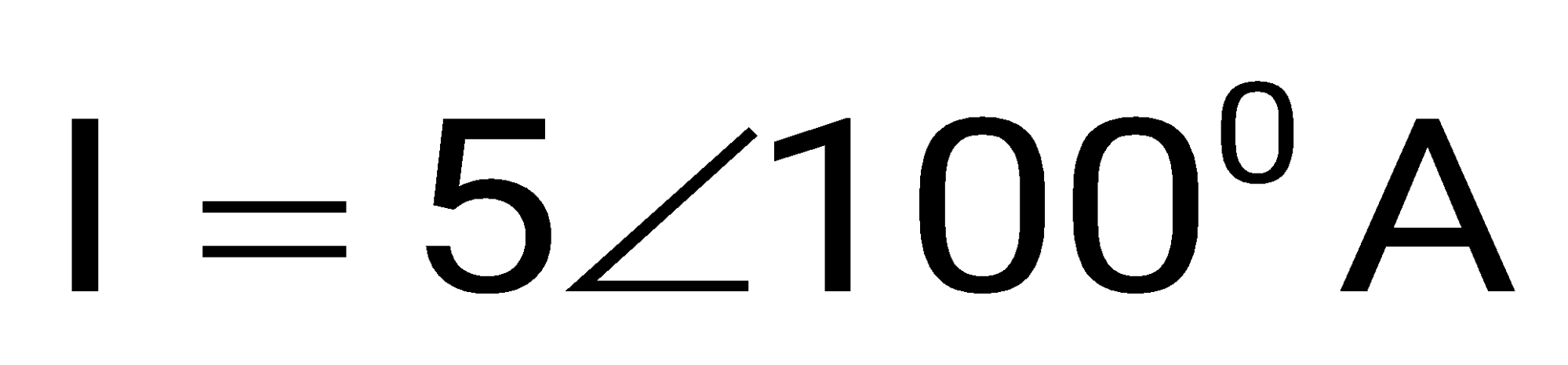

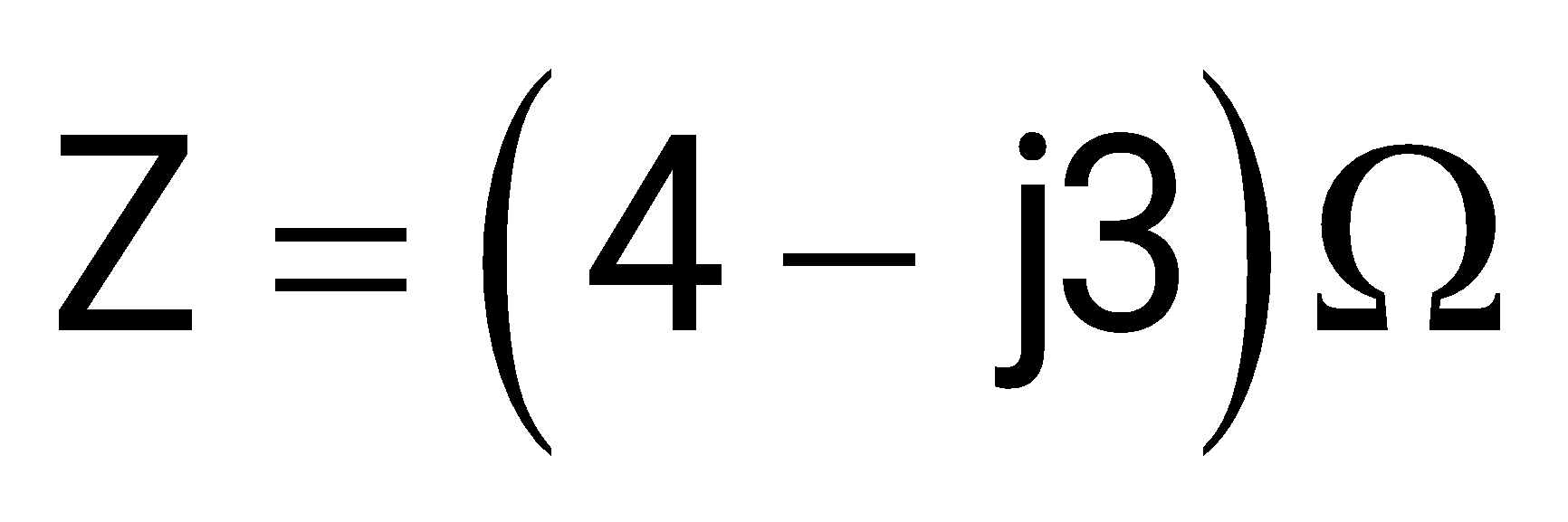

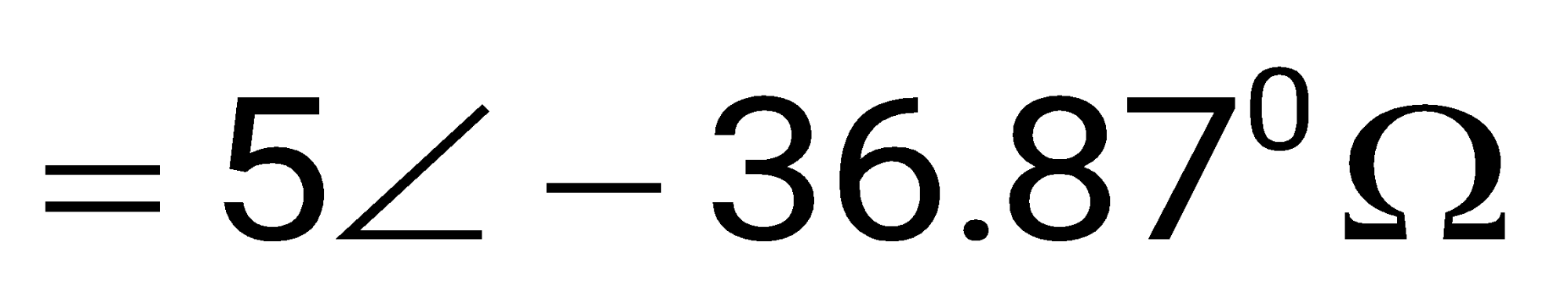

The average power delivered to an impedance (4–j3) by a current is

The current source can be represented in phasor form as,

Here, we are considering maximum value as the

magnitude of phasor.

Here, current is leading the voltage as the impedance has negative imaginary part which means that the impedance is capacitive.

Average Power,

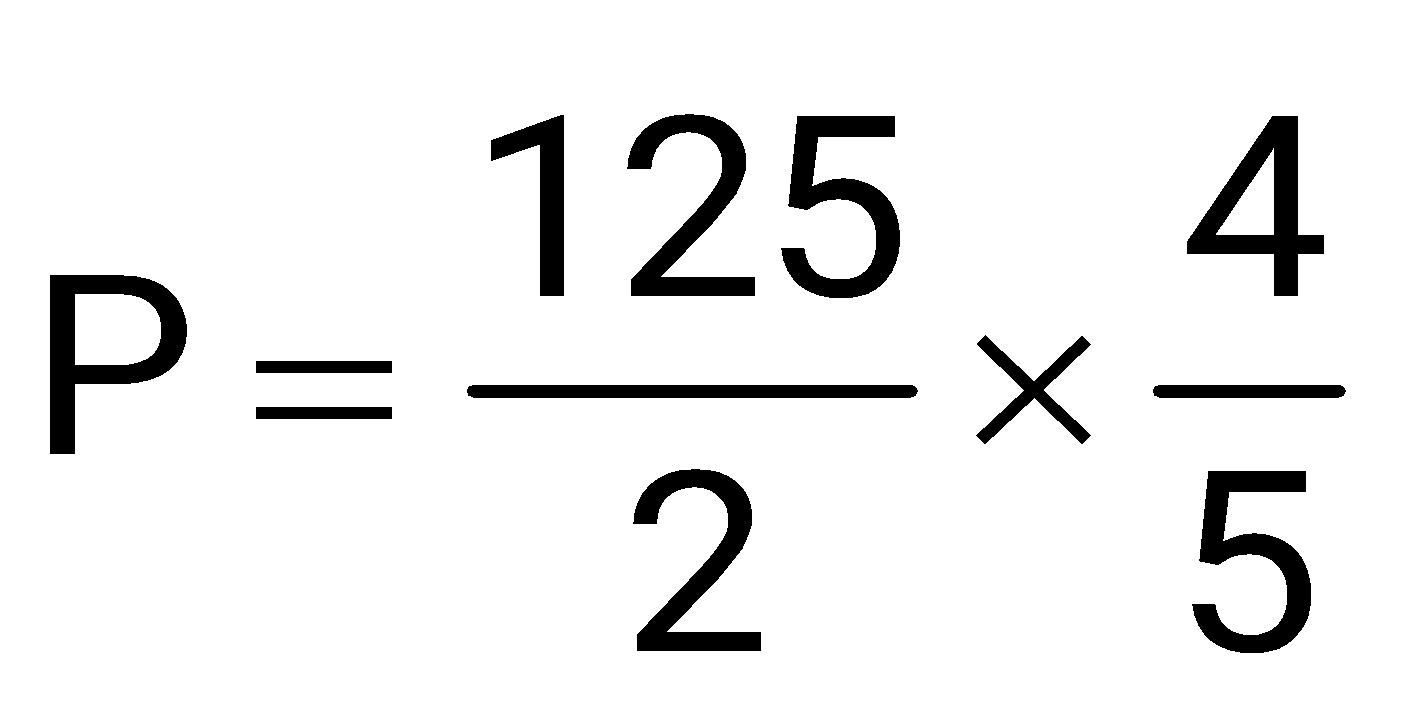

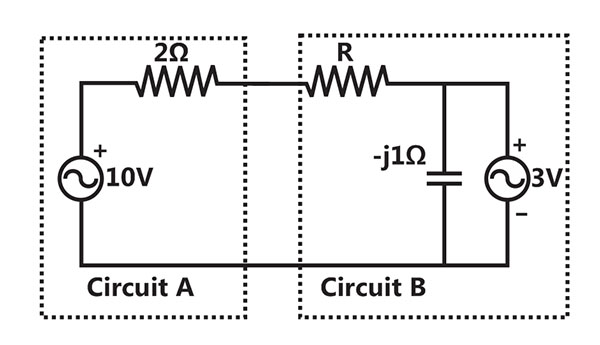

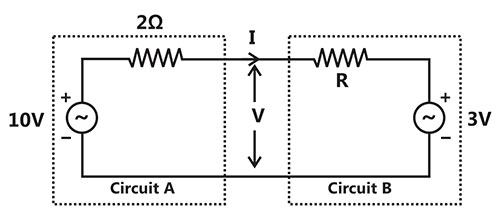

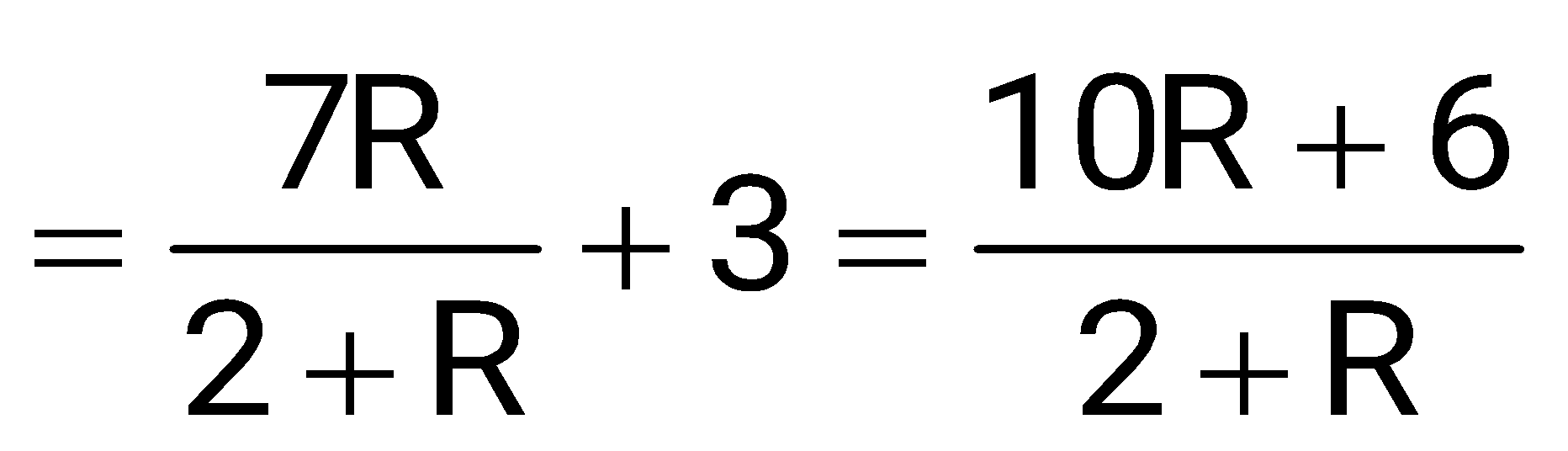

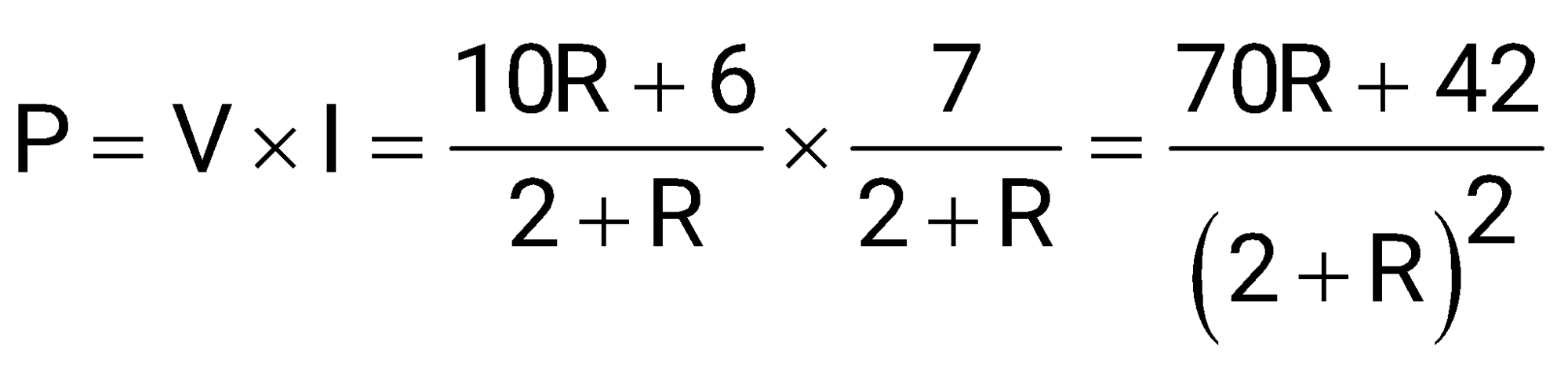

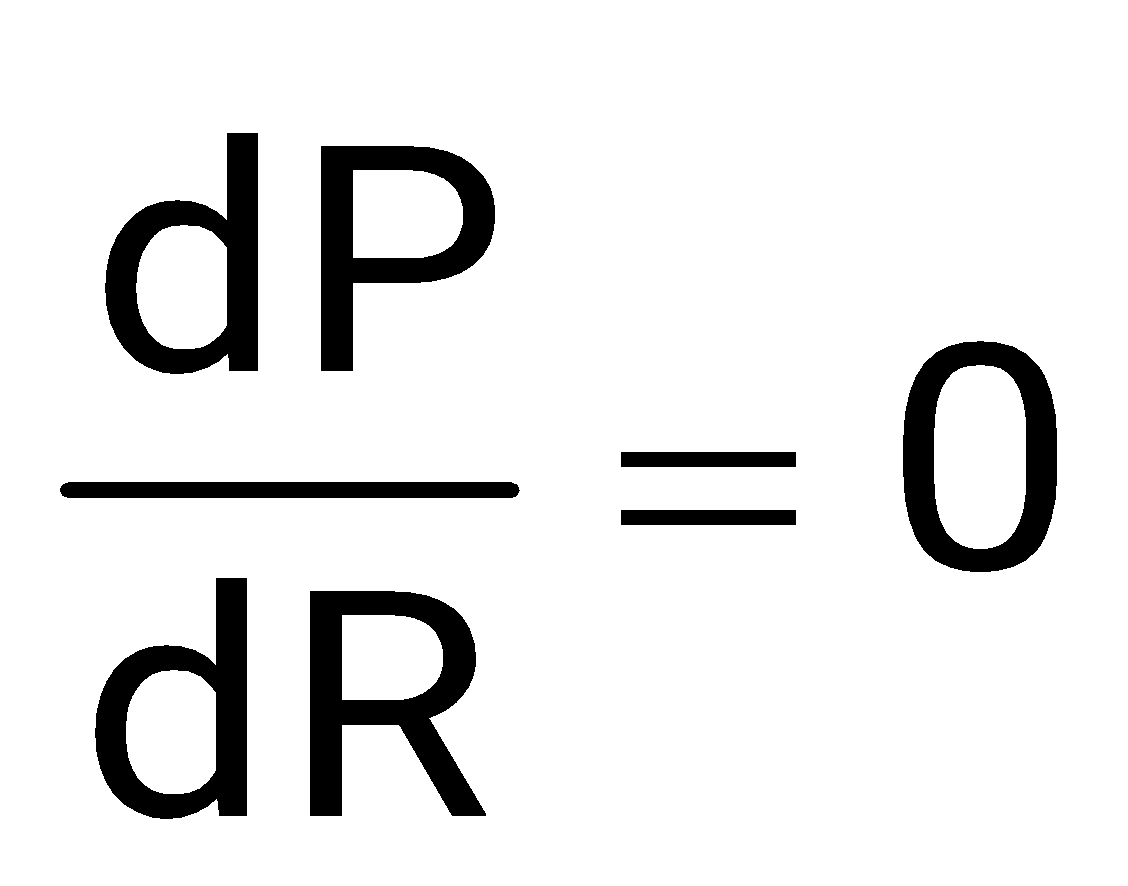

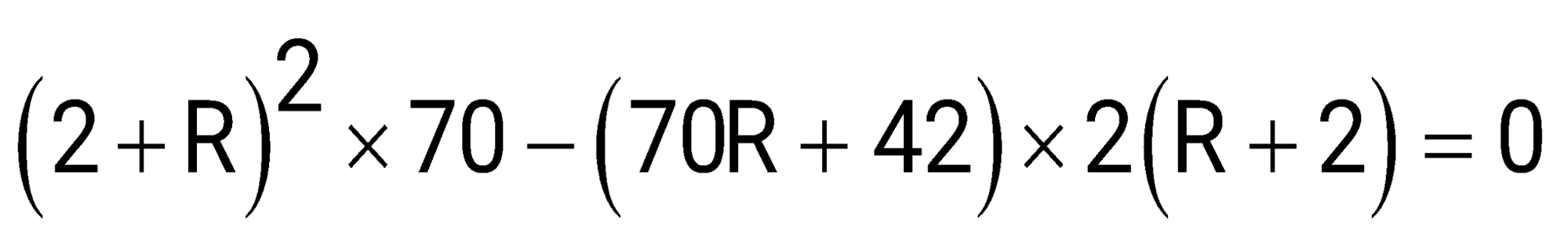

Assuming both the voltage sources are in phase, the value of R for which maximum power is transferred from circuit A to circuit B is

Finding thevenin’s equivalent circuit of circuit - B.

Open circuiting the terminals of circuit B.

Short the voltage source to determine the Thevenin Resistance.

Representing the circuit B by its Thevenin Equivalent.

----------(1)

Power transferred from A to B

For P to be maximum

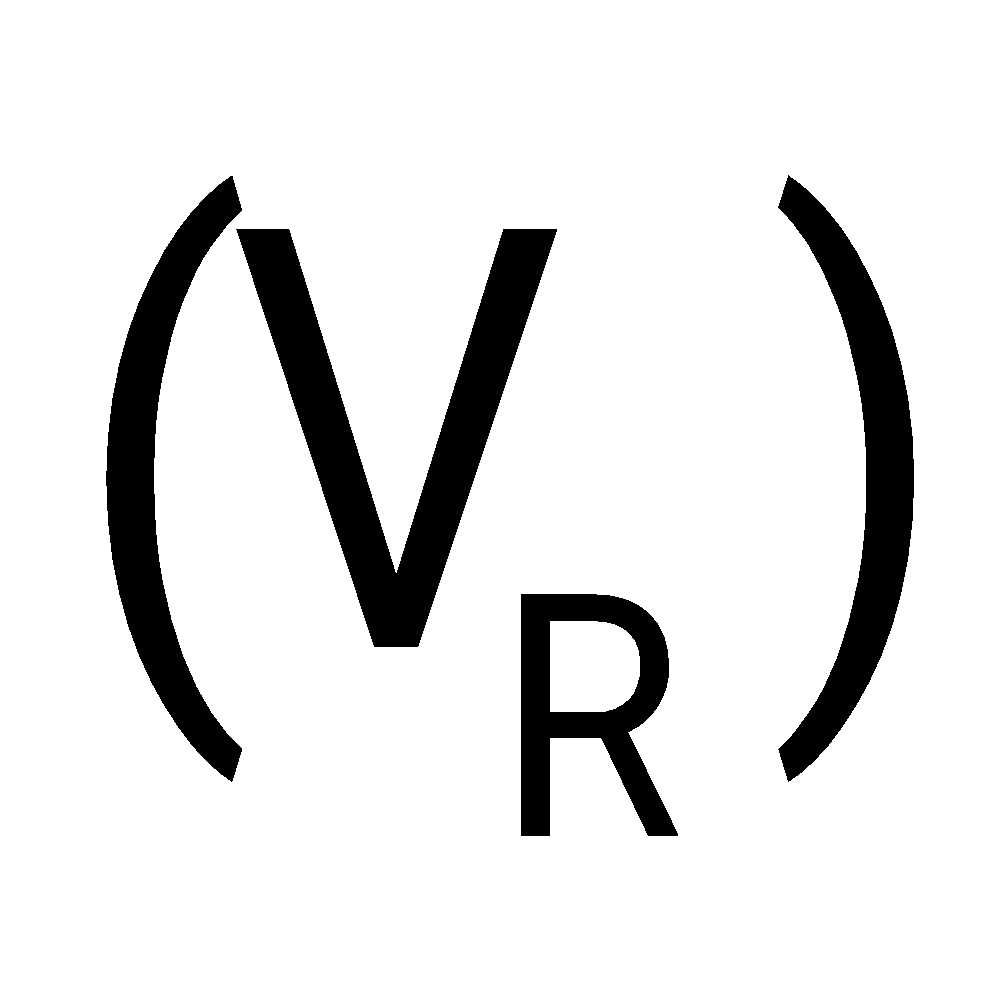

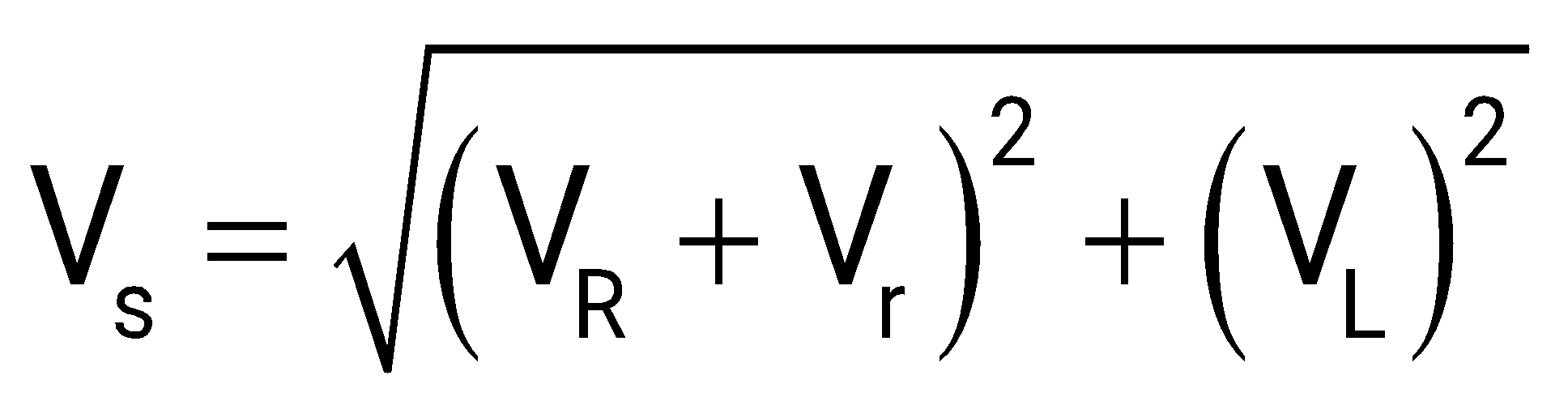

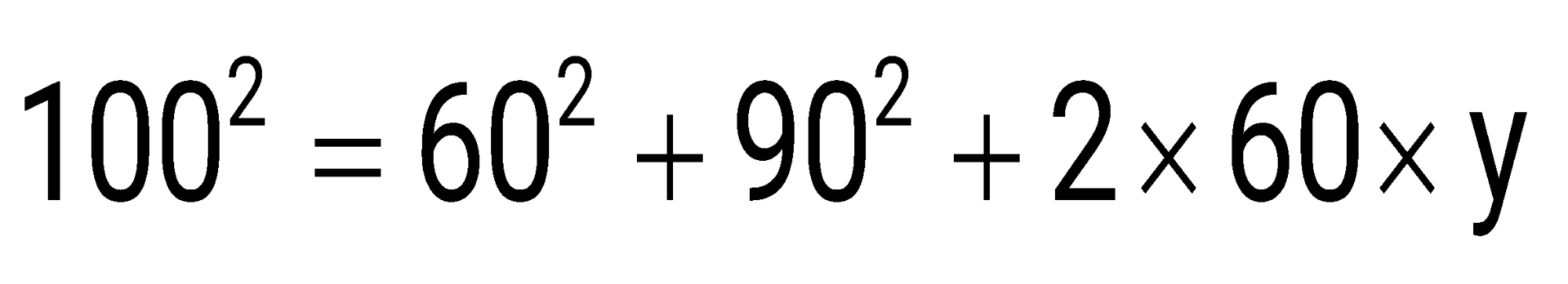

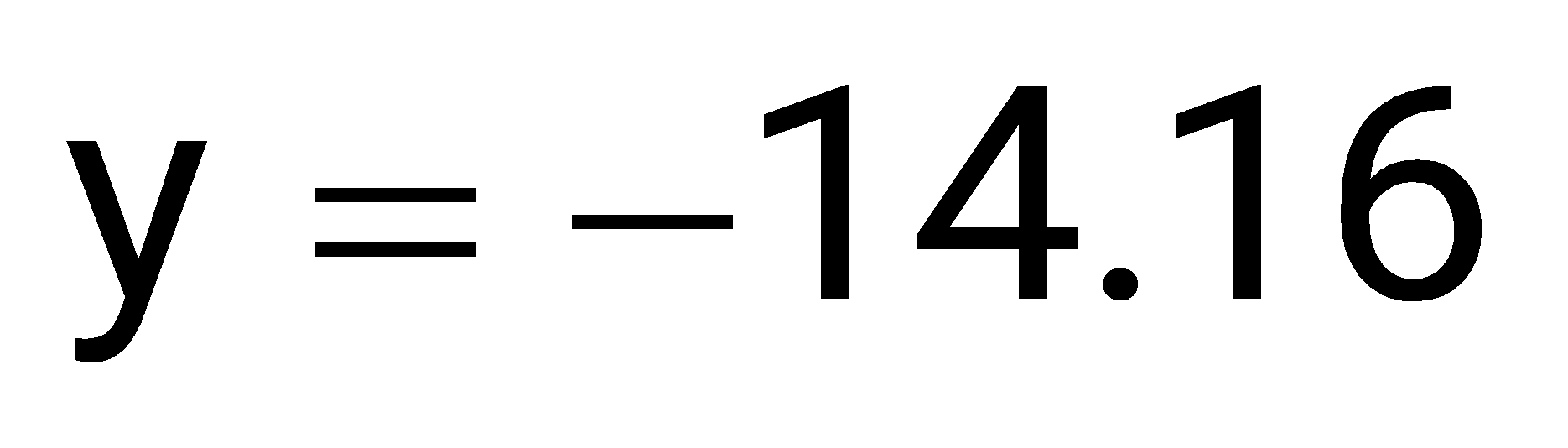

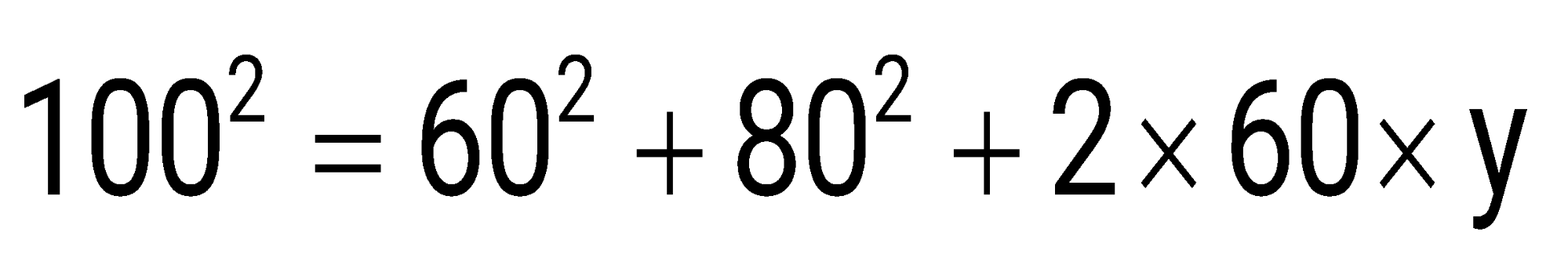

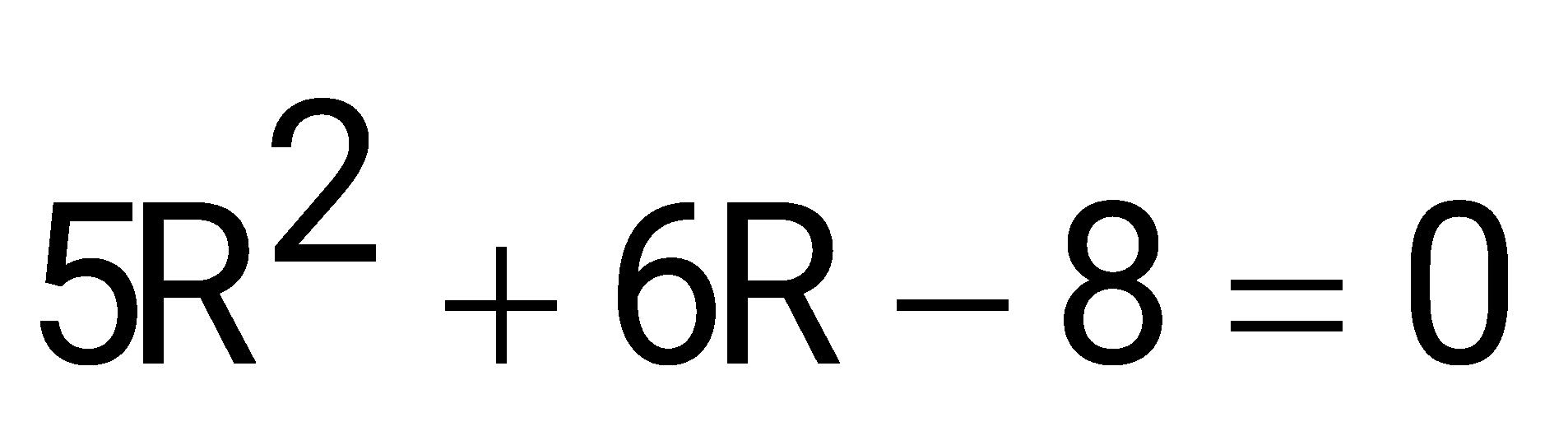

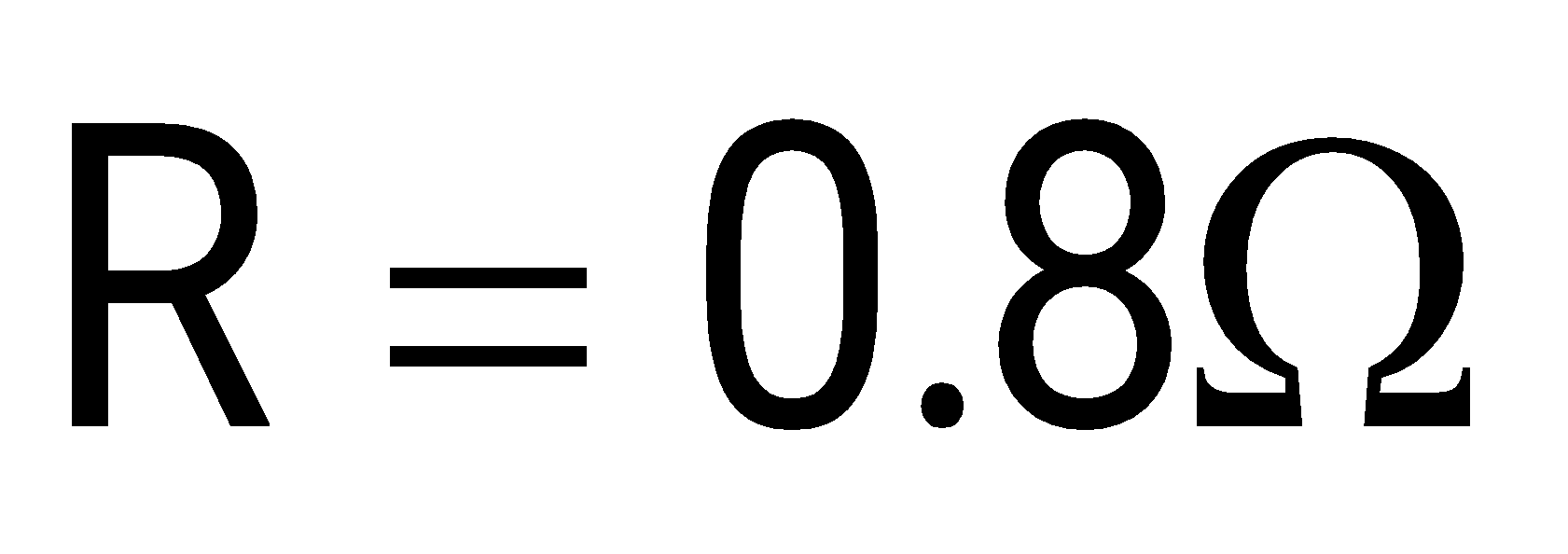

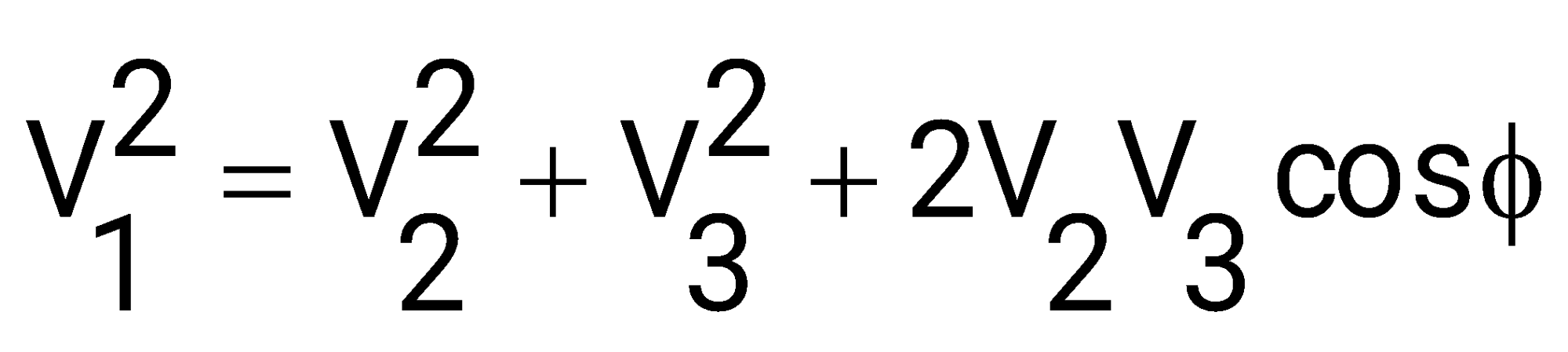

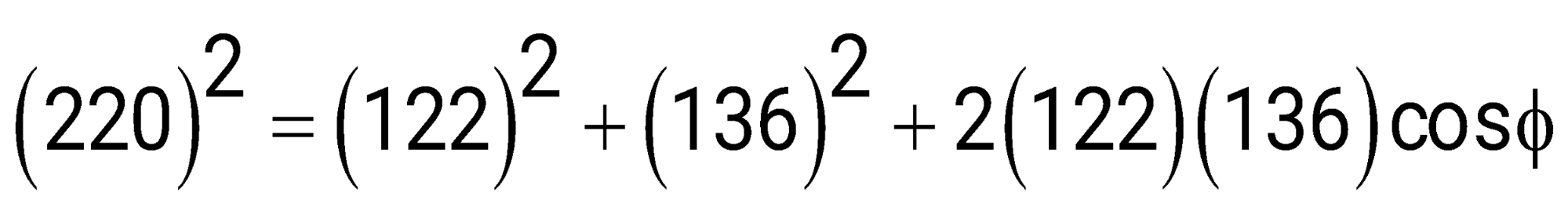

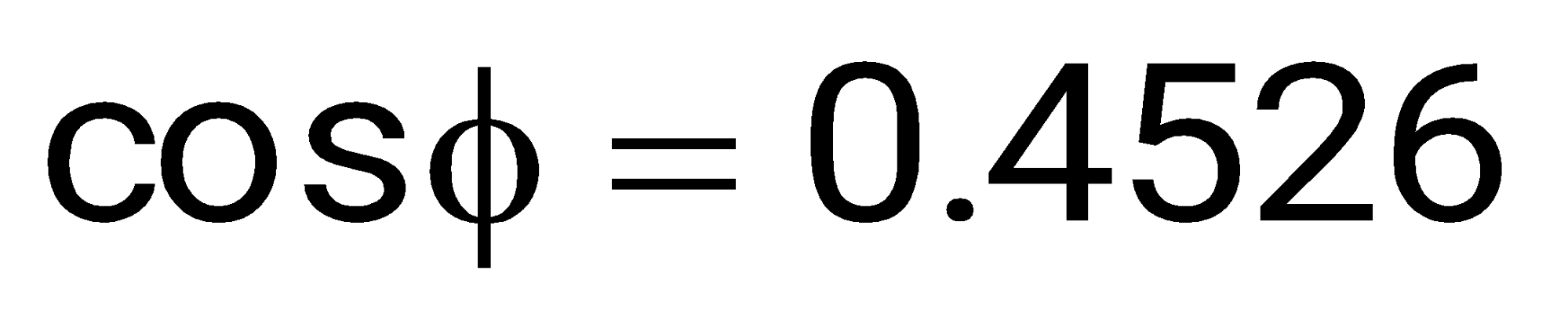

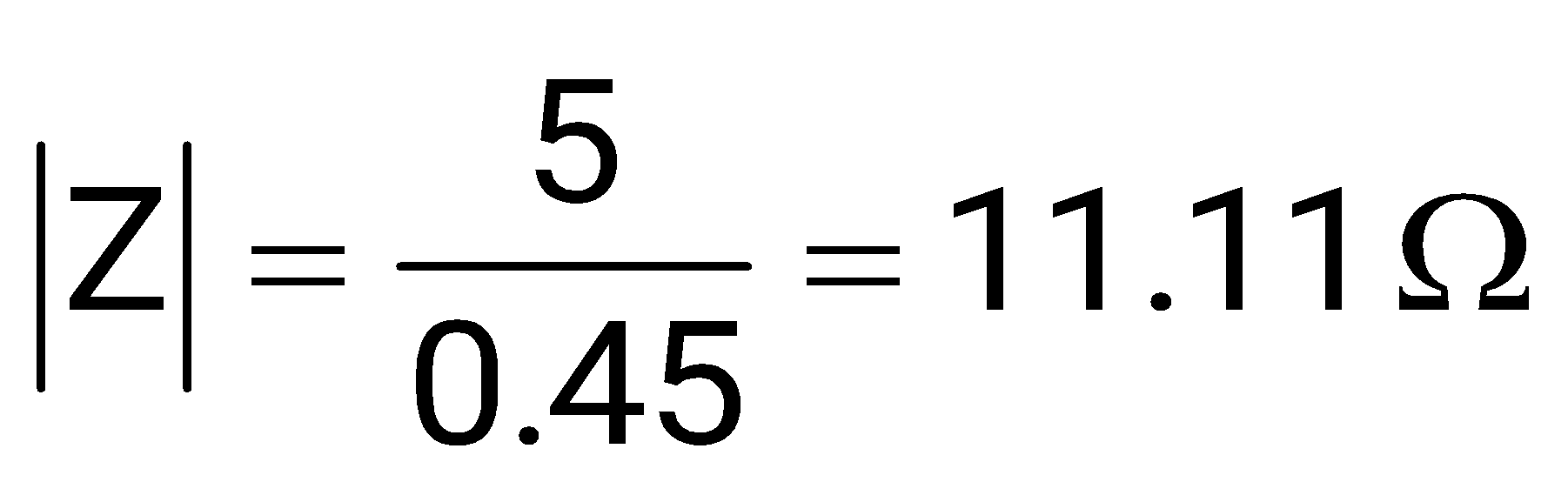

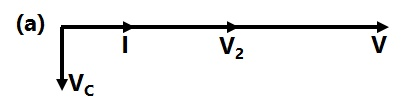

In the circuit shown, the three voltmeter readings are .

The power factor of the load is

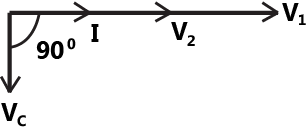

Since is the voltage across a resistor so, it will be in same phase as current but voltage across RL load will lead the voltage by power factor angle.

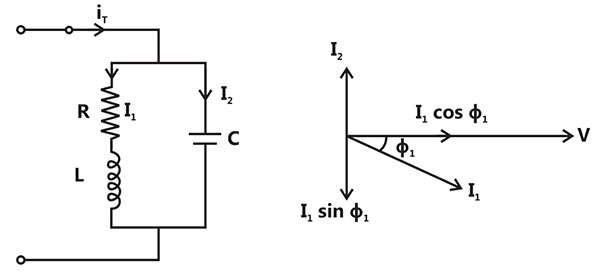

The circuit and phasor diagram are shown below,

By Phasor Sum,

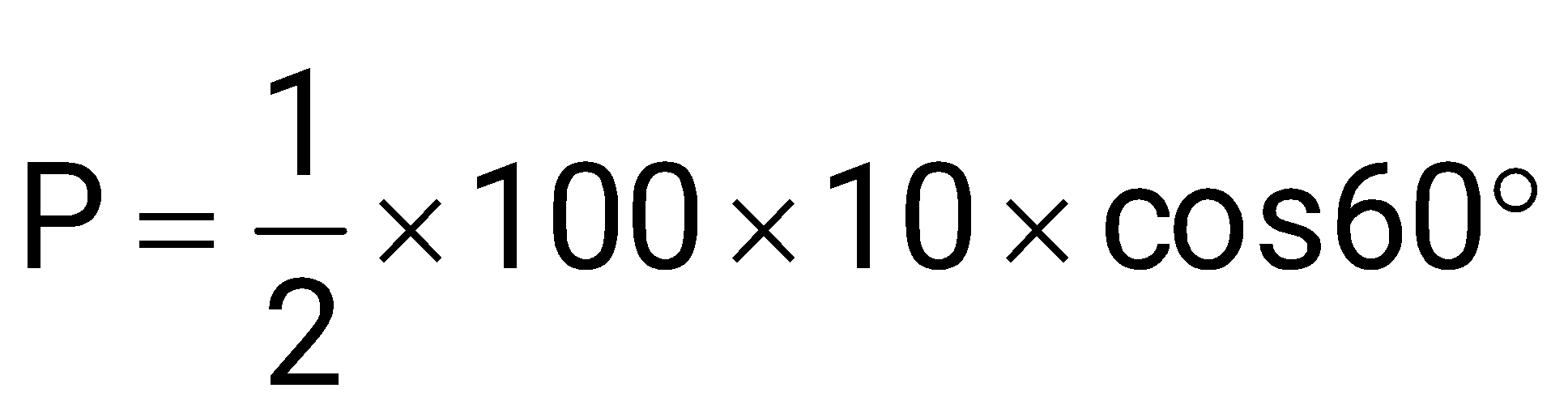

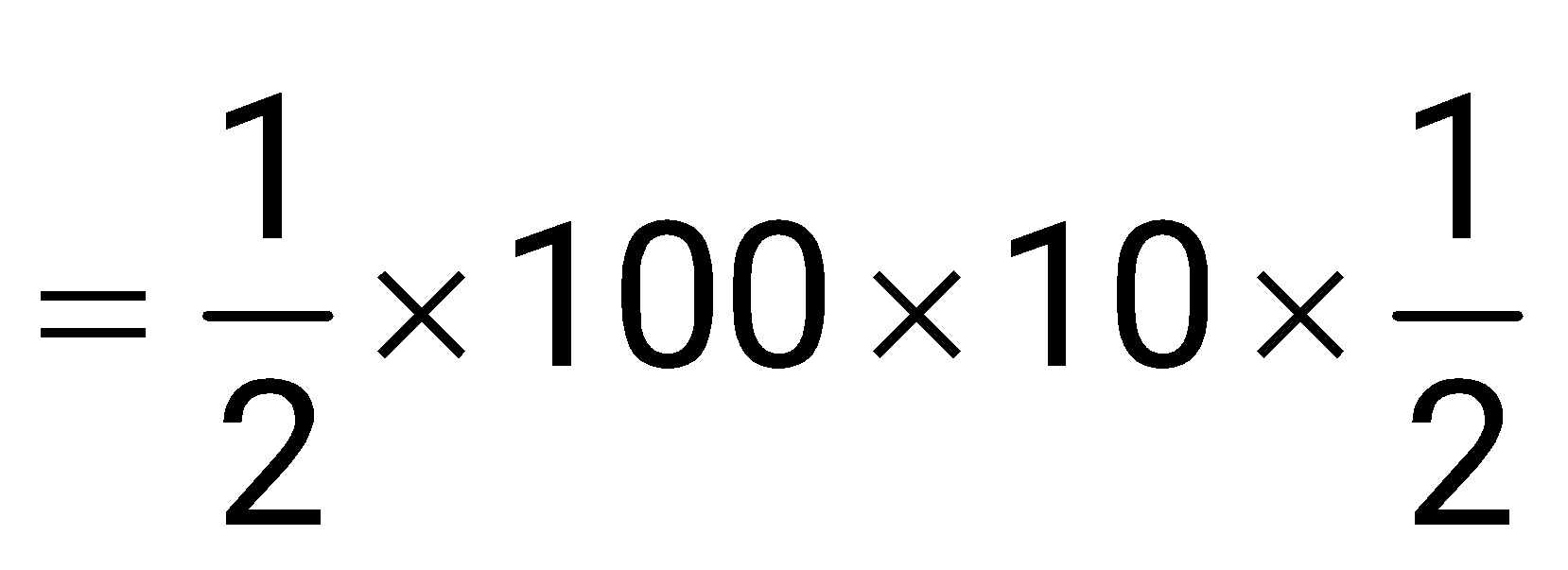

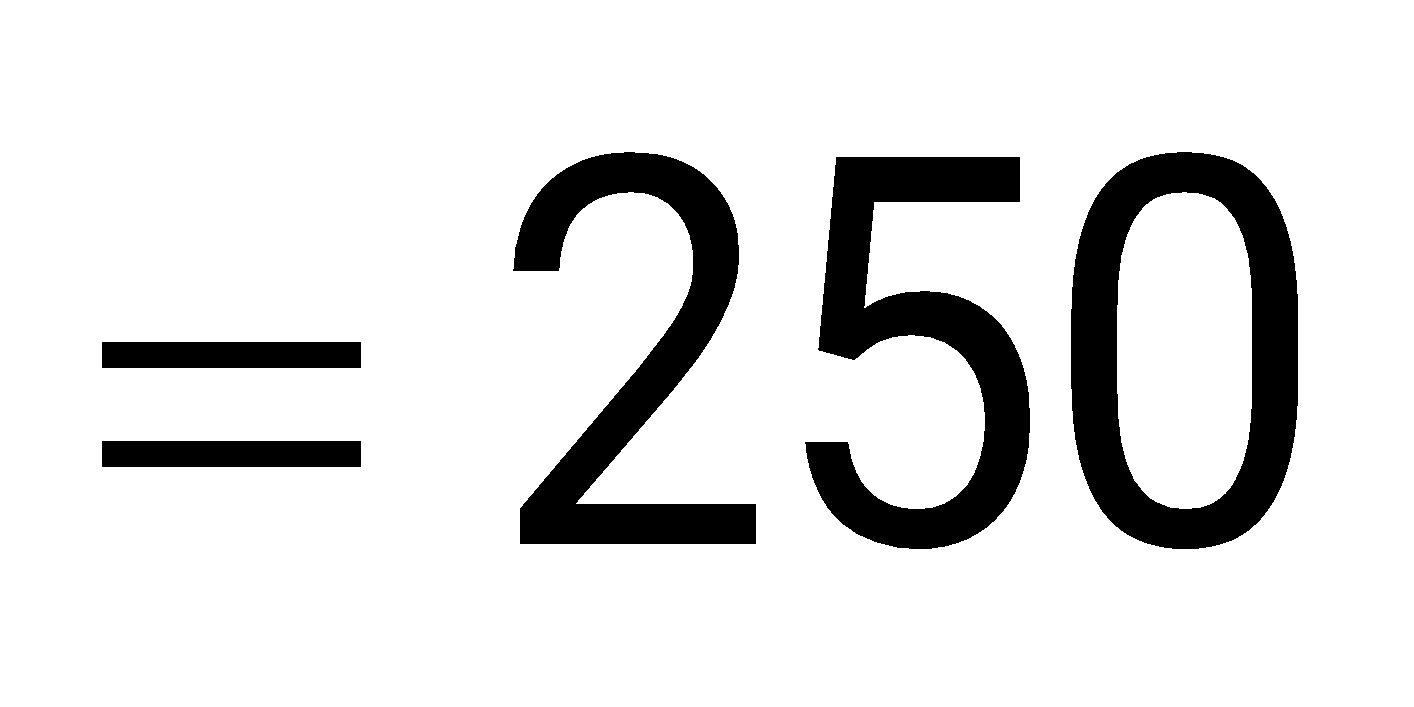

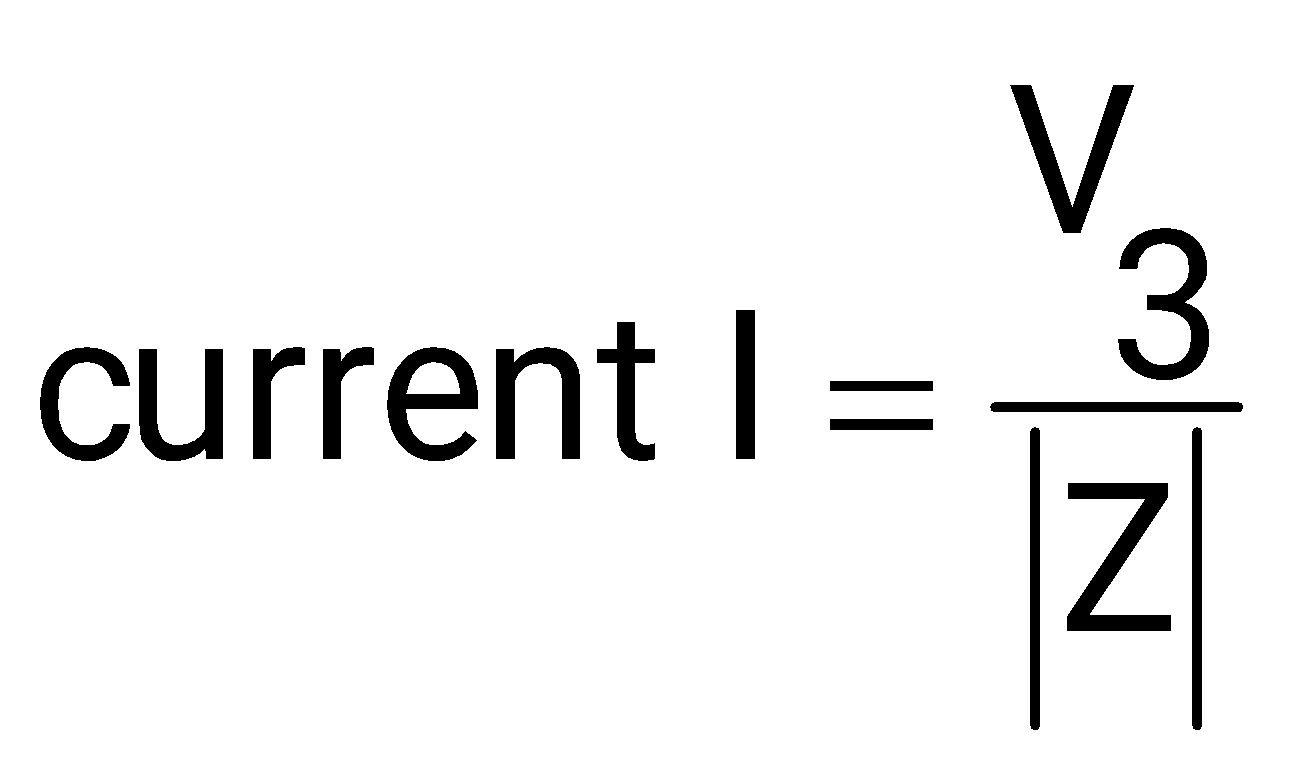

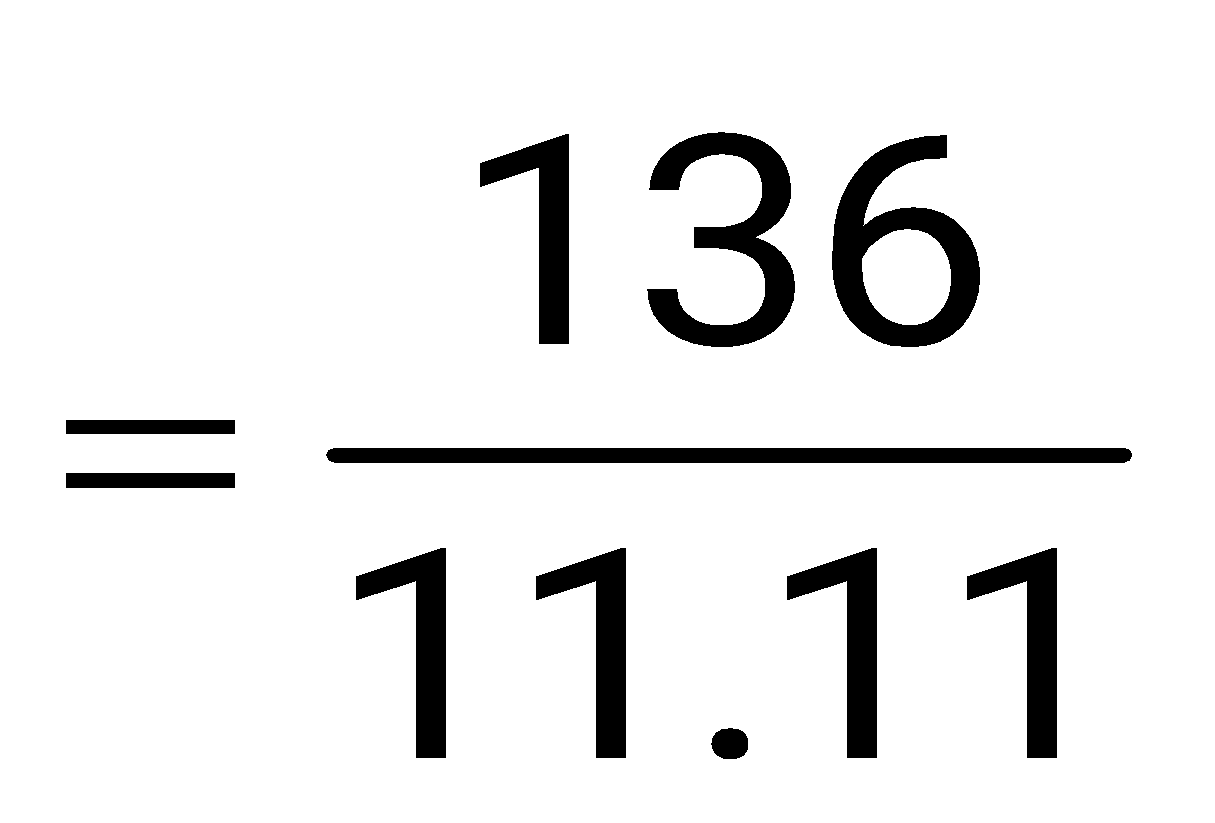

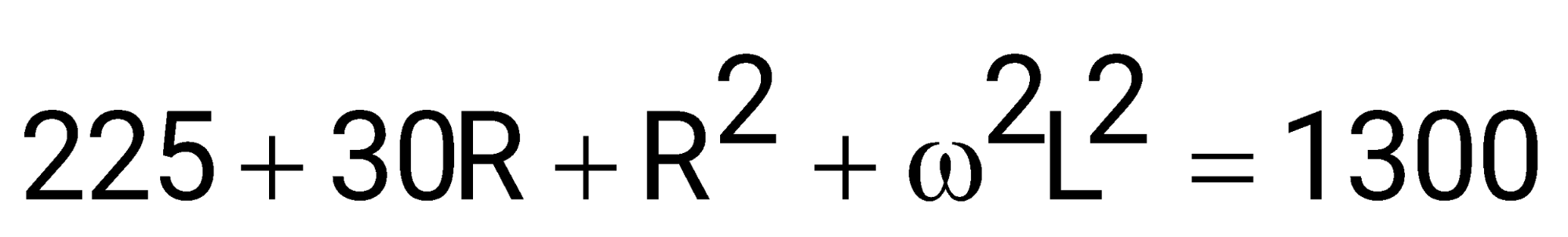

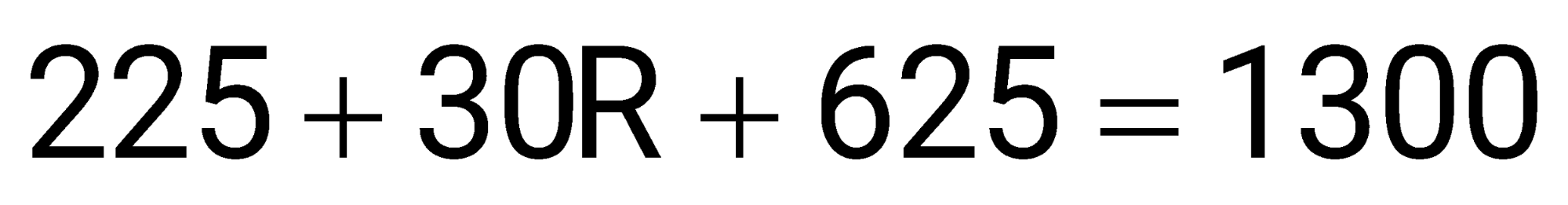

In the circuit shown, the three voltmeter readings are .

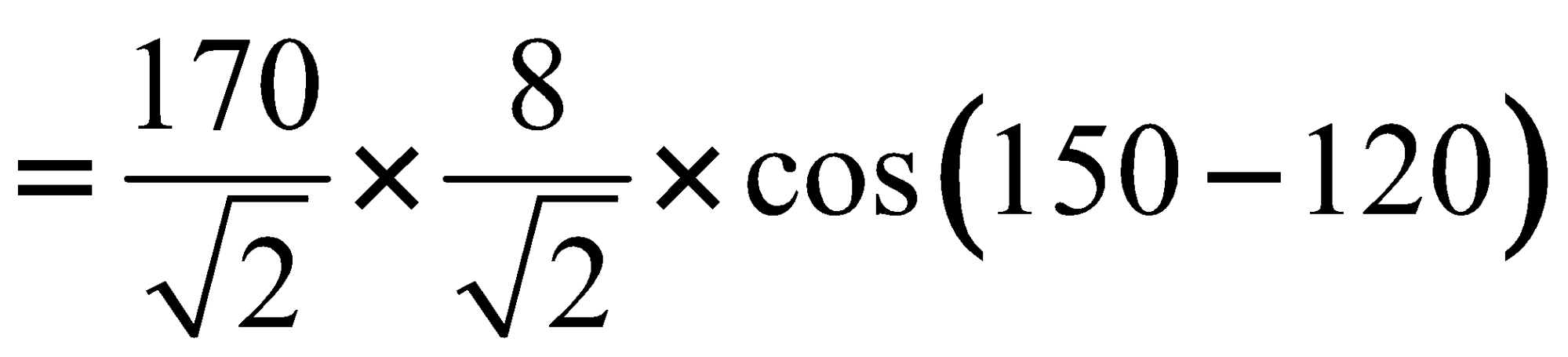

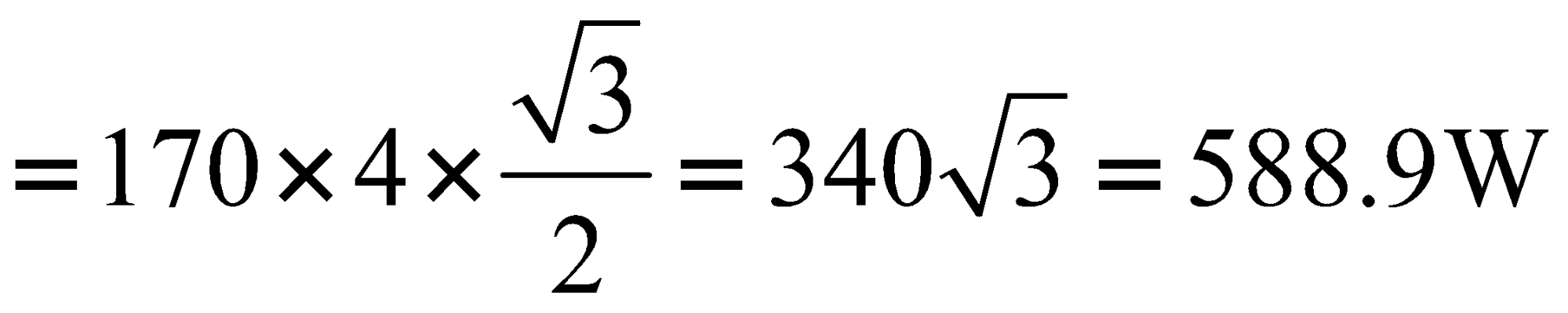

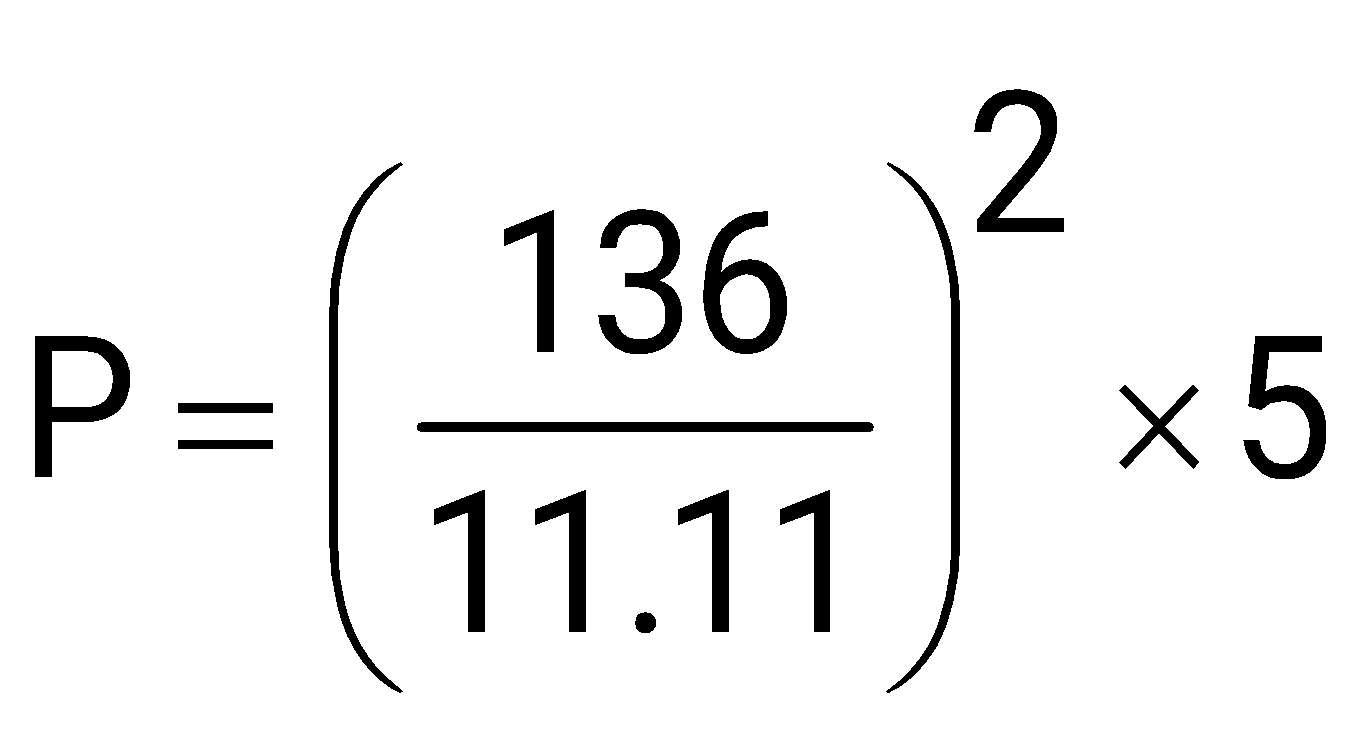

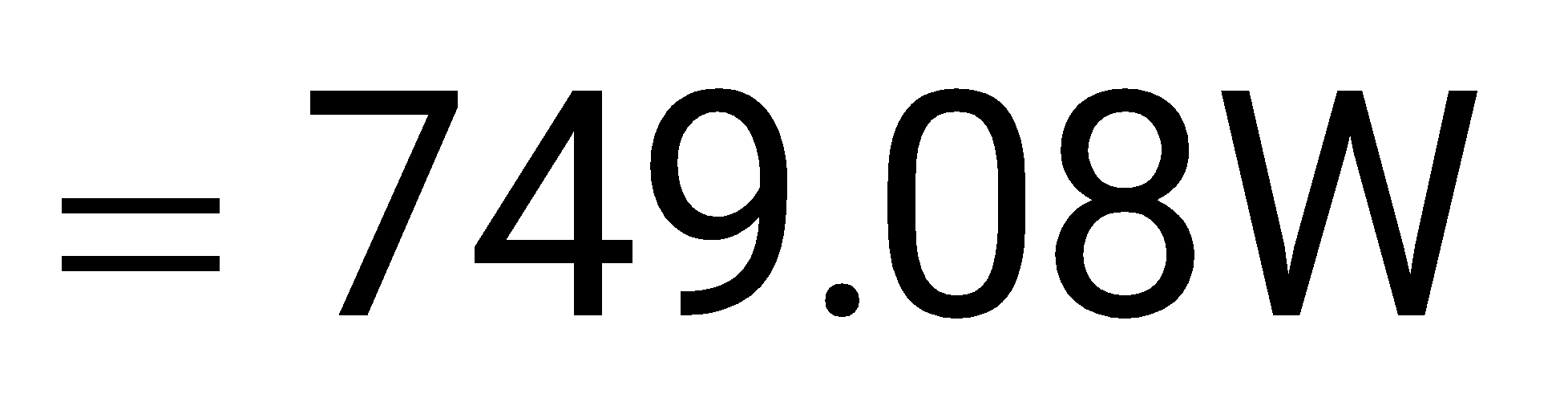

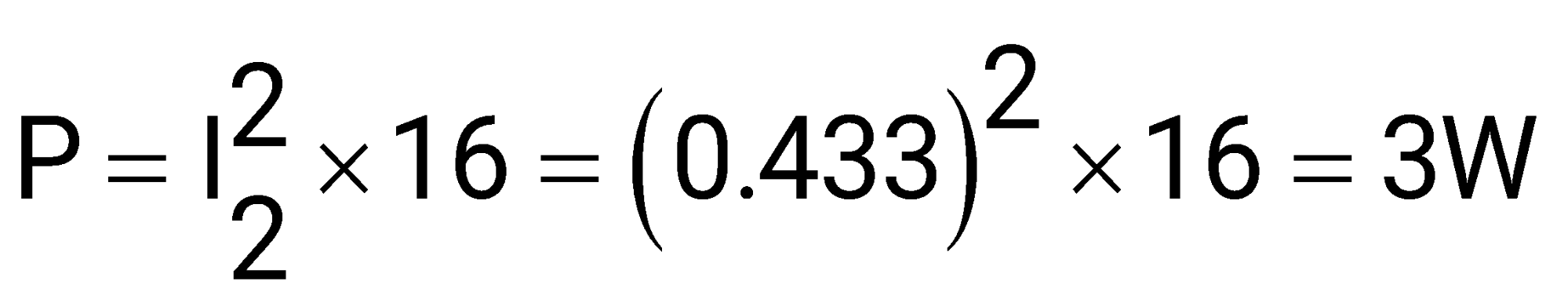

If , the approximate power consumption in the load is

Given,

Power consumption in load impedance is equal to

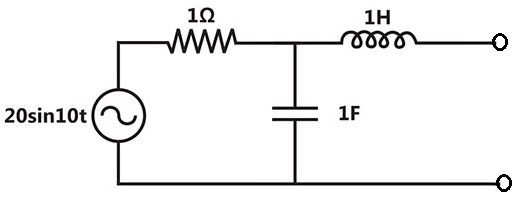

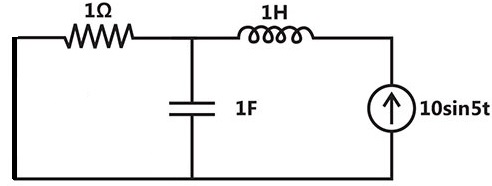

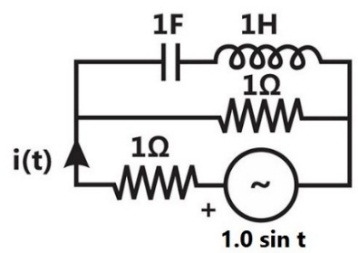

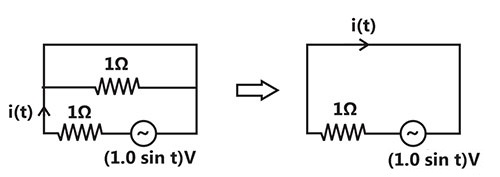

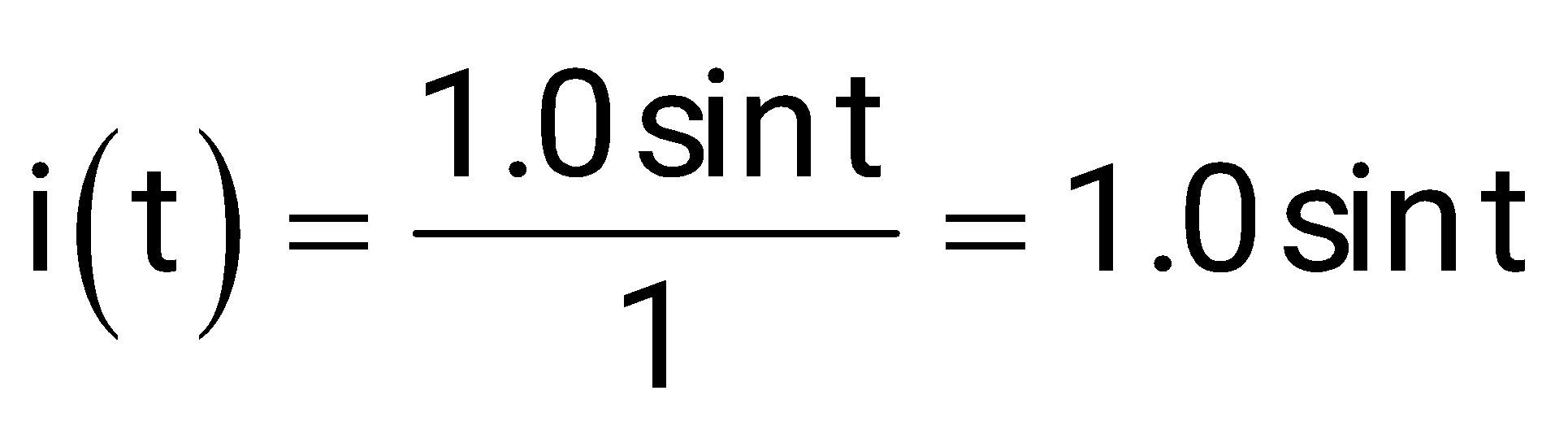

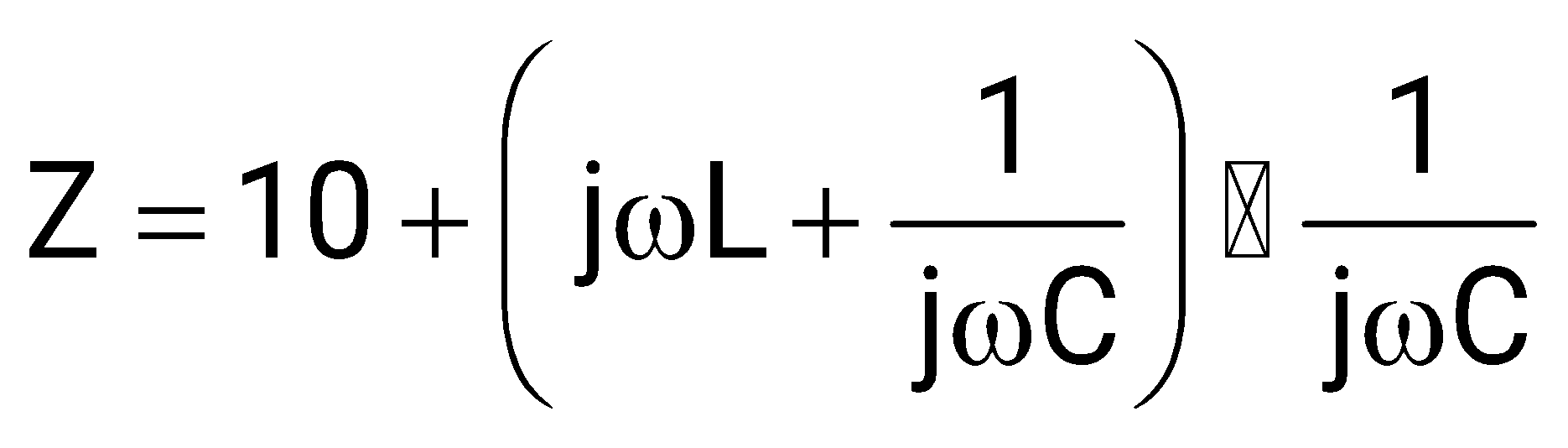

The RMS value of the current i(t) in the circuit shown below is

The circuit with each element represented as Impedance as,

1F capacitor

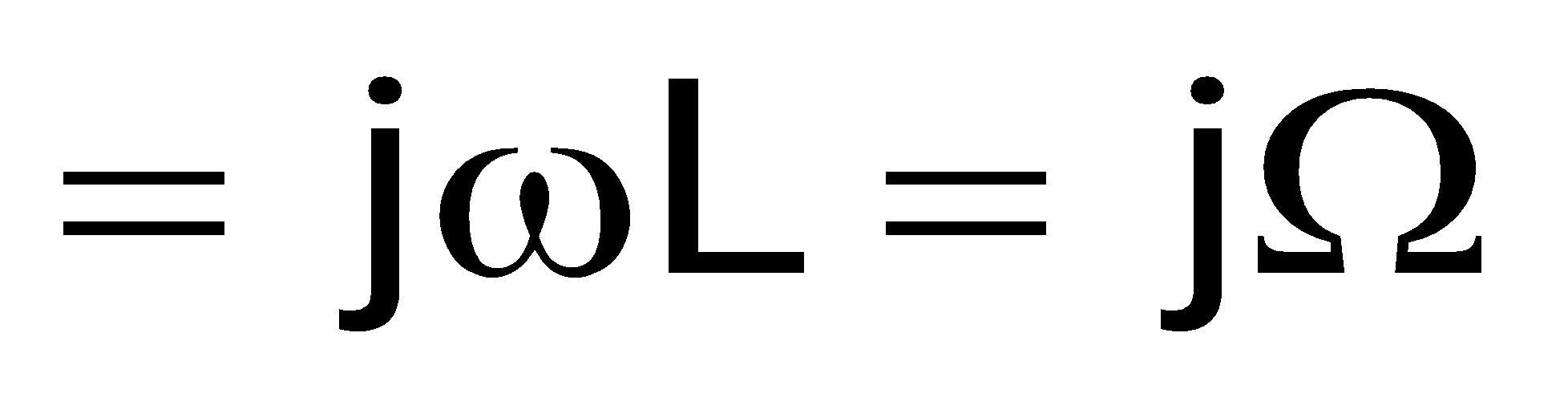

1H inductor

Inductor and Capacitor cancel the impedance of each other. So,

the upper branch act as Short Circuit.

RMS value of current

The voltage applied to a circuit is volts and the circuit draws a current of amperes. Taking the voltage as the reference phasor, the phasor representation of the current in amperes is

Taking V as reference phase

Since, current lags the voltage by an angle radians

Note: The magnitude of phasor is always rms value of the quantity.

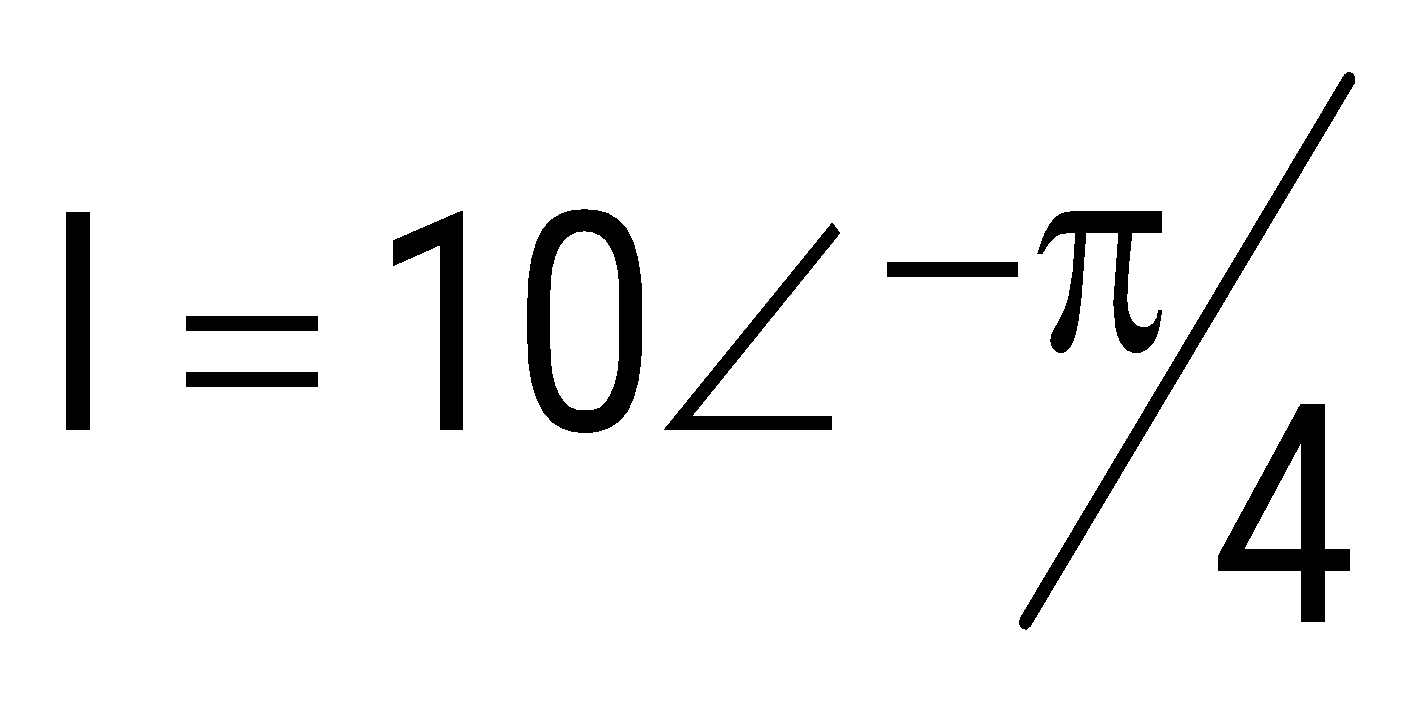

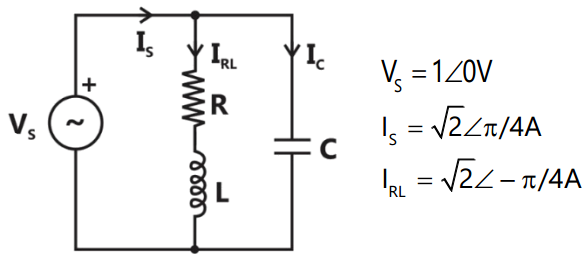

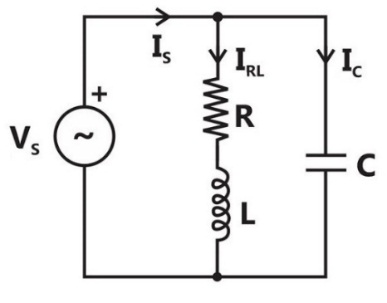

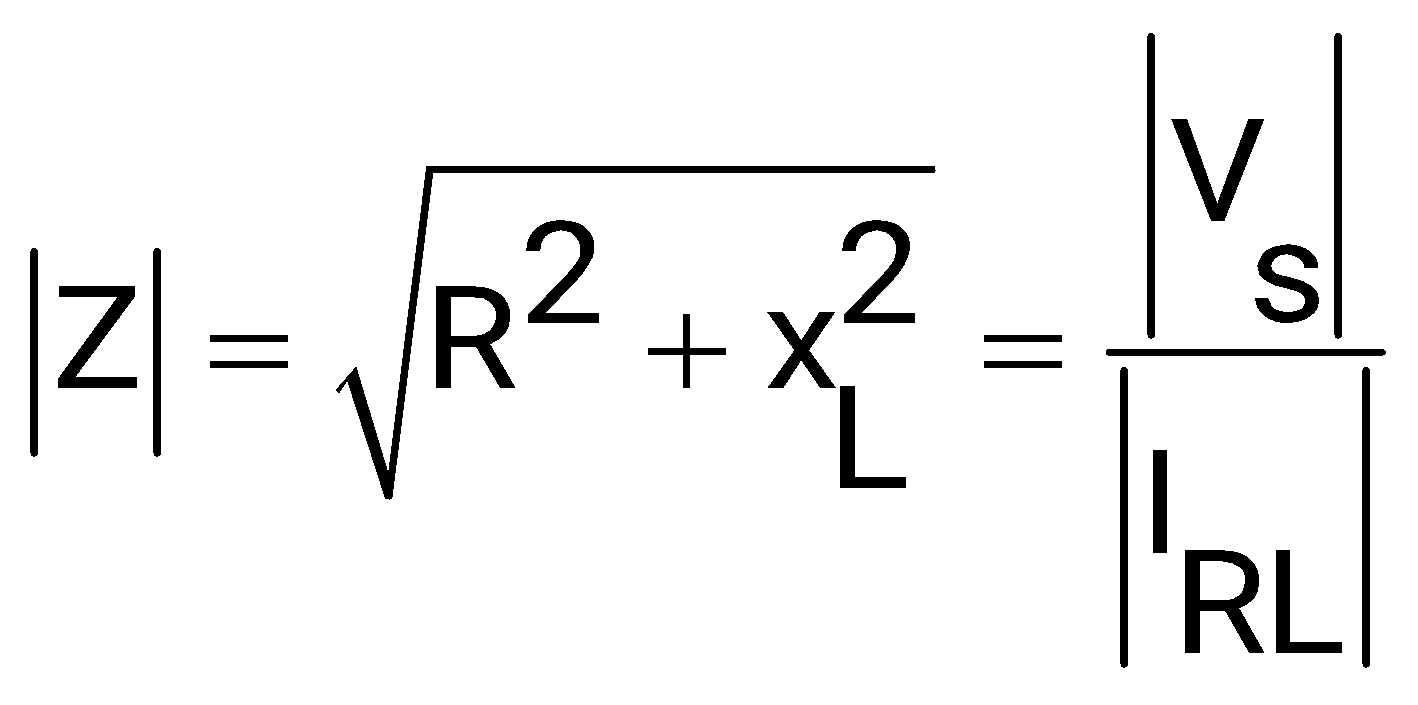

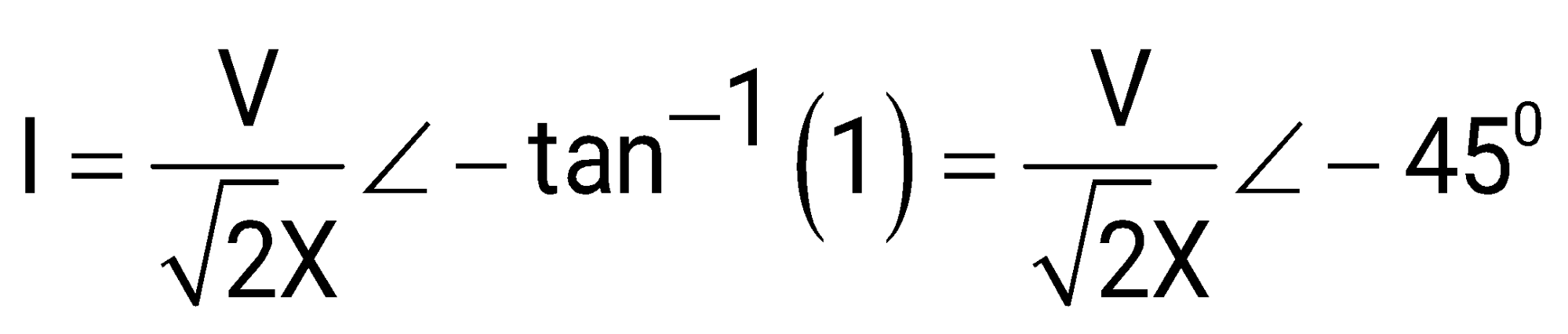

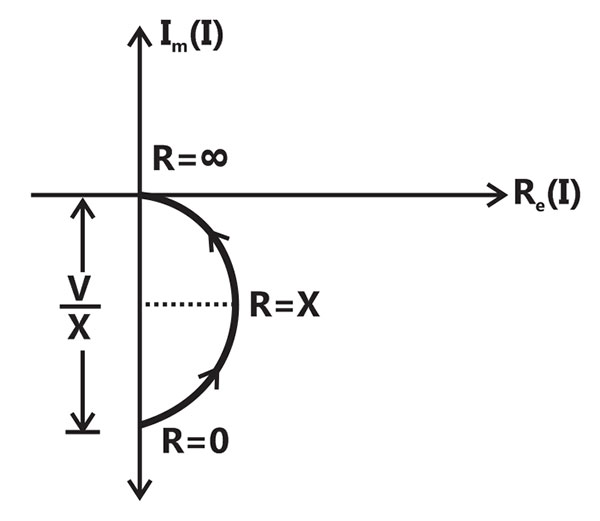

An RLC circuit with relevant data is given below.

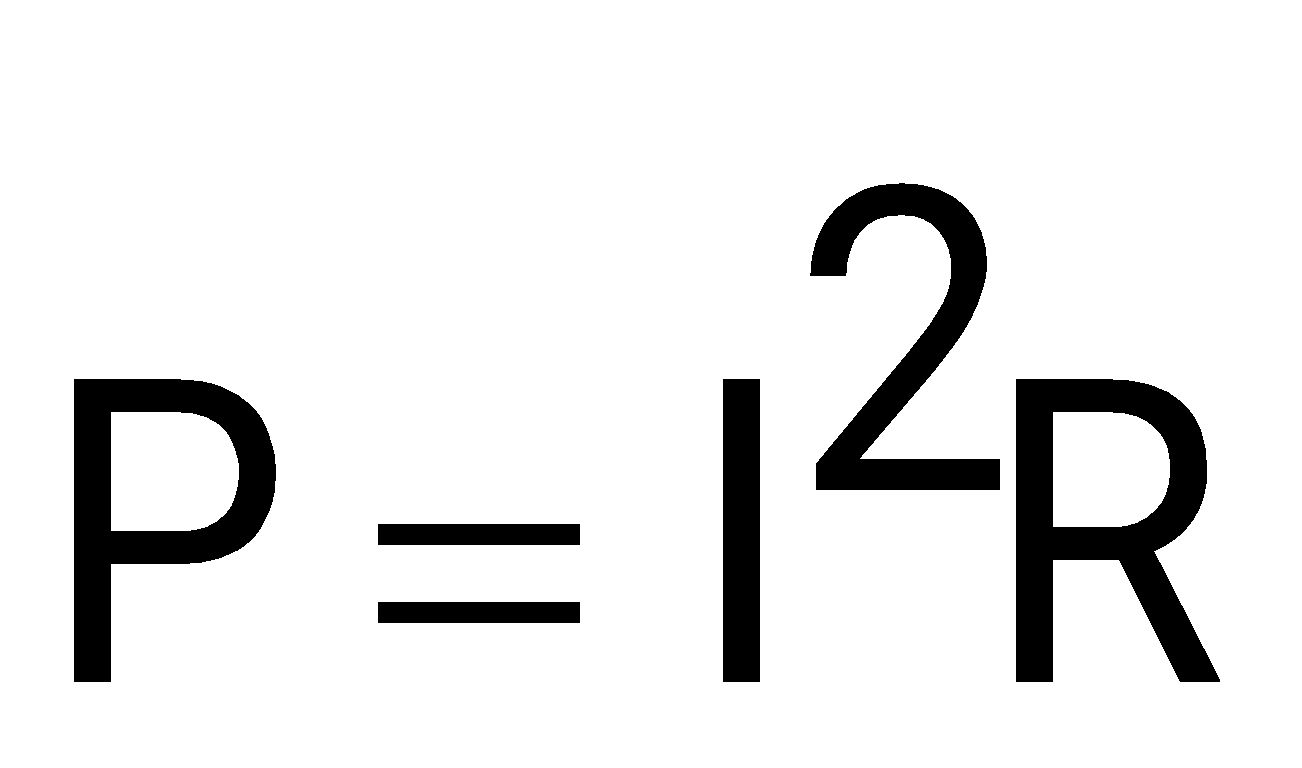

The power dissipated in the resistor R is

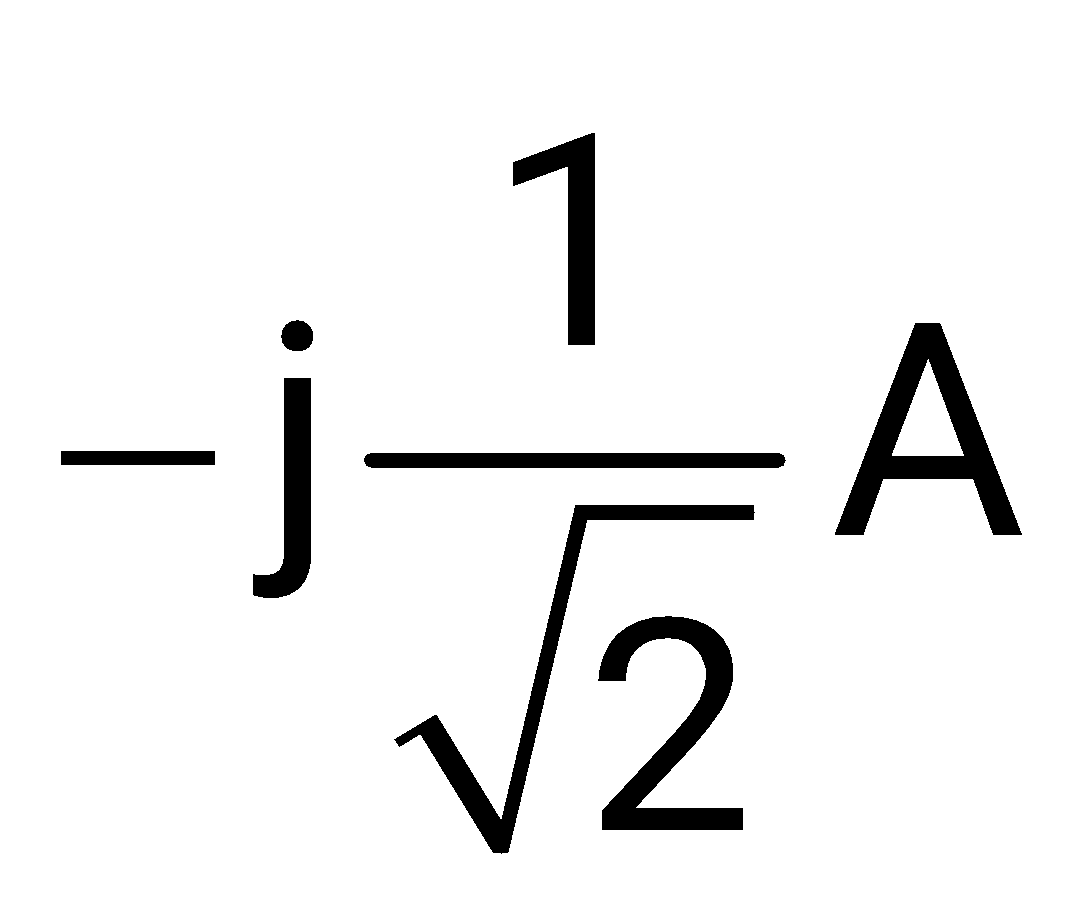

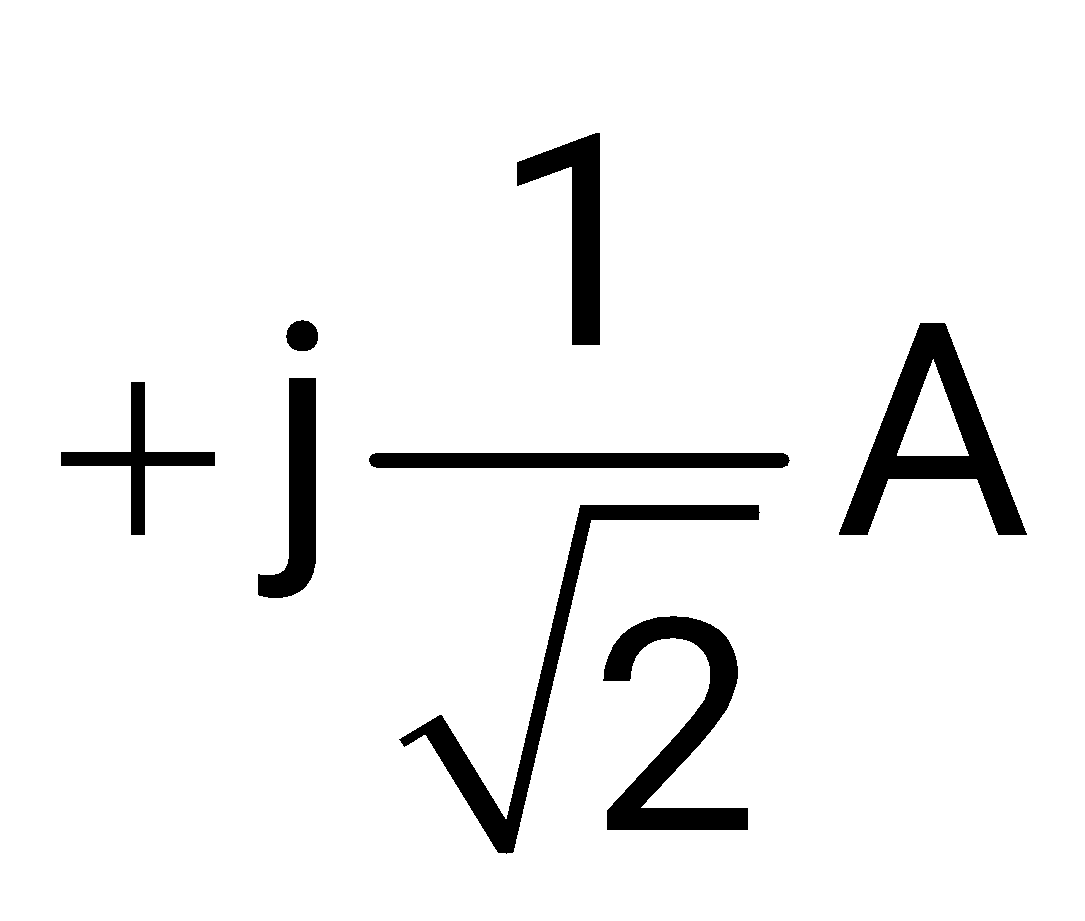

It is given that, ,

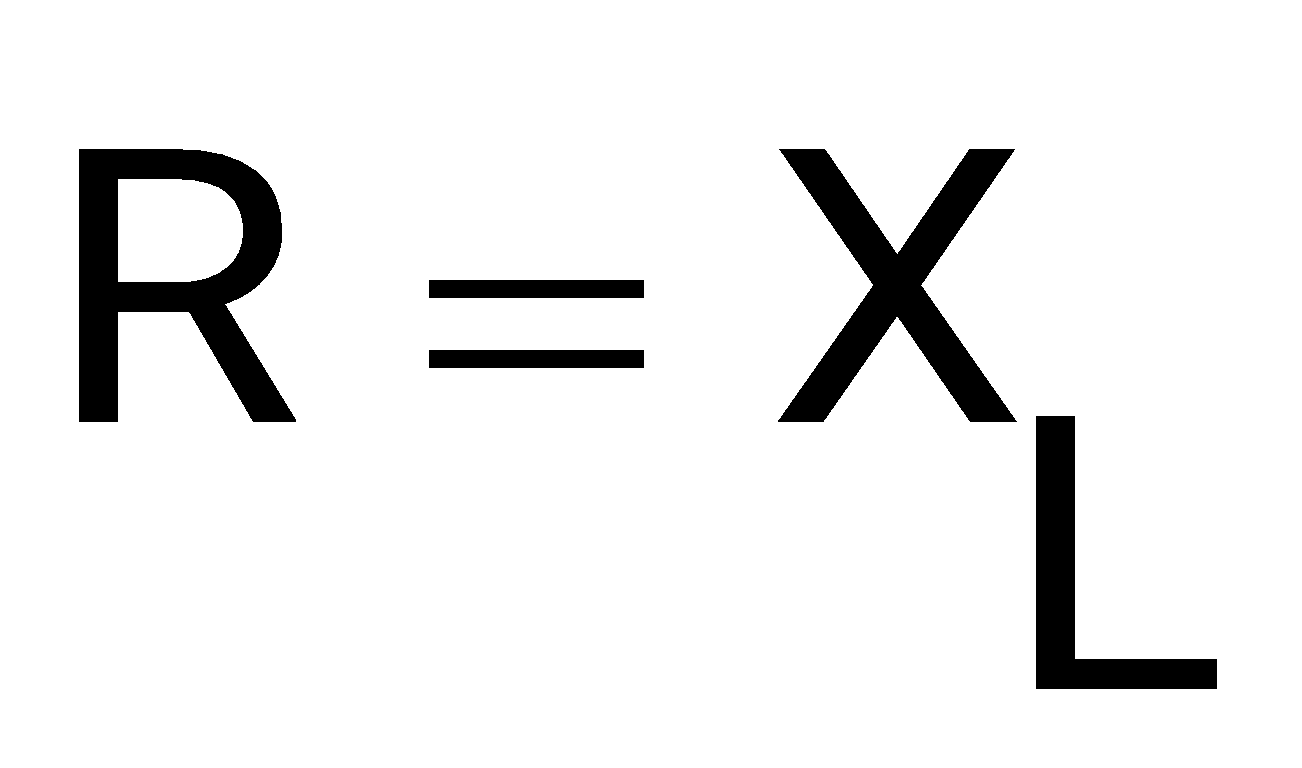

The current in RL branch lags the applied voltage by 45°

Power dissipated in R resistance

P=1W

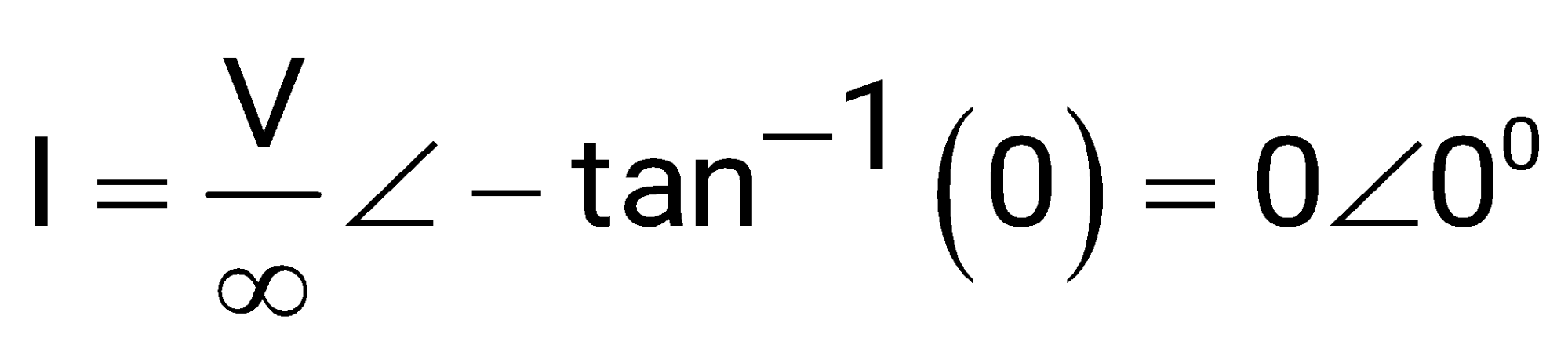

An RLC circuit with relevant data is given below.

The current in the figure above is

Since

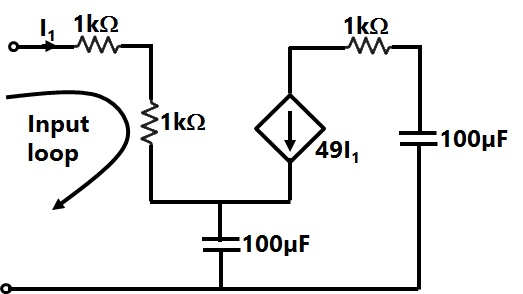

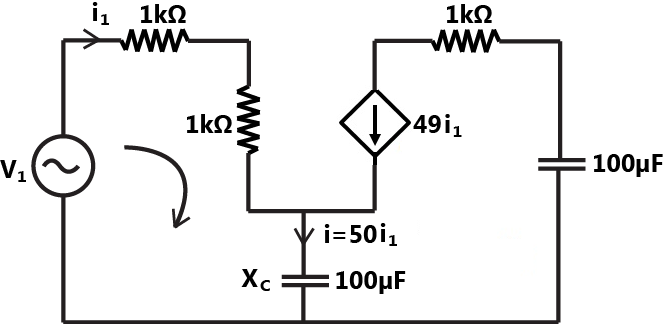

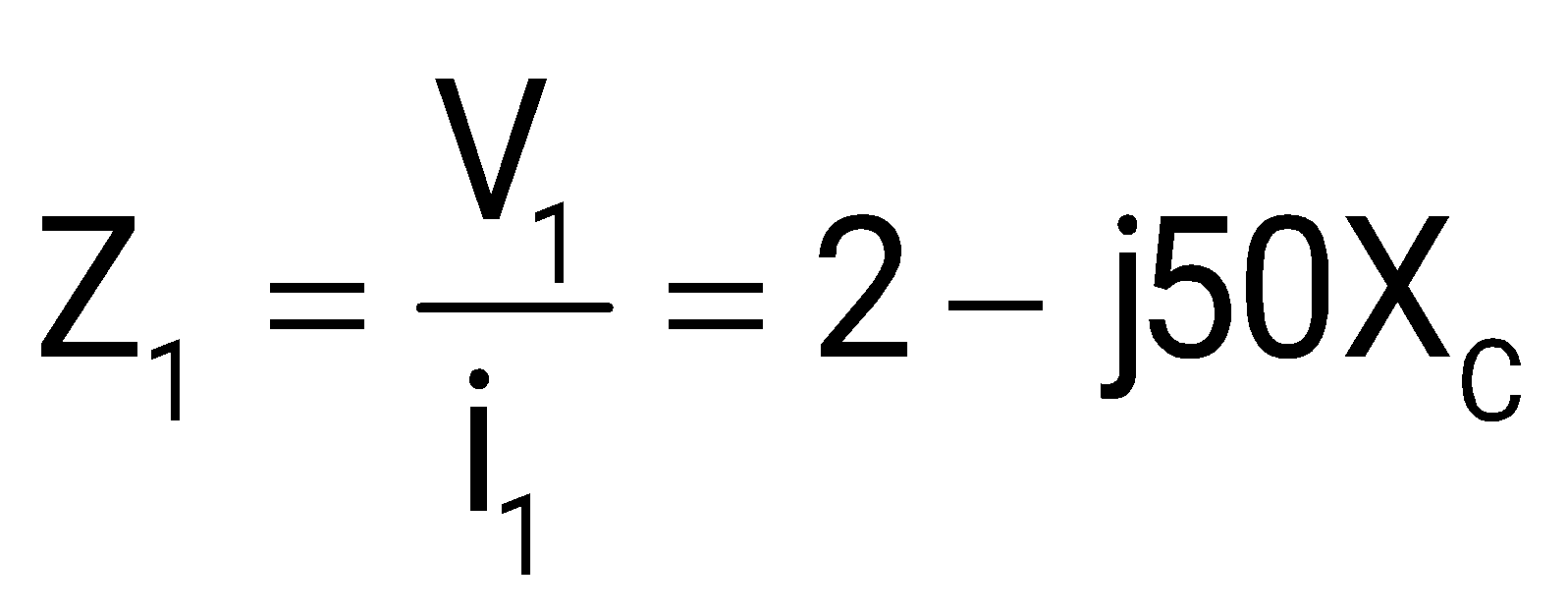

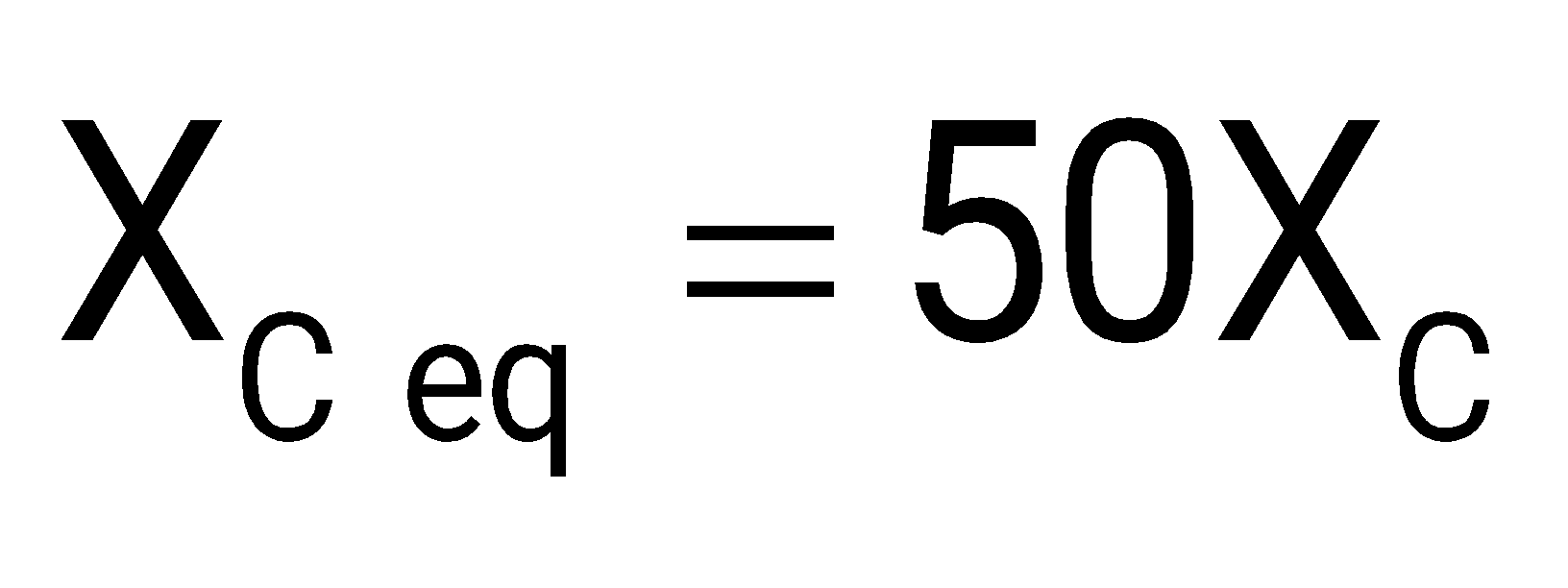

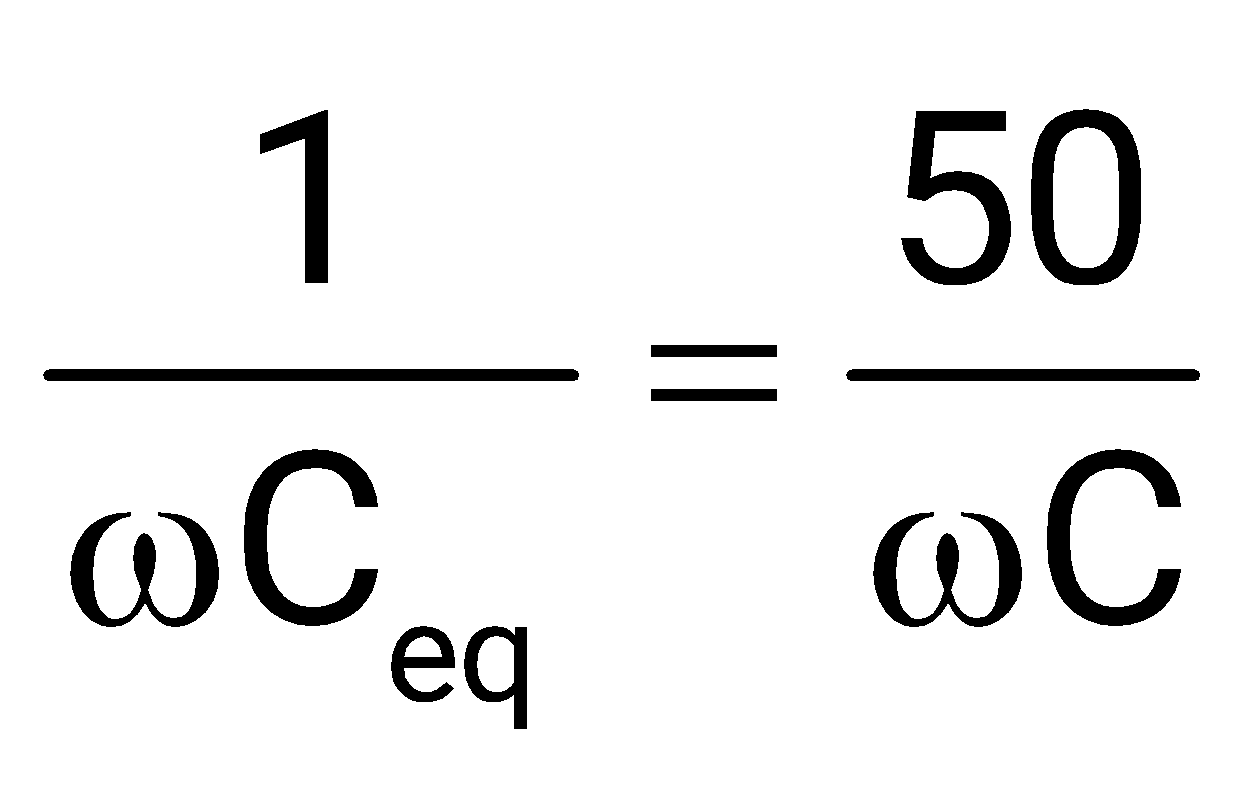

The equivalent capacitance of the input loop of the circuit shown is

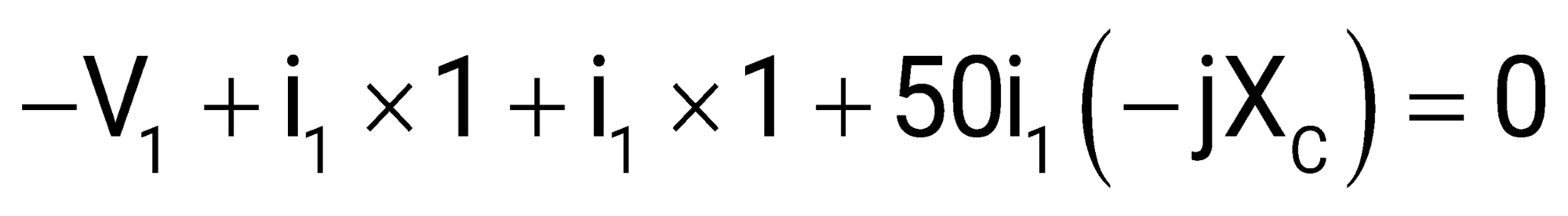

Let us applying a voltage source at input side as shown below,

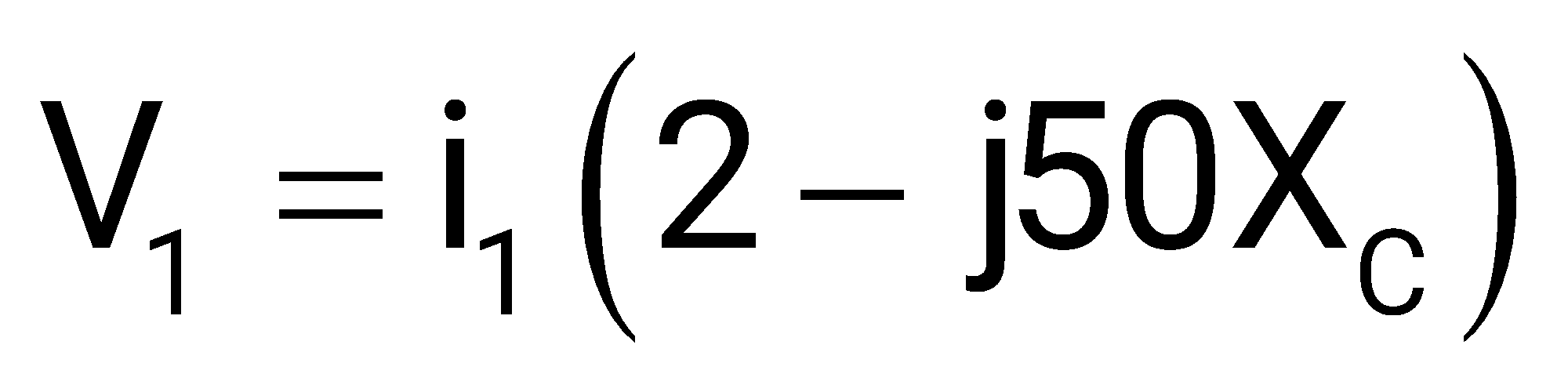

Applying KVL in input loop

Input impedance

Negative imaginary part of impedance shows capacitive reactance

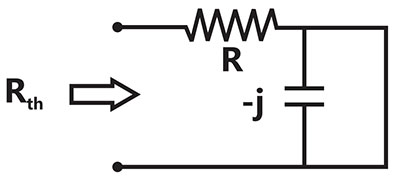

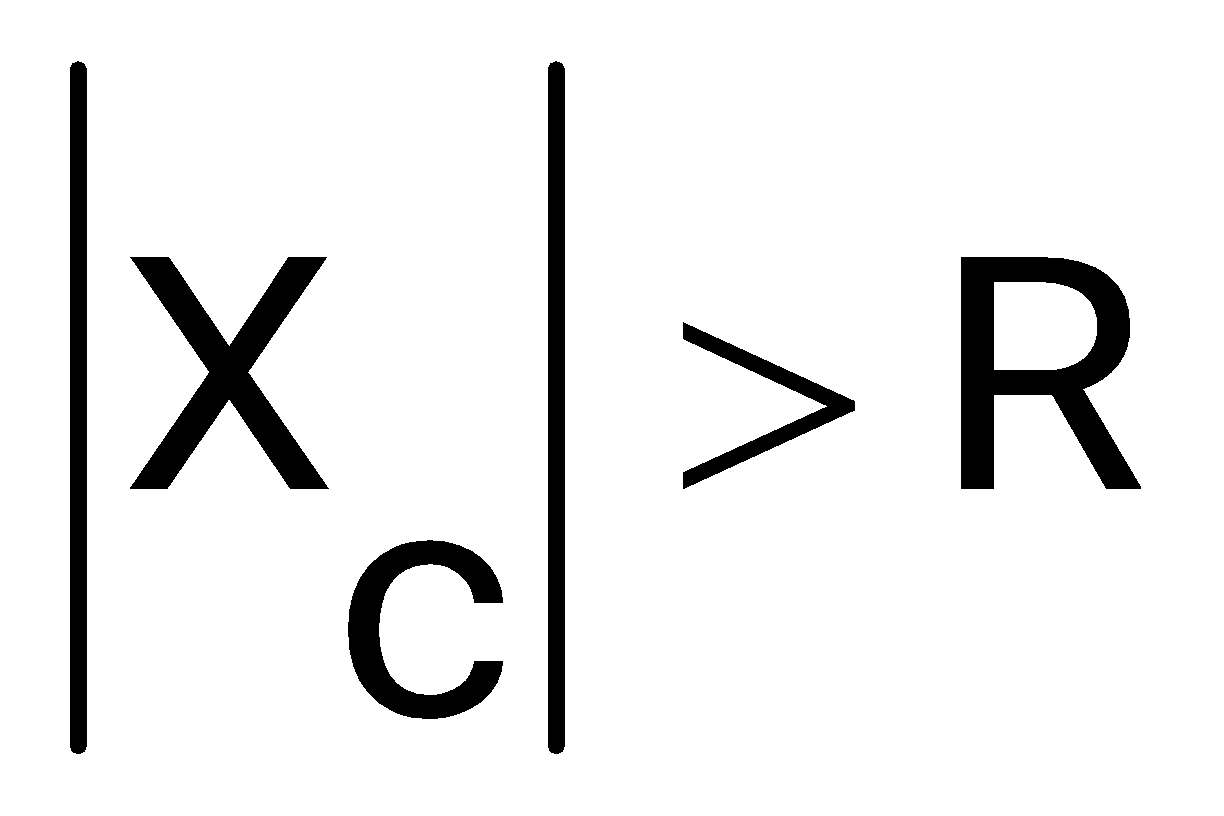

The Thevenin's equivalent of a circuit operating at, has and . At this frequency, the minimal realization of the Thevenin's impedance will have a

Since impedance has non-zero real part

So it has resistance

The impedance is having negative imaginary part. So it has overall reactance as capacitive. It may be purely capacitive or may have both capacitor and inductor having value of capacitive reactance greater than inductive reactance.

But for minimal realization of impedance a resistor and a capacitor will realize the Thevenin impedance.

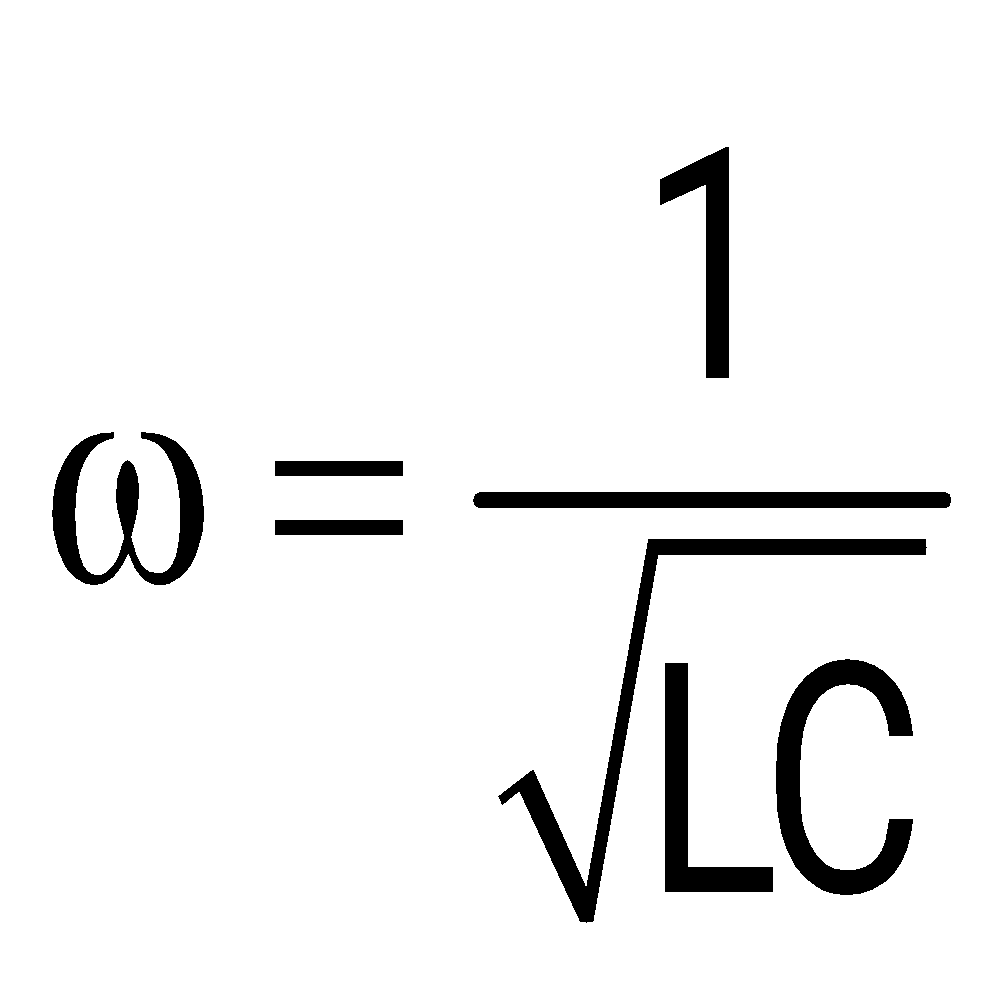

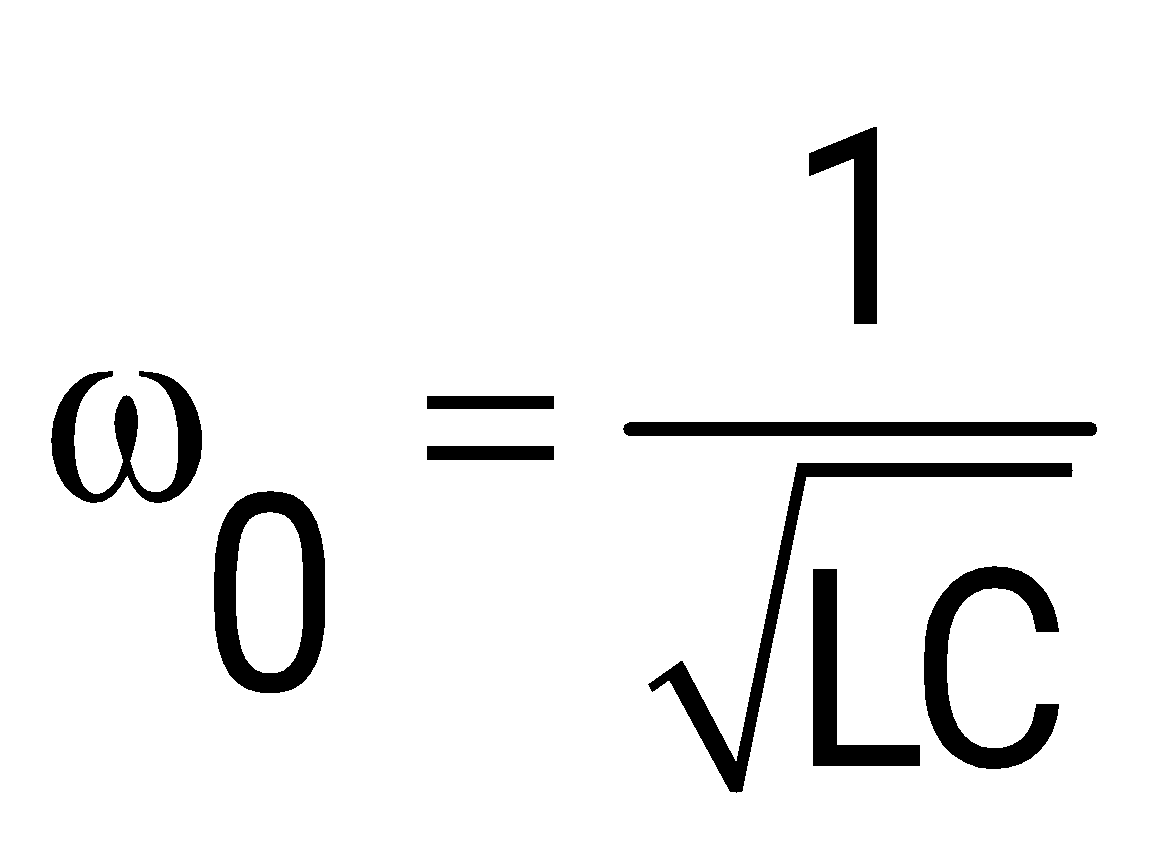

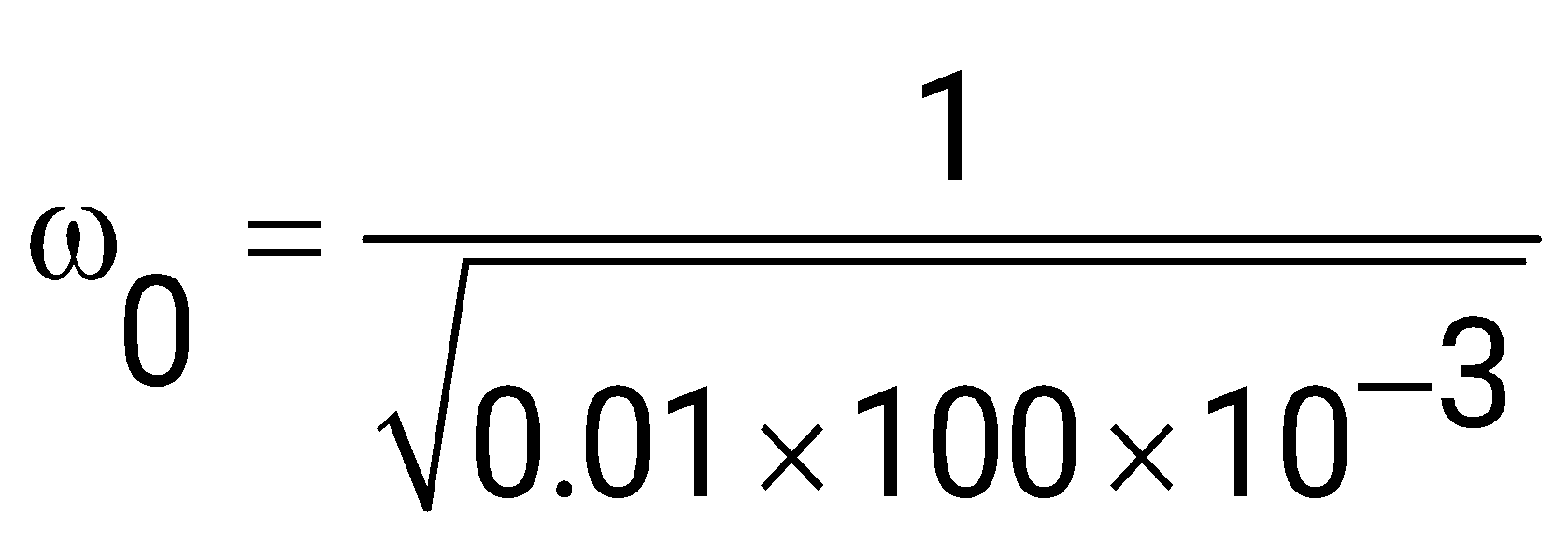

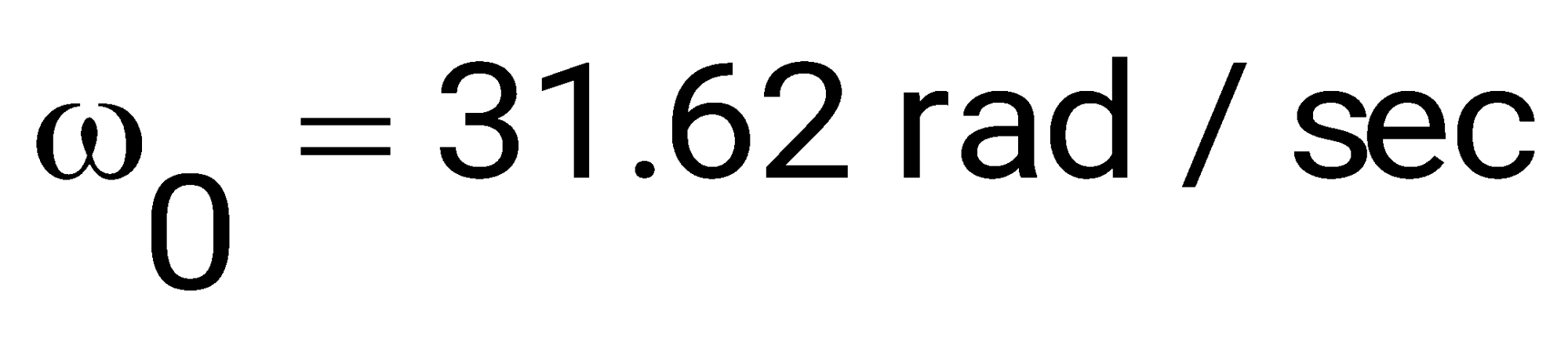

The resonant frequency for the given circuit will be

Representing each element in terms of its impedance, the circuit can be redrawn as shown below,

Impedance of parallel branch,

For resonant frequency imaginary of impedance should zero

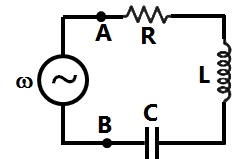

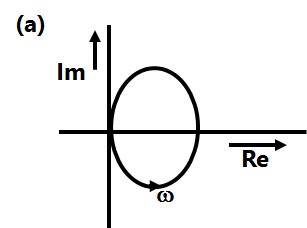

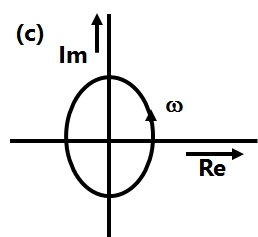

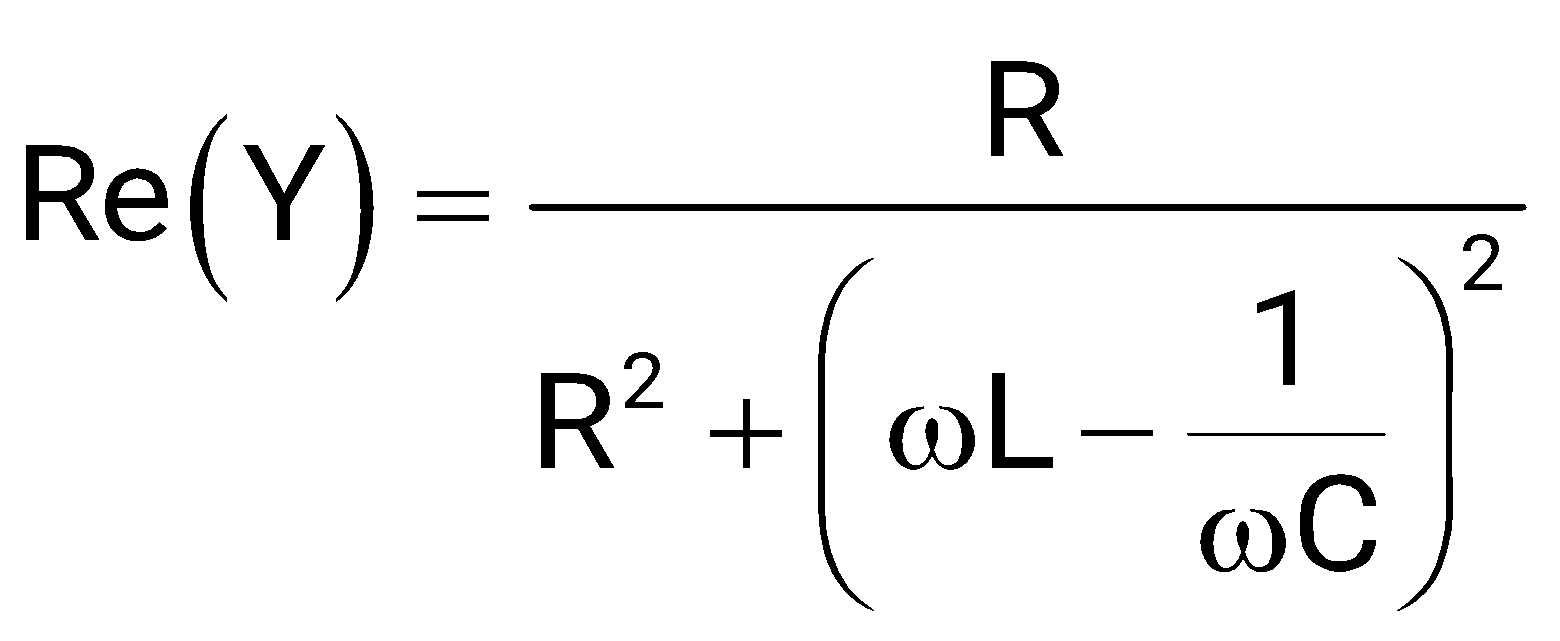

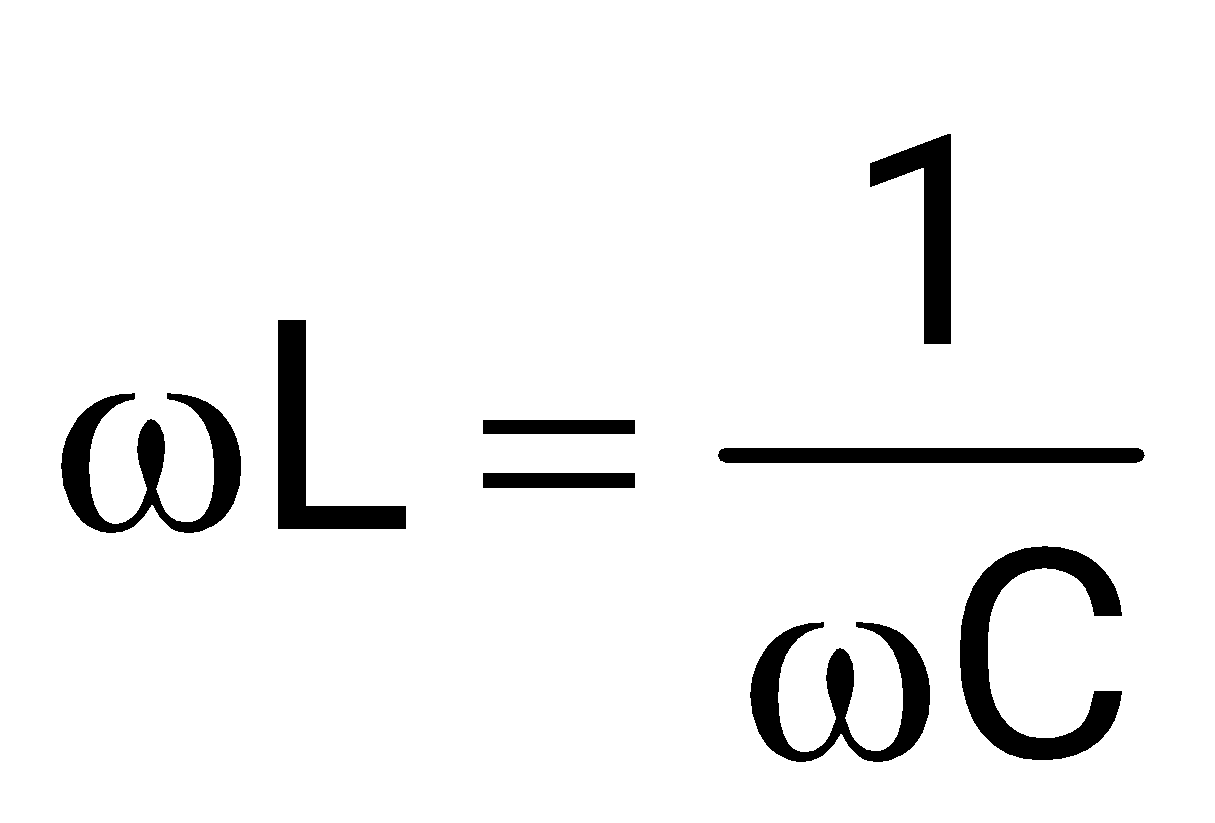

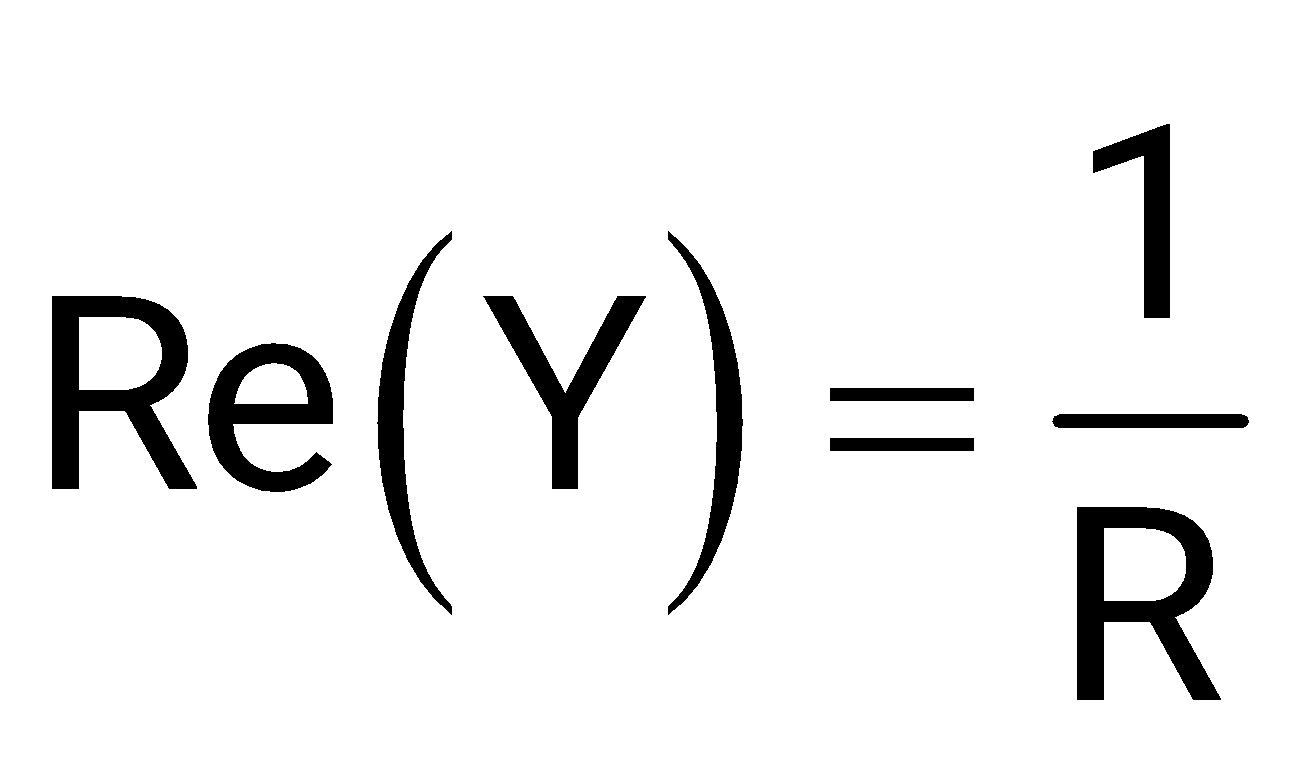

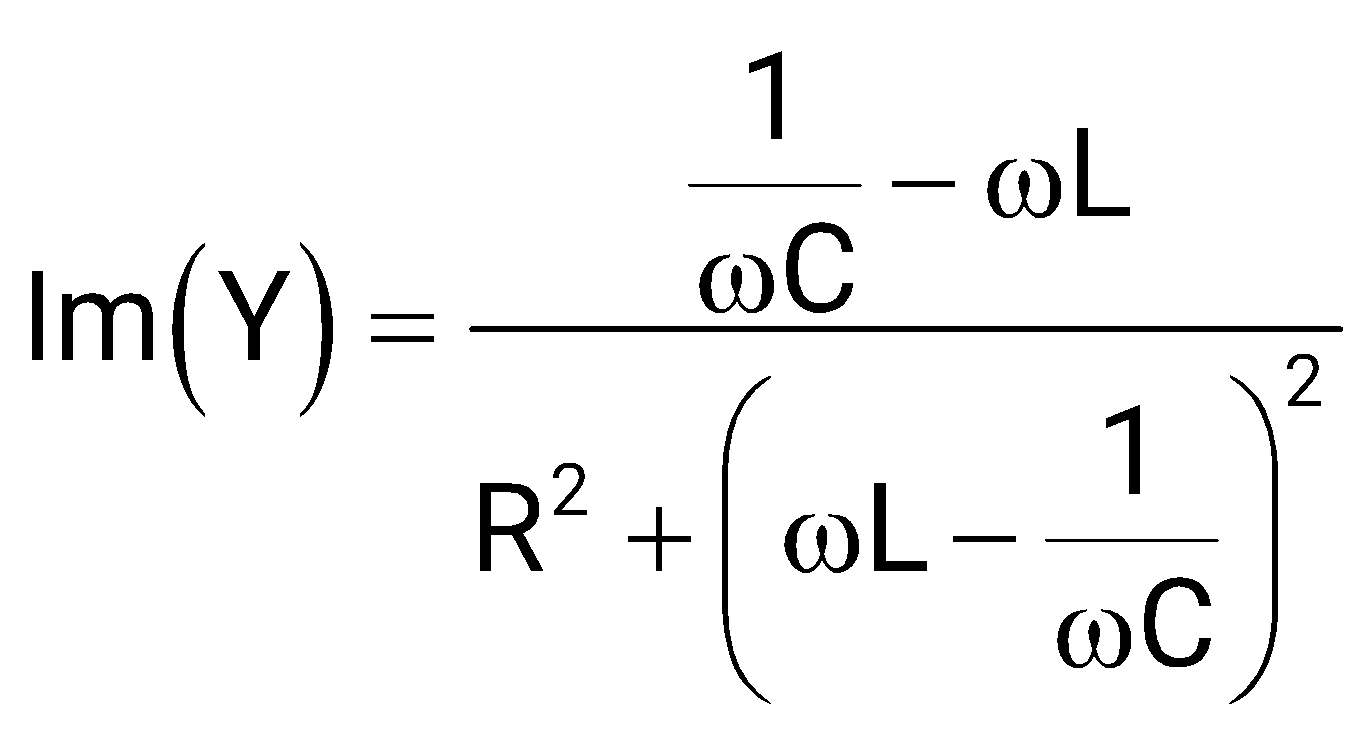

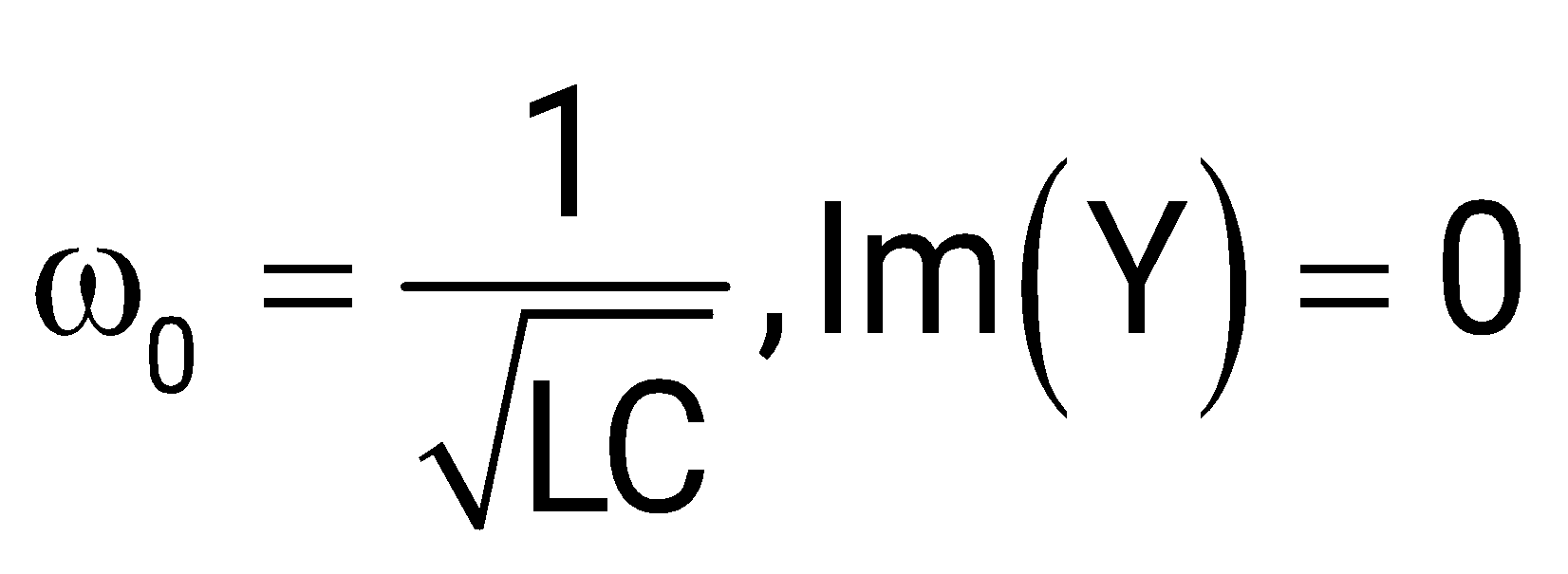

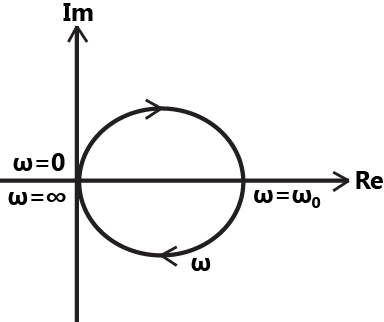

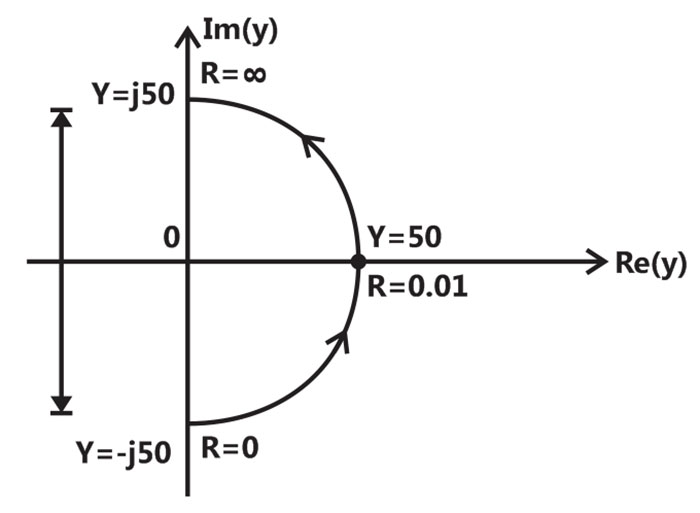

The R-L-C series circuit shown is supplied from a variable frequency voltage source. The admittance-locus of the R-L-C network at terminals AB for increasing frequency ω is

Admittance of the circuit

At

Real part of admittance

Real part will always be positive

At

[Maximum value]

Imaginary part of admittance

At

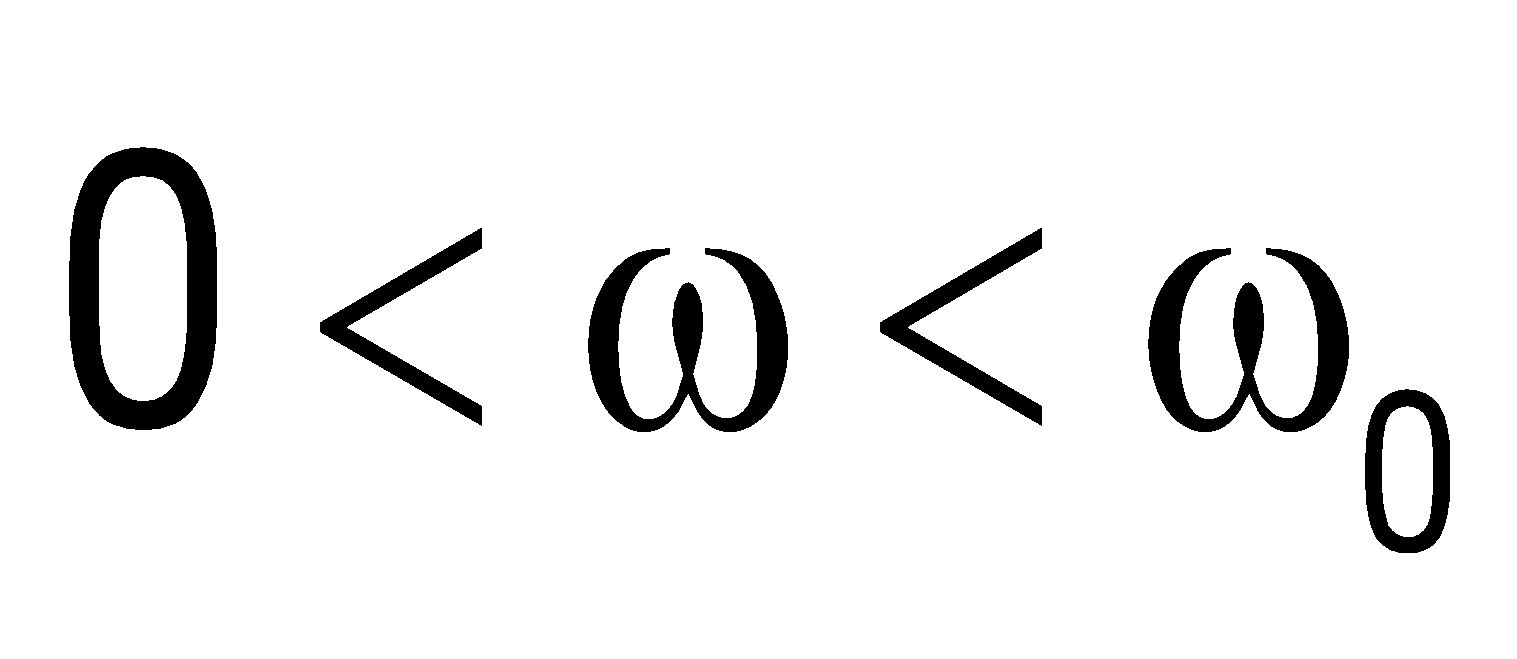

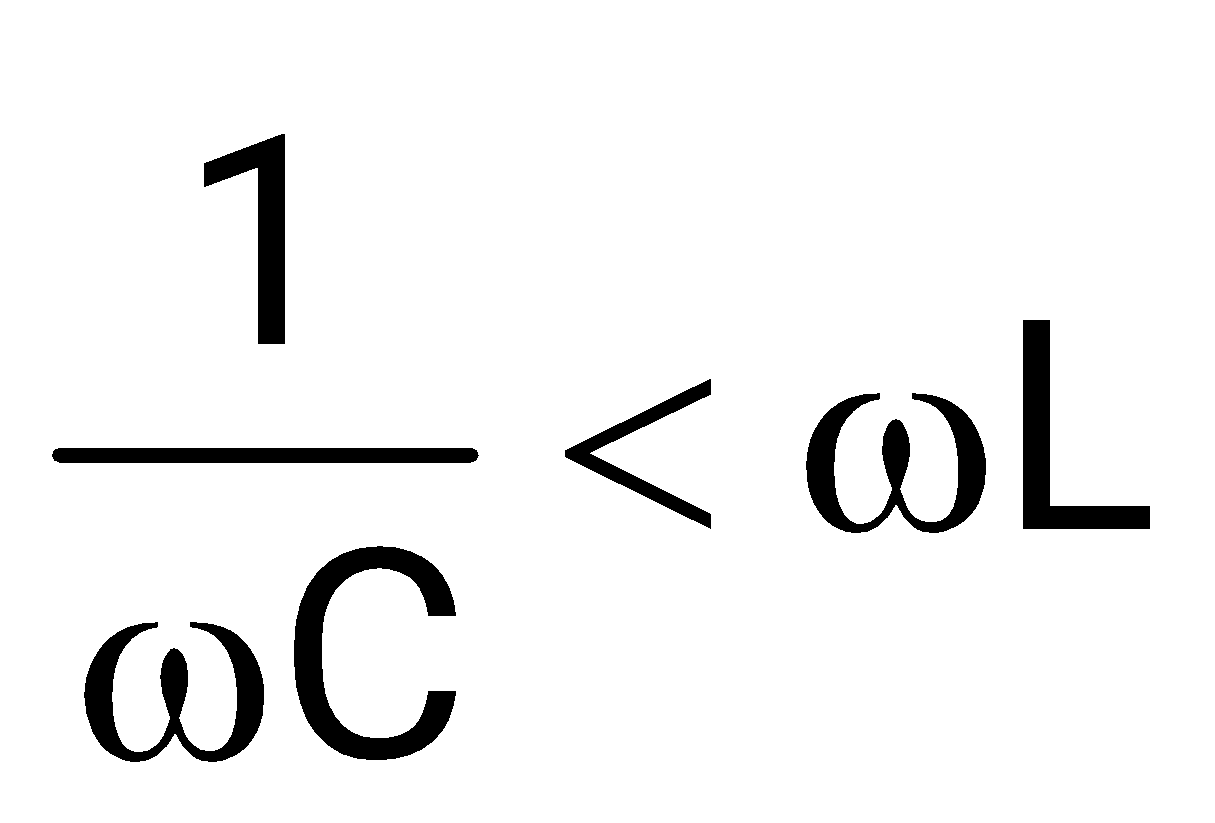

For

For

So the locus of admittance looks like as shown above.

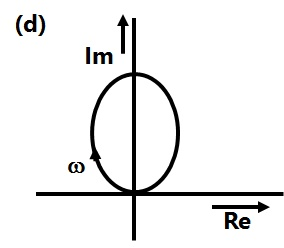

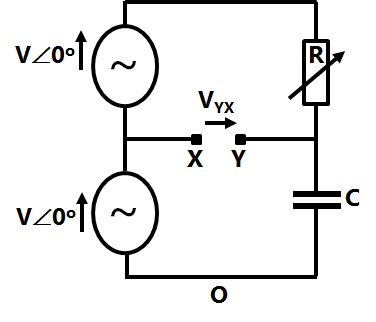

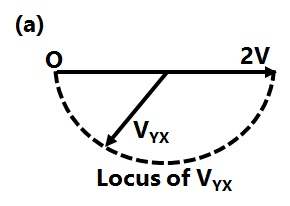

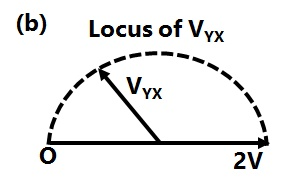

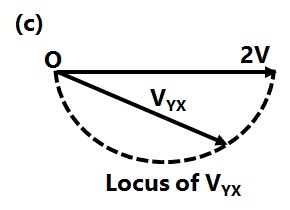

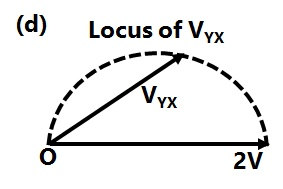

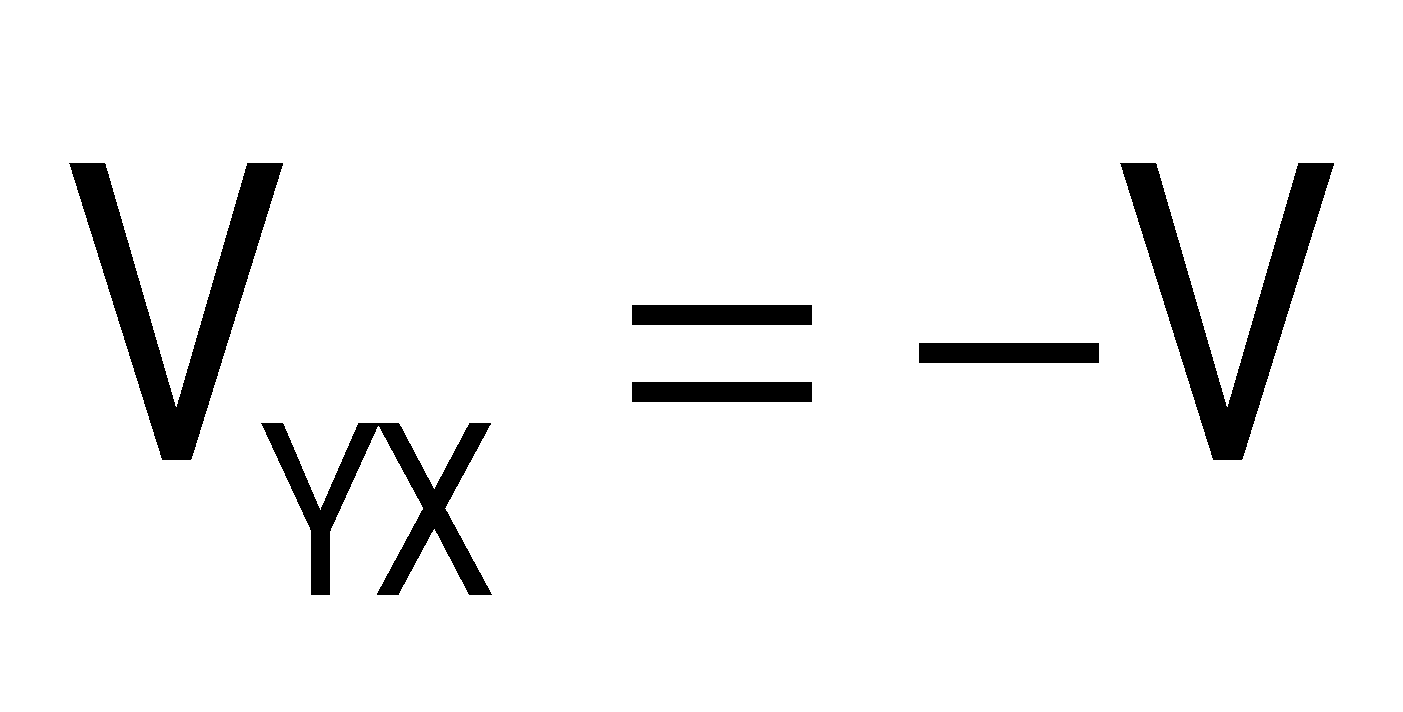

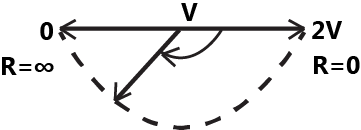

In the figure given below all phasors are with reference to the potential at point "O". The locus of voltage phasor as R is varied from zero to infinity is shown by

Reactance of

Applying KVL

When

When

Hence, the locus looks like as shown above.

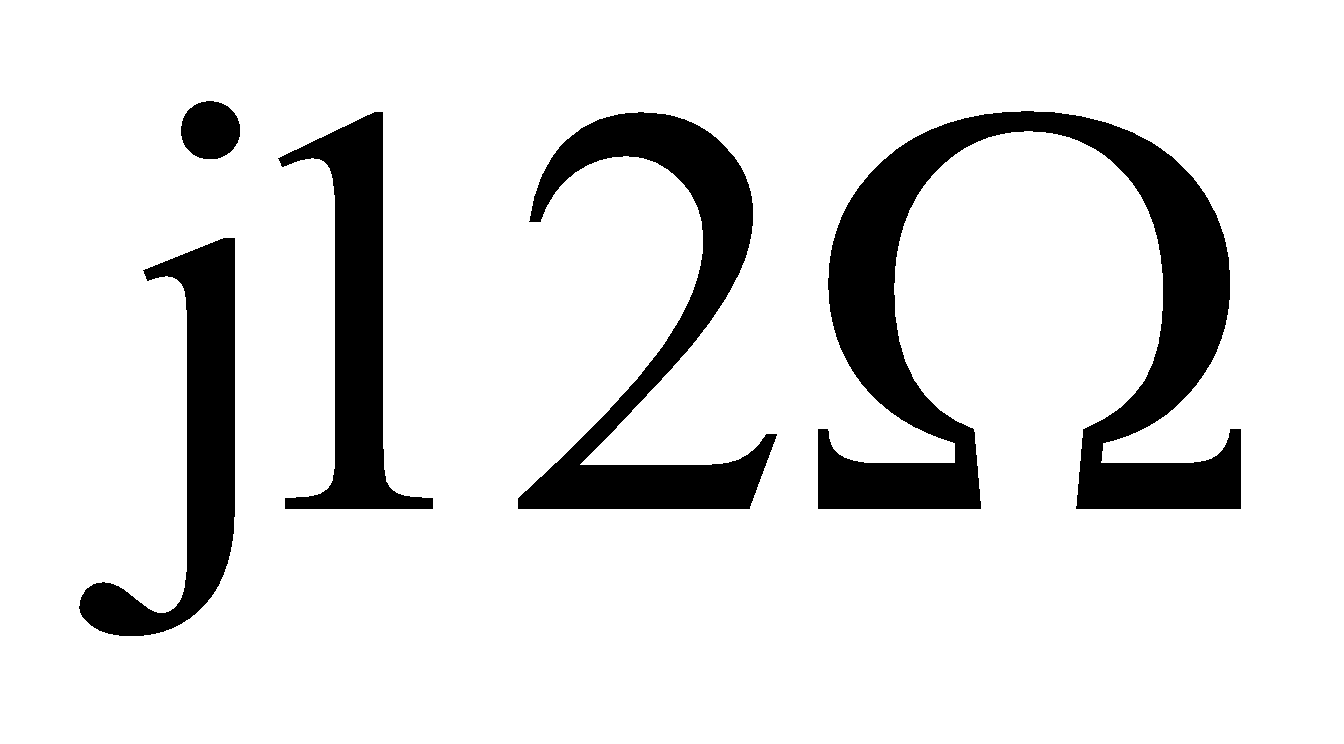

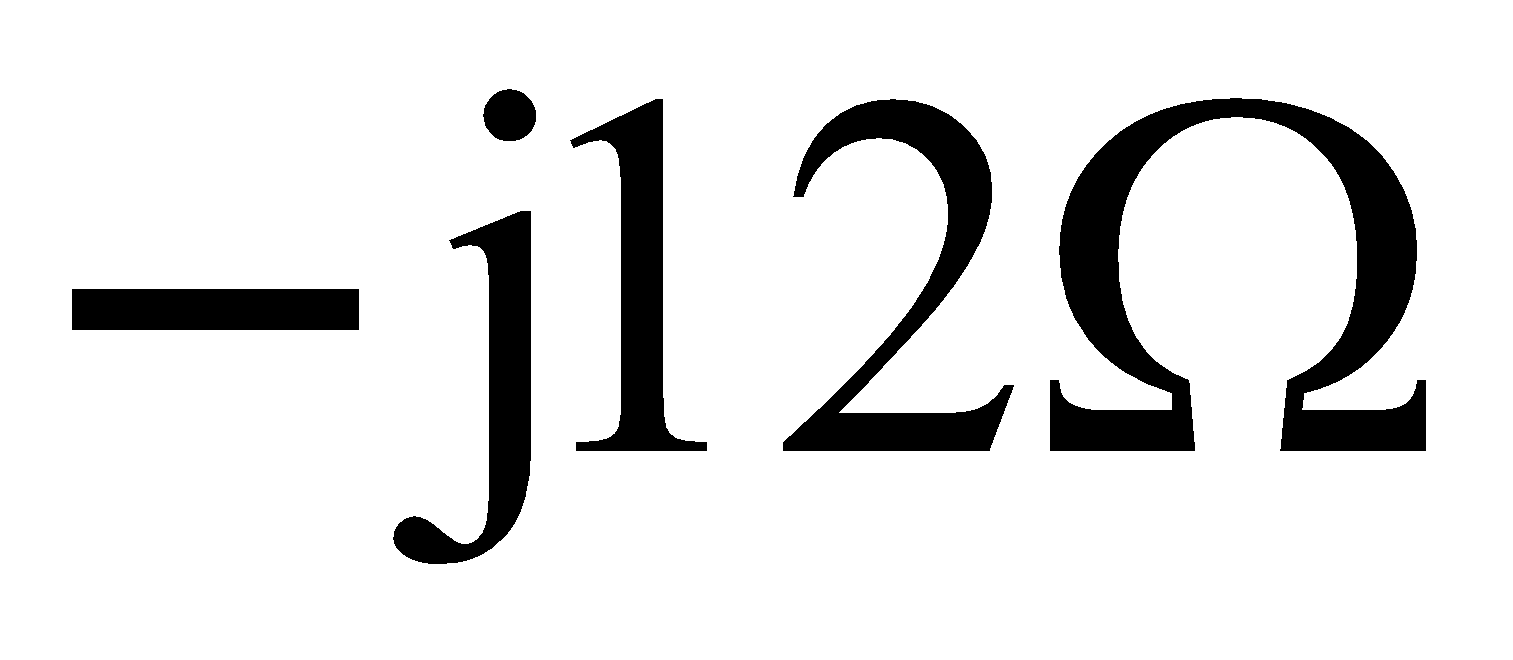

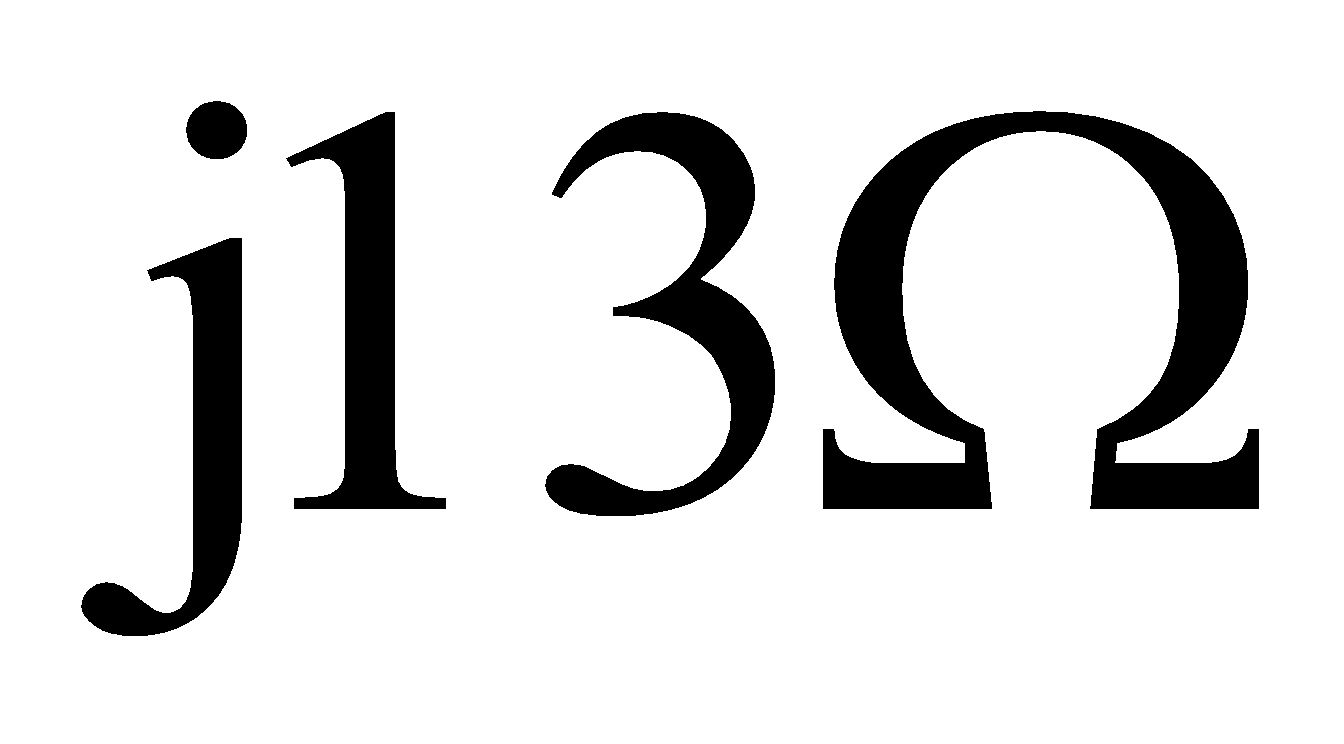

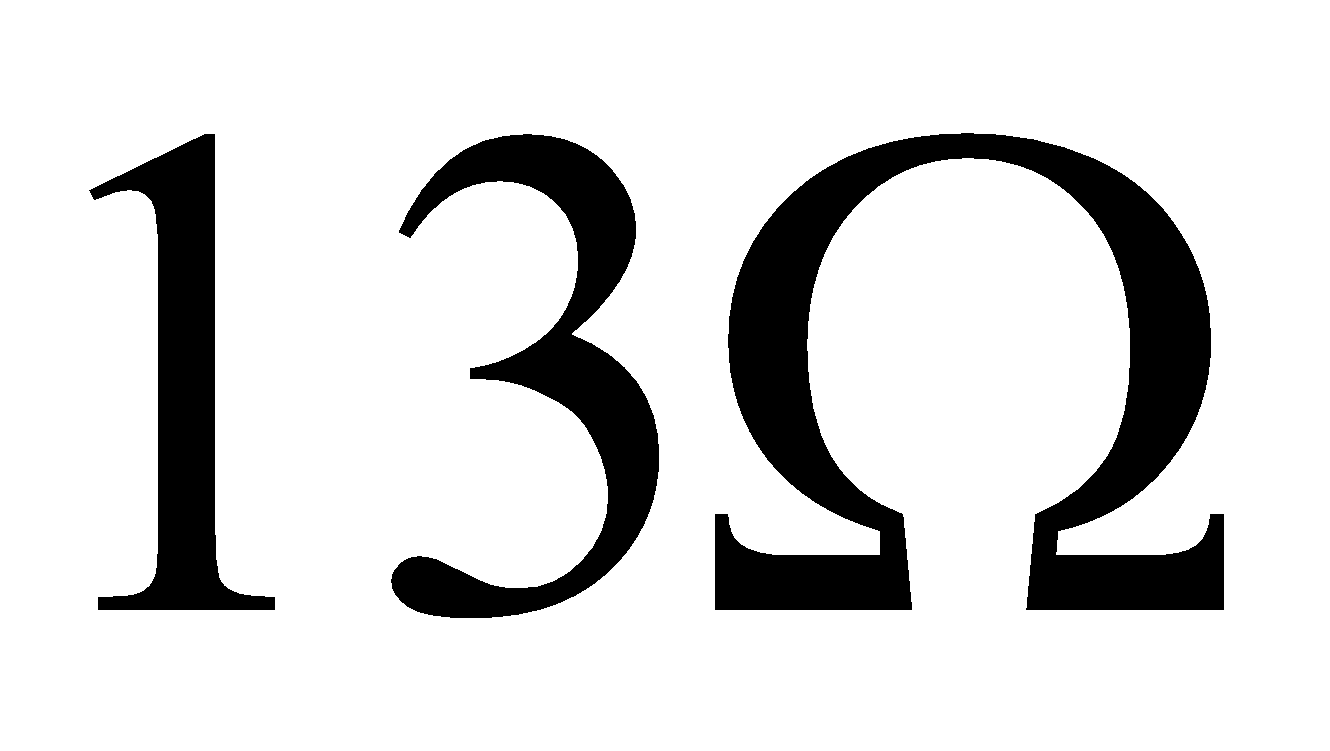

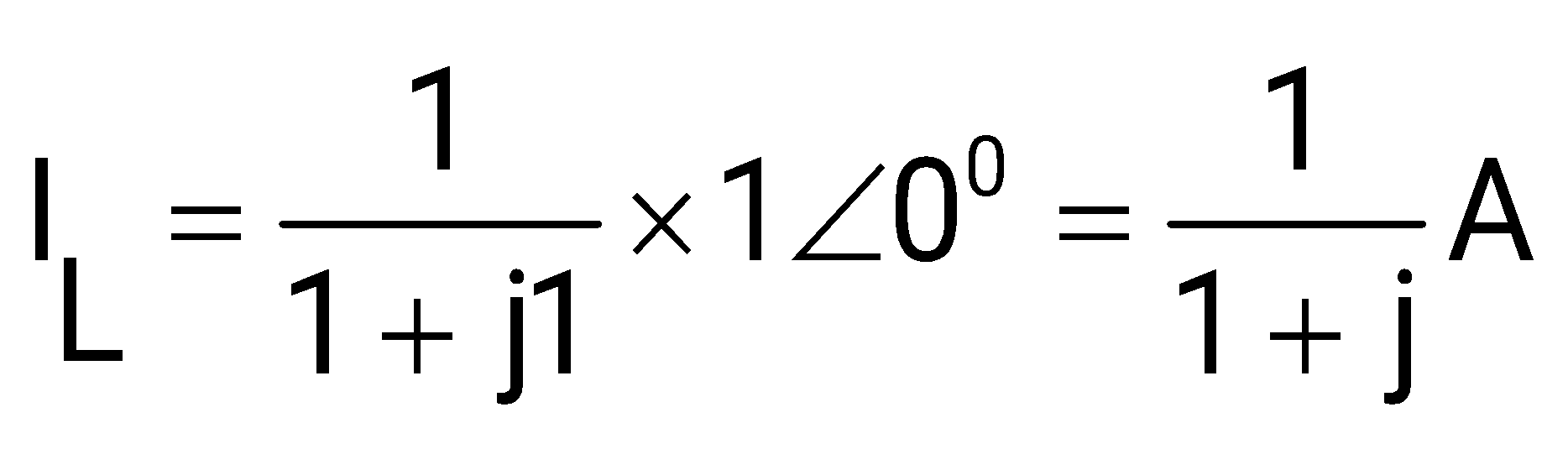

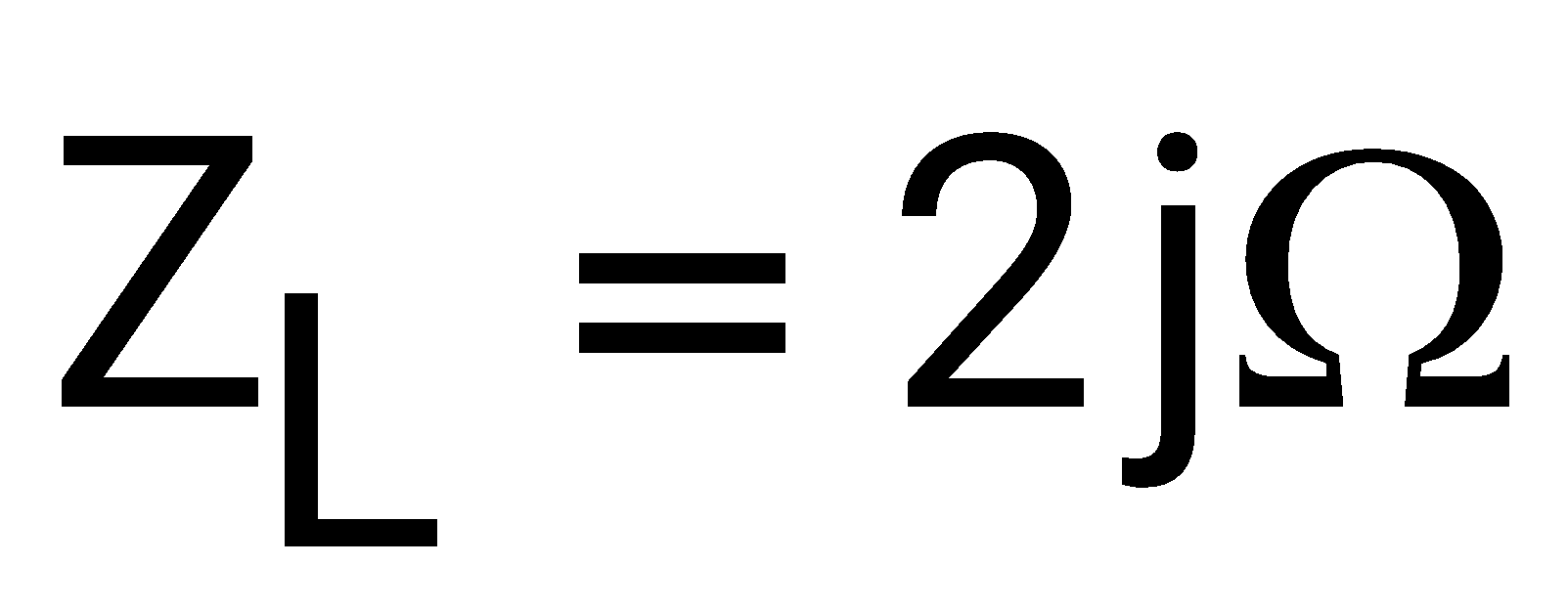

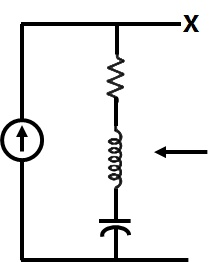

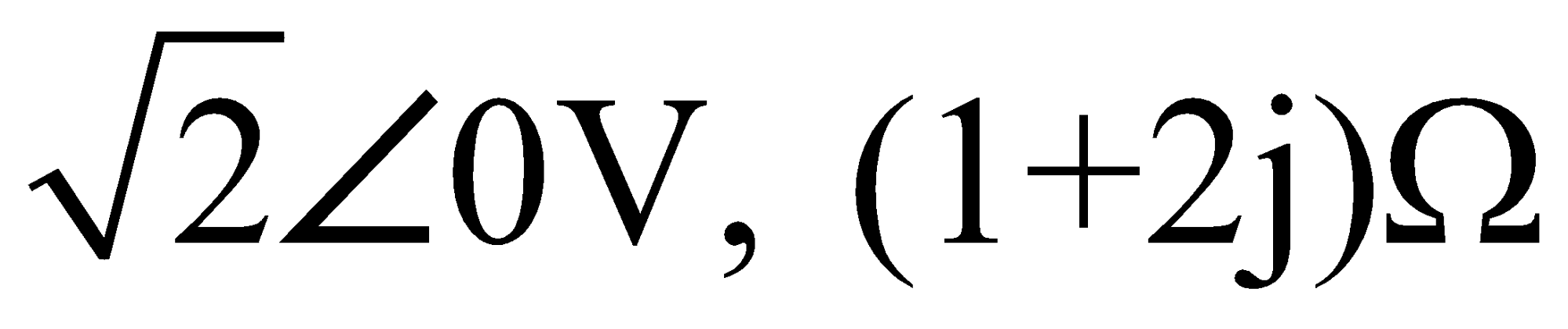

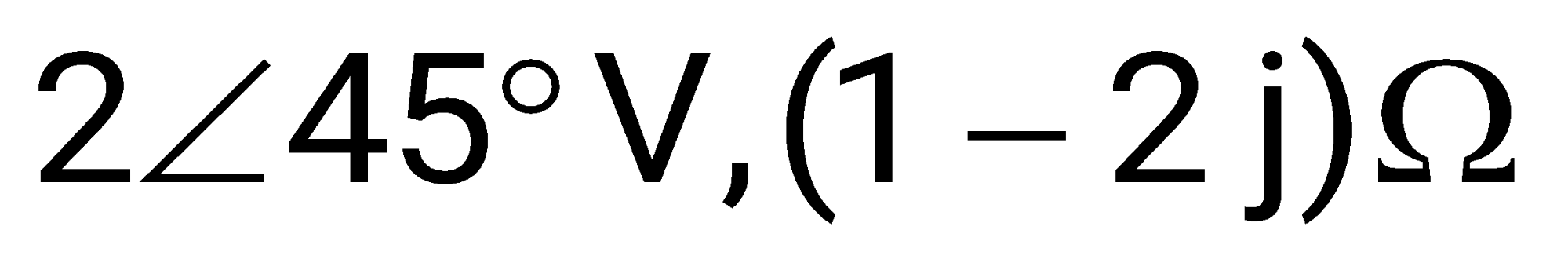

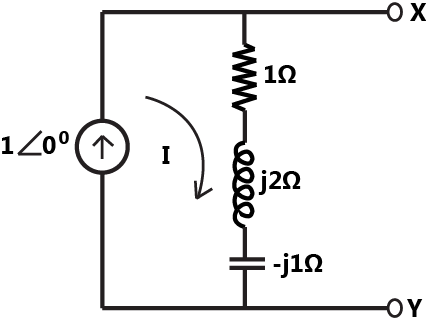

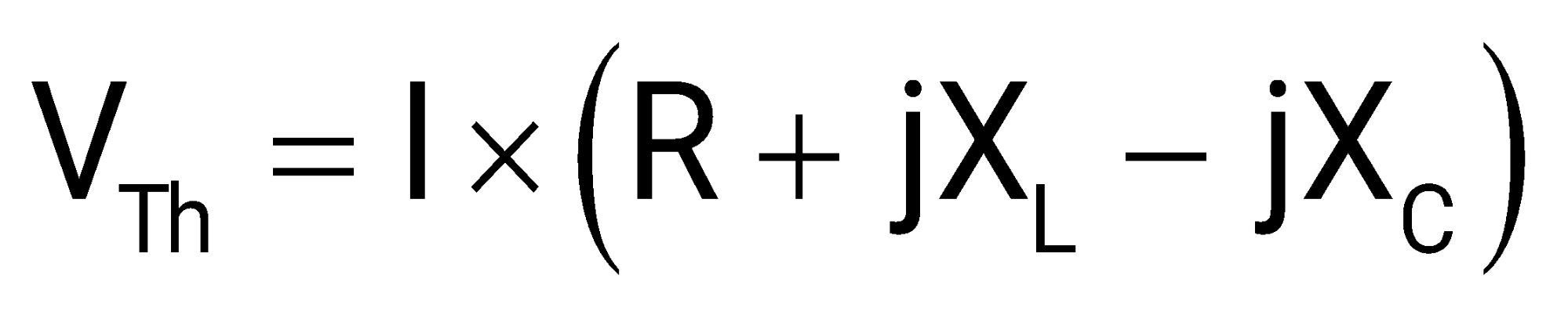

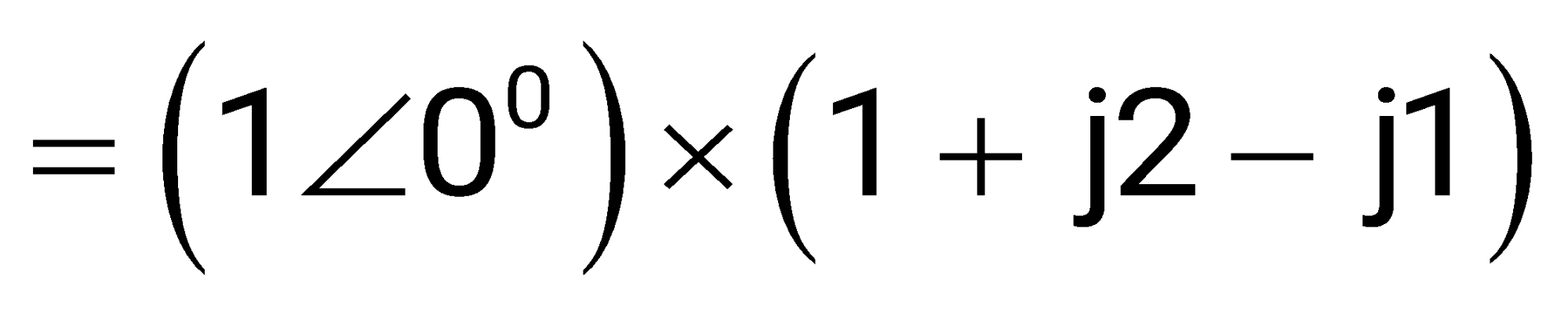

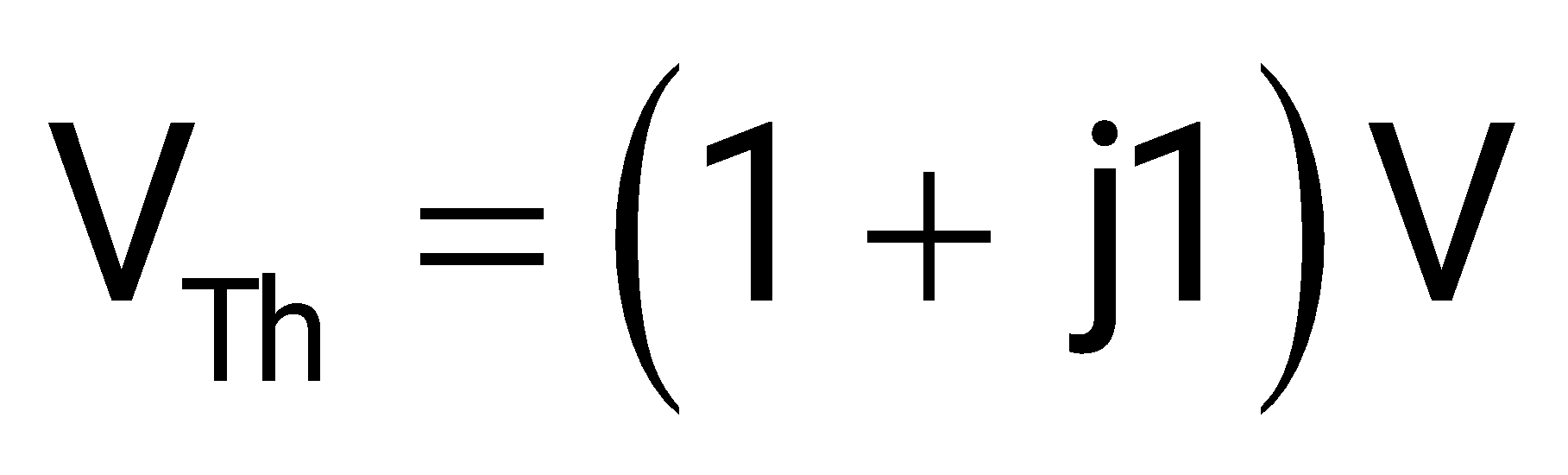

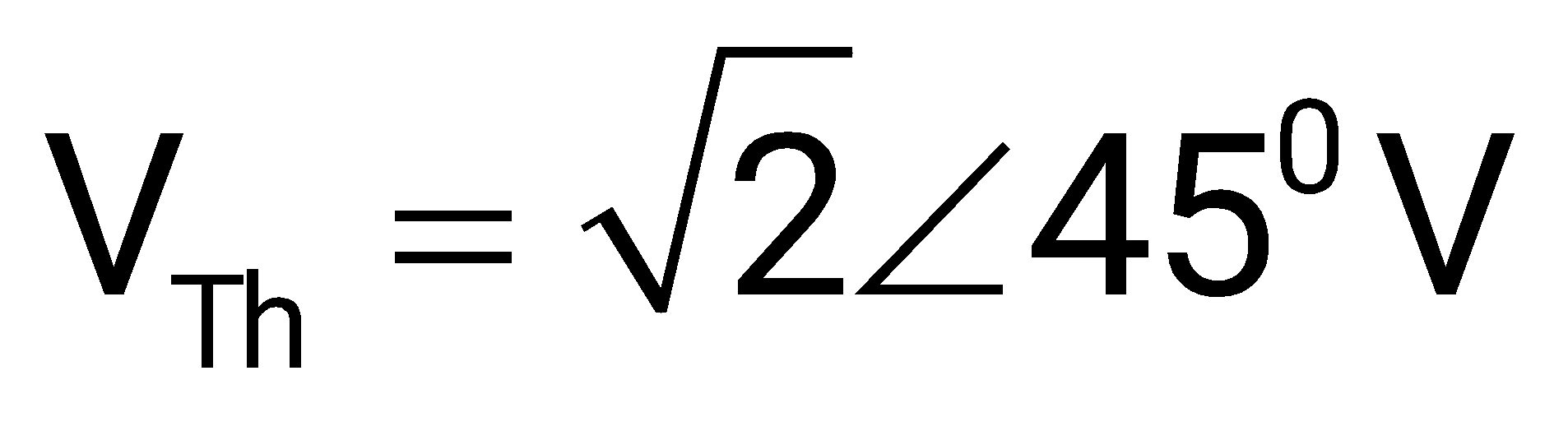

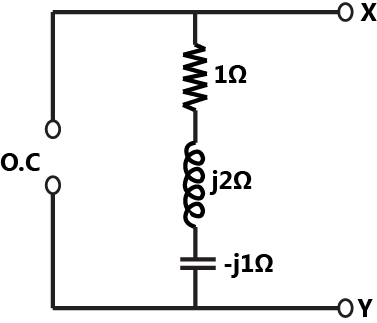

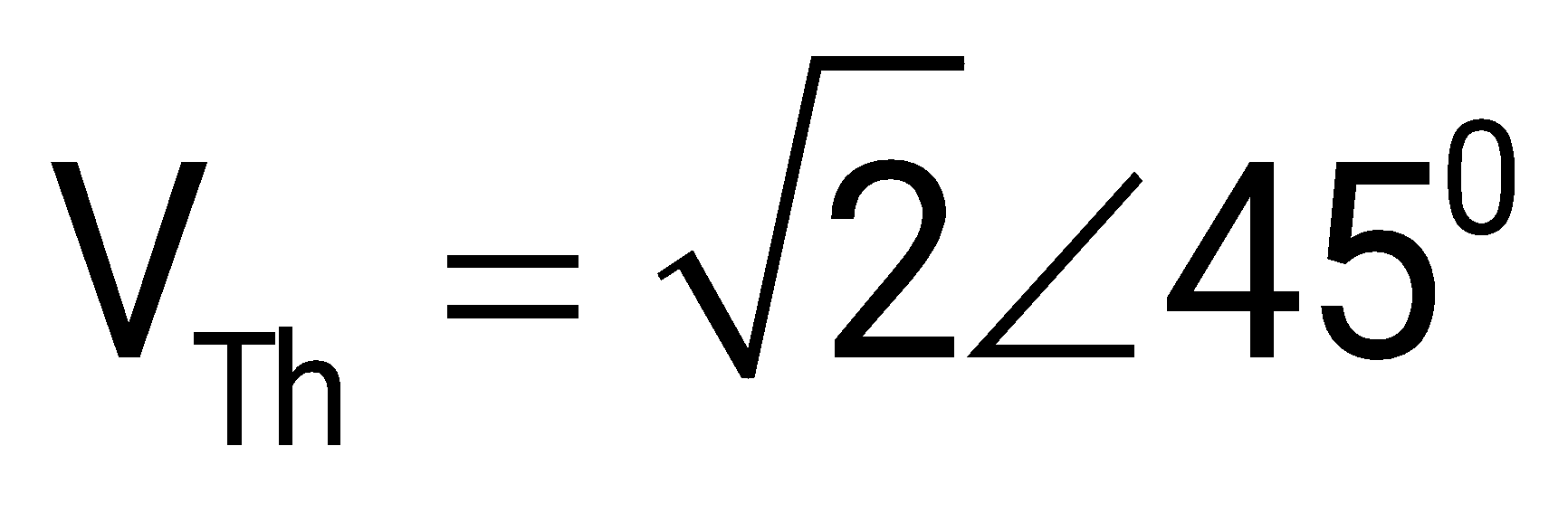

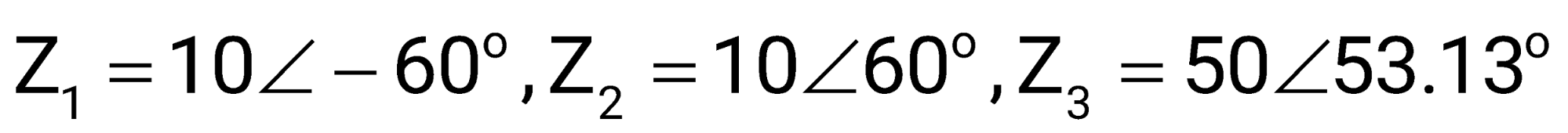

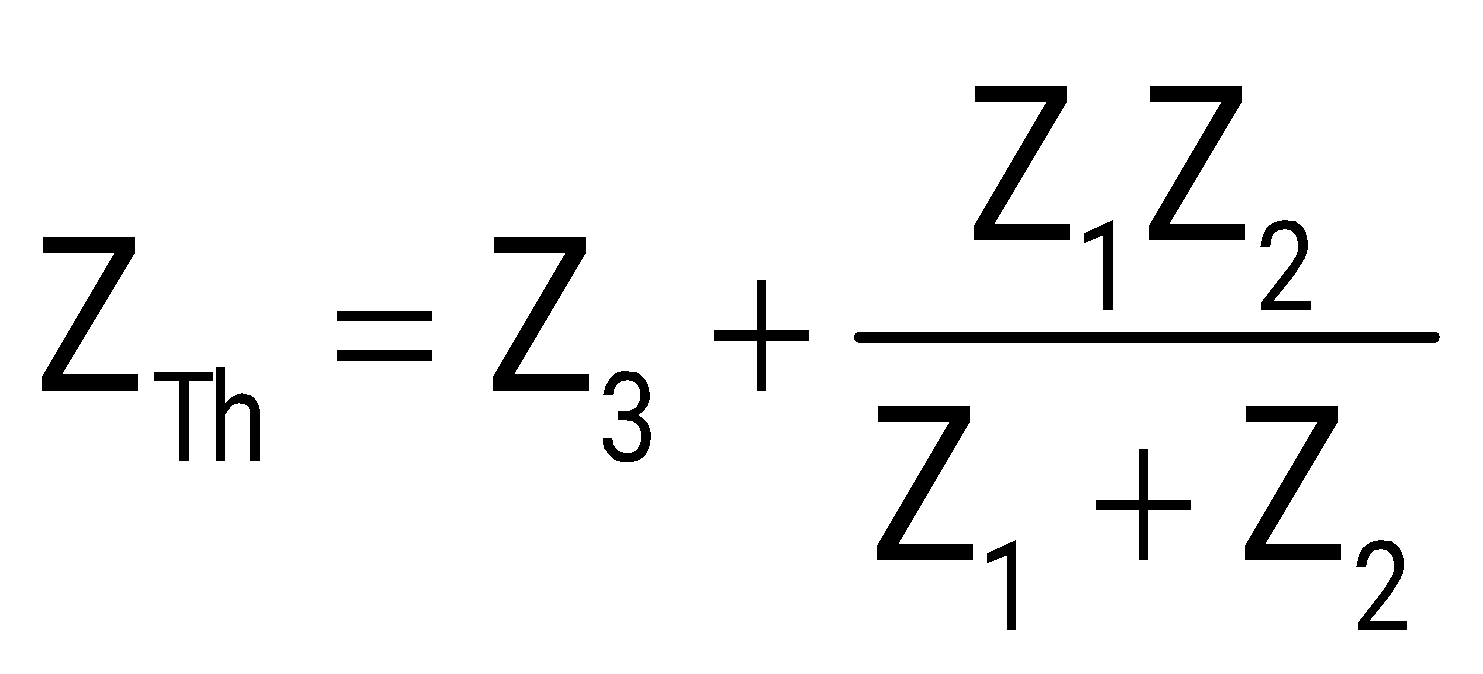

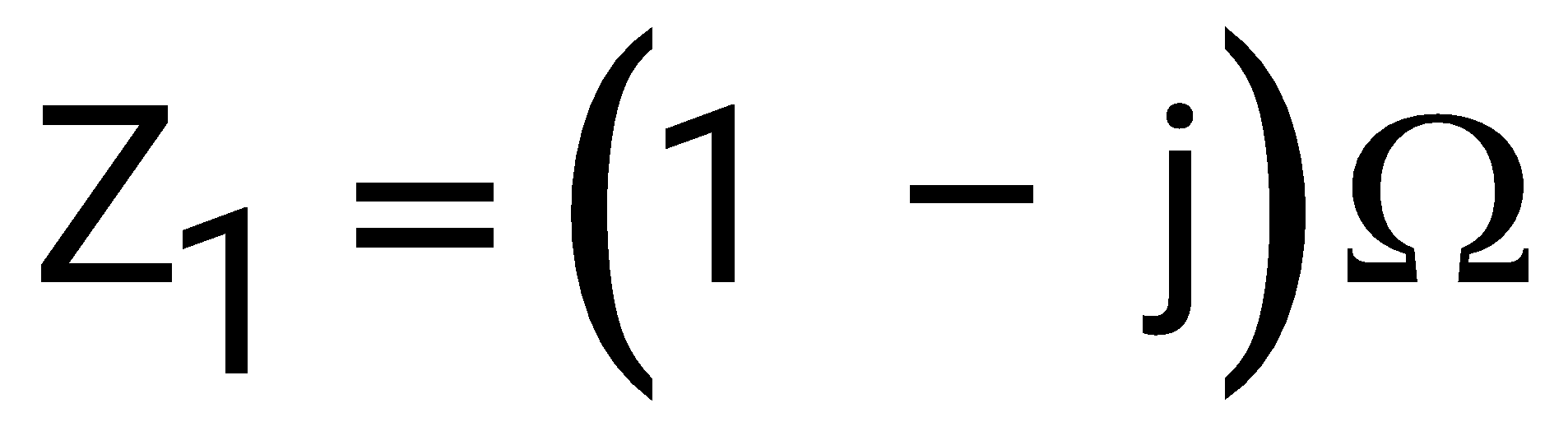

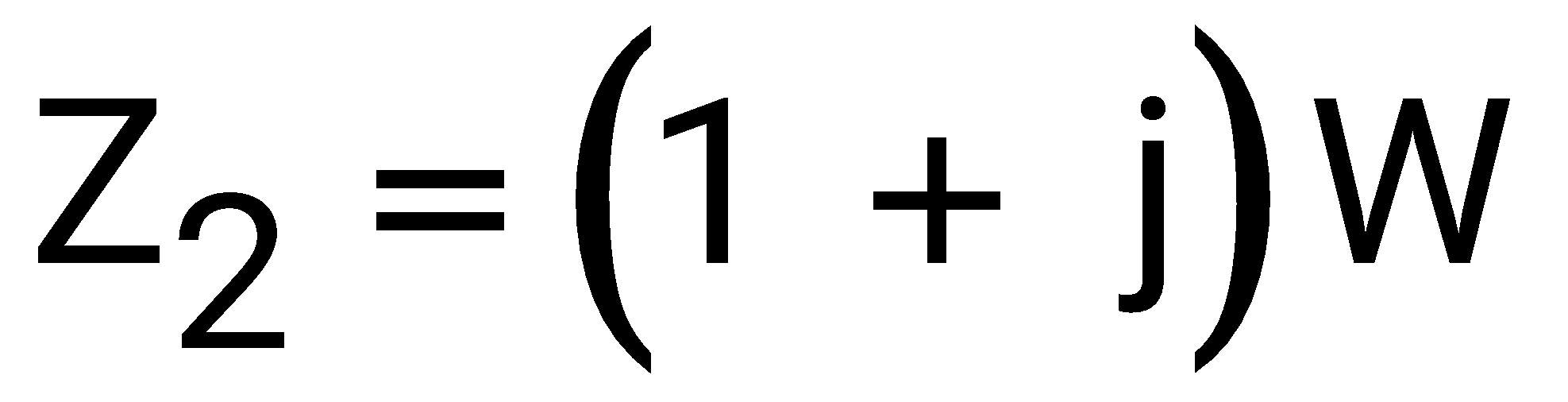

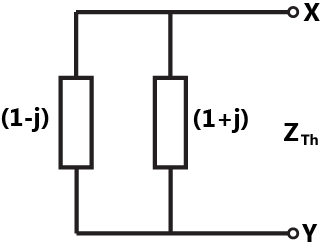

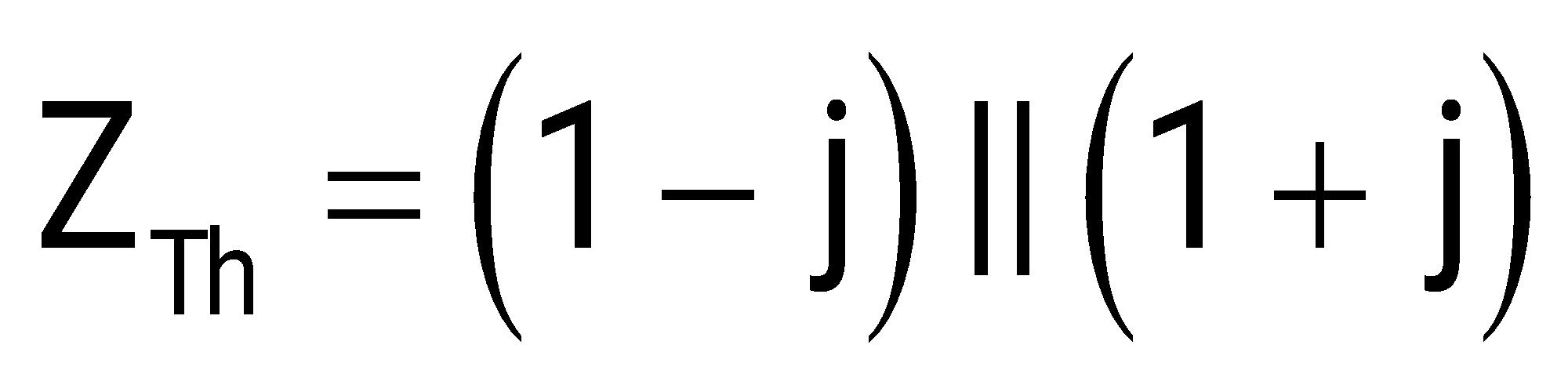

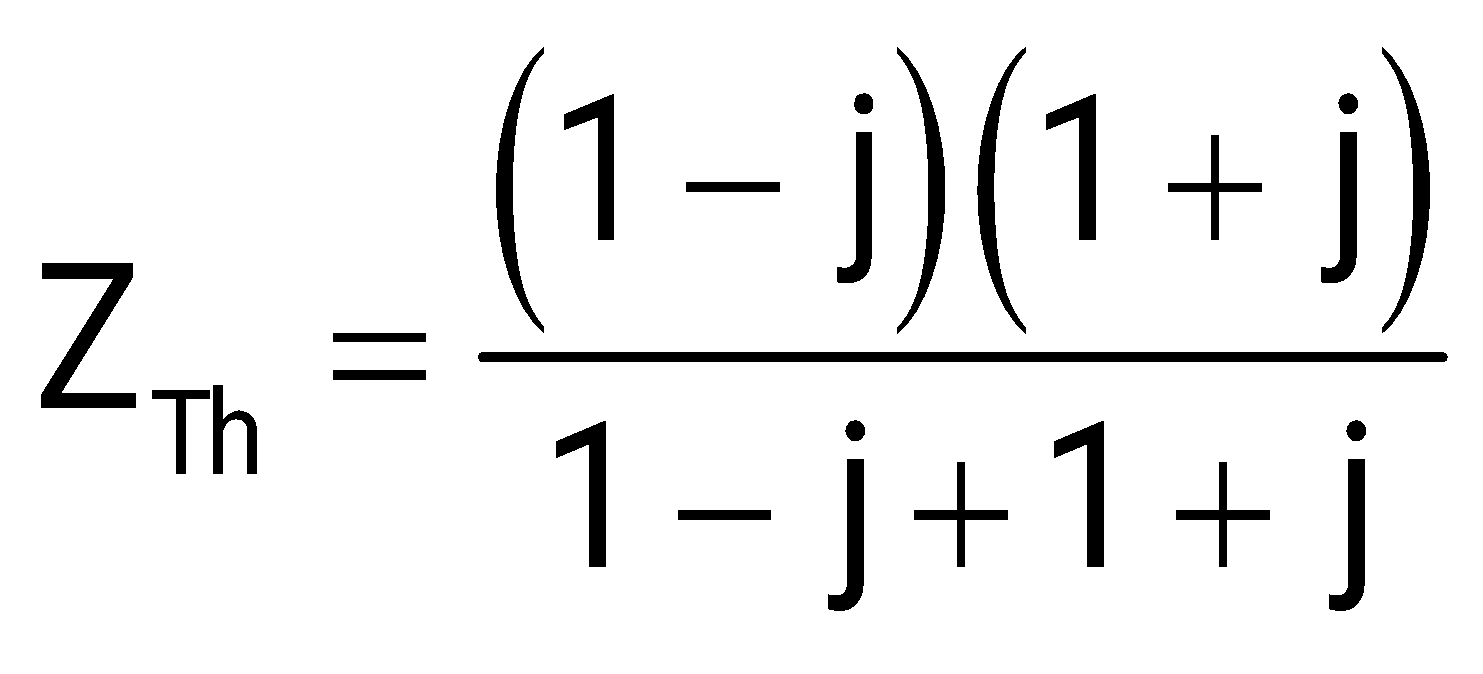

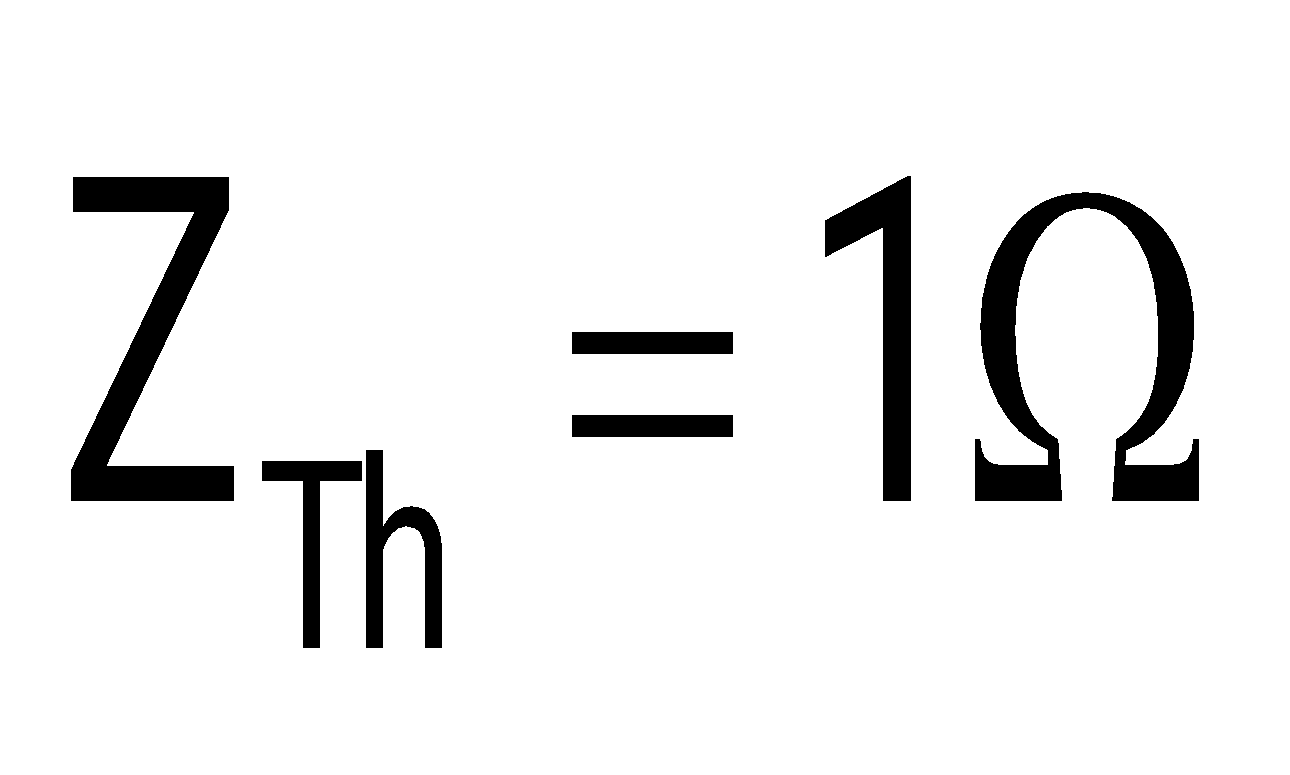

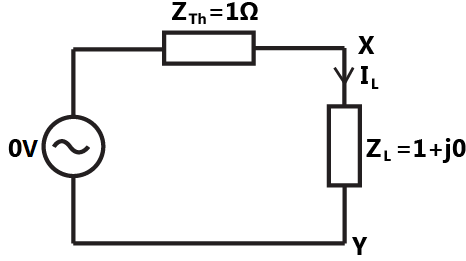

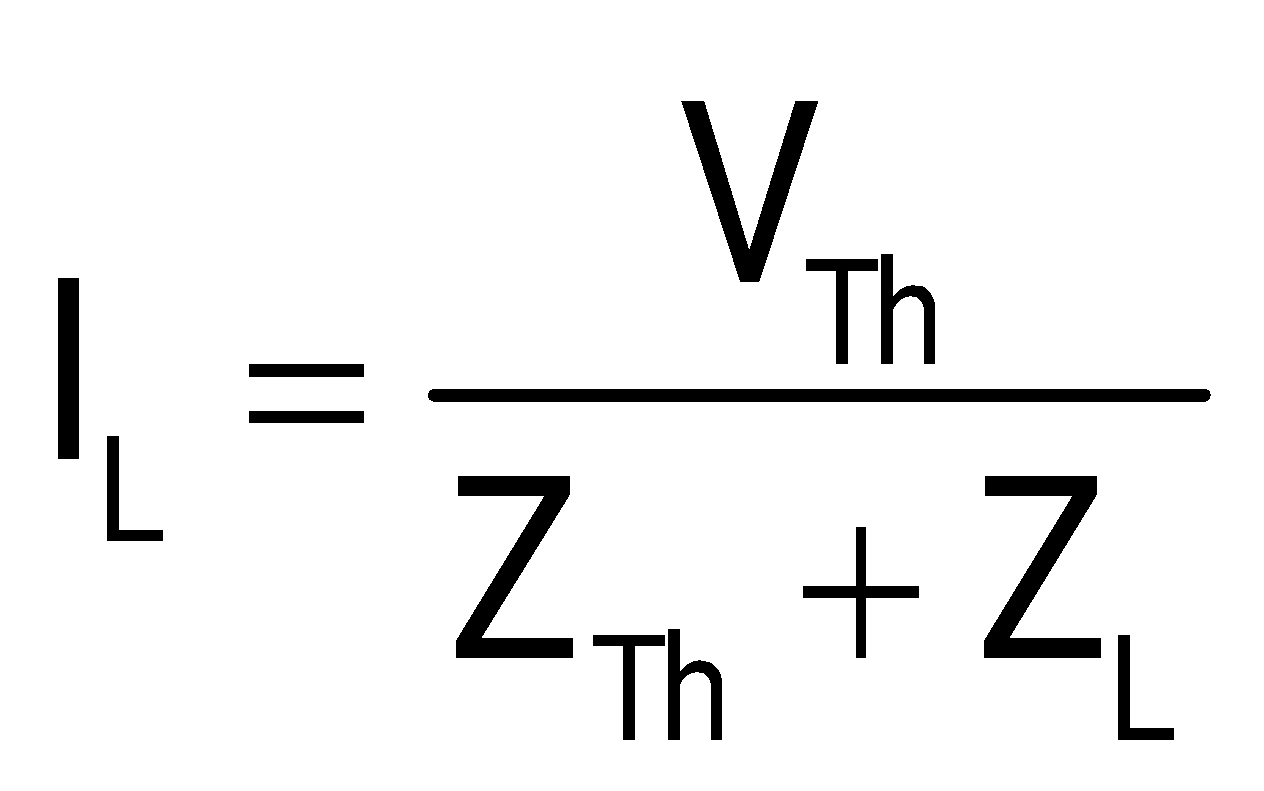

In the figure the current source is 1∠0 A, R=1Ω, the impedances are , and . The Thevenin equivalent looking into the circuit across X-Y is

For Open the XY terminals as shown,

Open circuit the current source

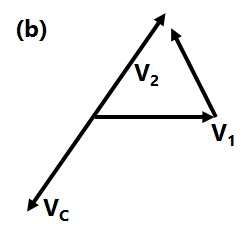

The circuit shown in the figure is energized by a sinusoidal voltage source at a frequency which causes resonance with a current of I.

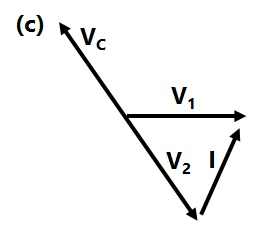

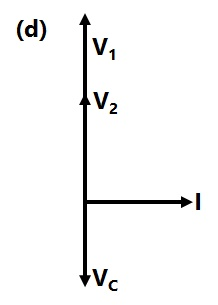

The phasor diagram which is applicable to this circuit is

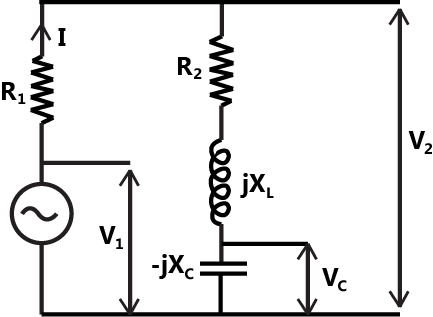

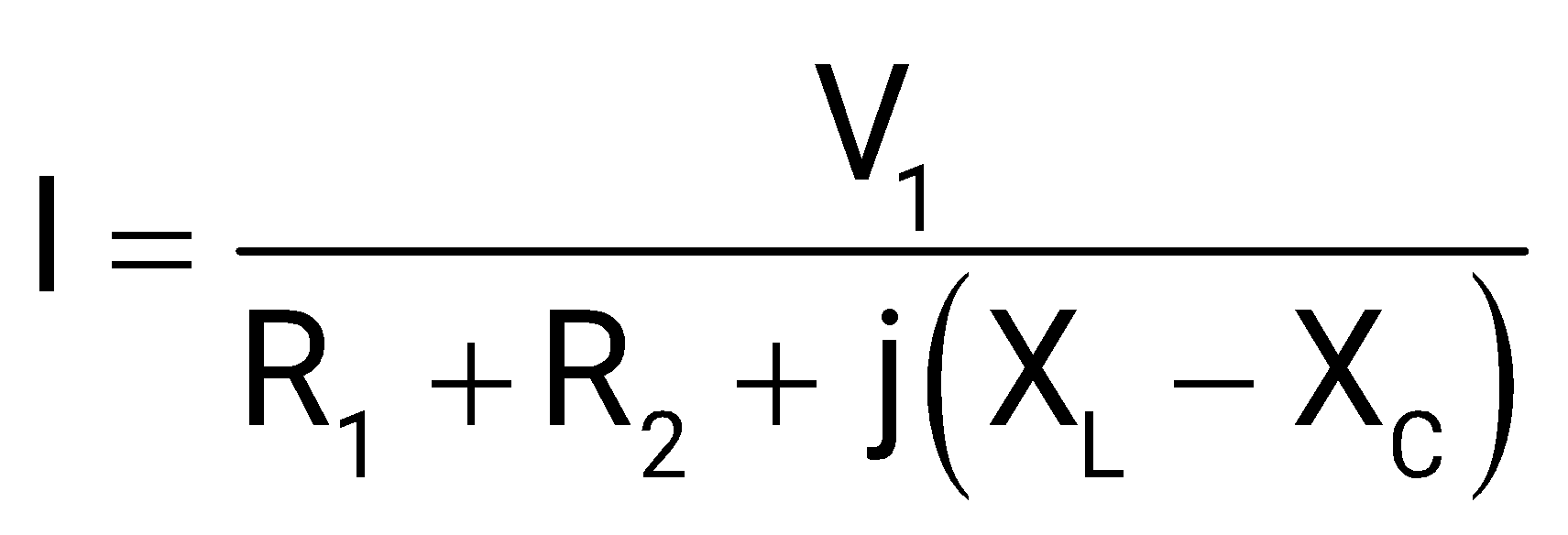

Various resistances and impedances have been marked in the circuit shown below,

At resonance,

I is in phase with

At resonance

is also in phase with and less than

Hence the phasor diagram is,

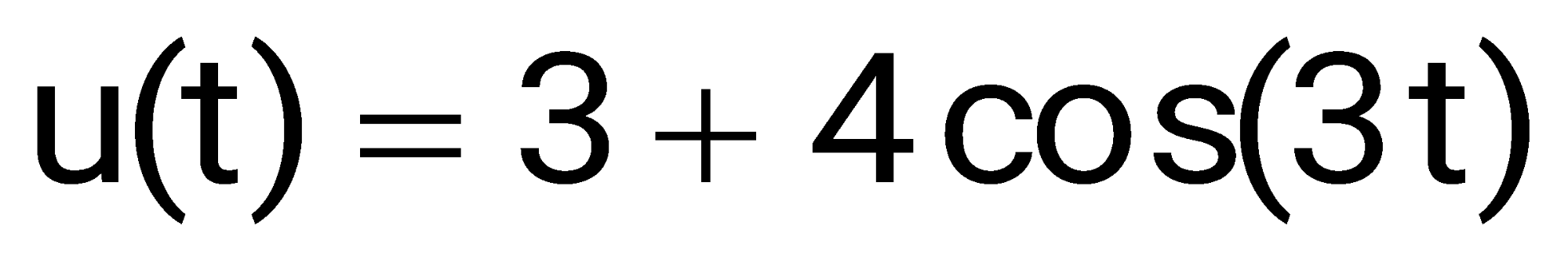

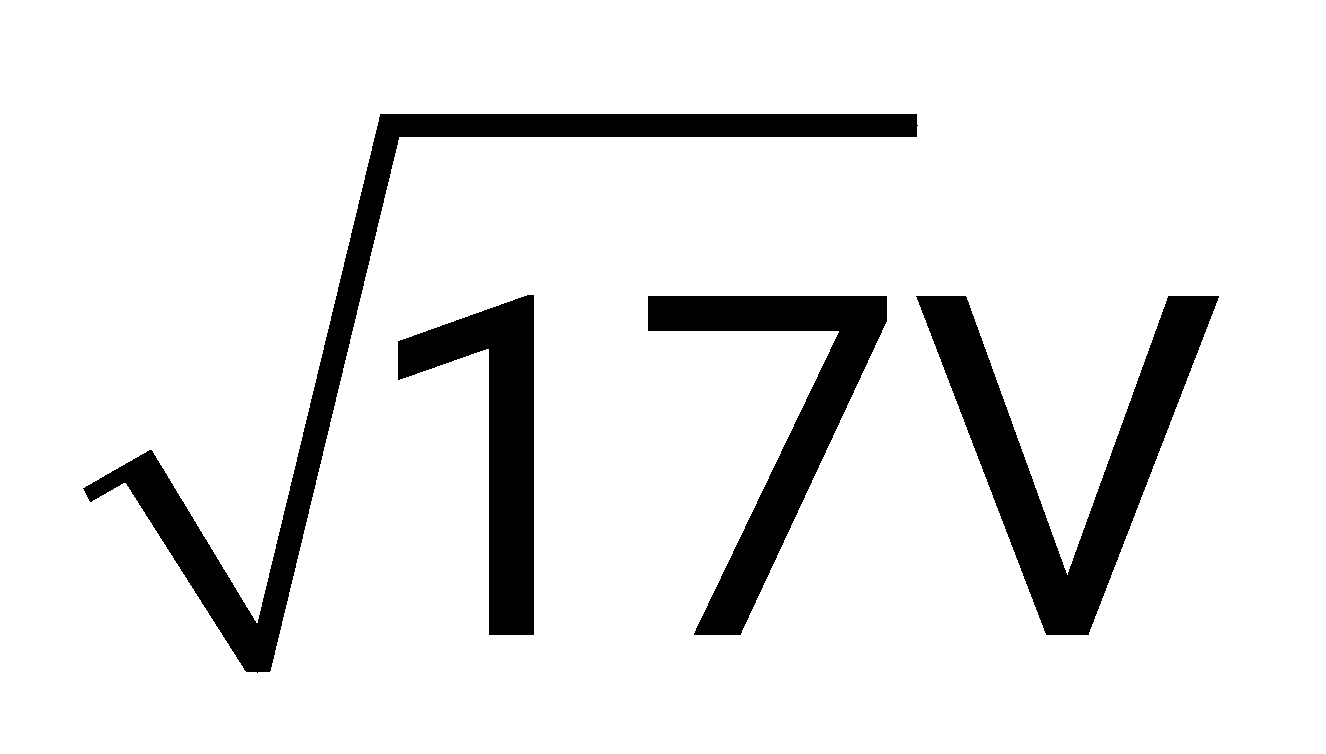

The RMS value of the voltage is:

RMS of 3 volts=3

RMS of

RMS of

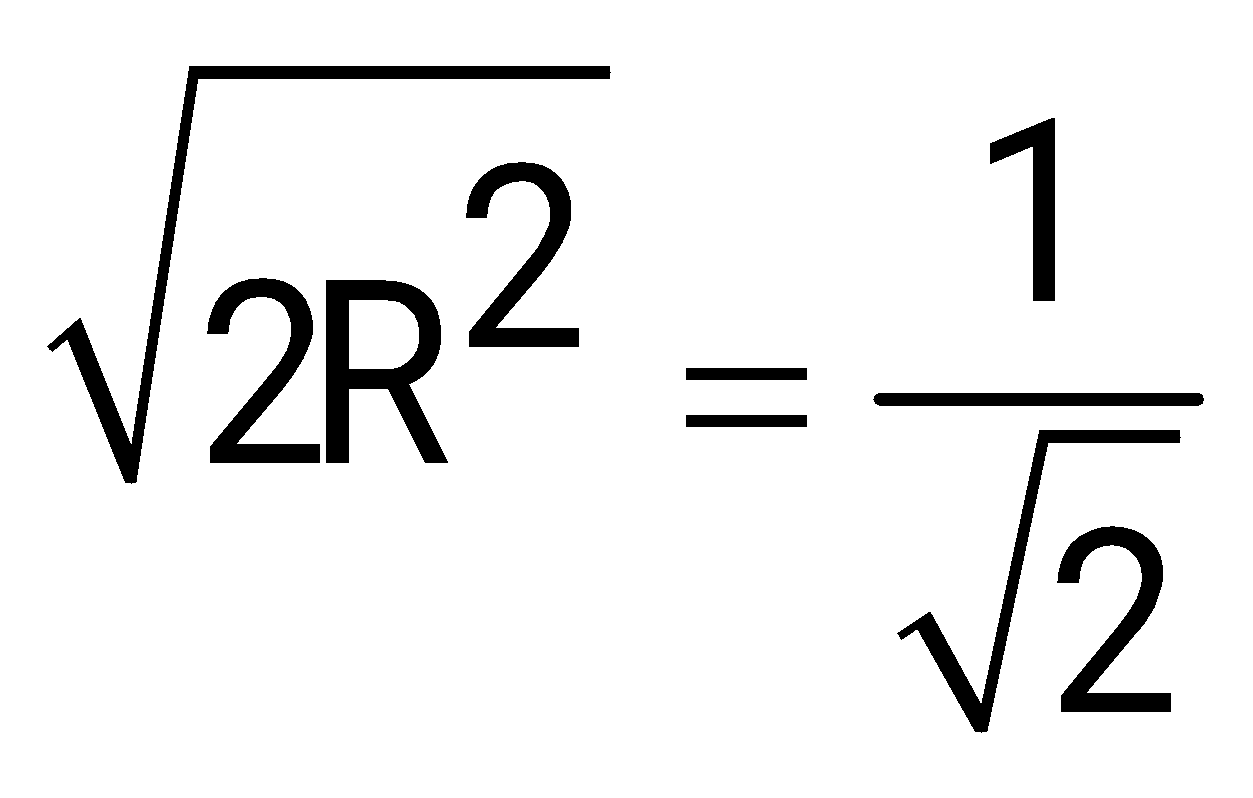

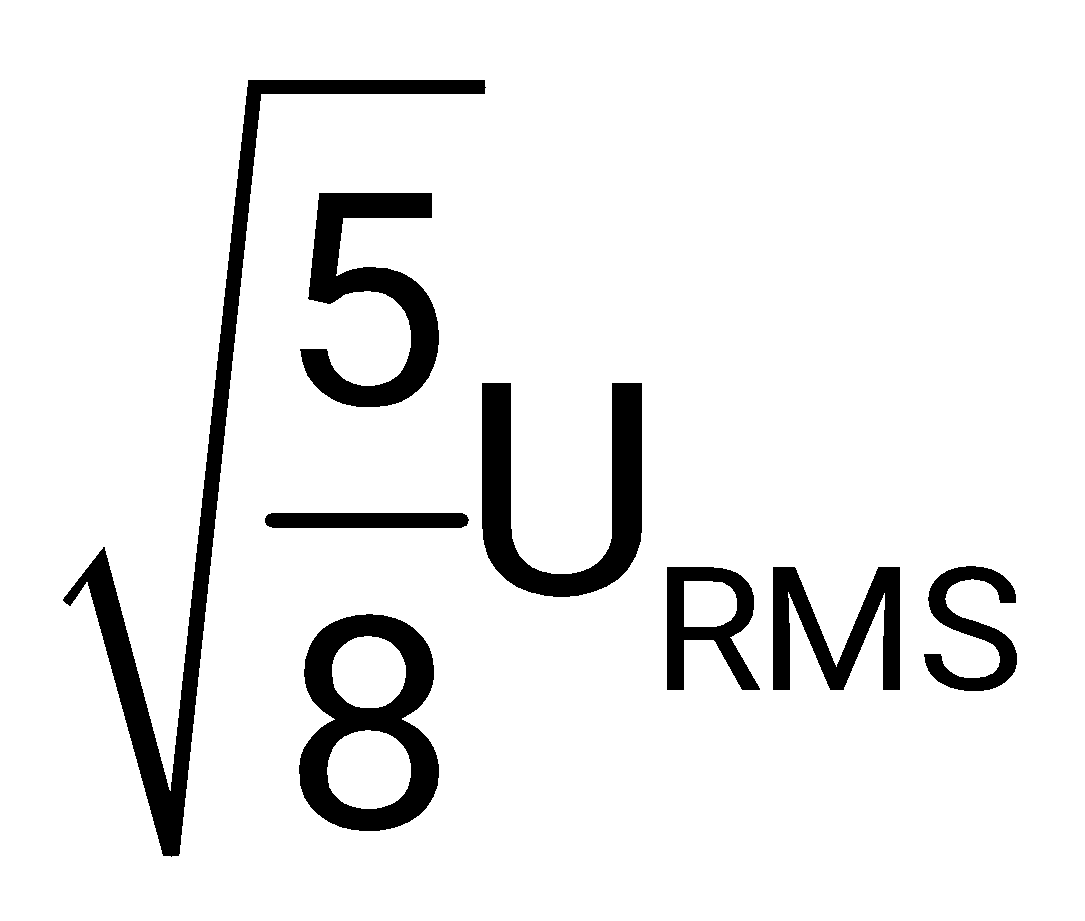

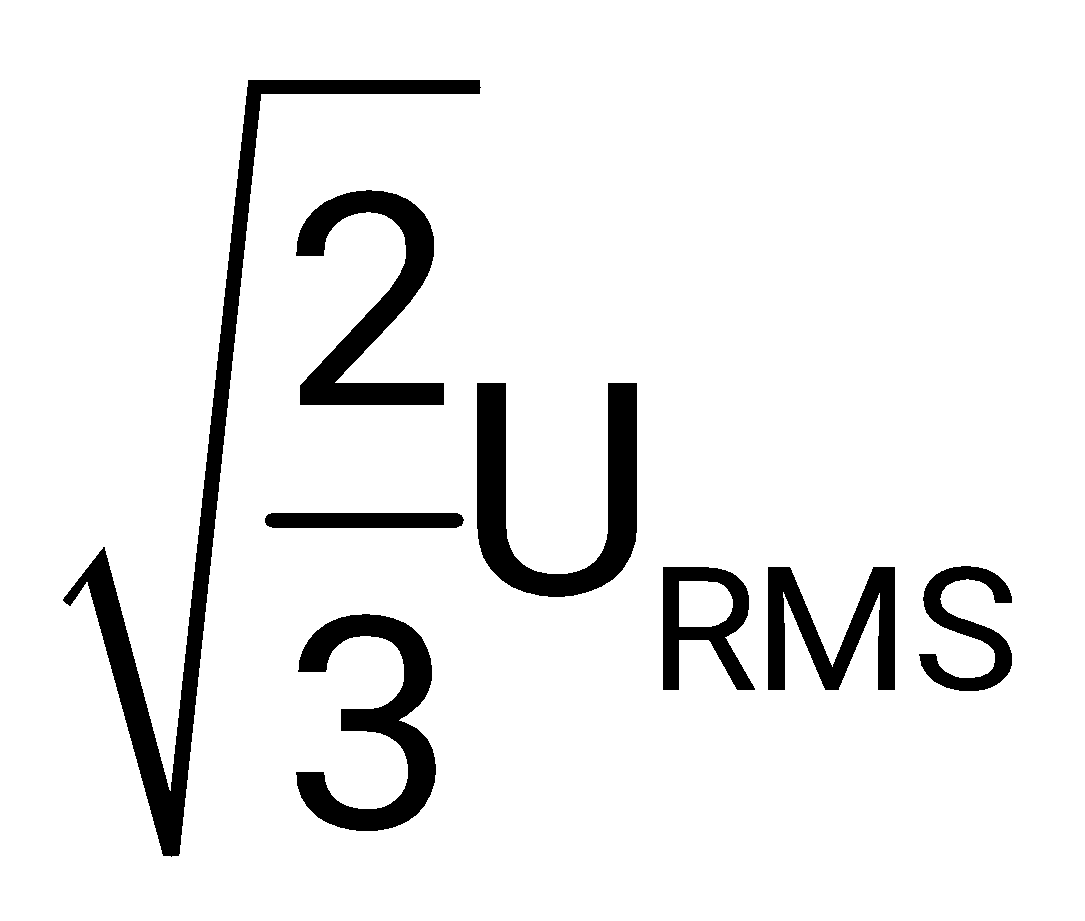

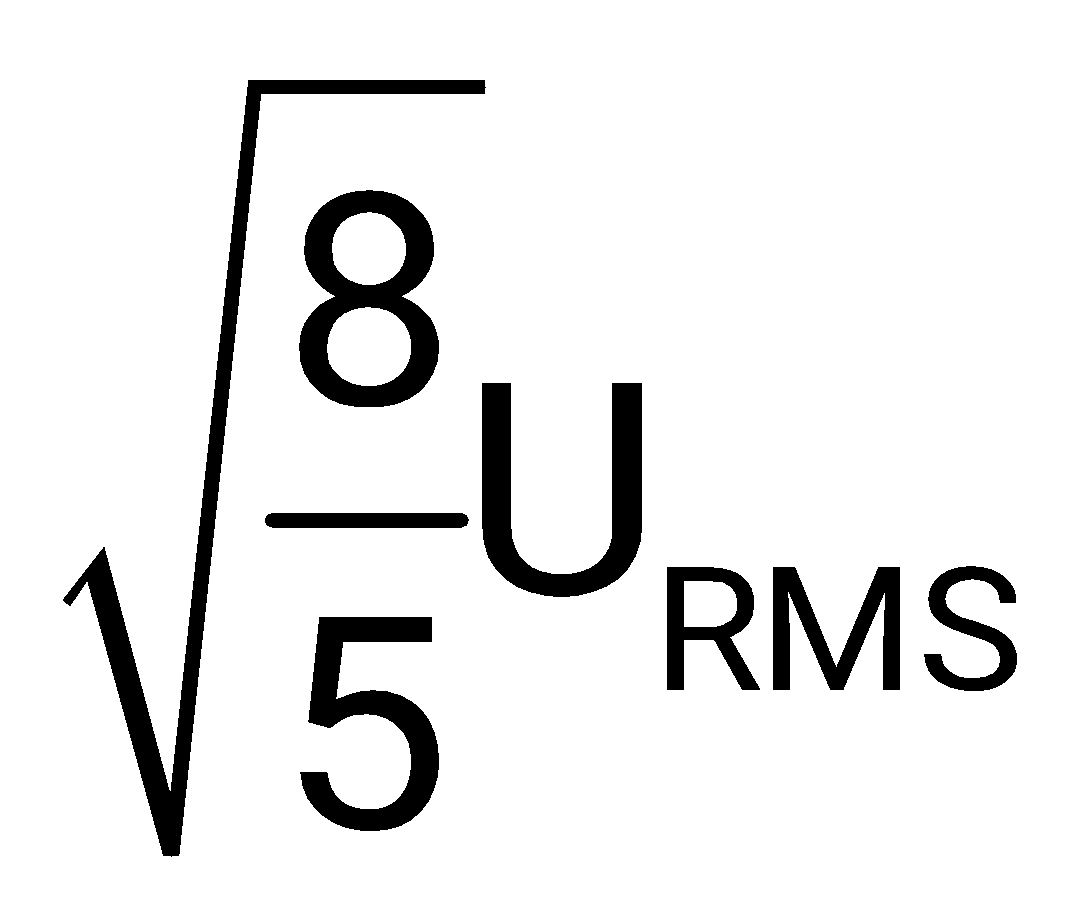

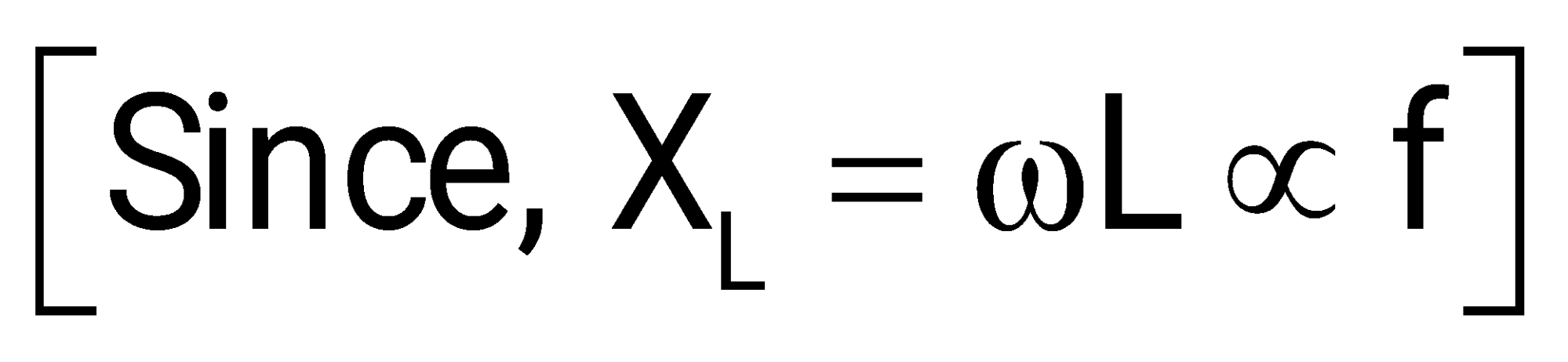

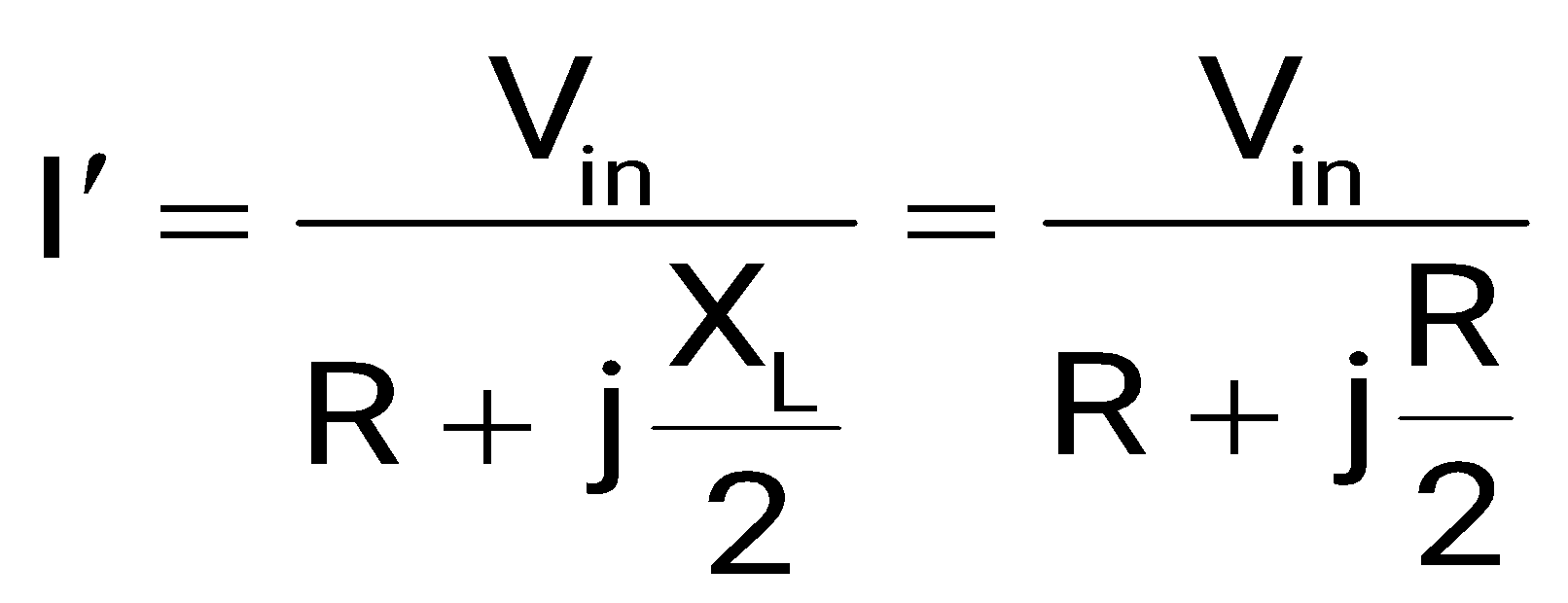

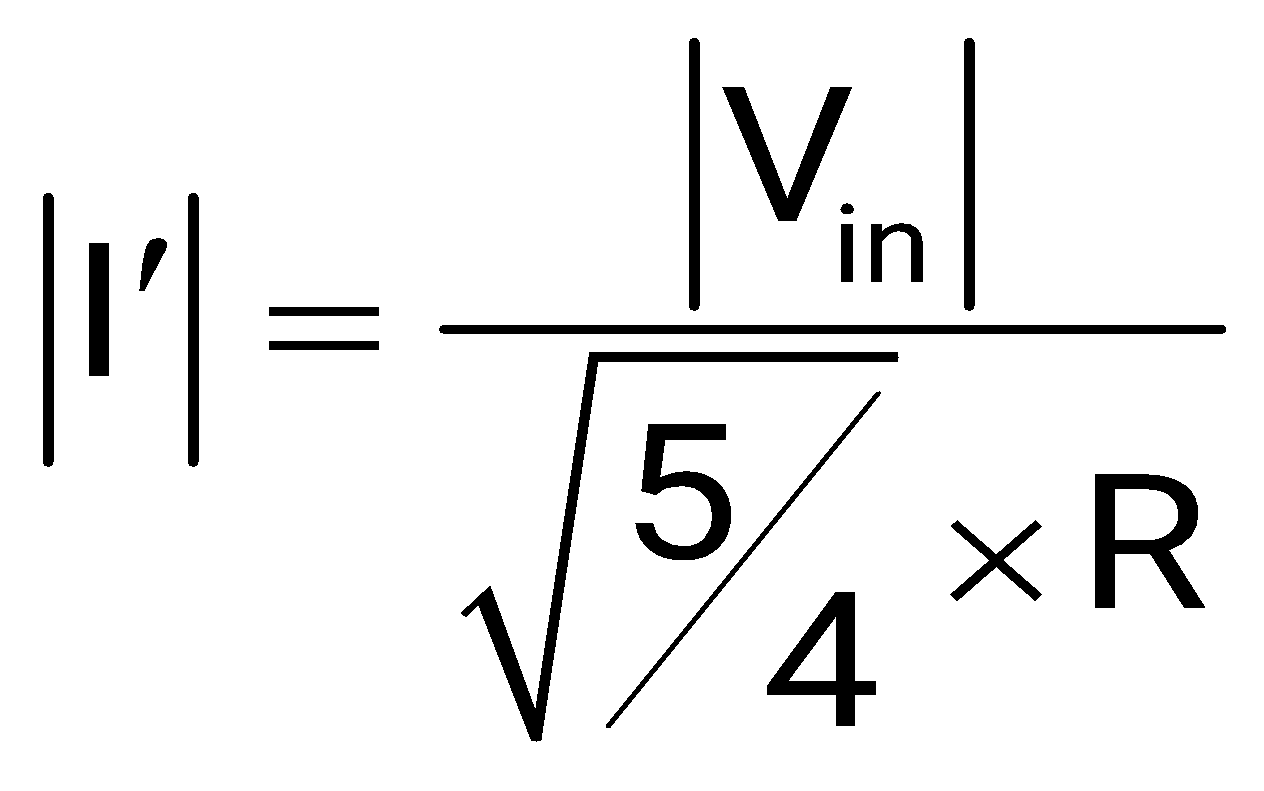

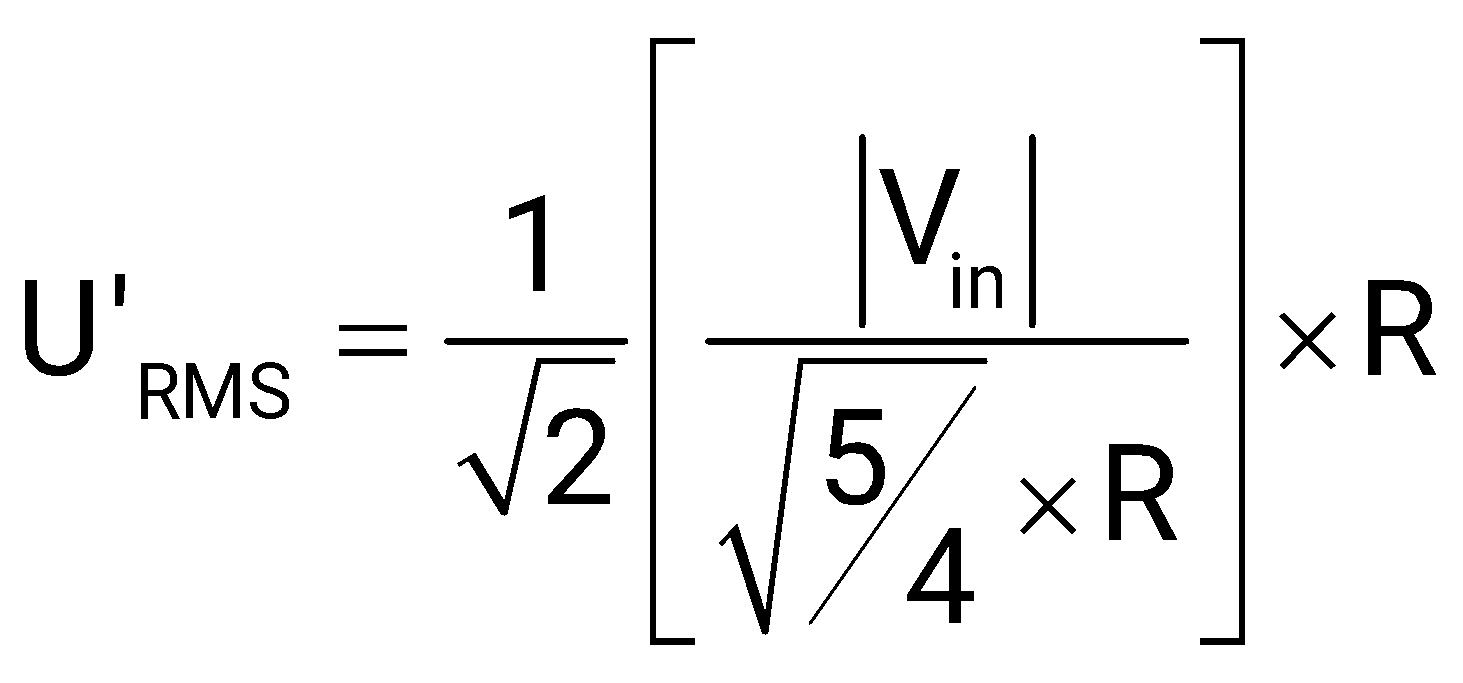

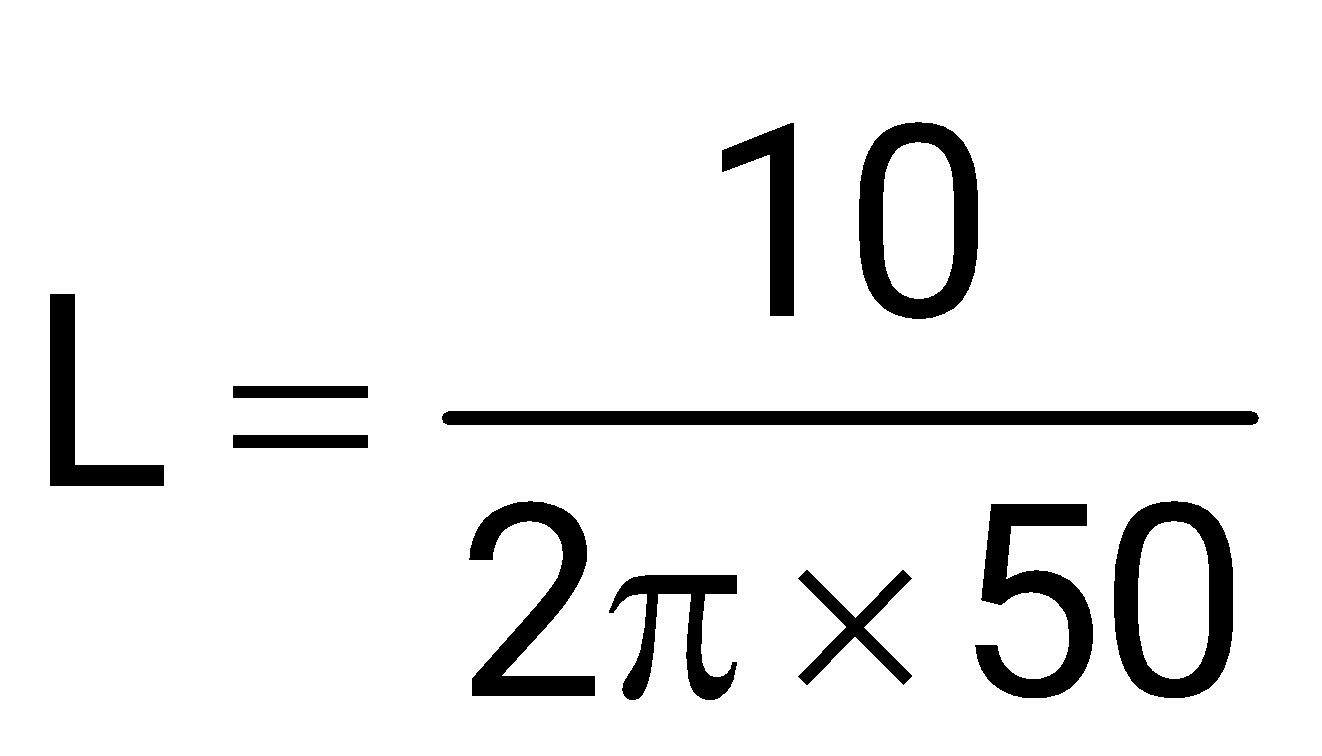

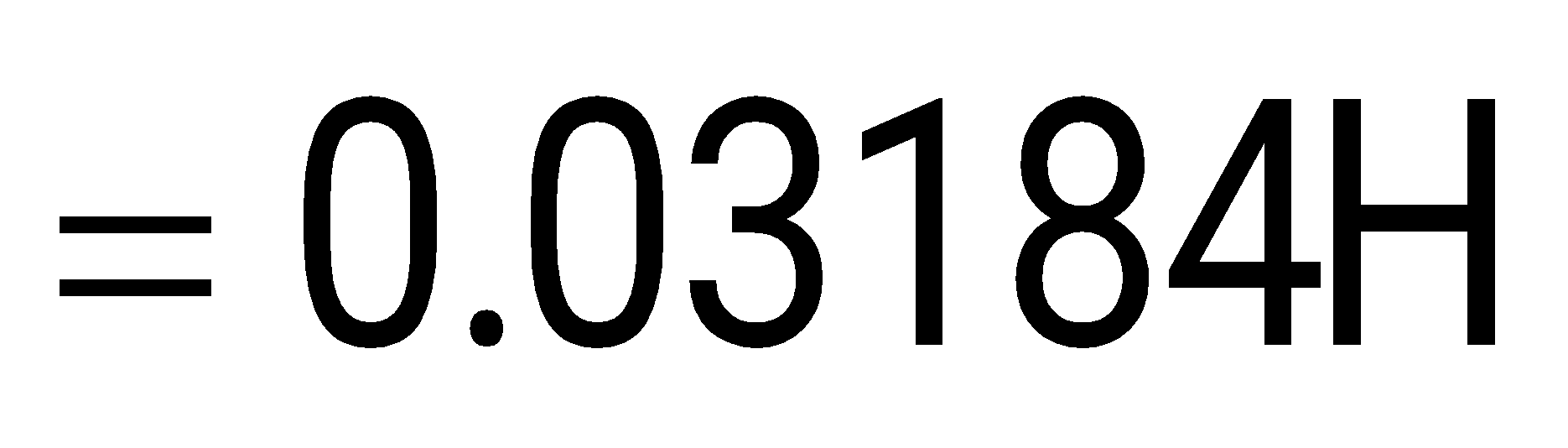

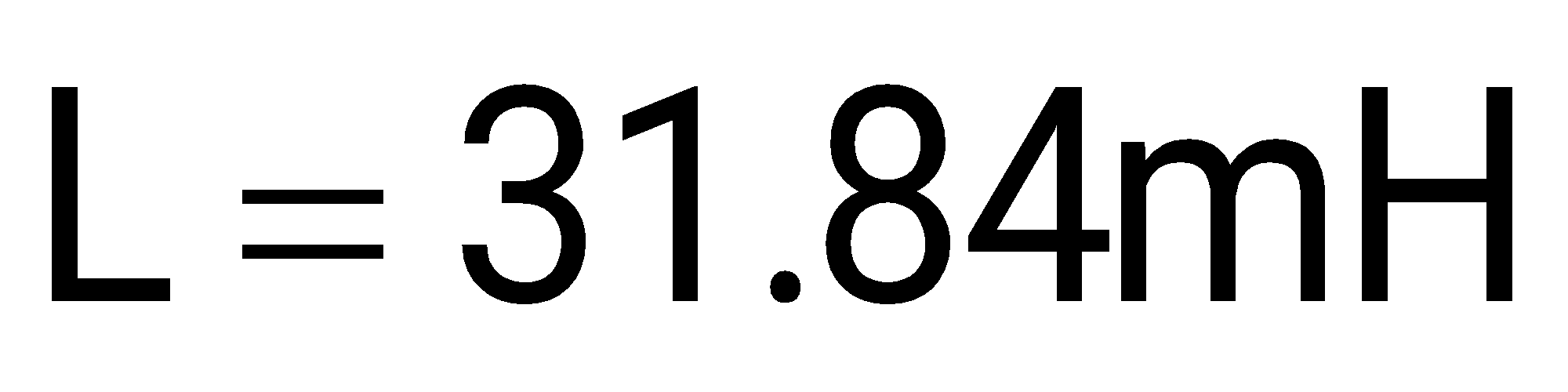

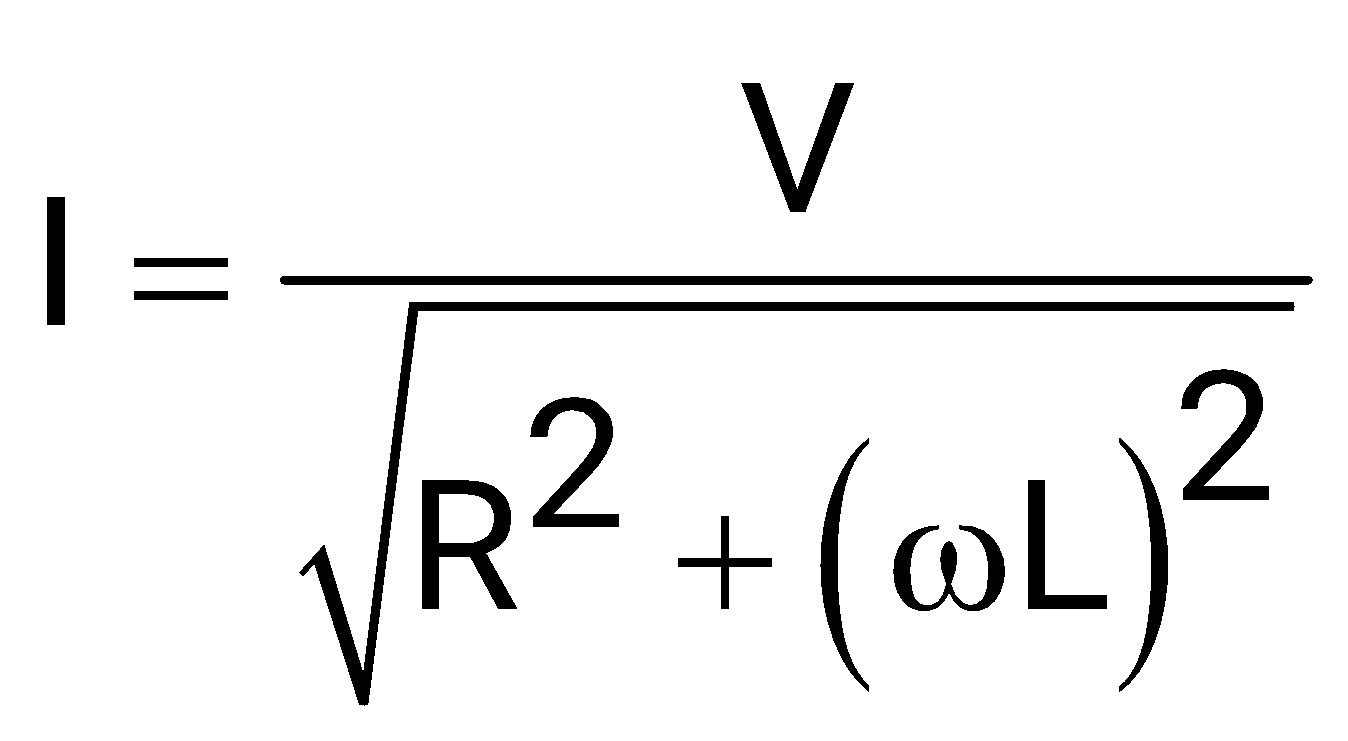

The RL circuit of Figure is fed from a constant magnitude, variable frequency sinusoidal voltage source . At 100 Hz, the R and L elements each have a voltage drop . If the frequency of the source is changed to 50 Hz, the new voltage drop across R is:

Let inductive reactance at 100Hz is

Since voltage drop across R & L is equal at 100Hz

Magnitude

RMS voltage across

Now at 50Hz

Inductive reactance=

Current at 50Hz

RMS voltage drop across R at 50Hz=

Now from equation (4) & (2)

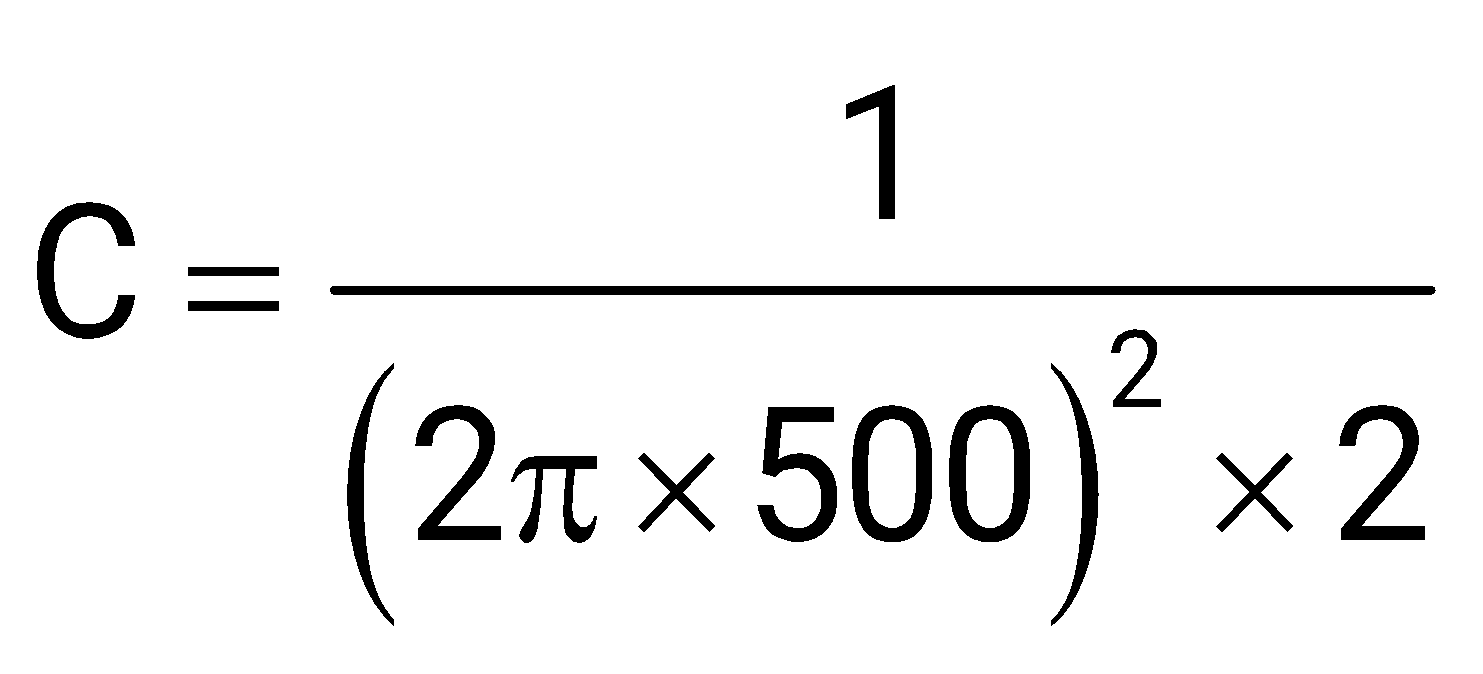

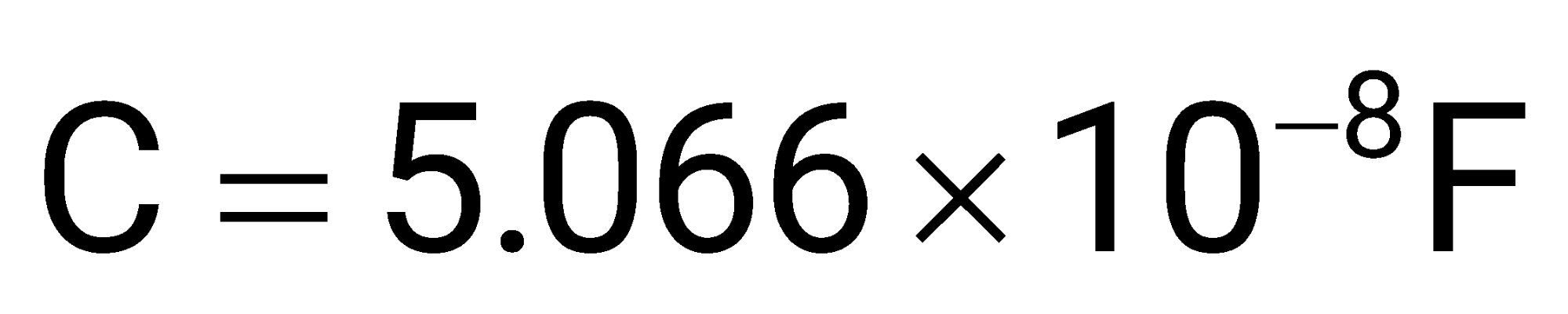

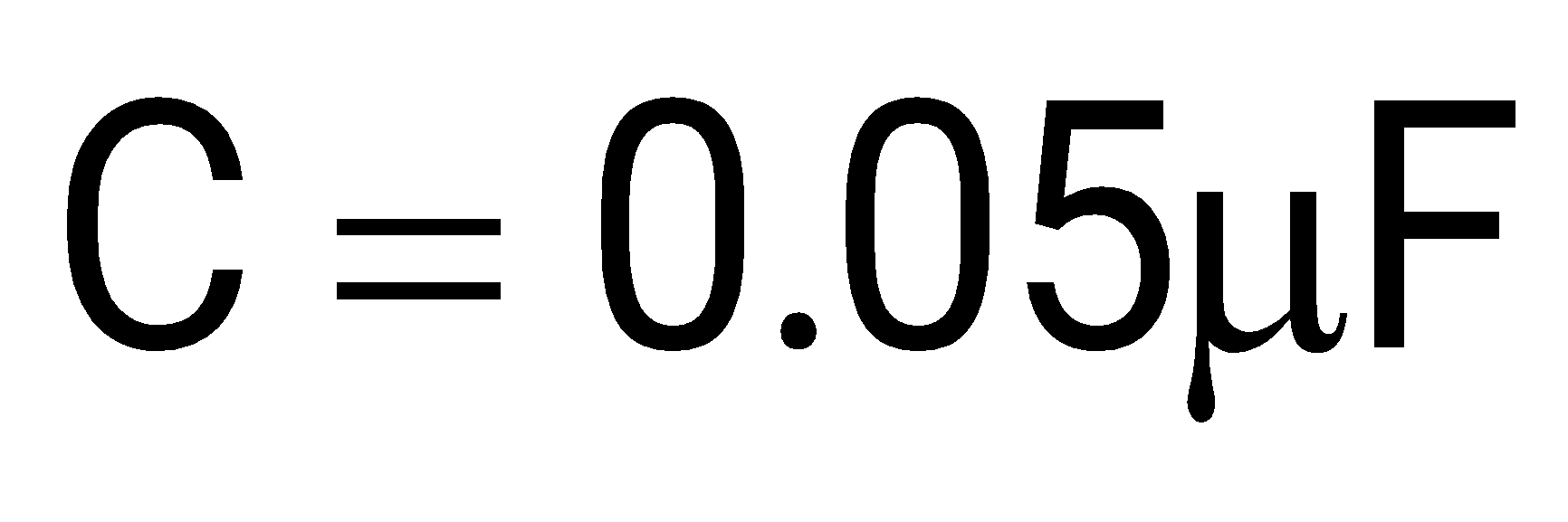

In the figure the value of Z in Figure, which is most appropriate to cause parallel resonance at 500 Hz, is

For parallel resonance to be happen, imaginary part of admittance of parallel network should be zero.

Since inductor is already exists. So, Z should be capacitive

Admittance of parallel network, Y=

=

For imaginary part of admittance of zero

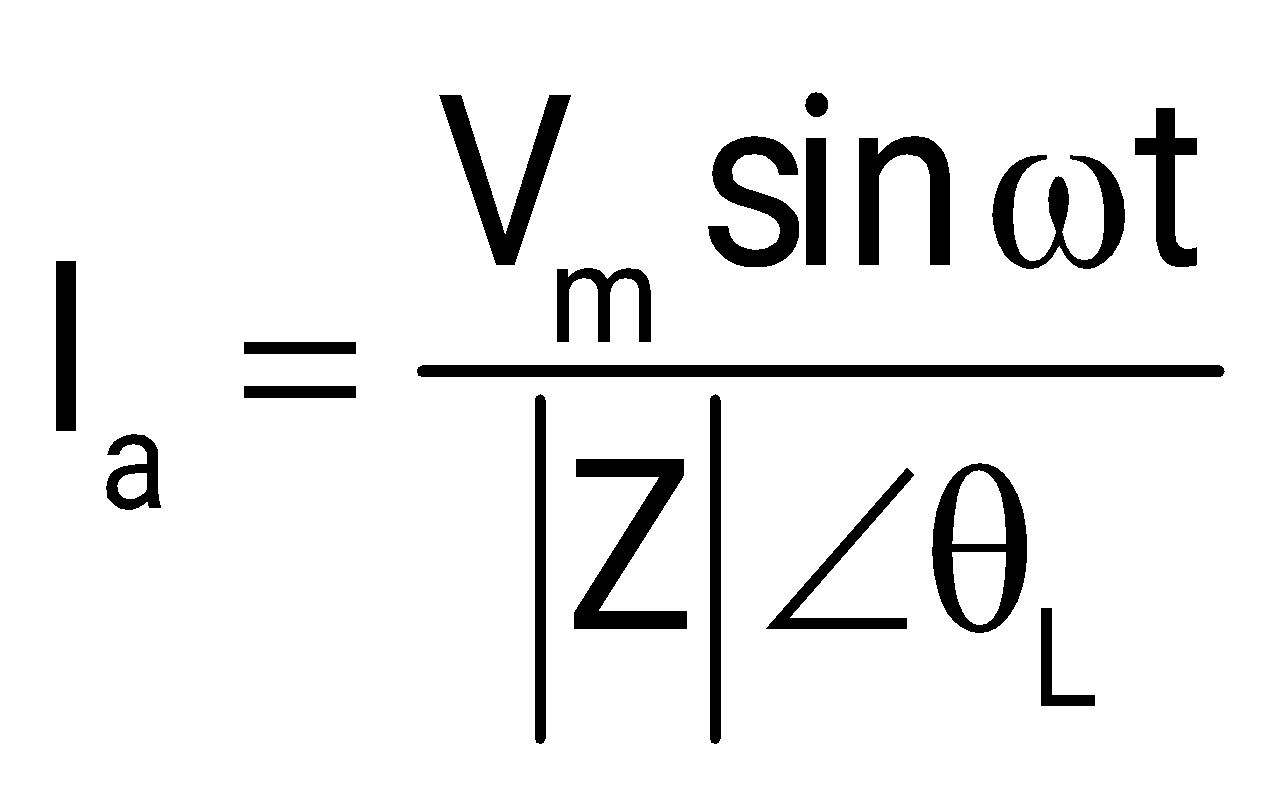

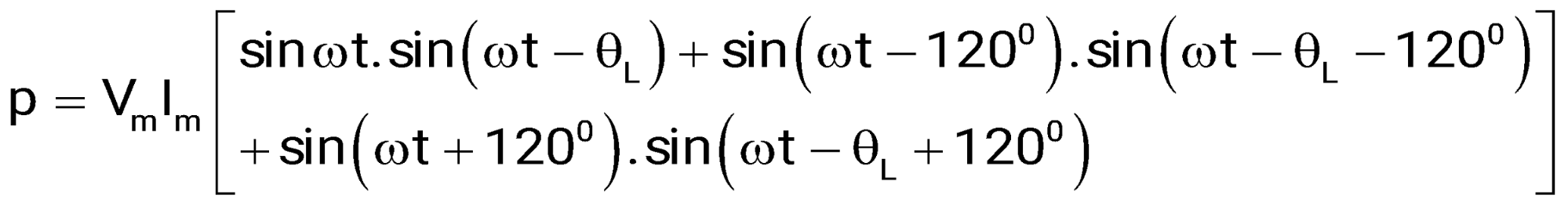

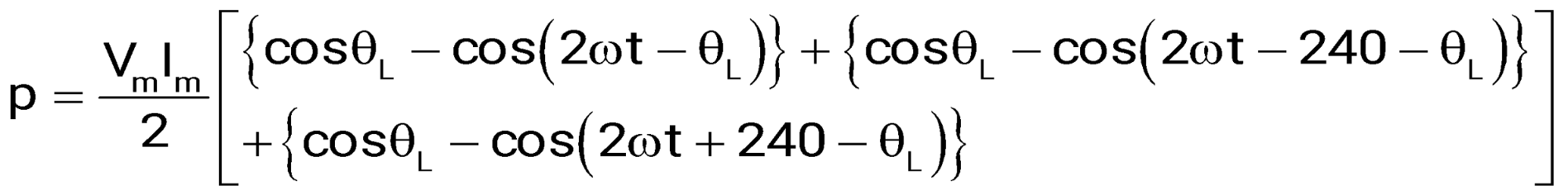

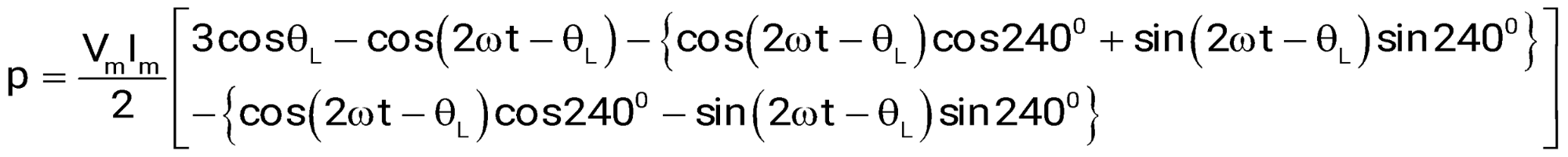

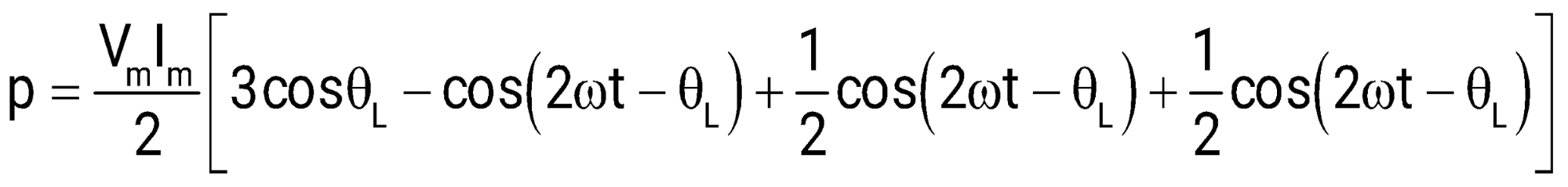

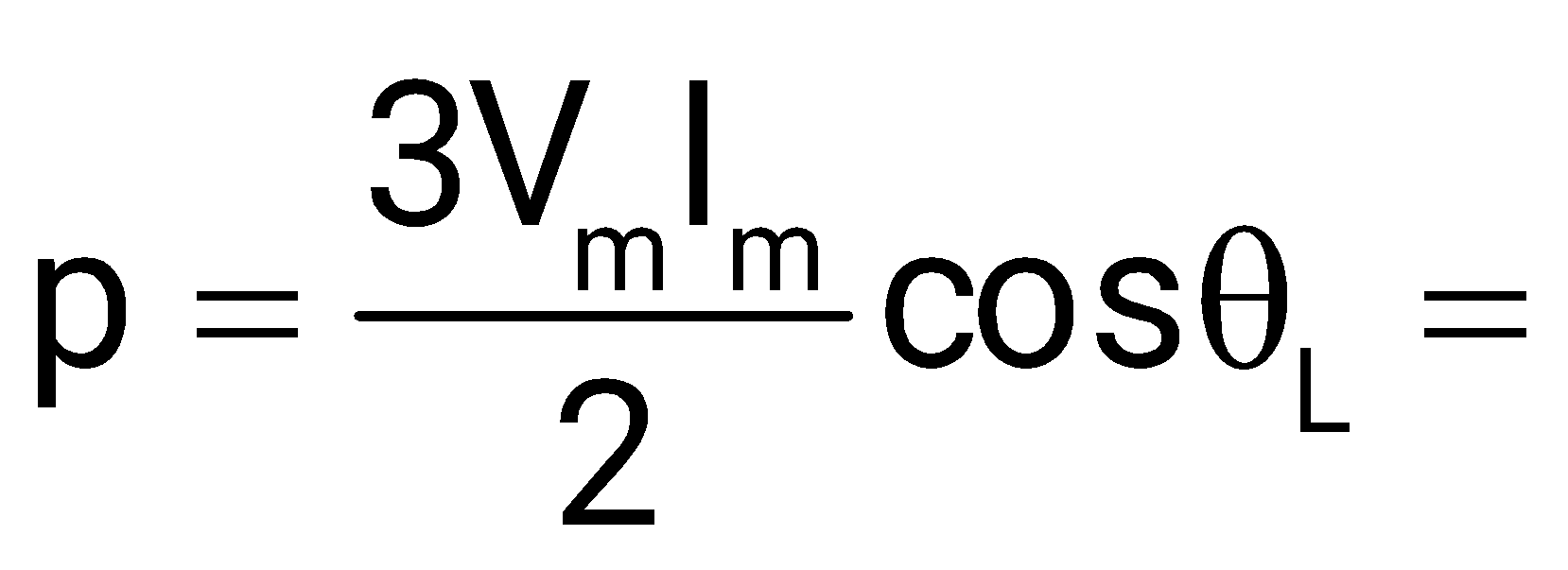

Total instantaneous power supplied by a 3-phase ac supply to a balanced R-L load is

Load impedance

Where &

Balanced voltage supply

Current in the balanced load,

Similarly,

Instantaneous power in load ‘p’

Constant

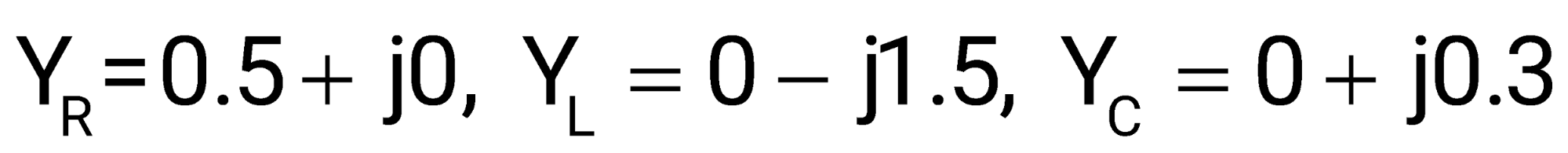

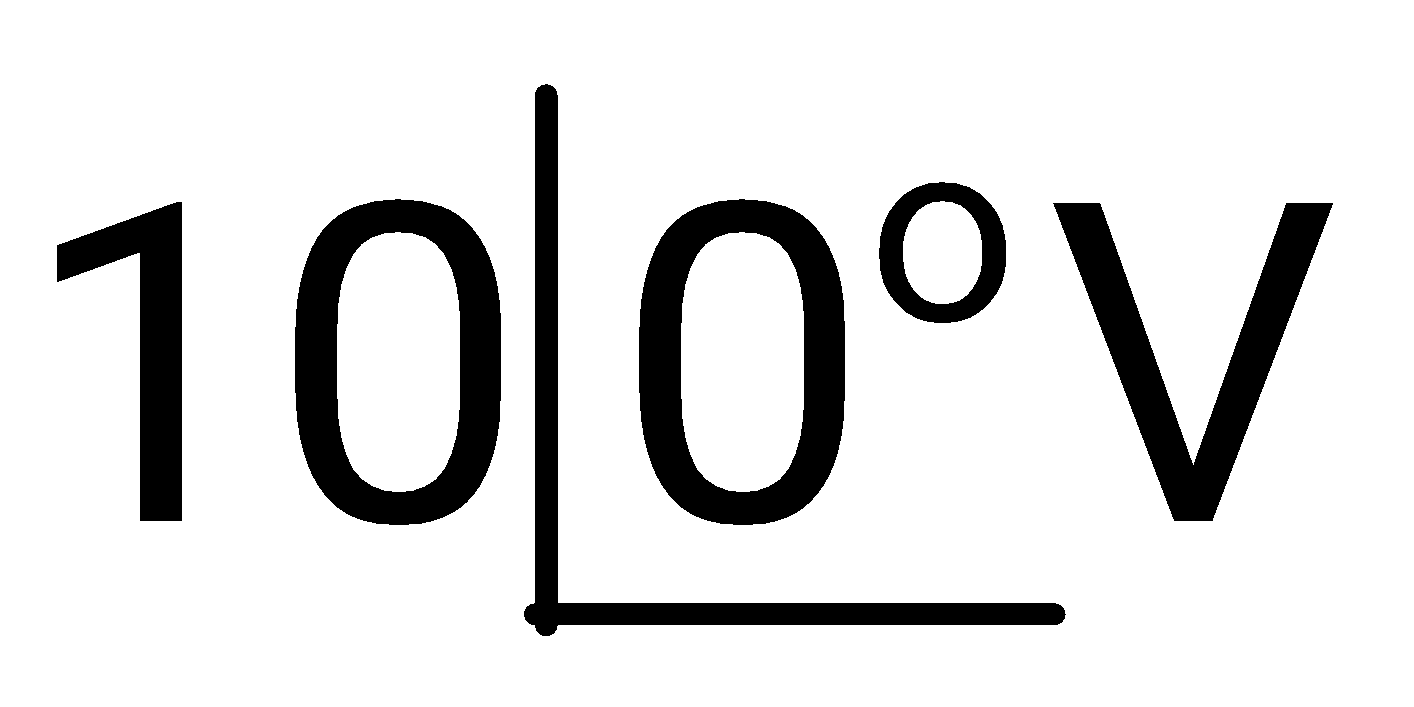

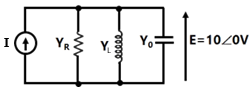

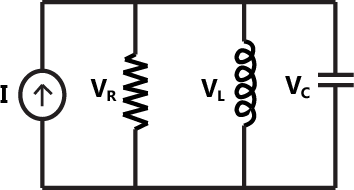

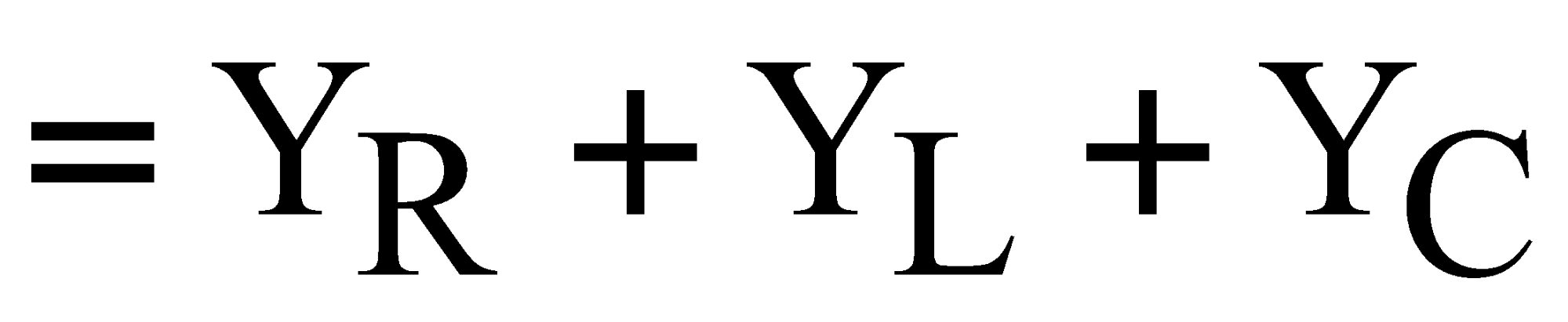

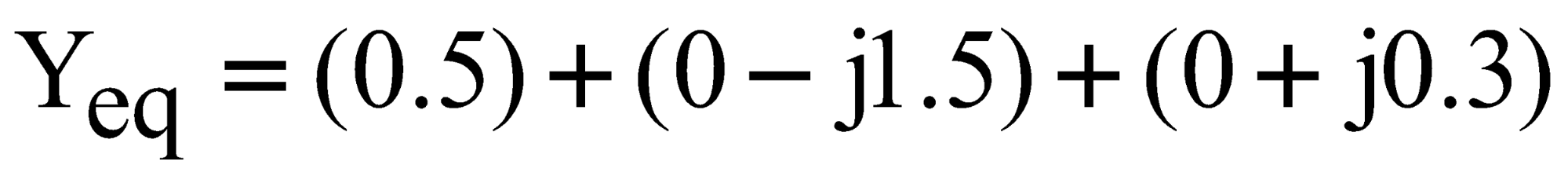

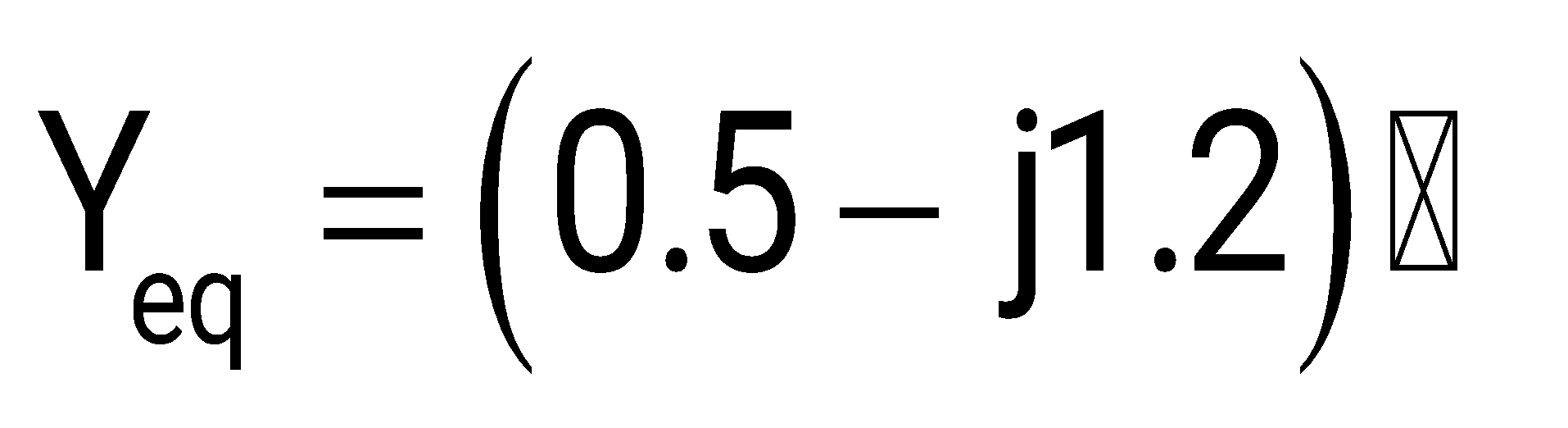

In figure, the admittance values of the elements in Siemens are

respectively.

The value of I as a phasor when the voltage E across the elements isis

Total admittance of parallel combination

A segment of a circuit is shown in Figure. , . The voltage is given by

Current in resistor

Current in capacitor

Using KCL at node ‘0’

Voltage across inductor=

In the Figure.

.

The thevenin impedance seen from X-Y is

For thevenin impedance short circuiting the voltage source

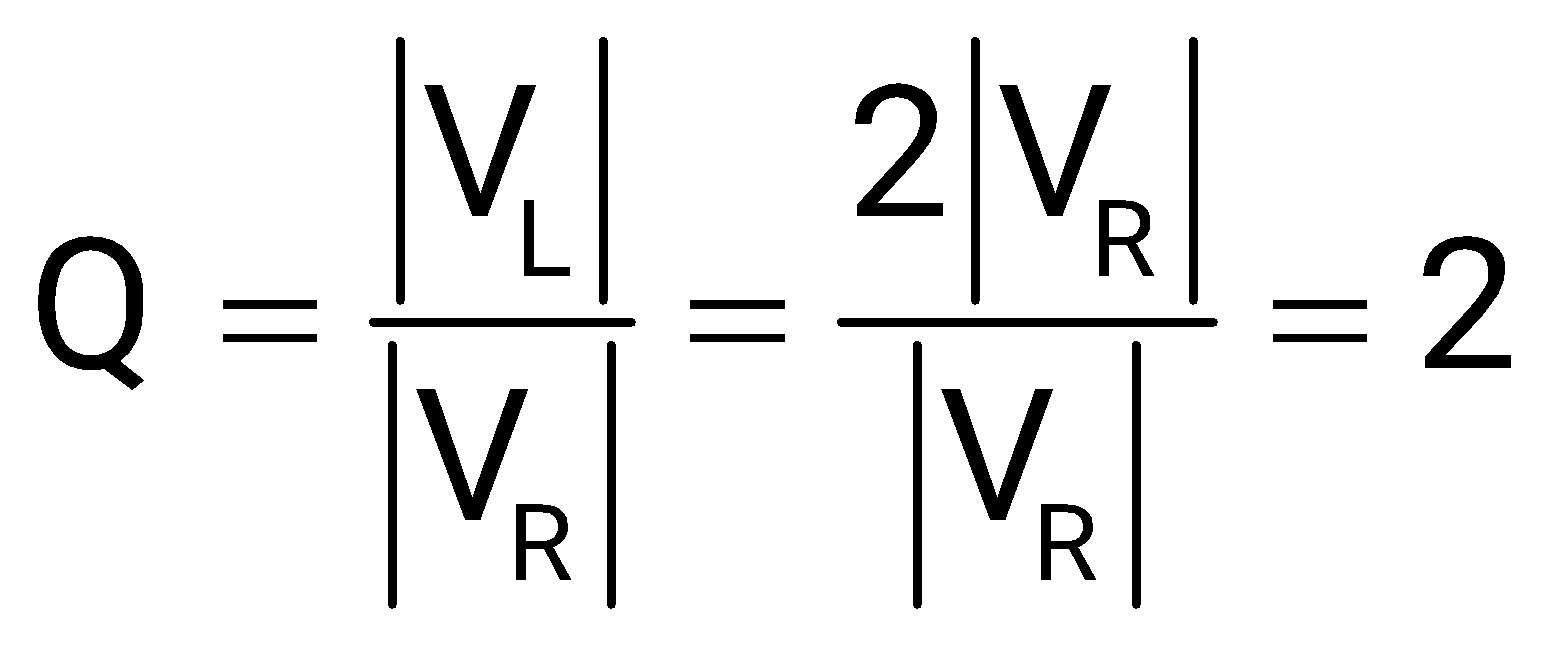

In the circuit of Figure, the magnitudes of and are twice that of . The inductance of the coil is

Given,

By using KVL in circuit

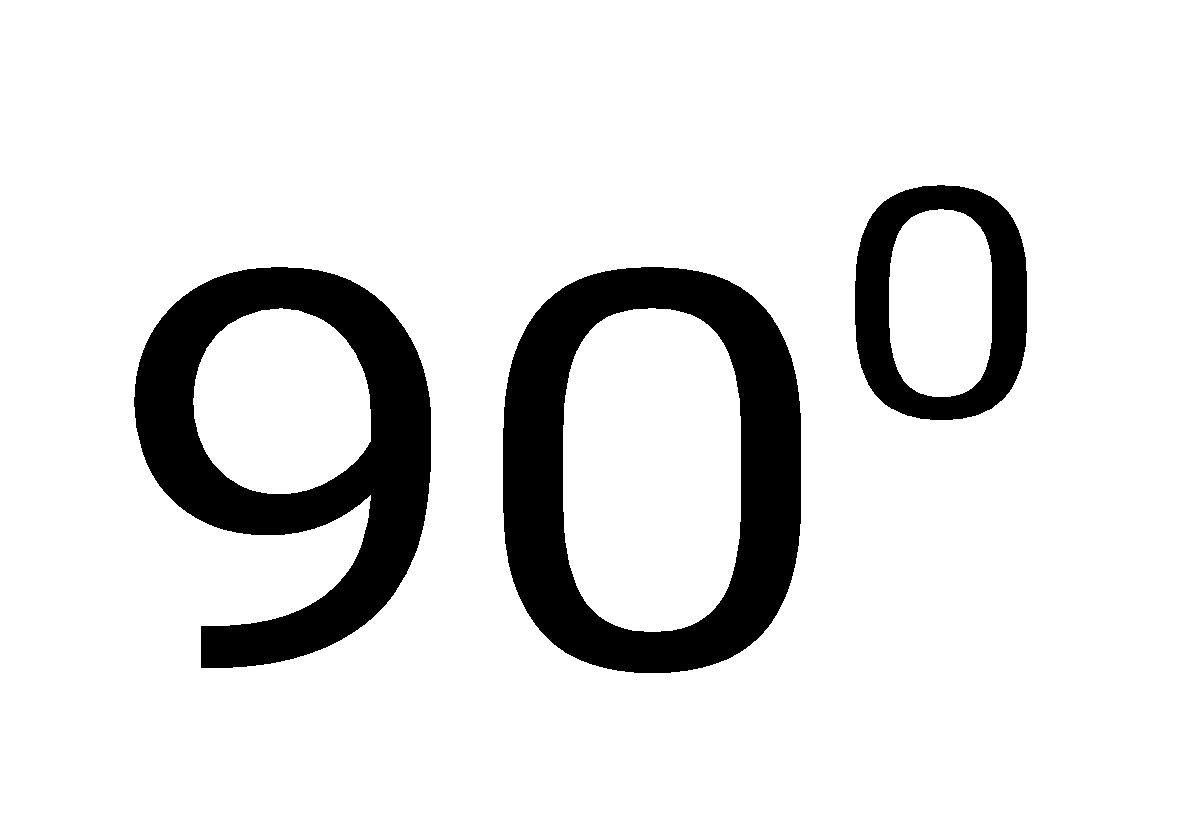

In a series RLC circuit, the inductor and capacitor voltage are out

of phase.

Hence,

So the circuit is at resonance

Hence

Quality factor of circuit

Since

In the circuit shown in Figure, what value of C will cause a unity power factor at the ac source?

Admittance of capacitor

Admittance of combination

Total admittance of parallel combination

For unity power factor at source end

Imaginary part of admittance should be zero.

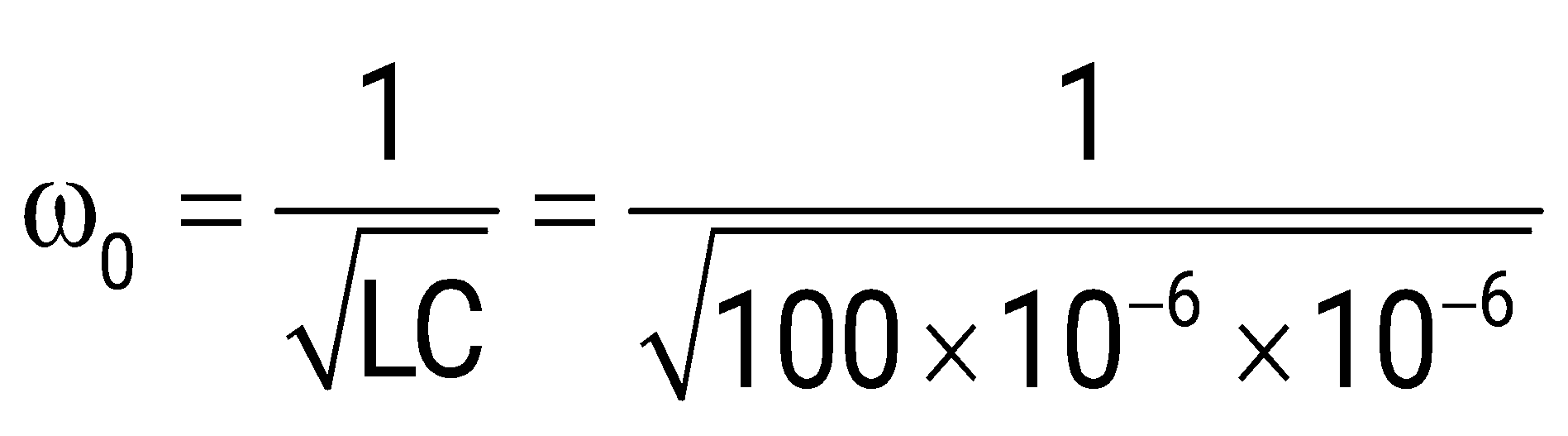

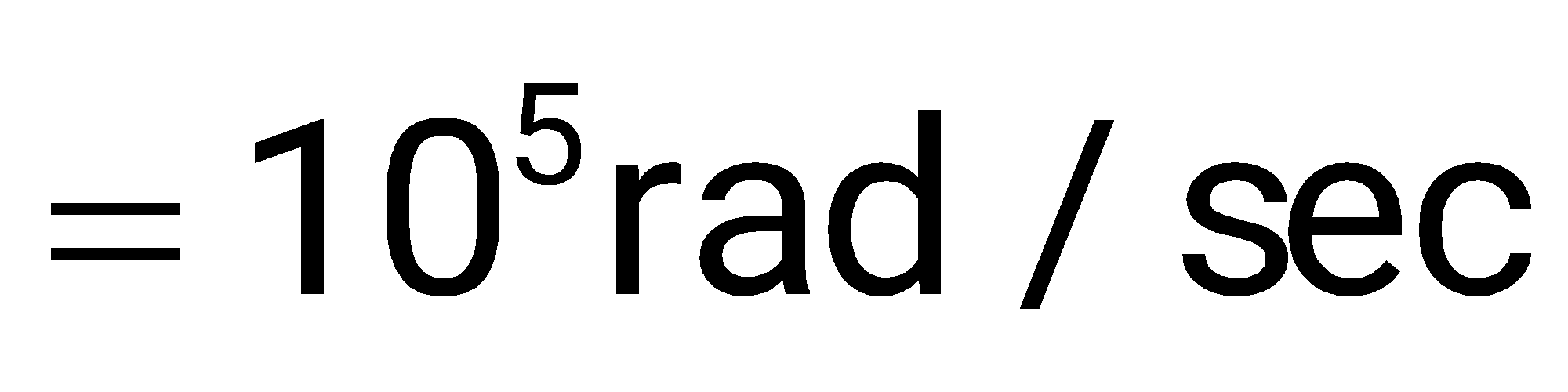

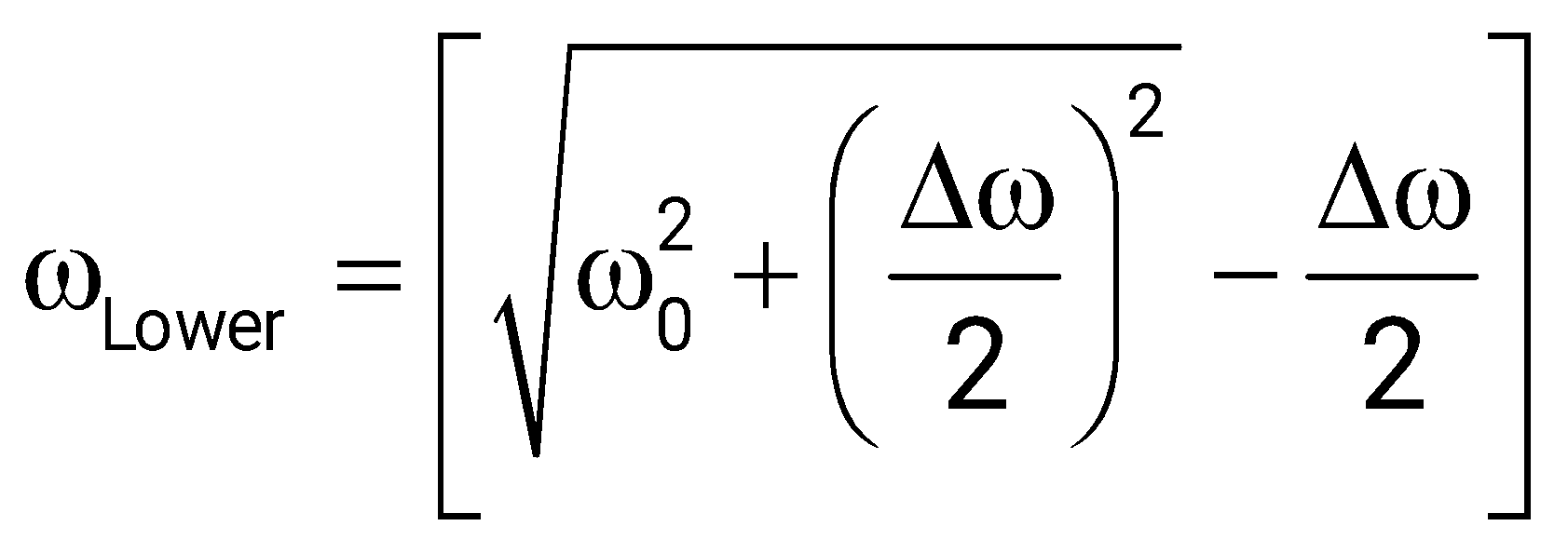

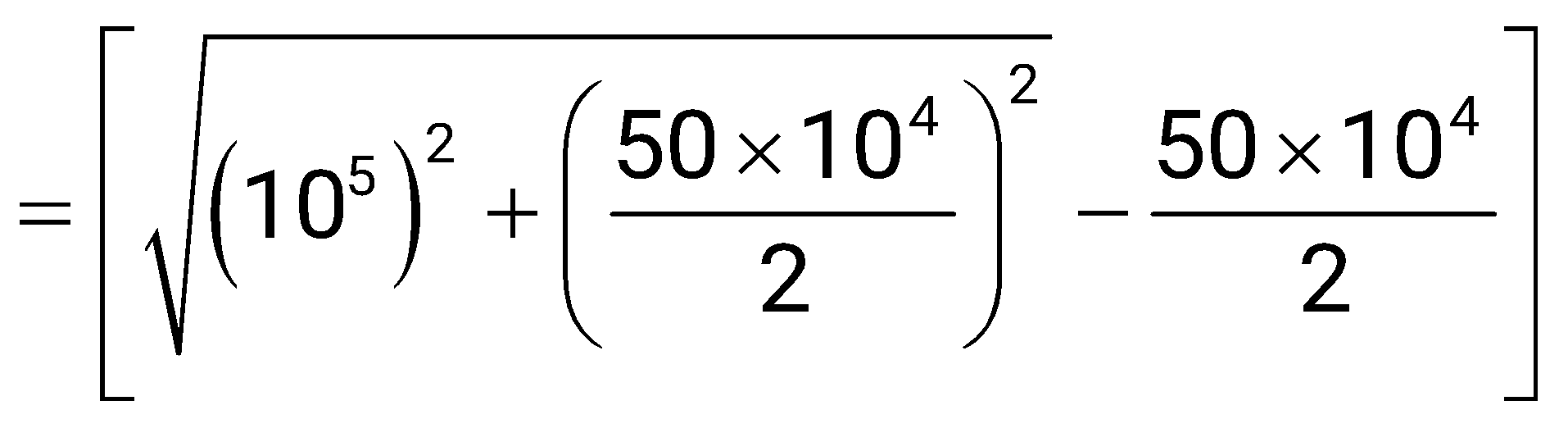

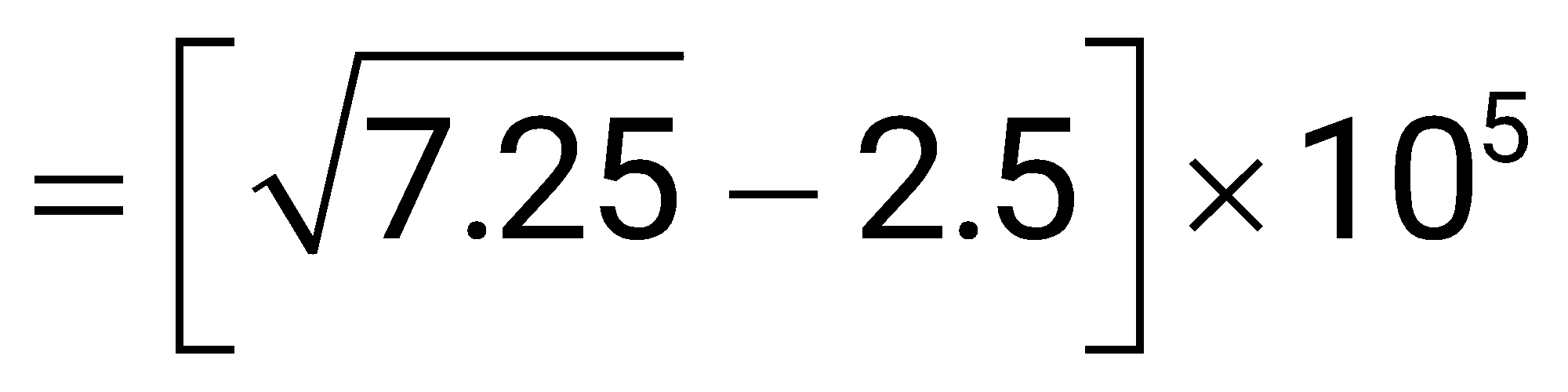

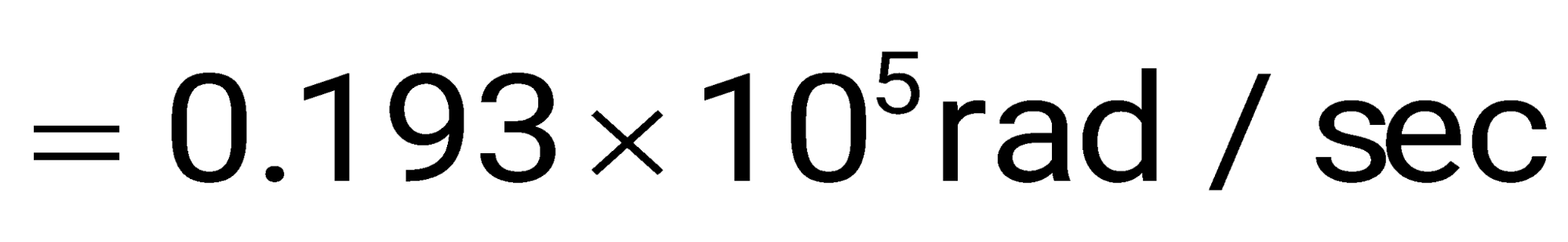

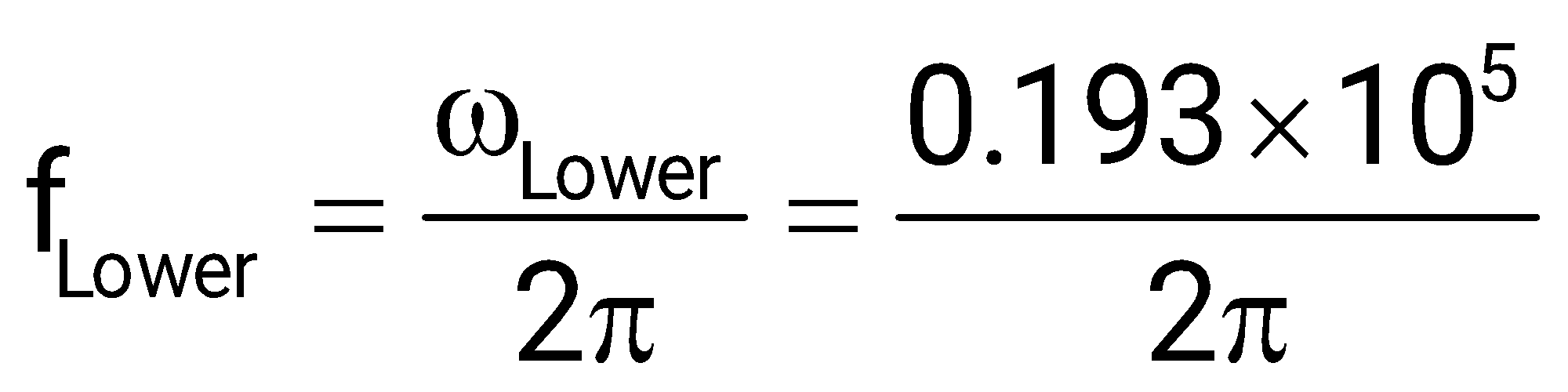

A series R-L-C circuit has R = 50Ω, L = 100 μH and C = 1 μF. the lower half power frequency of the circuit is

Resonance frequency

Hence

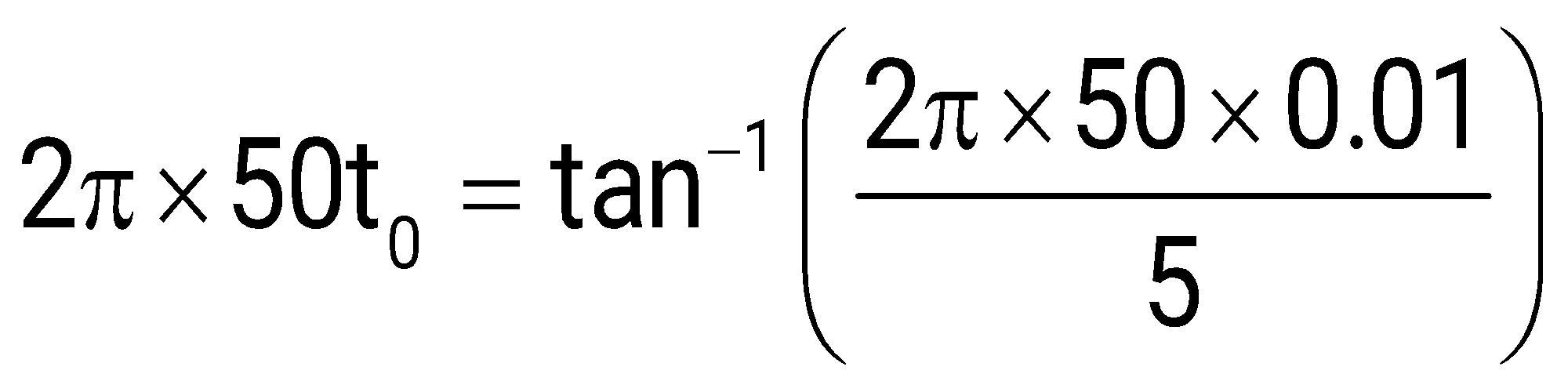

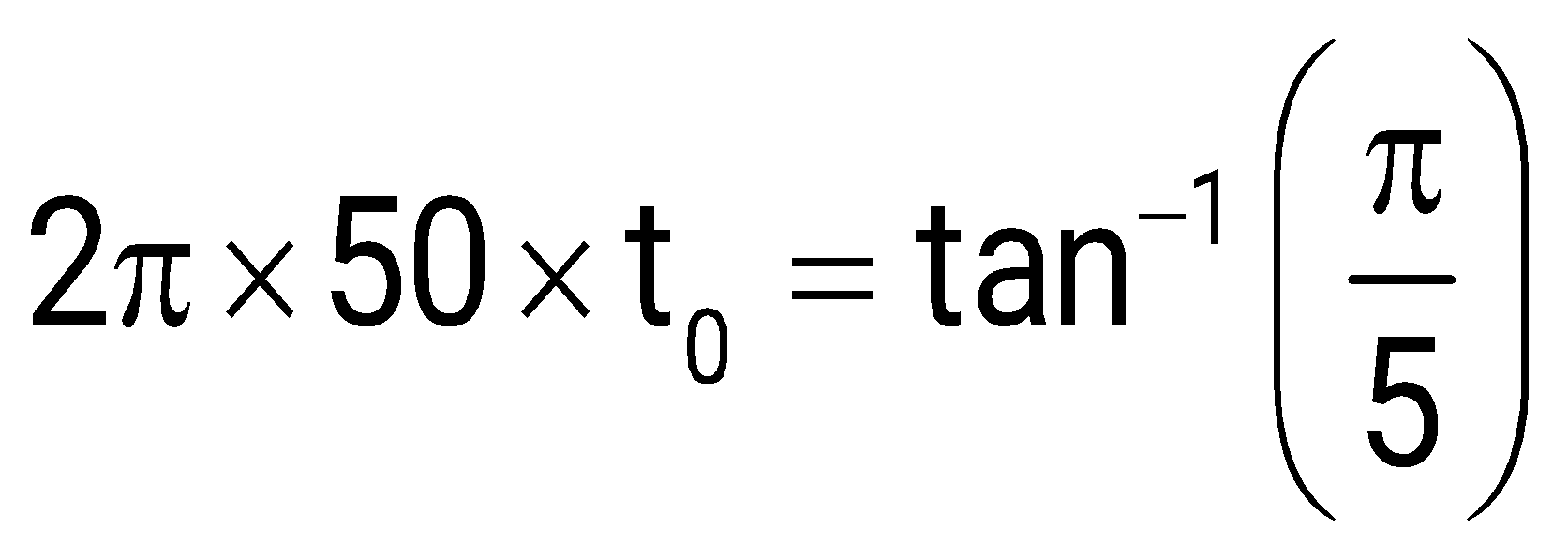

Consider the circuit shown in Figure. If the frequency of the source is 50 Hz, then a value of which results in a transient free response is

For transient free response

Power factor angle

This is based on the concept that if we switch ON at the time corresponding to lagging angle between voltage and current then current starts from 0 and it follows steady state current so there is no transient.

If we switch ON when the steady state current is non-zero then transients are induced.

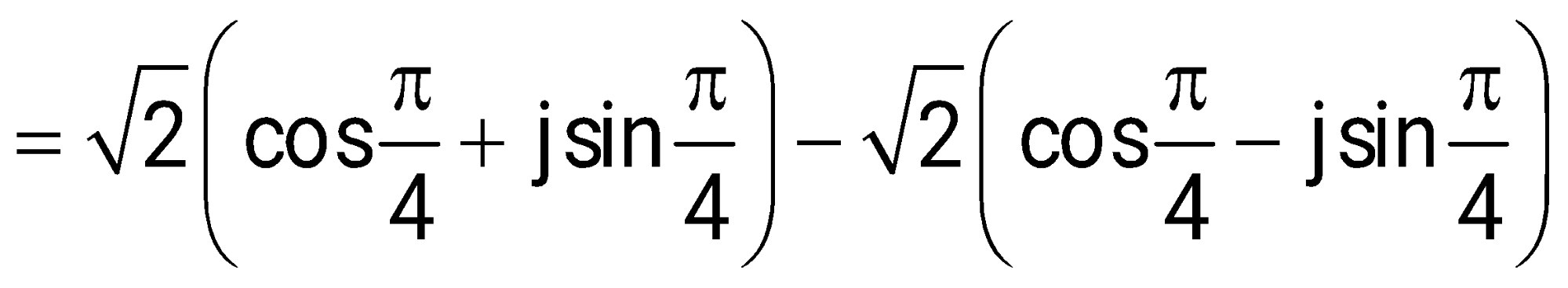

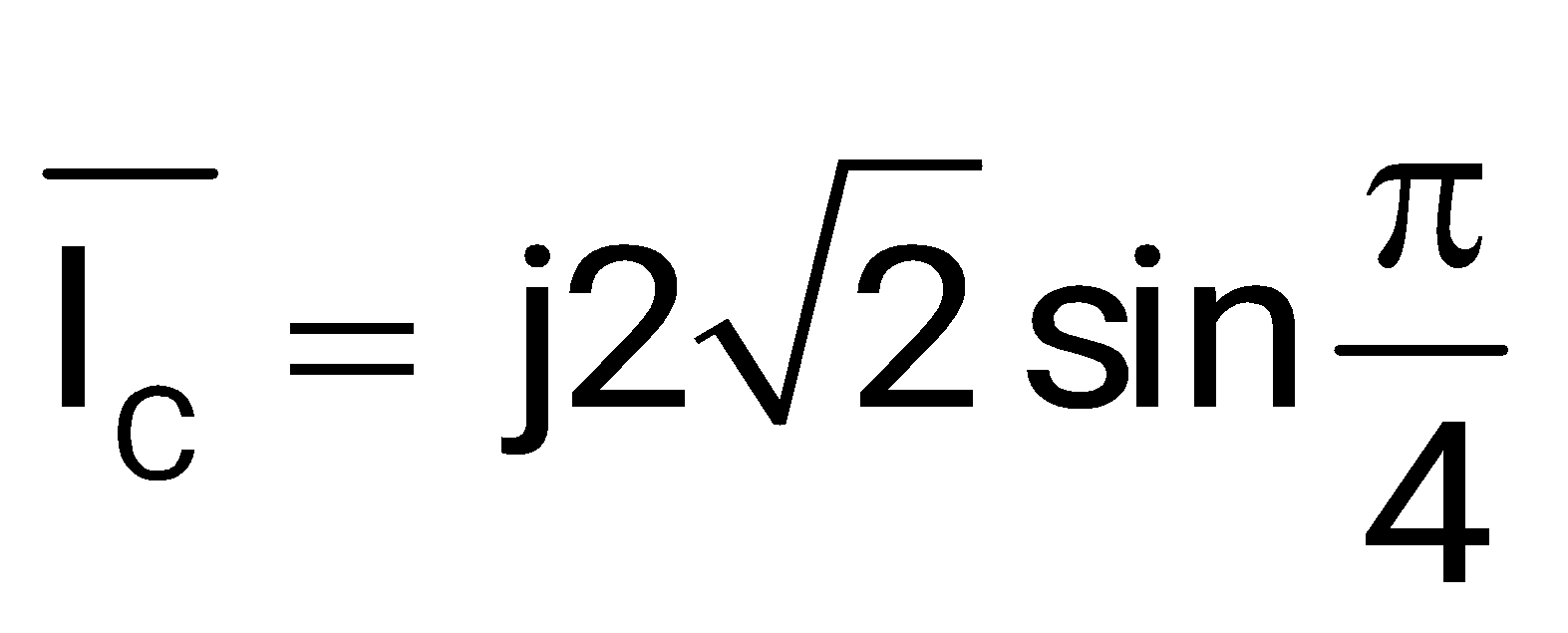

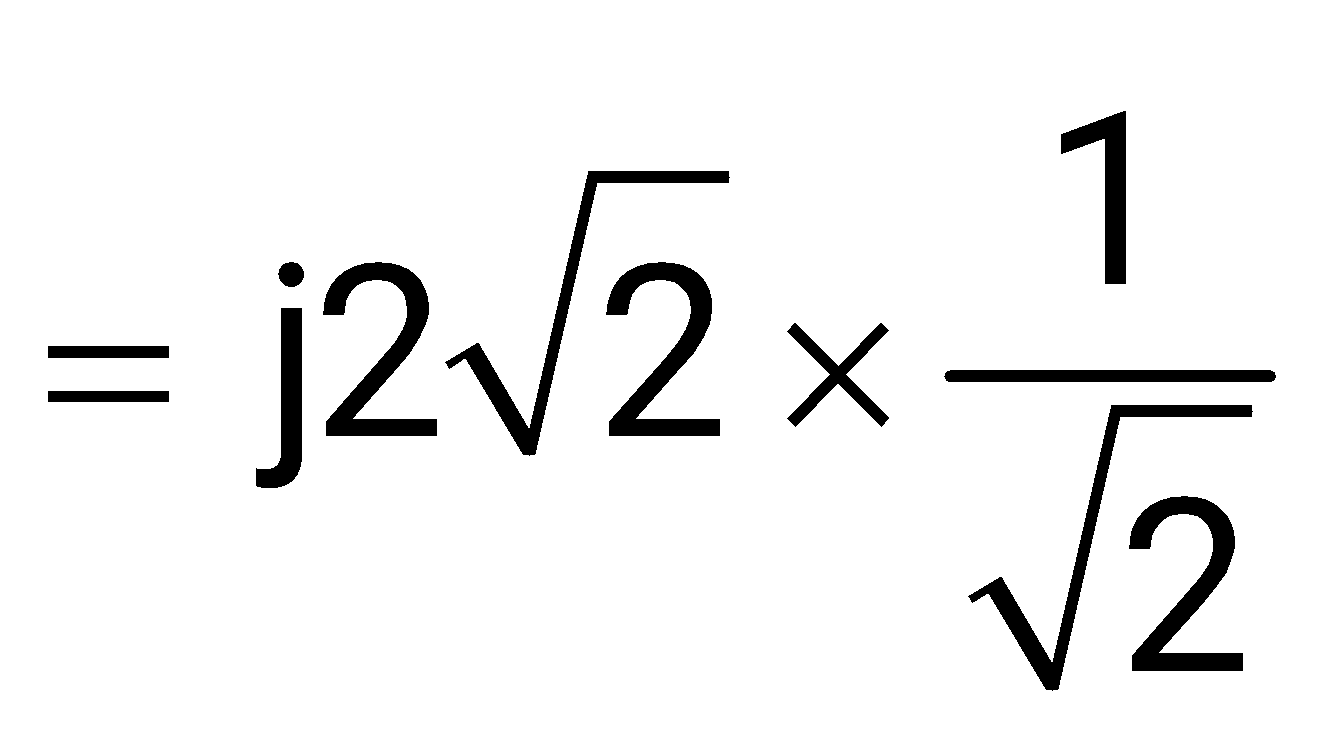

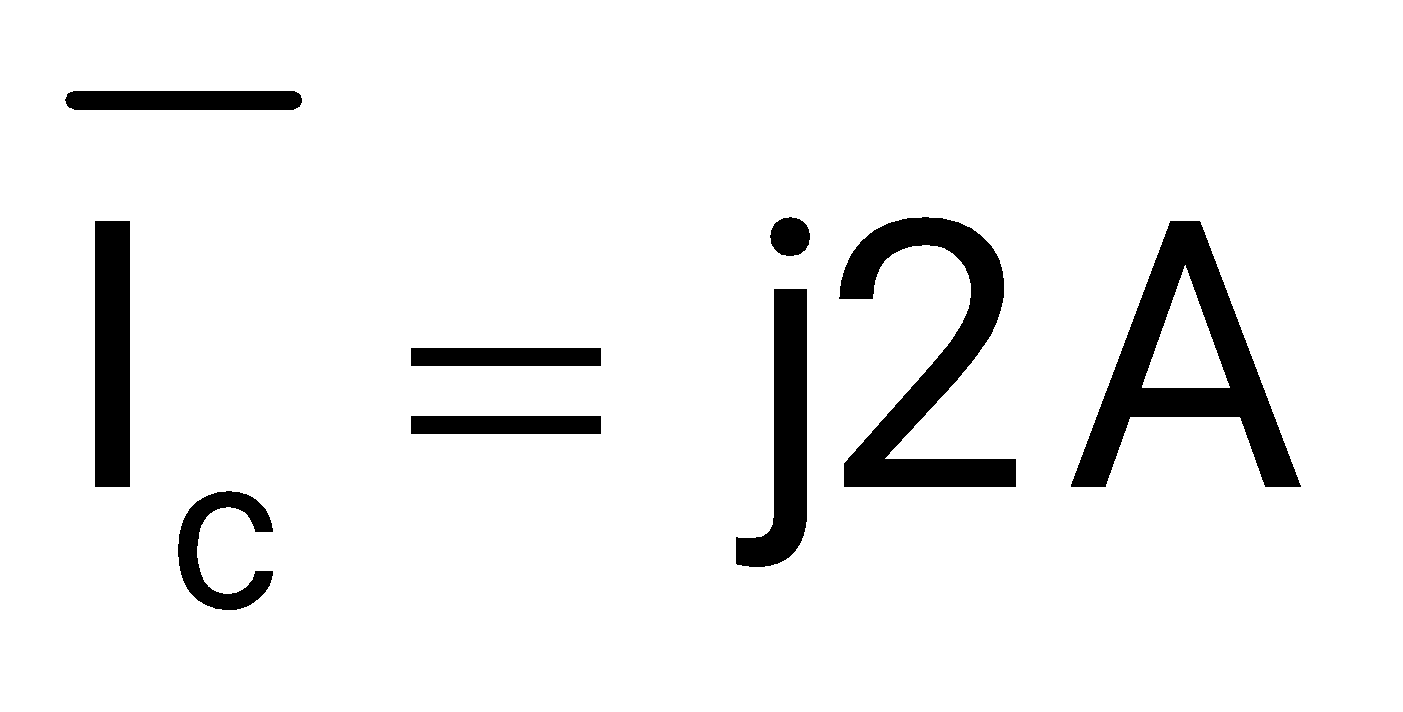

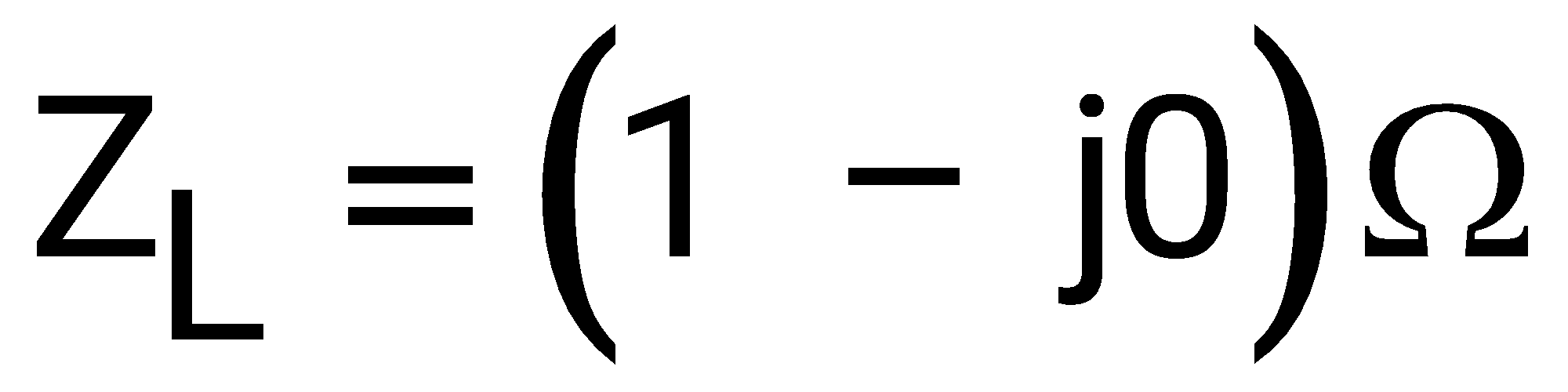

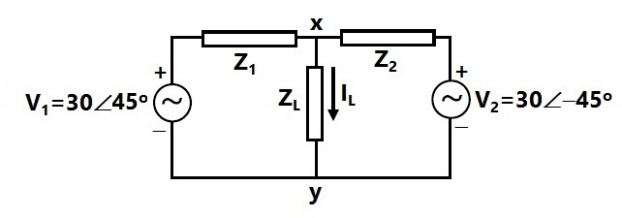

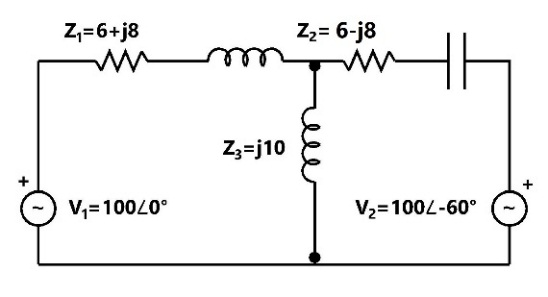

An electrical network is fed by two ac sources, as shown Figure. Given that , and . Obtain the Thevenin equivalent circuit (Thevenin voltage and impedance) across terminals x and y, and determine the current through the load .

To determine the Thevenin Voltage, the load terminals must be opened as shown below,

Applying KVL in loop

To determine Thevenin Impedance, both voltage sources must be shorted as shown below,

Thevenin equivalent circuit:

= 0A

In a series RLC circuit at resonance, the magnitude of the voltage developed across the capacitor.

Current in series RLC circuit is,

Under Resonance Condition,

(in phase with voltage source)

Voltage across capacitor

if ; then = so can be greater than voltage source and is phase behind the source voltage.

A 240 V single-phase ac source is connected to a load with an impedance of . A capacitor is connected in parallel with the load. If the capacitor supplied 1250 VAR, the real power supplied by the source is

Real Power will only be absorbed by Load and not by Capacitor.

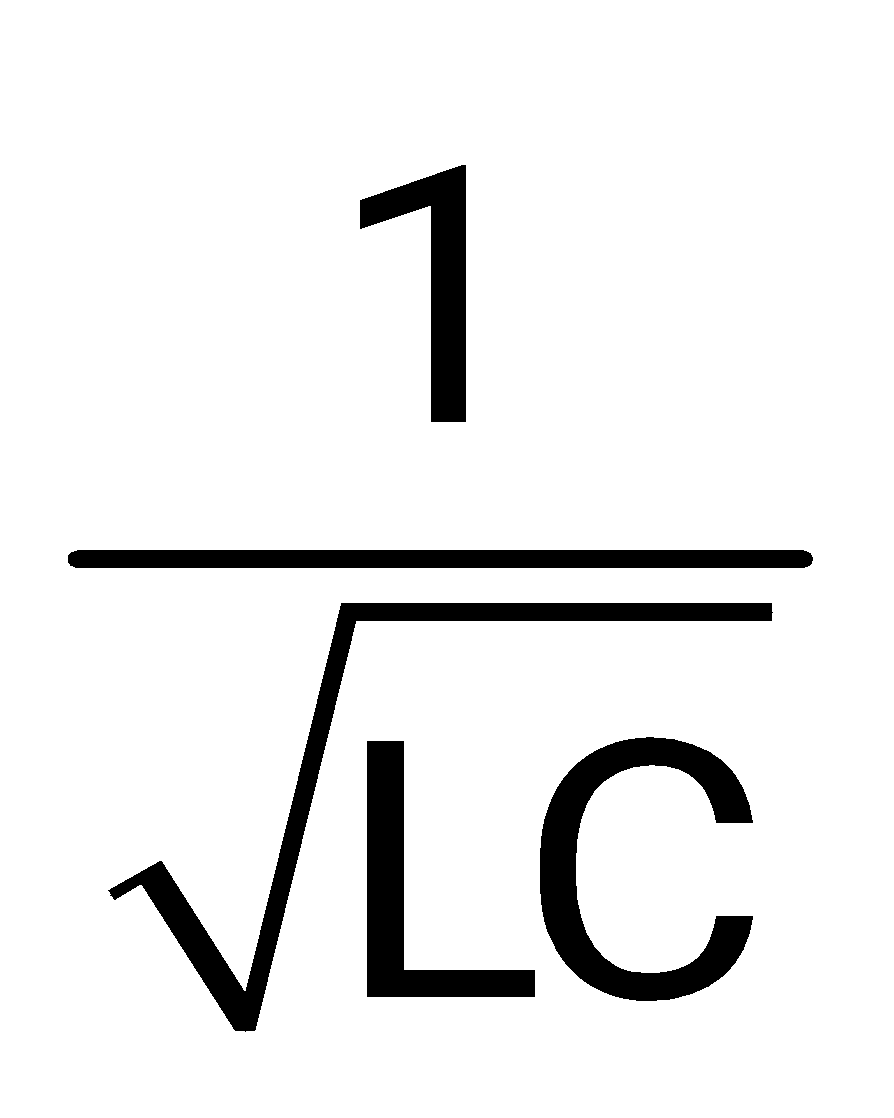

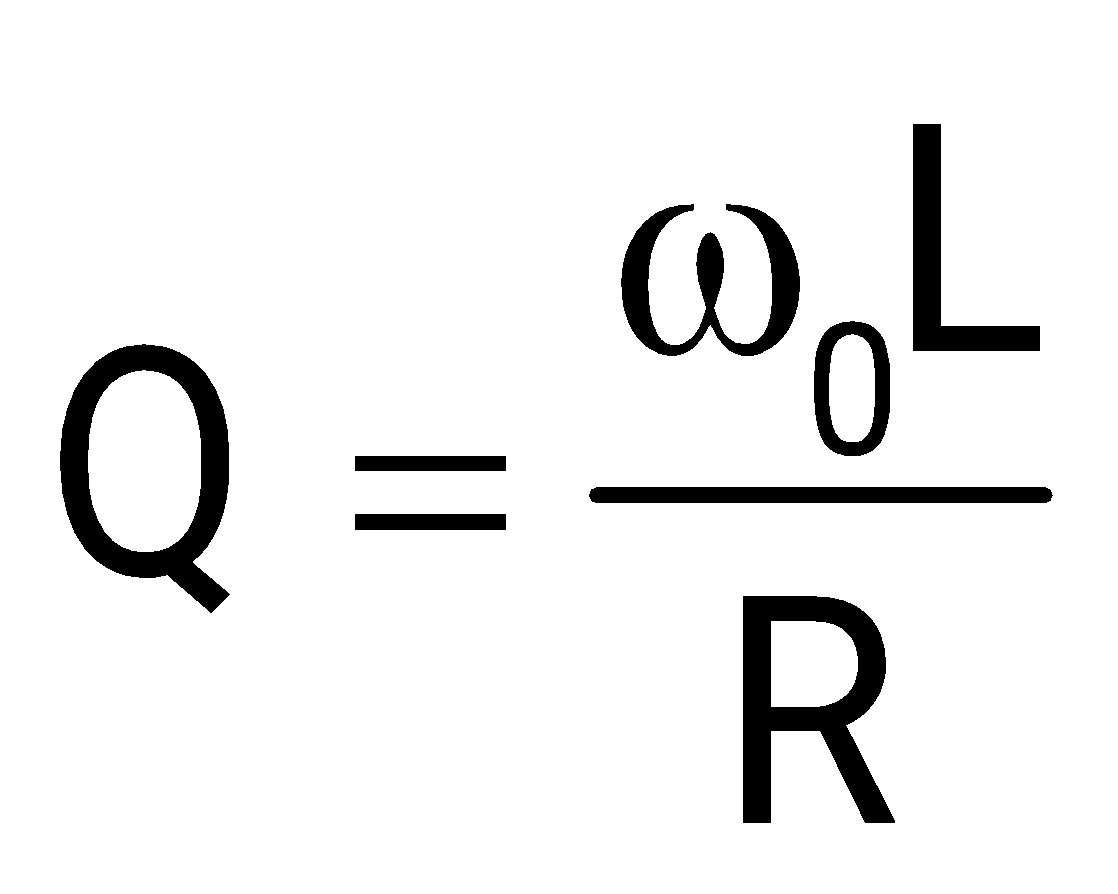

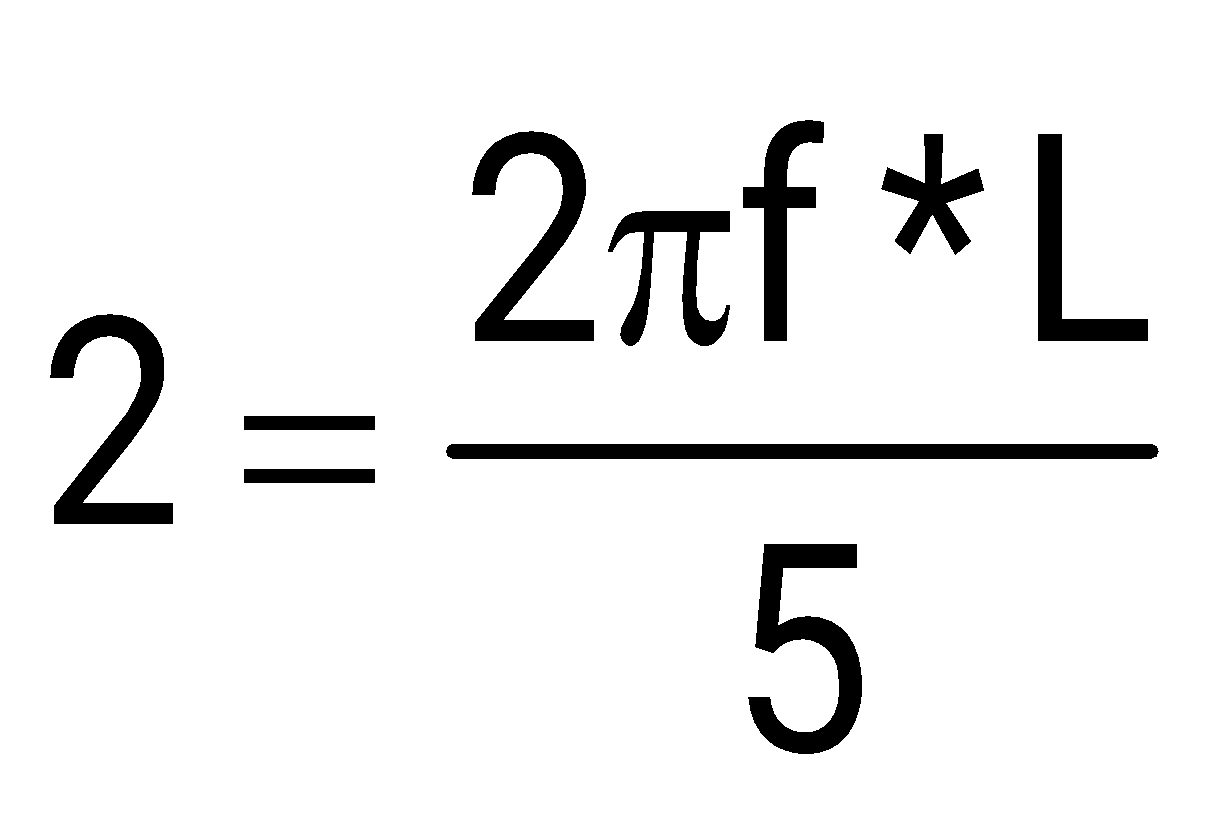

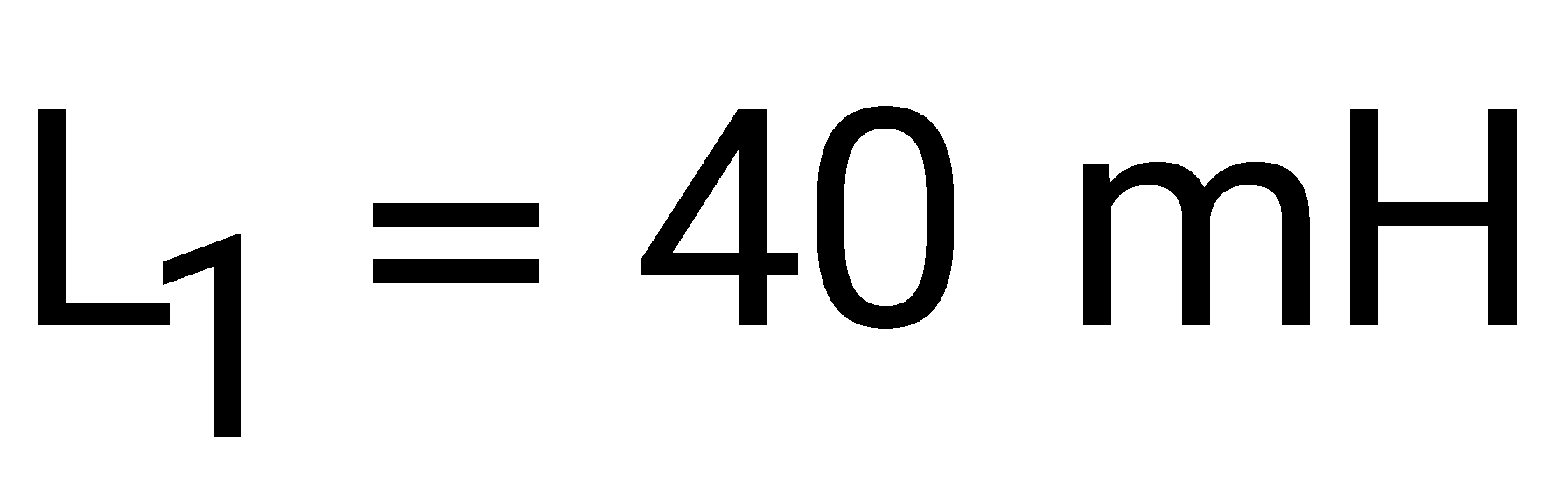

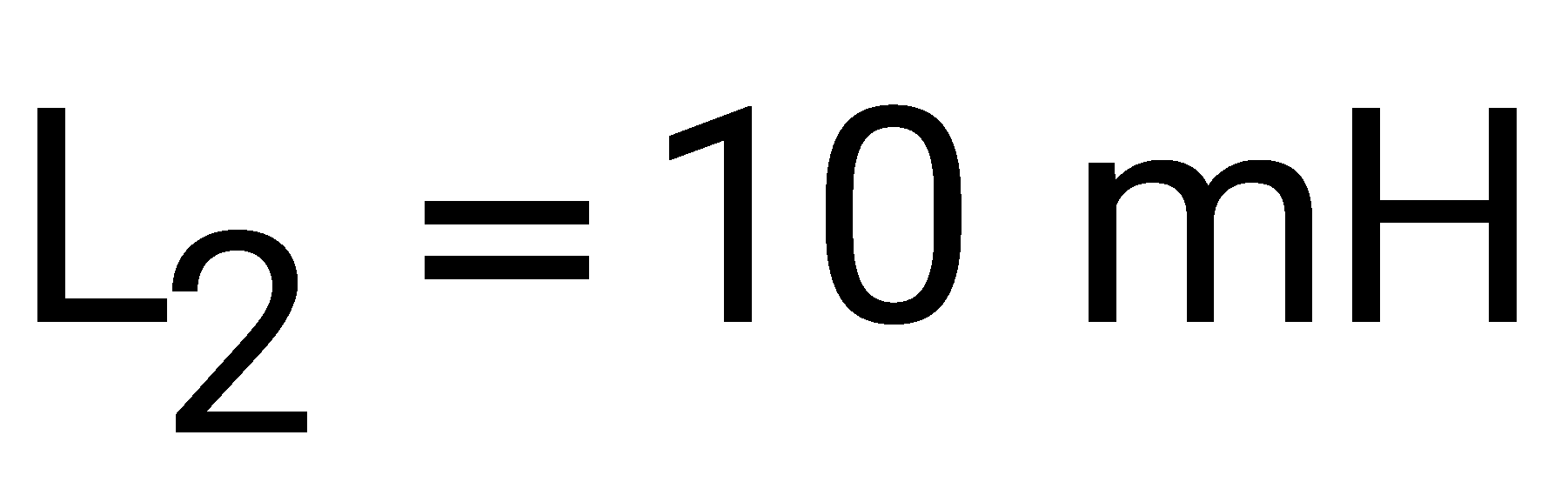

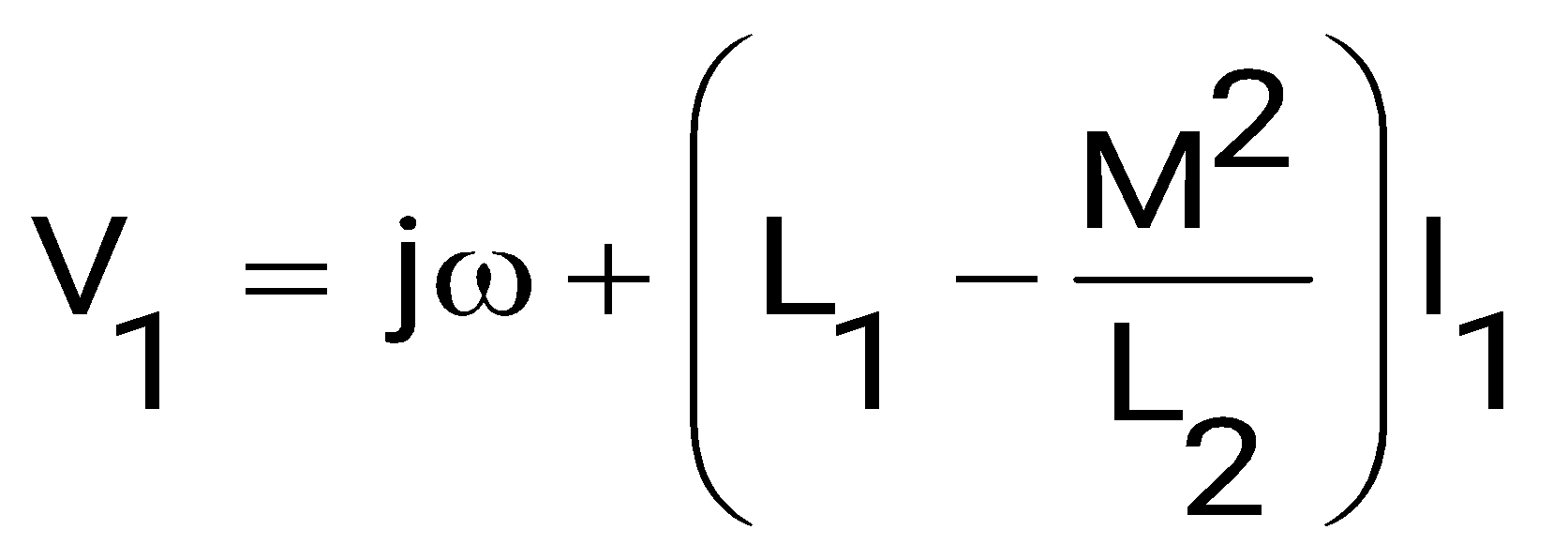

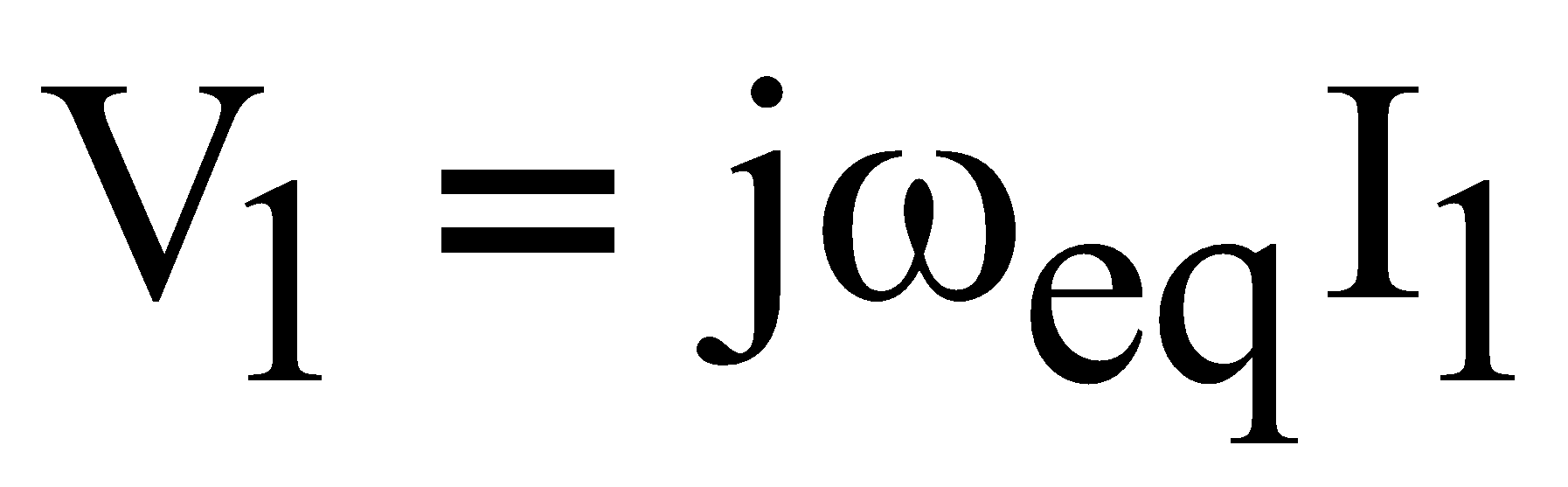

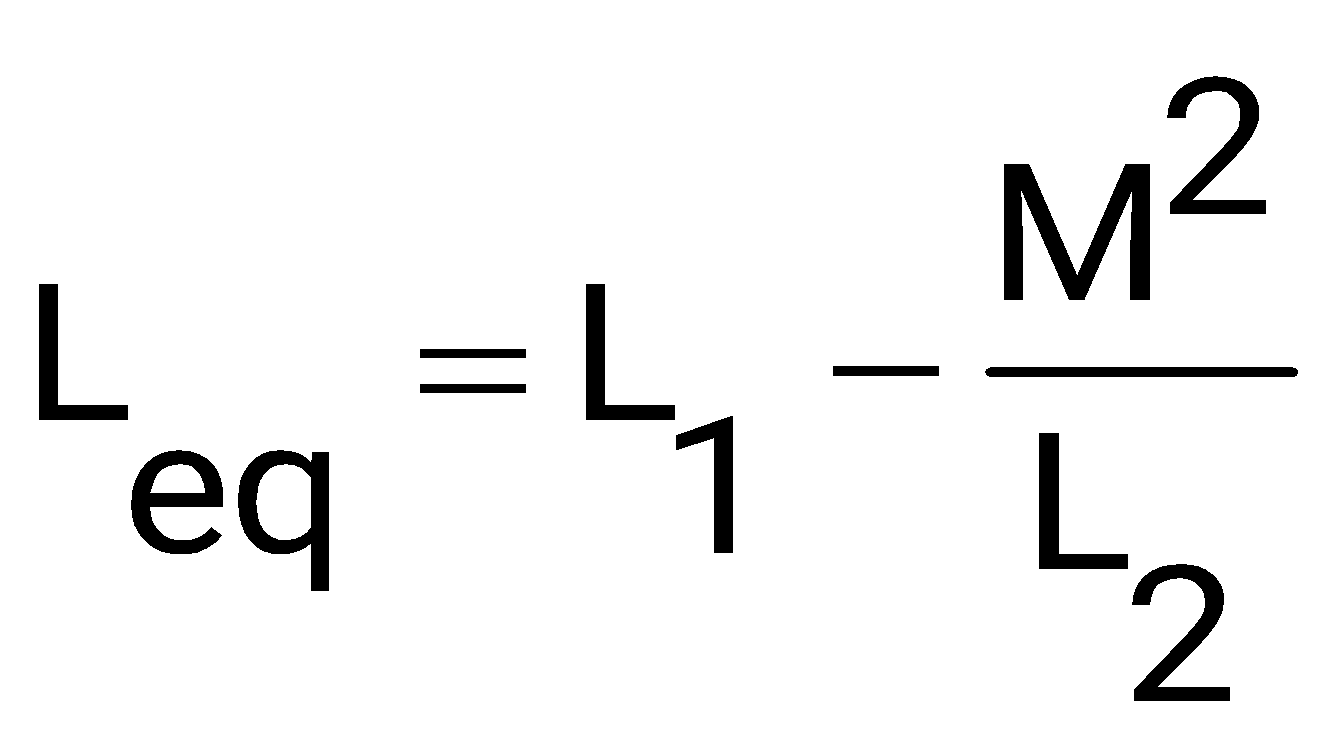

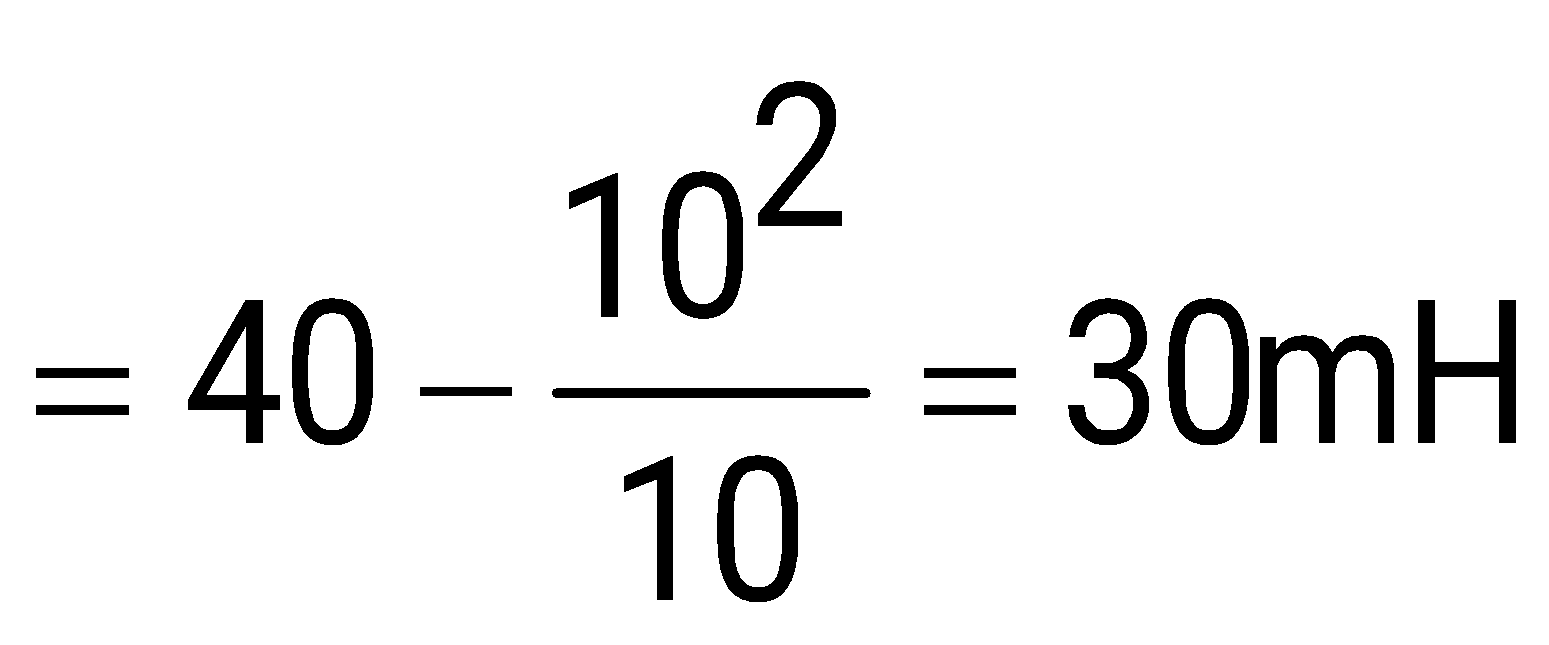

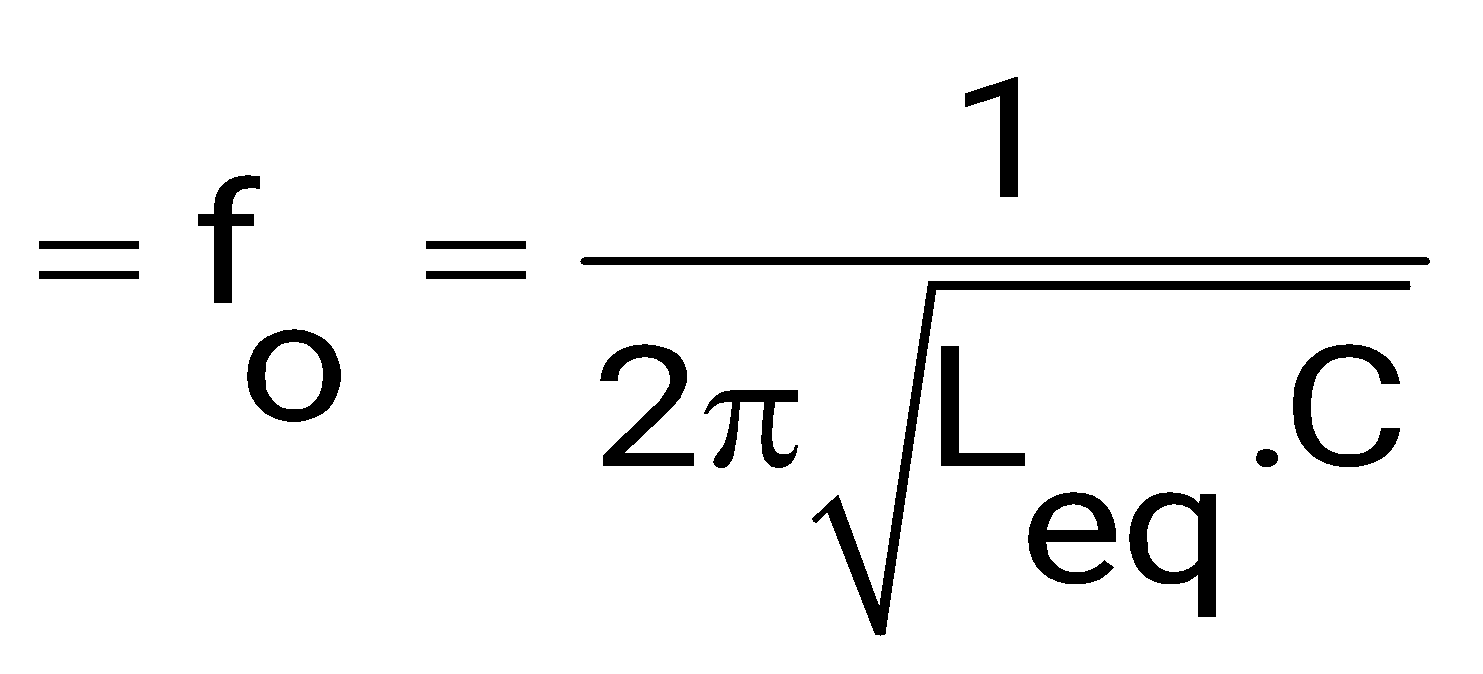

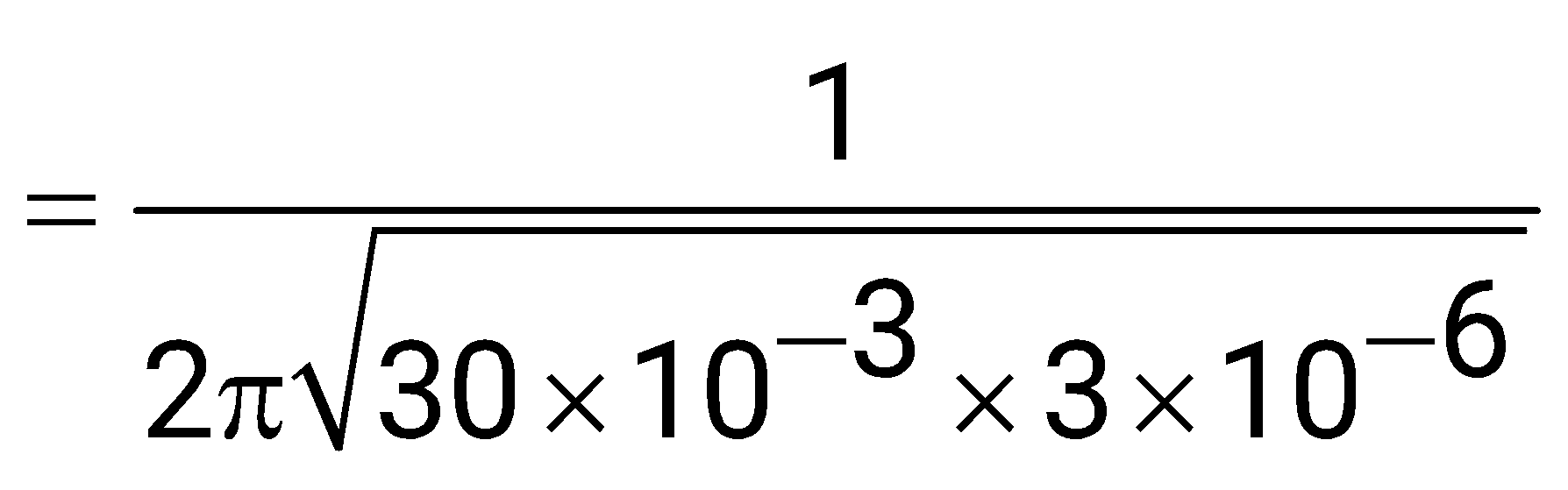

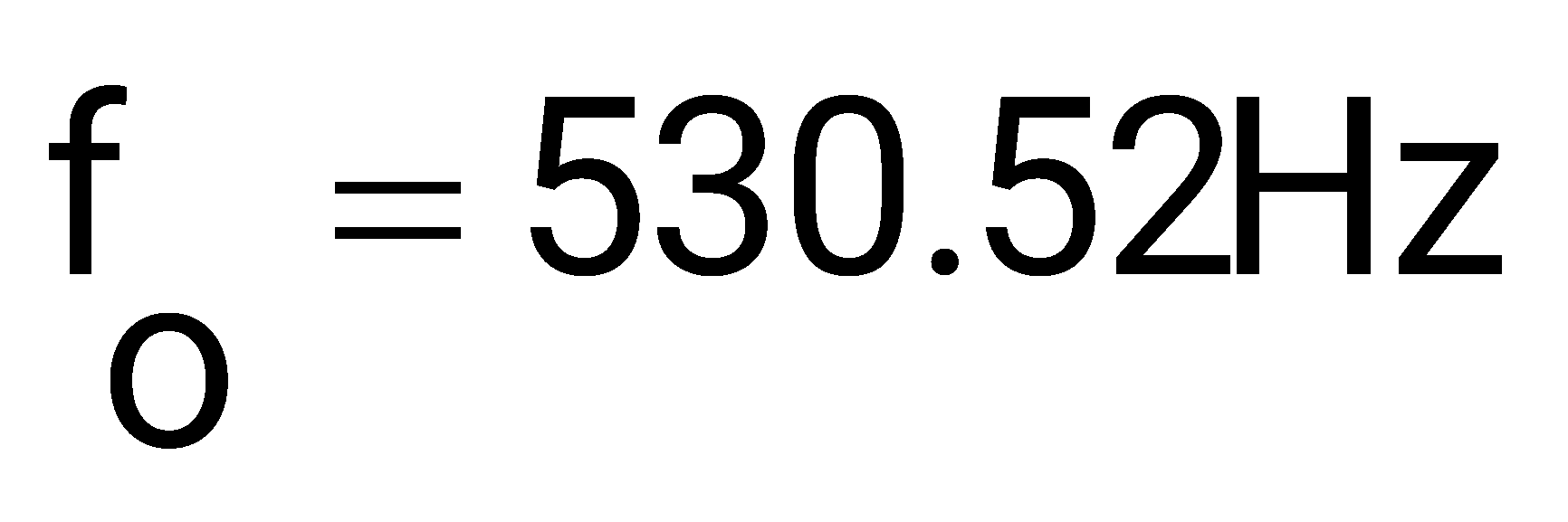

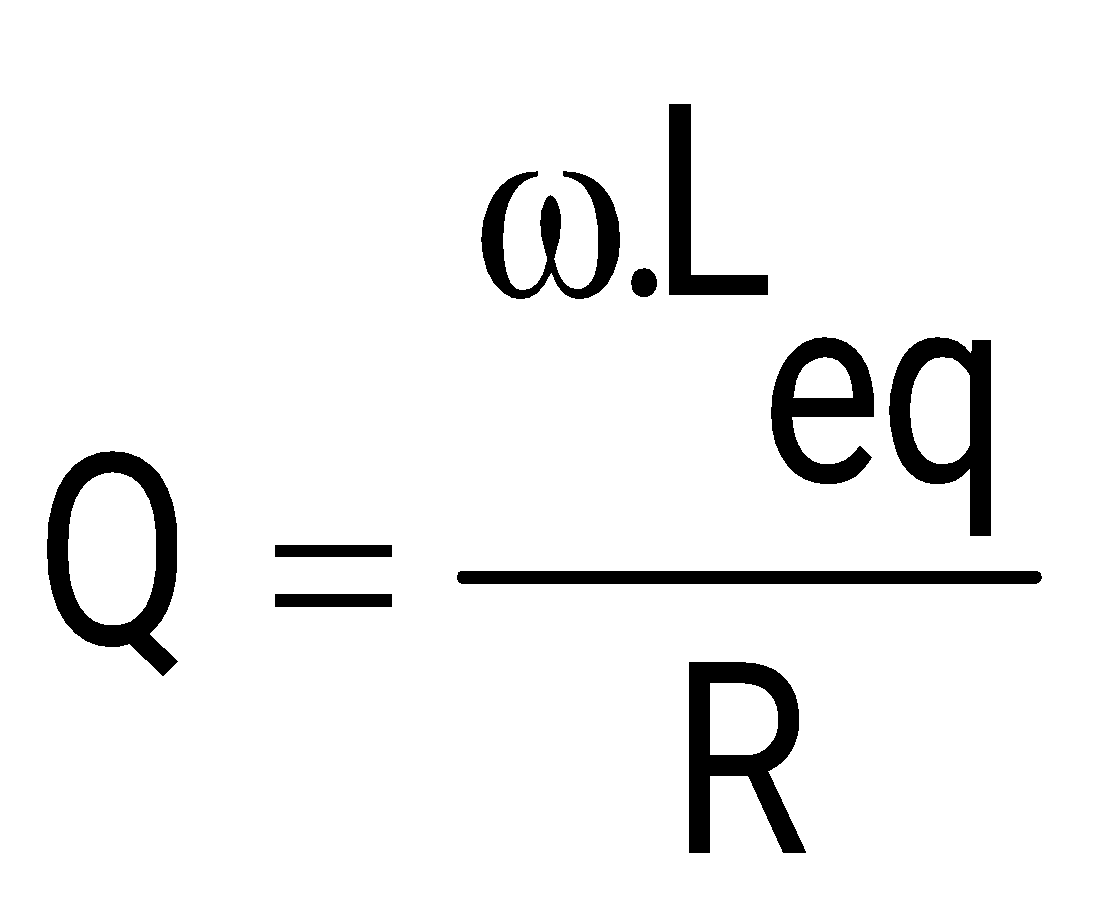

Determine the resonance frequency and the Q-factor of the circuit shown in figure.

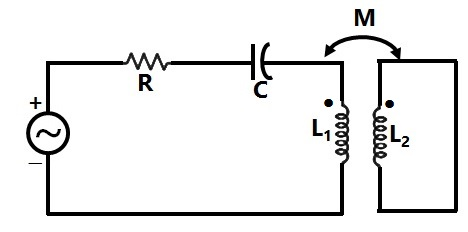

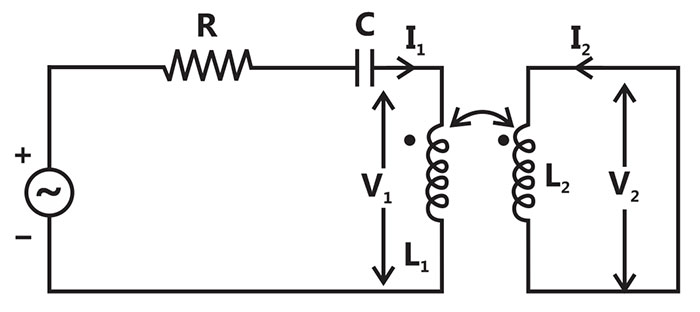

Data: R = 10Ω, C = 3µF, , and M = 10 mH.

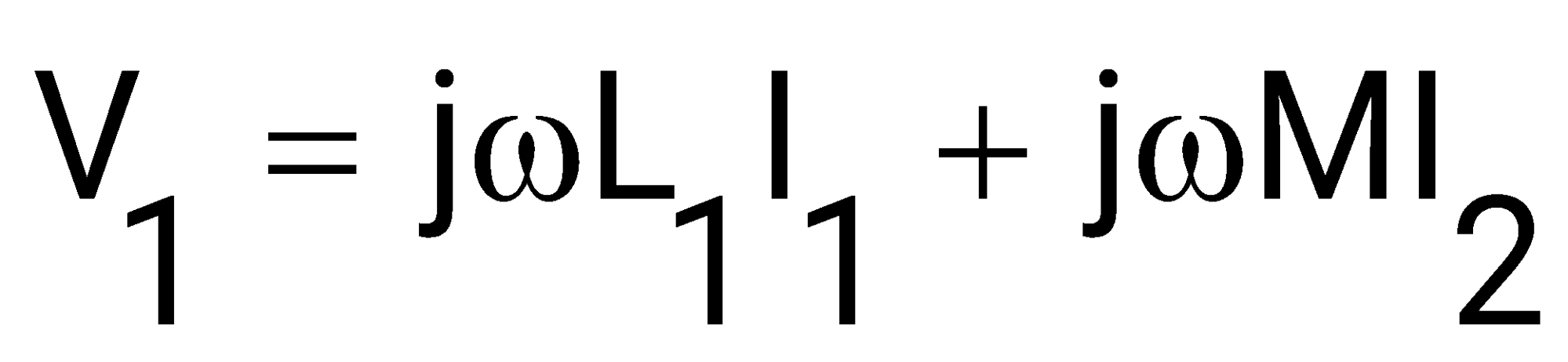

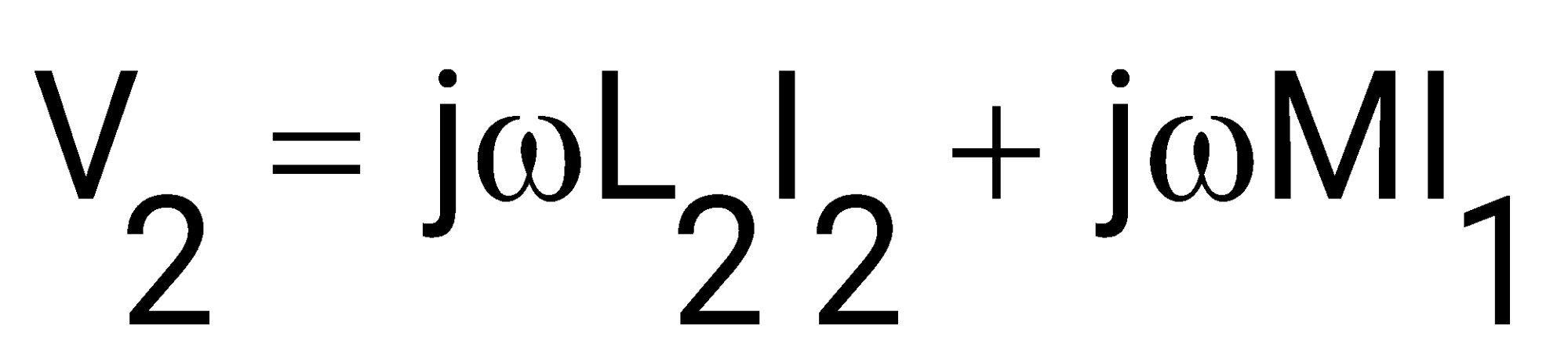

Assuming currents and voltages on both sides the system is shown below

Since, ---------(1)

---------(2)

Since output side is short circuited, so

---------(3)

From equation 1 & 3

When

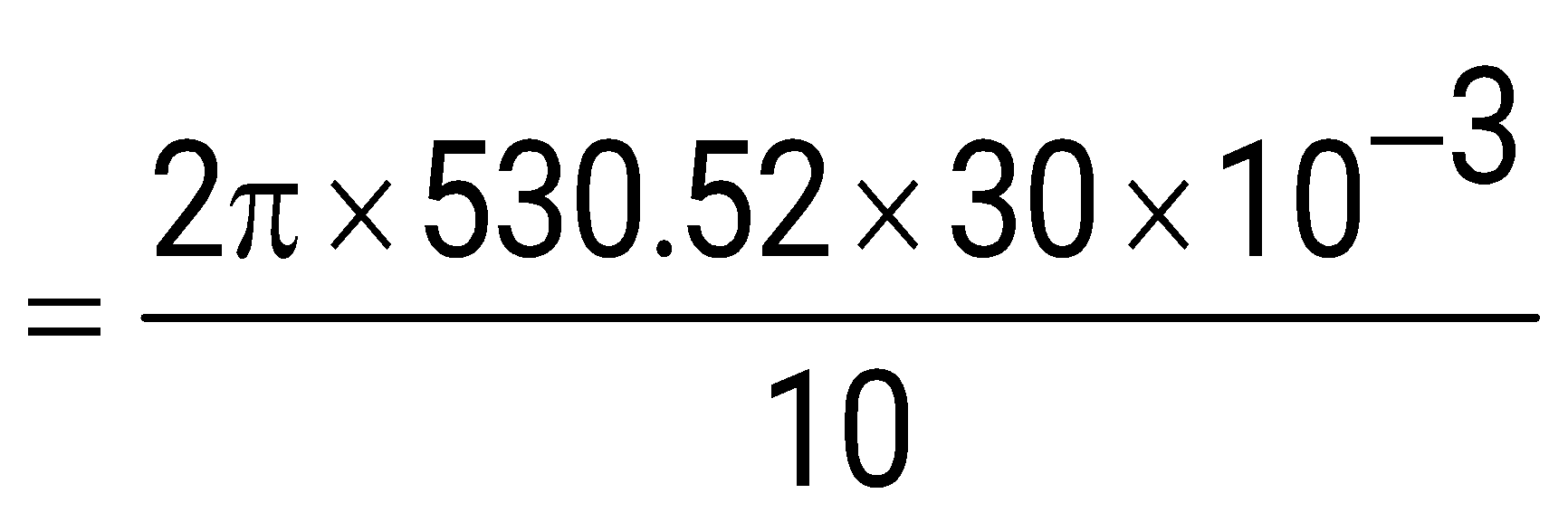

Resonance Frequency

Quality factor

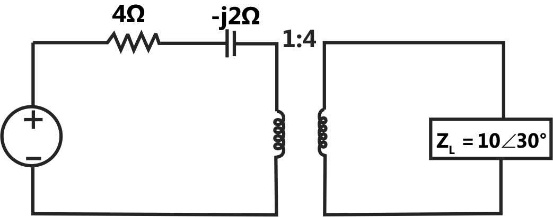

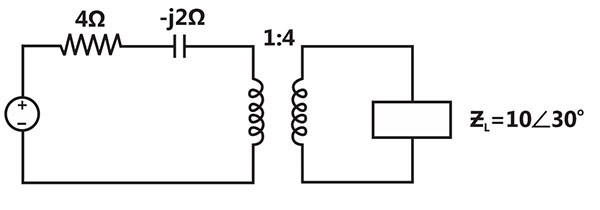

The impedance seen by the source in the circuit in figure, is given by

The given system is shown below,

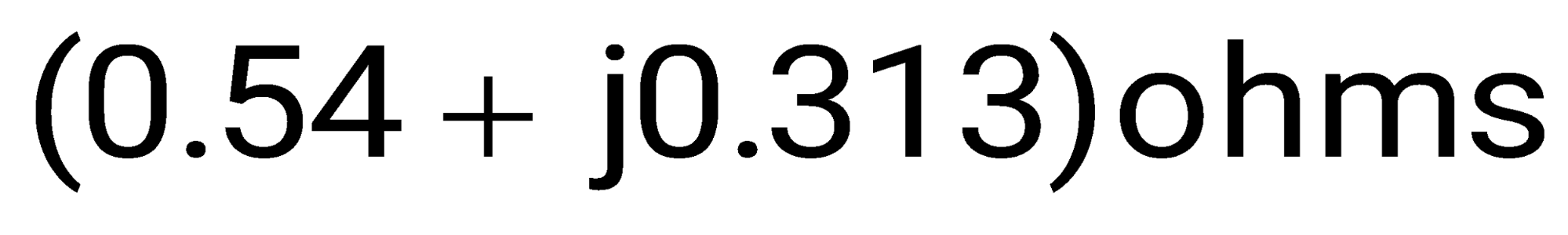

Referring load impedance

‘’ to primary side

Equivalent circuit becomes as shown below,

Impedance seen by source,

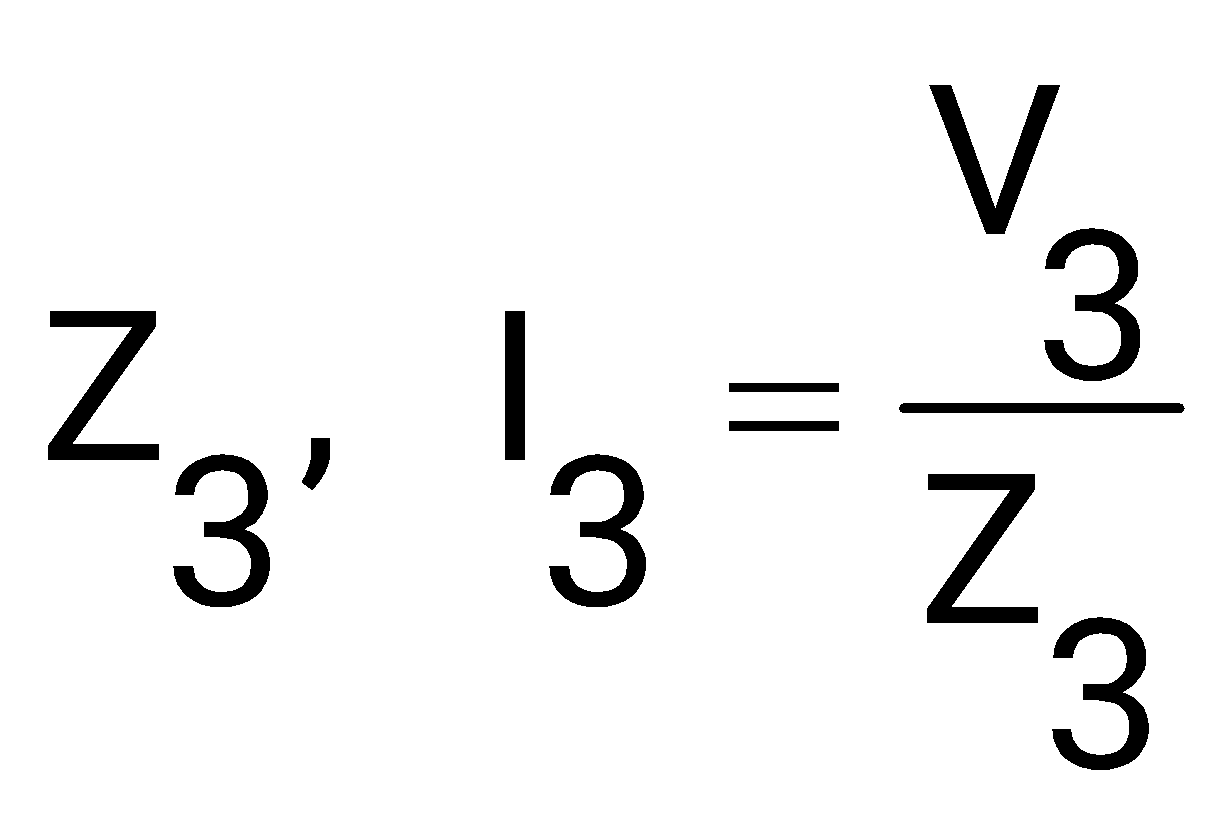

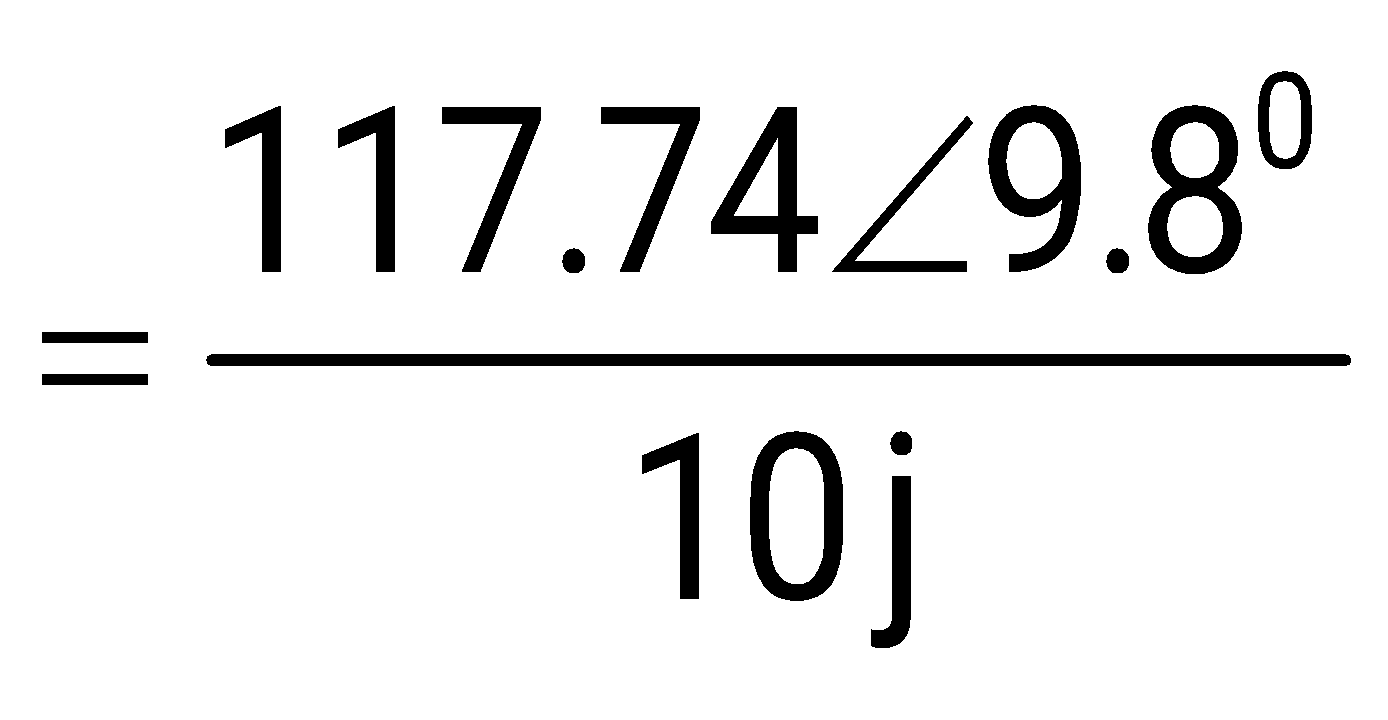

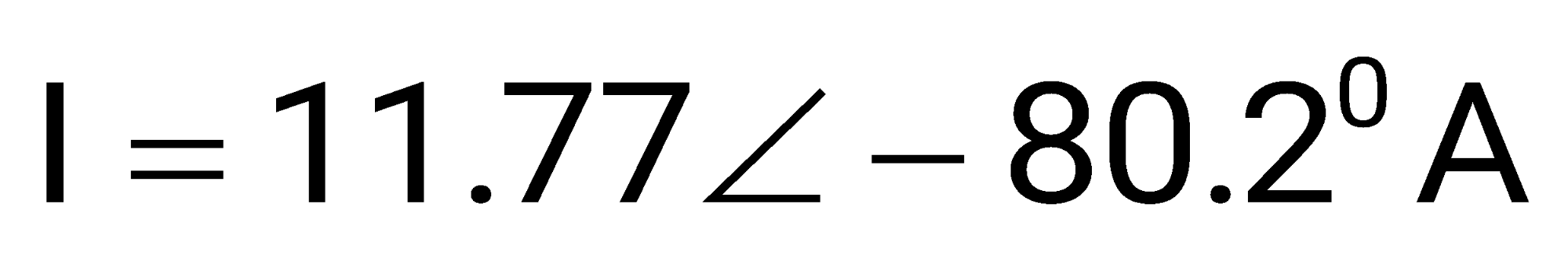

Predict the current I in figure in response to a voltage of . The impedance values are given in ohms. Use the thevenin’s theorem.

To determine Thevenin equivalent across the 10Ω resistor, the resistor must be open circuited as shown below,

By voltage divider rule

Zth across resistor, the voltage source is short circuited,

So, Thevenin equivalent circuit is shown below,

The current in the circuit shown in figure is:

Since,

but voltage across capacitor are opposite in phase.

So, net effect of capacitor and inductor cancels out. Circuit is under resonance.

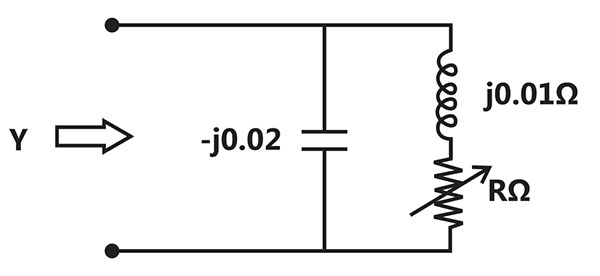

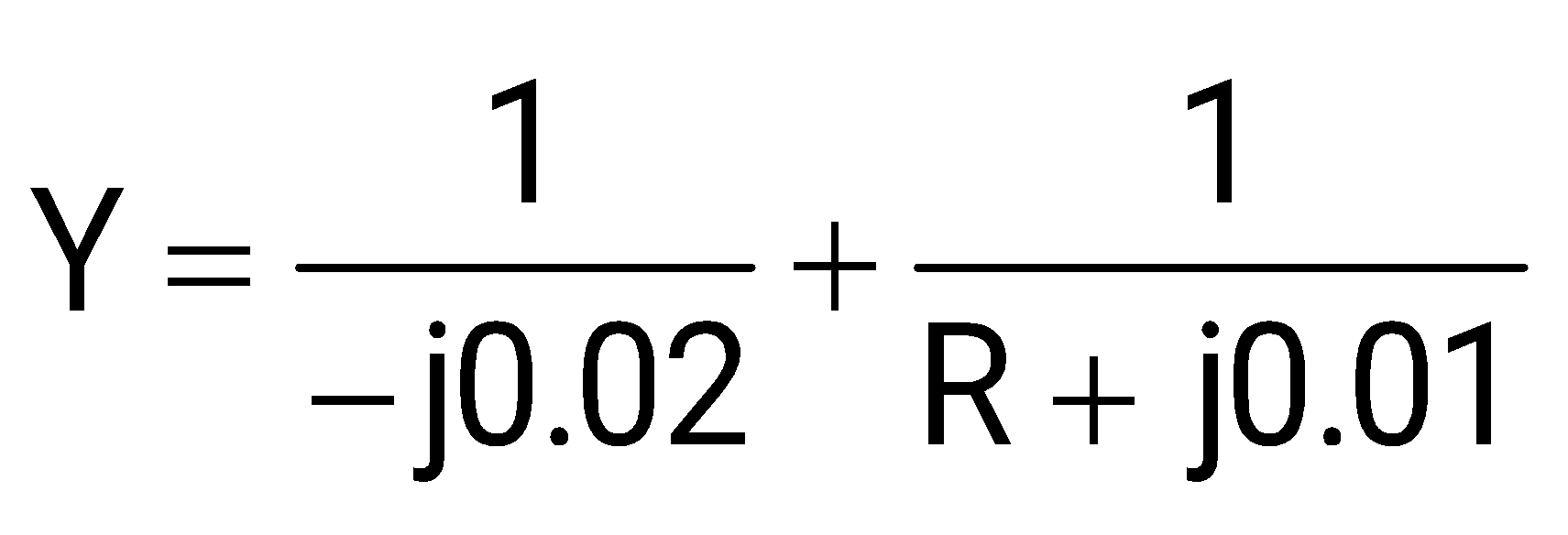

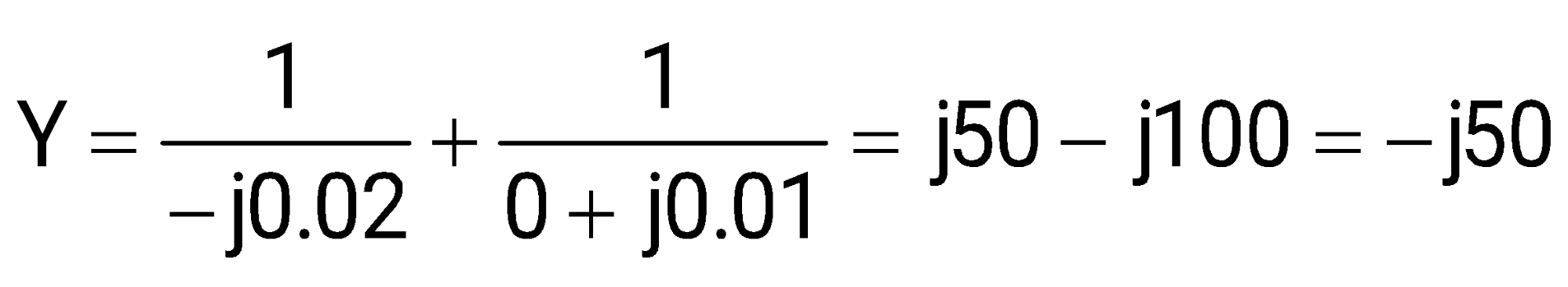

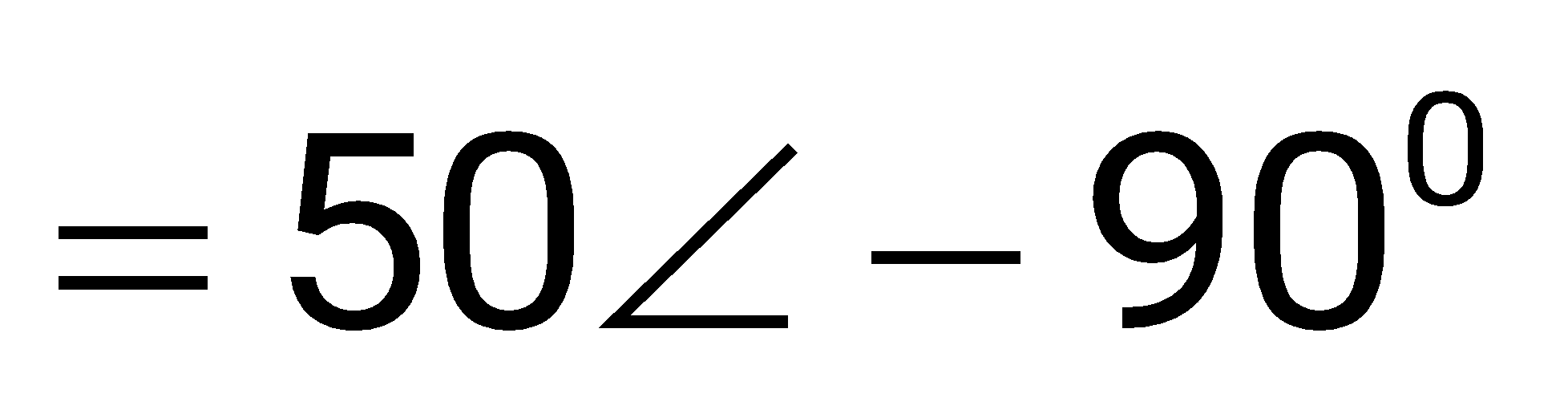

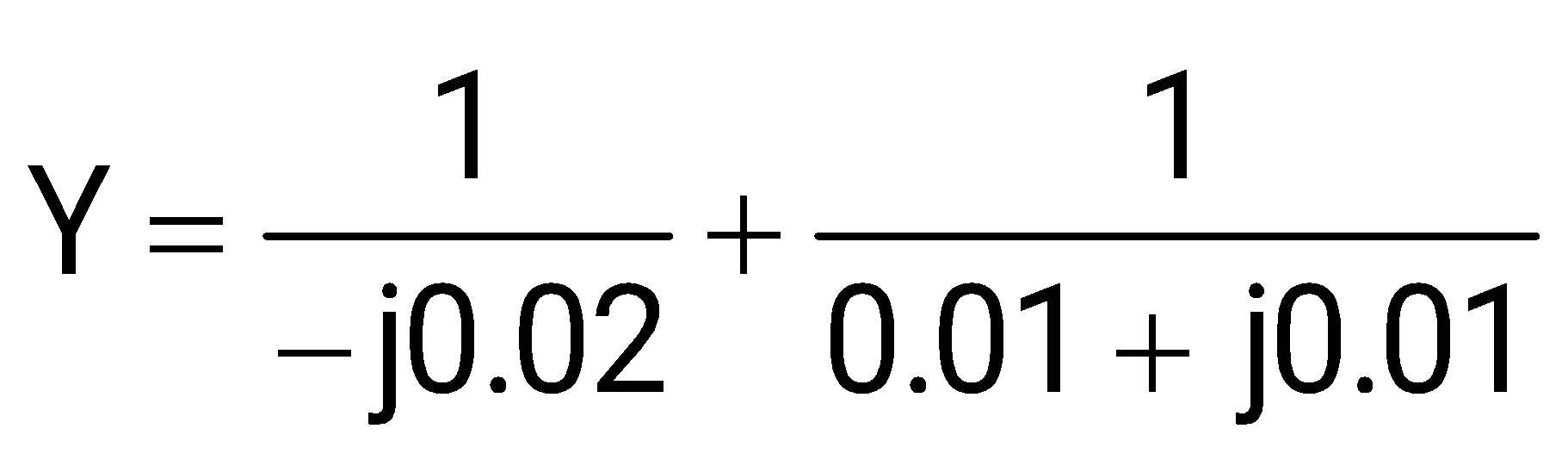

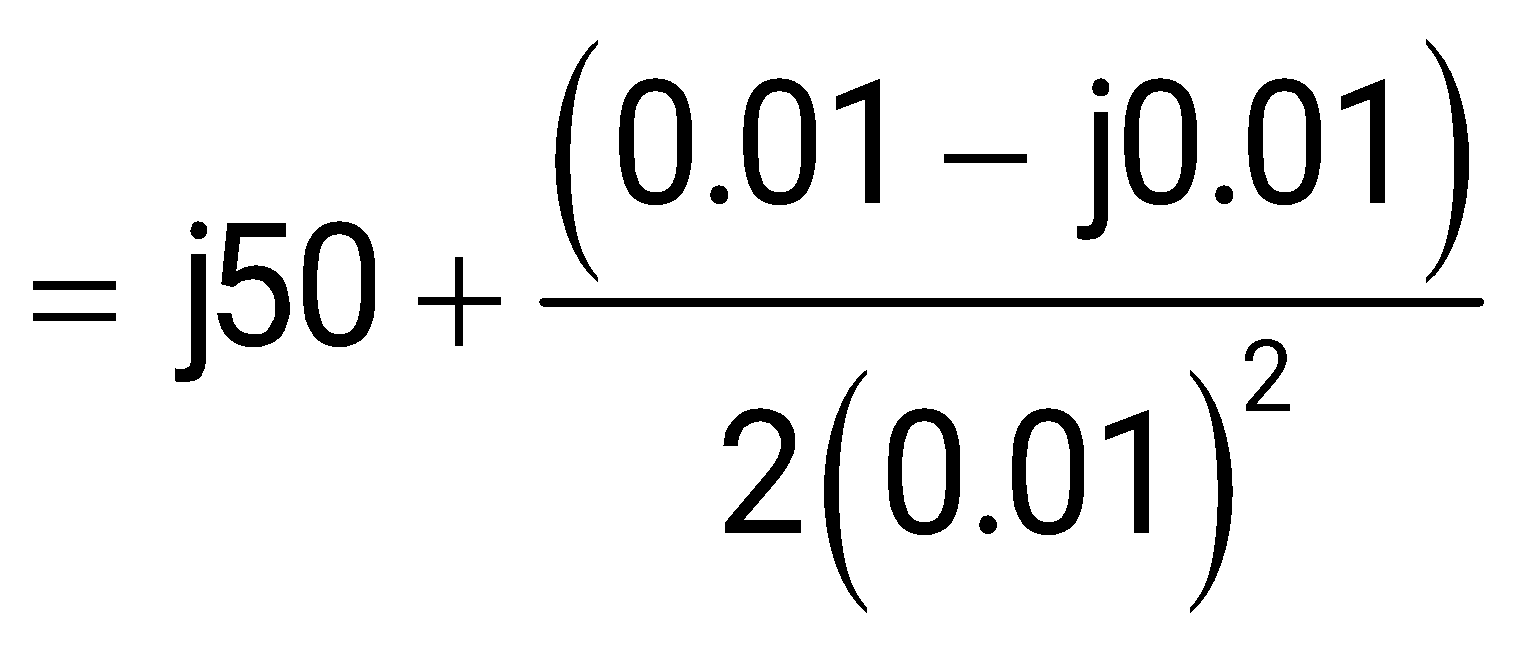

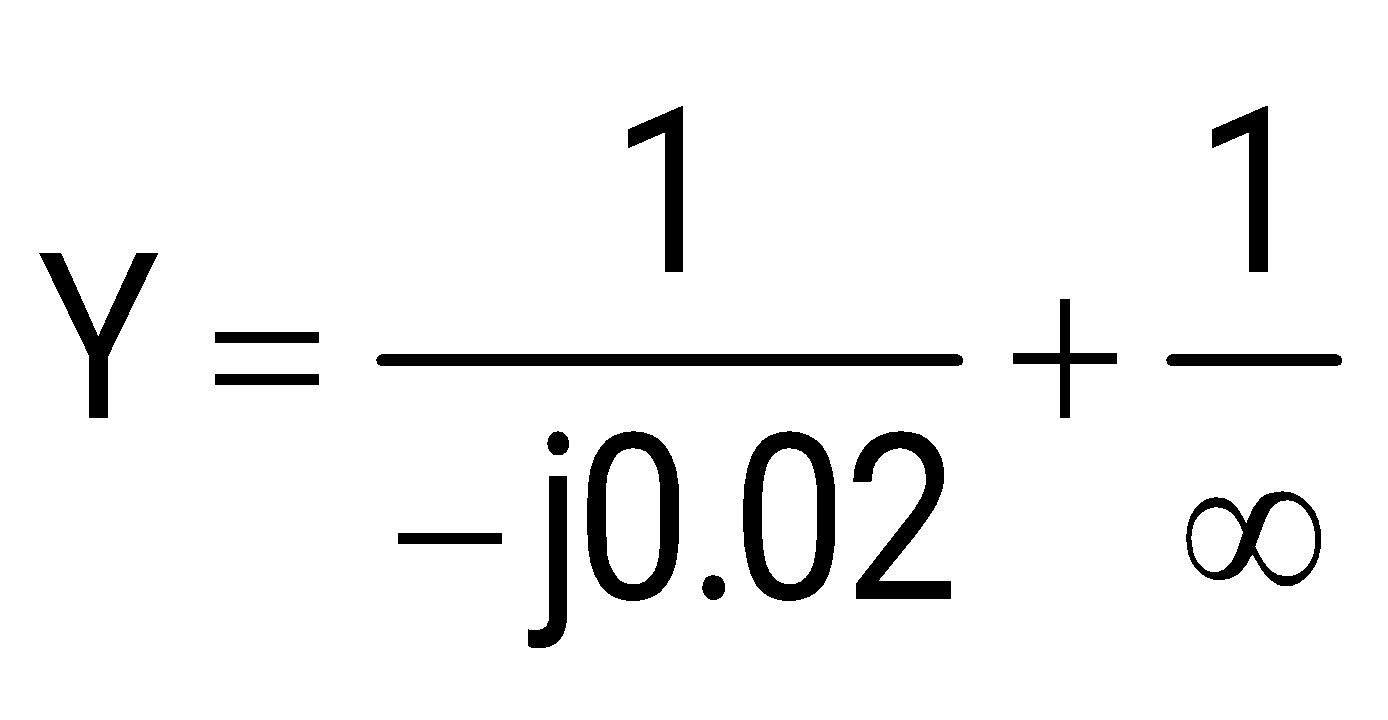

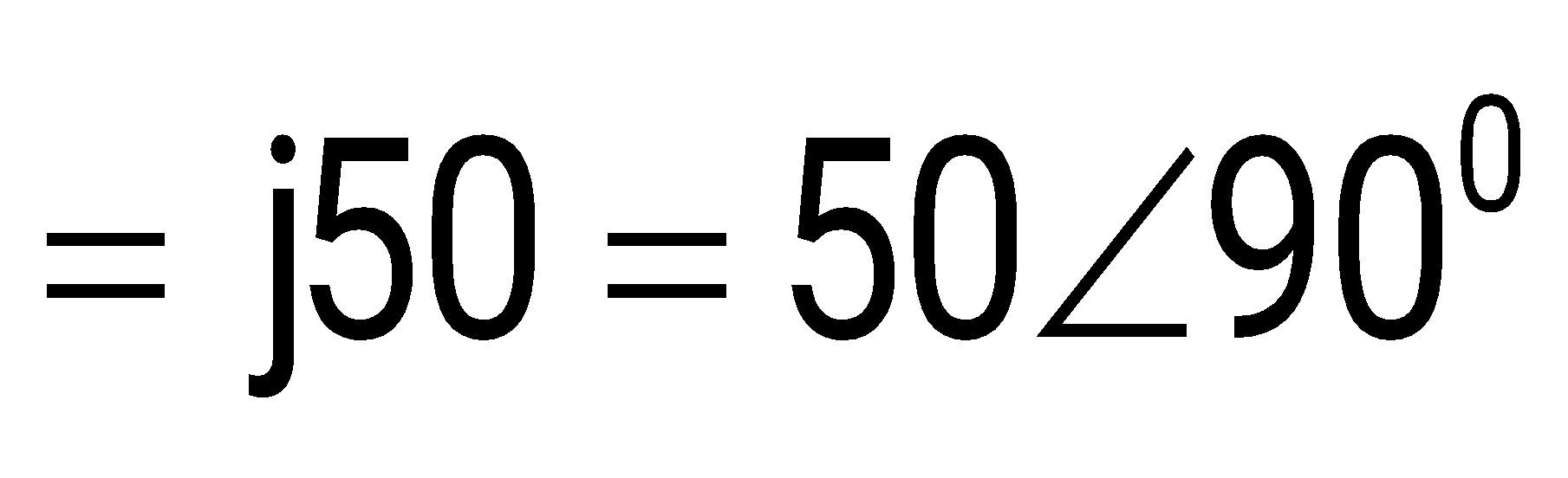

A fixed capacitor of reactance –j0.02 kΩ is connected in parallel across a series combination of a fixed inductor of reactance j0.01 kΩ and a variable resistance R. As R is varied from zero to infinity, the locus diagram of the admittance of this L-C-R circuit will be

The arrangement in the question is shown below,

Admittance

When R = 0

When R = 0.01

= 50 S

When

So the locus of Y looks like as shown below,

It is a semi-circle of diameter j100 and center at zero.

The voltage phasor of a circuit is and the current phasor is A. The active and the reactive powers in the circuit are:

Given voltage source,

Supply Current,

Complex power

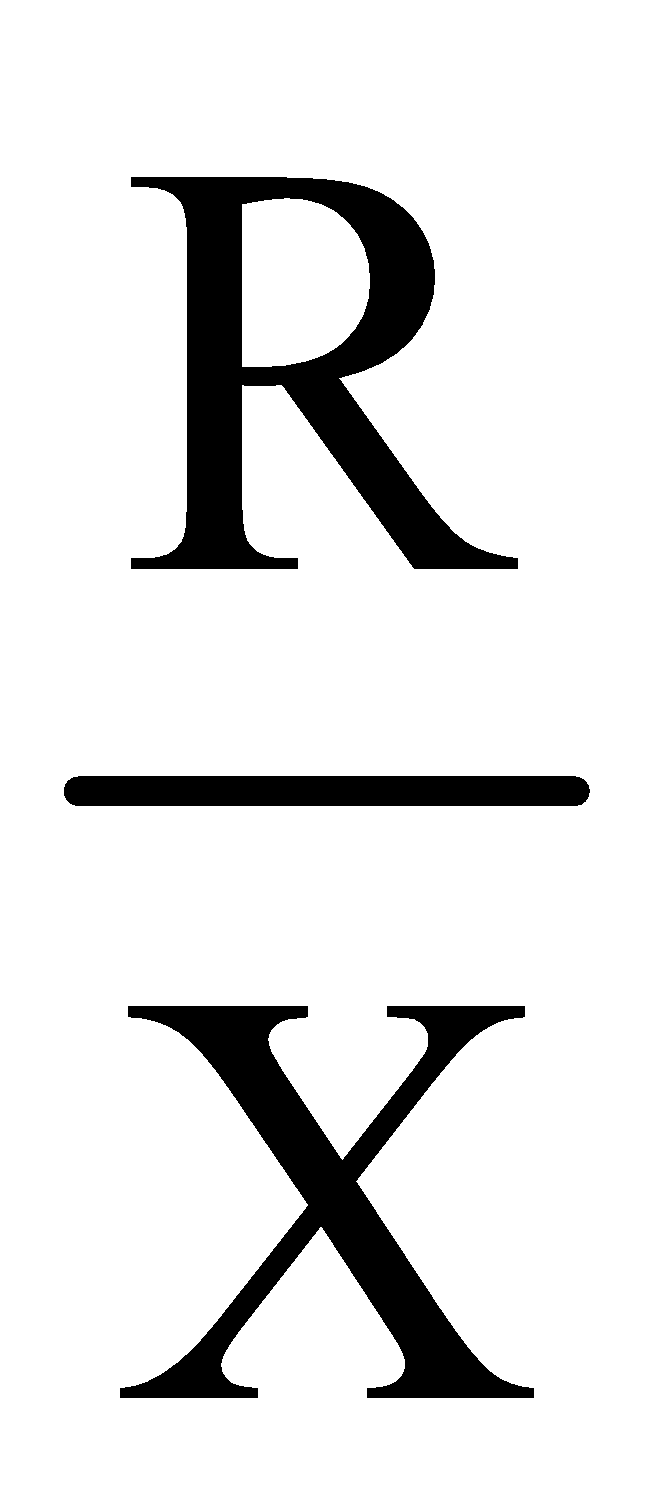

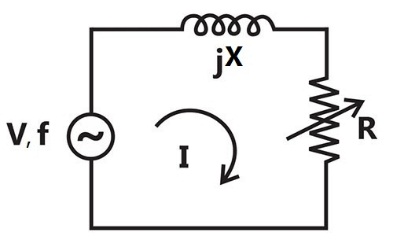

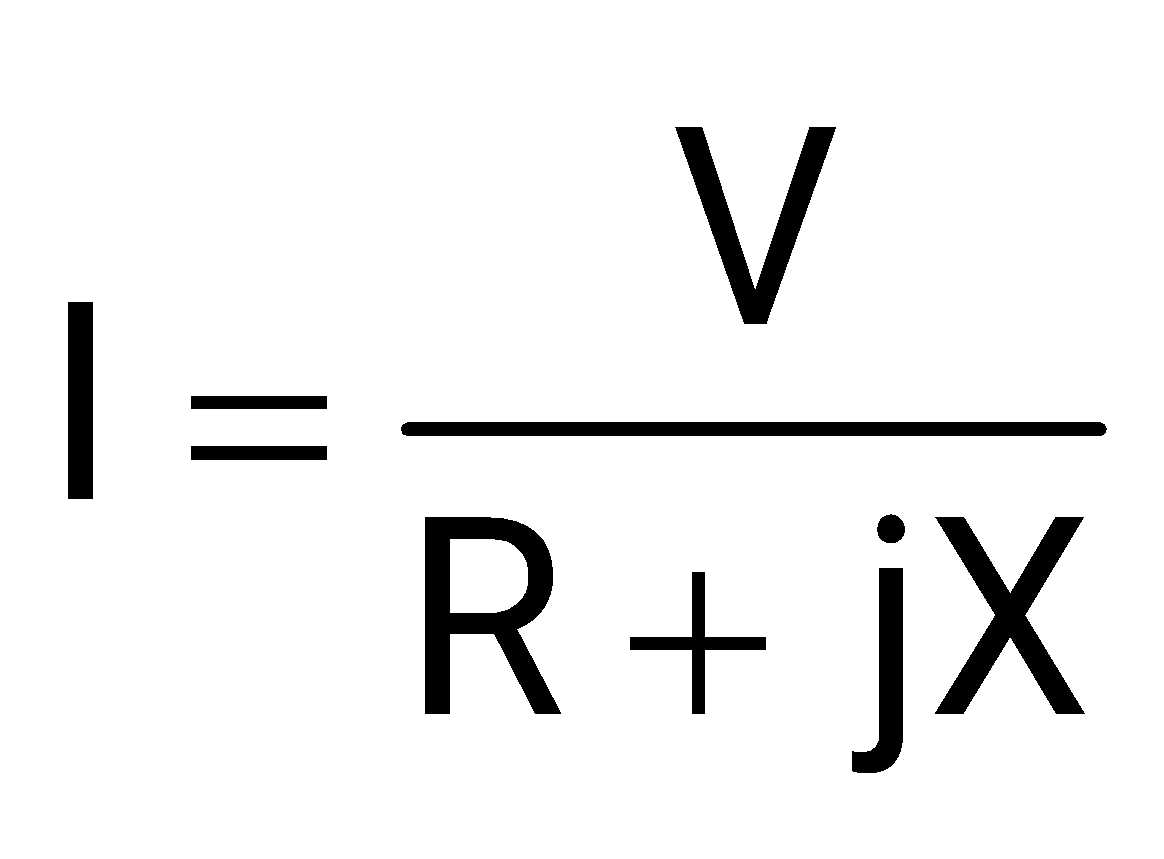

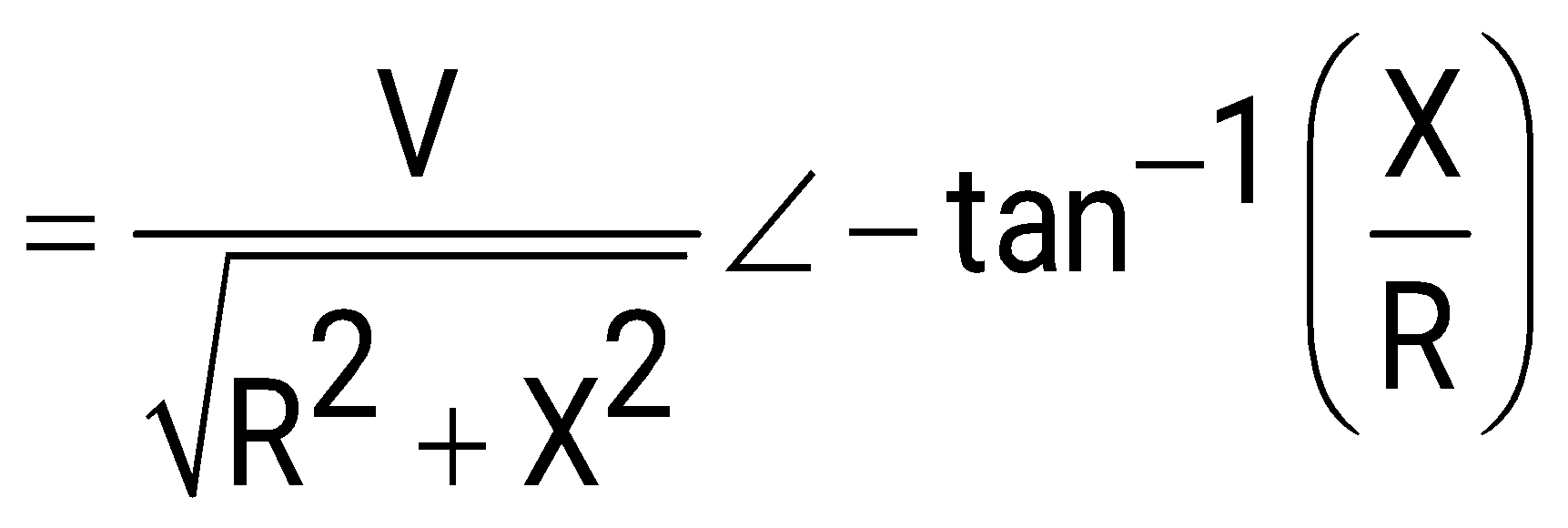

A sinusoidal source of voltage V and frequency f is connected to a series circuit of variable resistance, R and a fixed reactance, X. the locus of the tip of the current-phasor I, as R is varied from 0 to ∞ is:

Current

Since ‘X’ is fixed and ‘R’ is variable

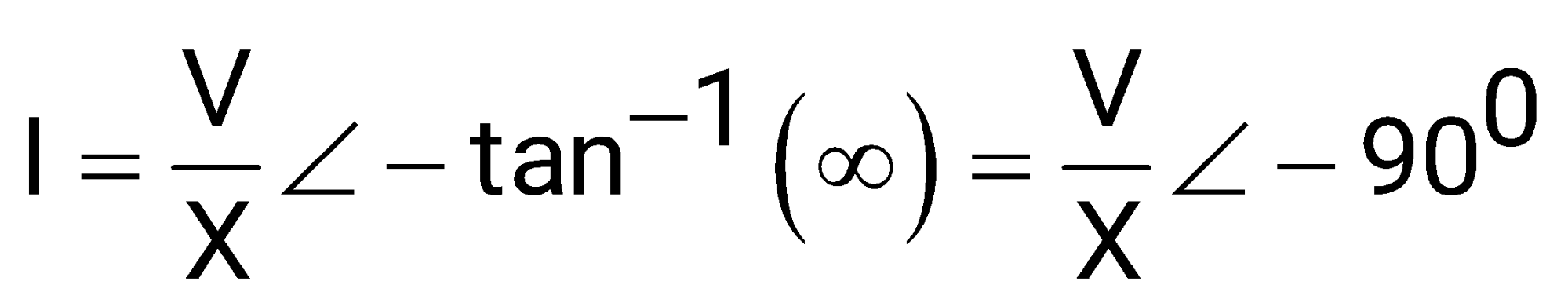

When R = 0;

When R = X;

When ;

So the locus of I will ok like as shown below

So the locus of I is a semicircle with diameter

Note: In such type of questions, the process followed is similar to drawing Polar Plot in Control Systems.

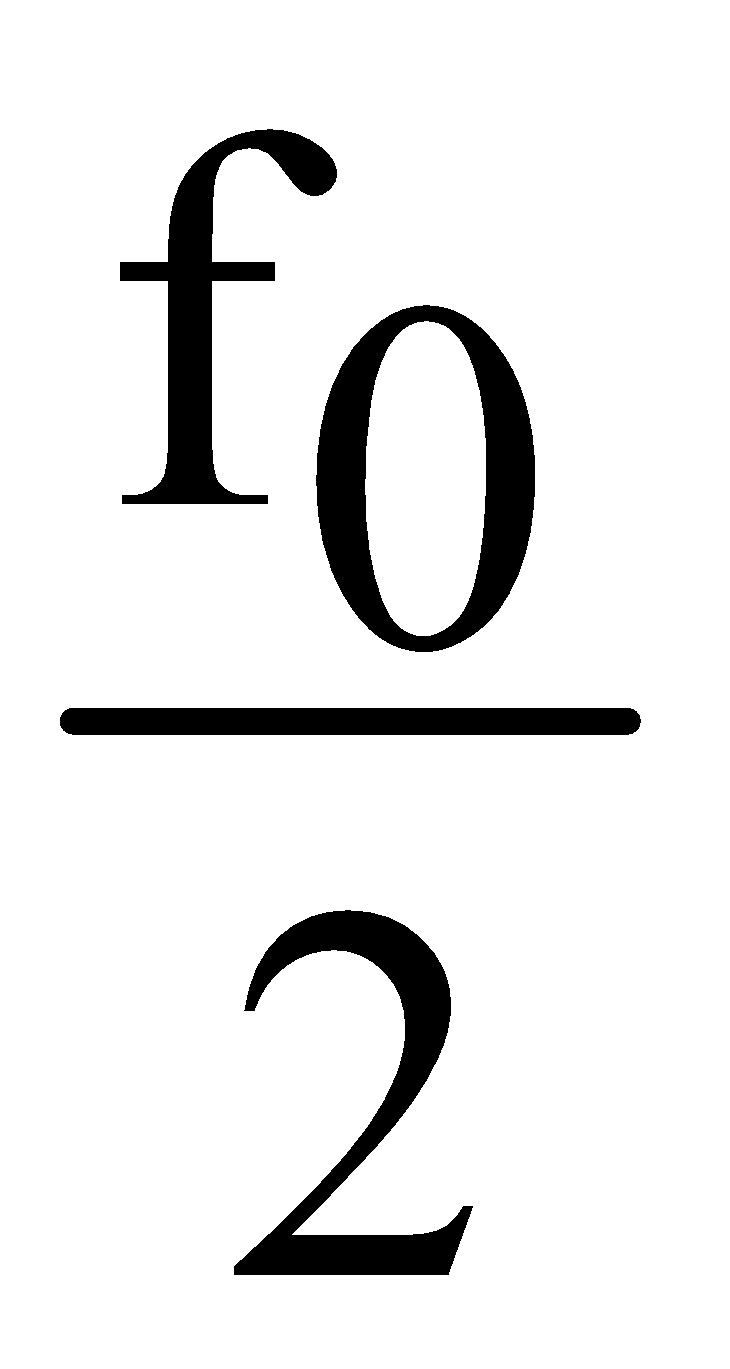

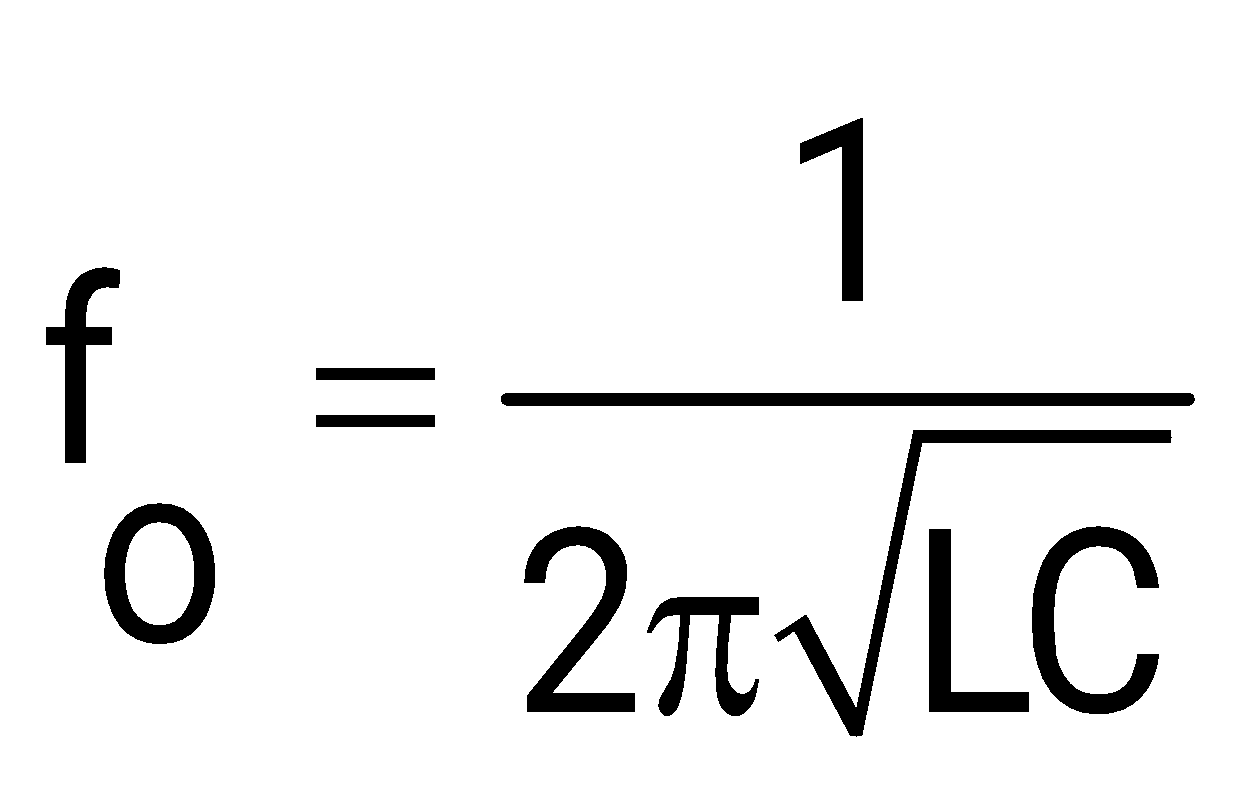

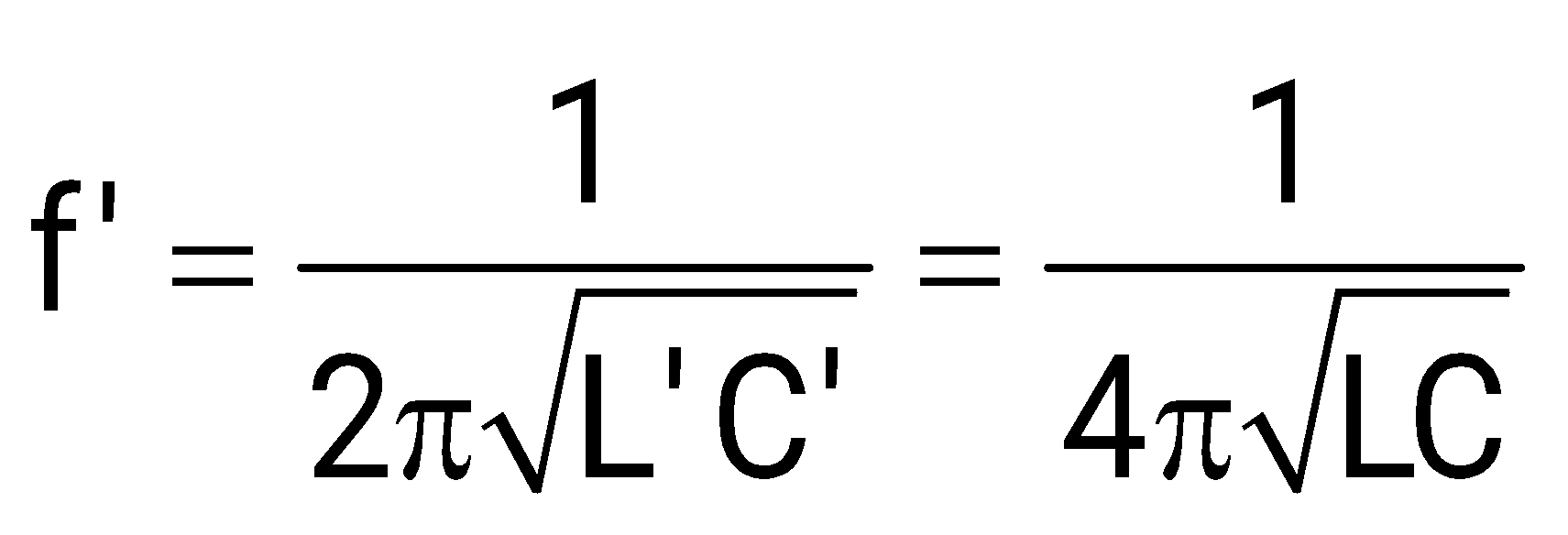

A circuit with a resistor, inductor and capacitor in series is resonant of If all the component values are now doubled, the new resonant frequency is:

Let initially resistance, capacitance & inductance is R, C & L respectively and resonant frequency is .

Now, new resistance, capacitance & inductance

R’ = 2R

C’ = 2C

L’ = 2L

New resonant frequency

Hence,

So, resonance frequency is halved.

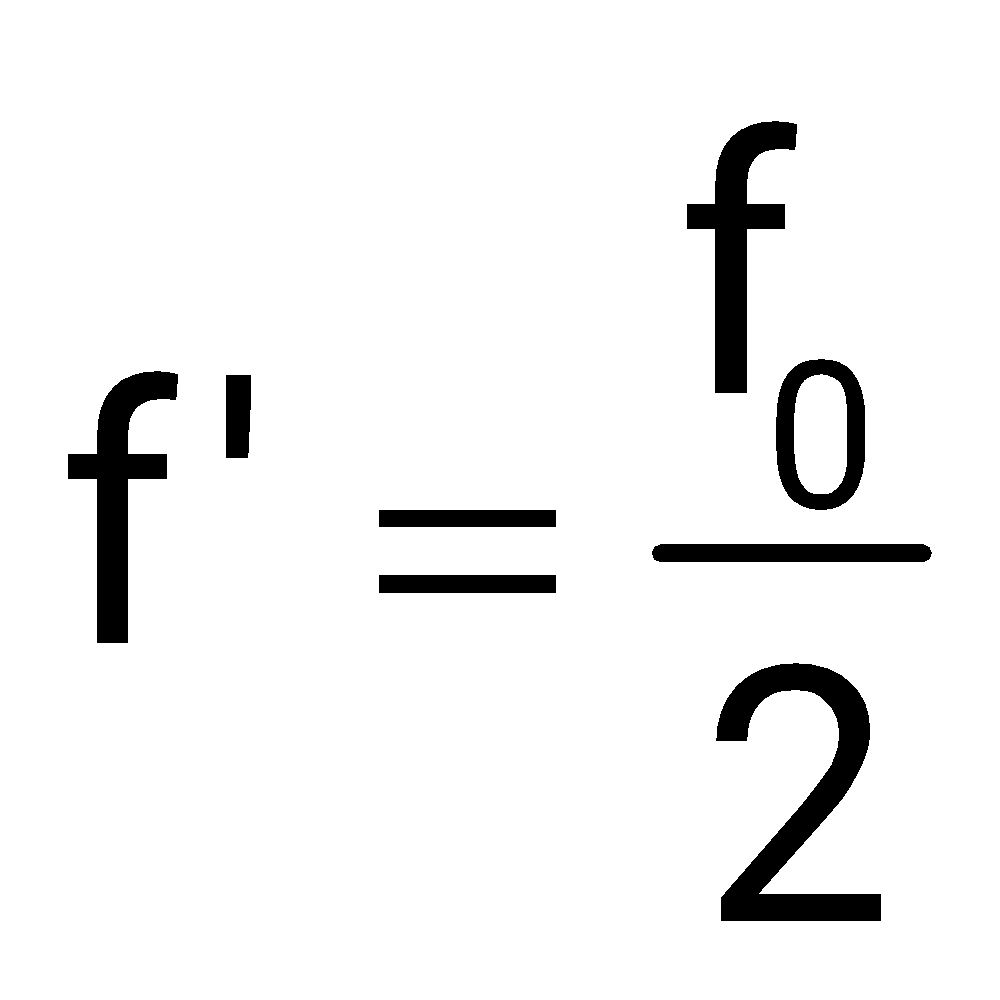

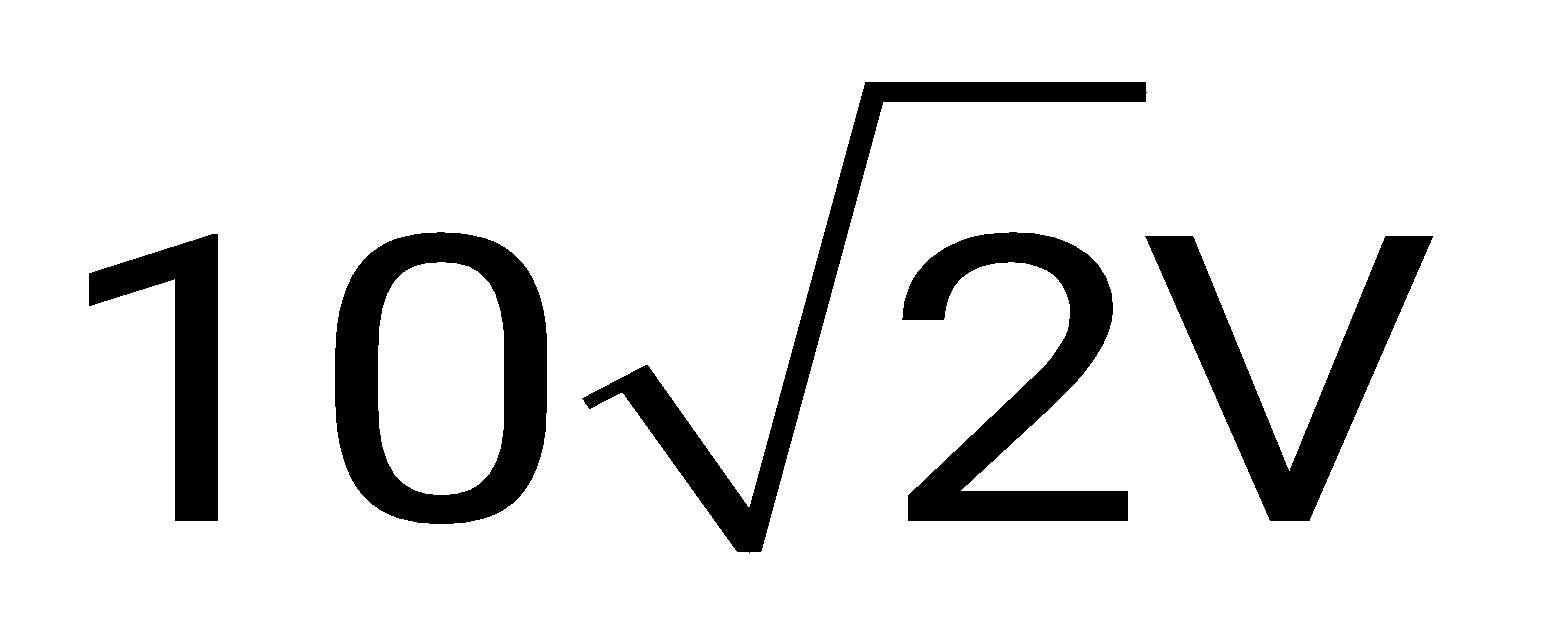

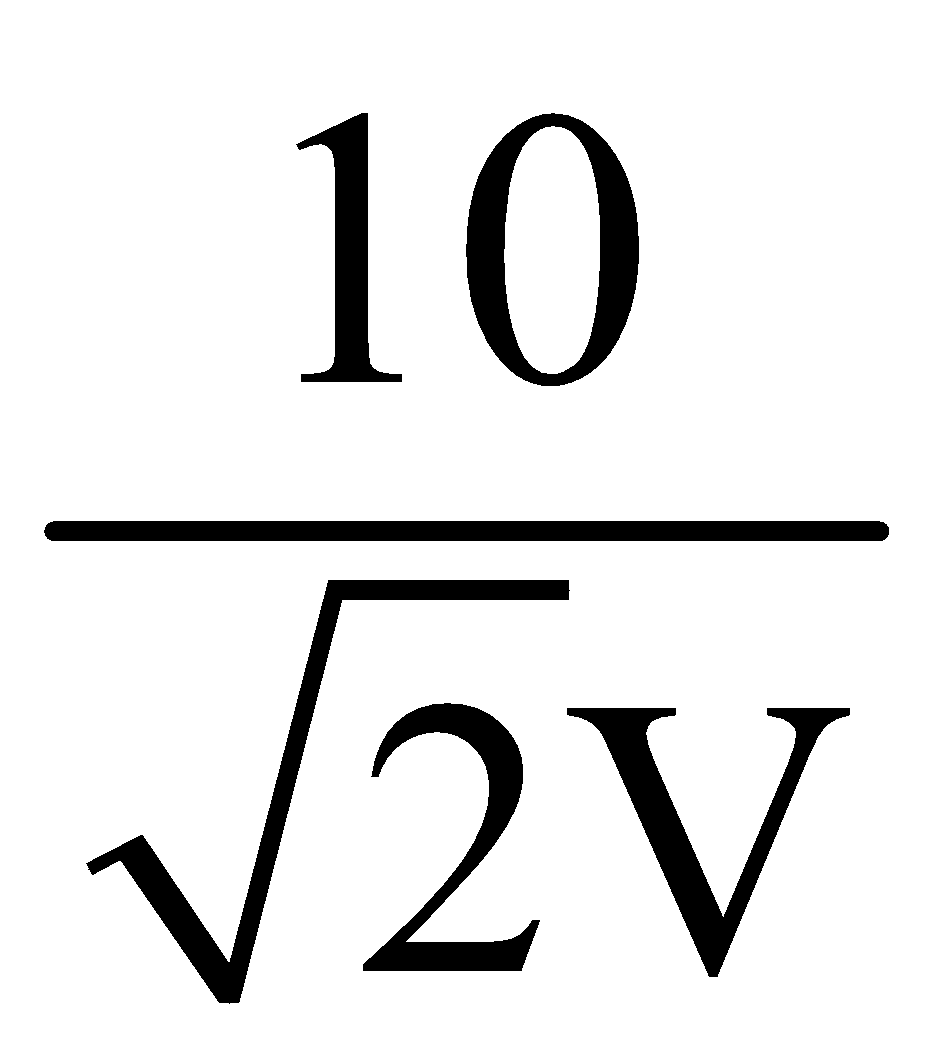

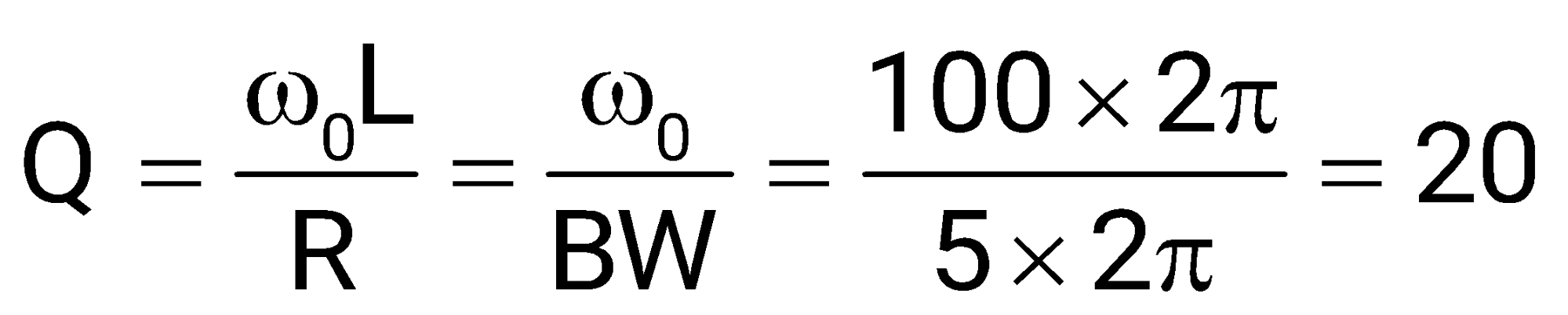

A series R-L-C circuit when excited by a 10V sinusoidal voltage source of variable frequency, exhibits resonance at 100Hz and has a 3 dB bandwidth of 5Hz. The voltage across the inductor L at resonance is:

Quality Factor,

Voltage across inductor at resonance= 20 x 10= 200Volt

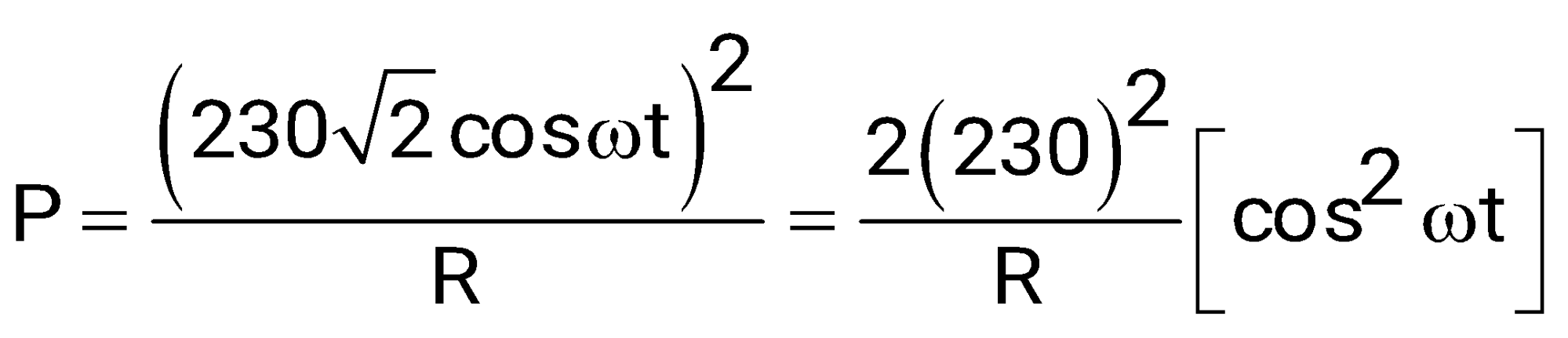

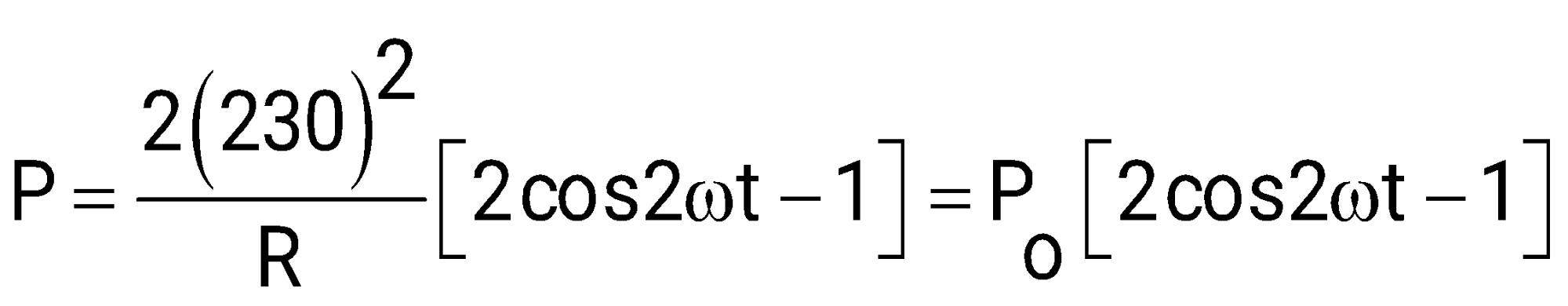

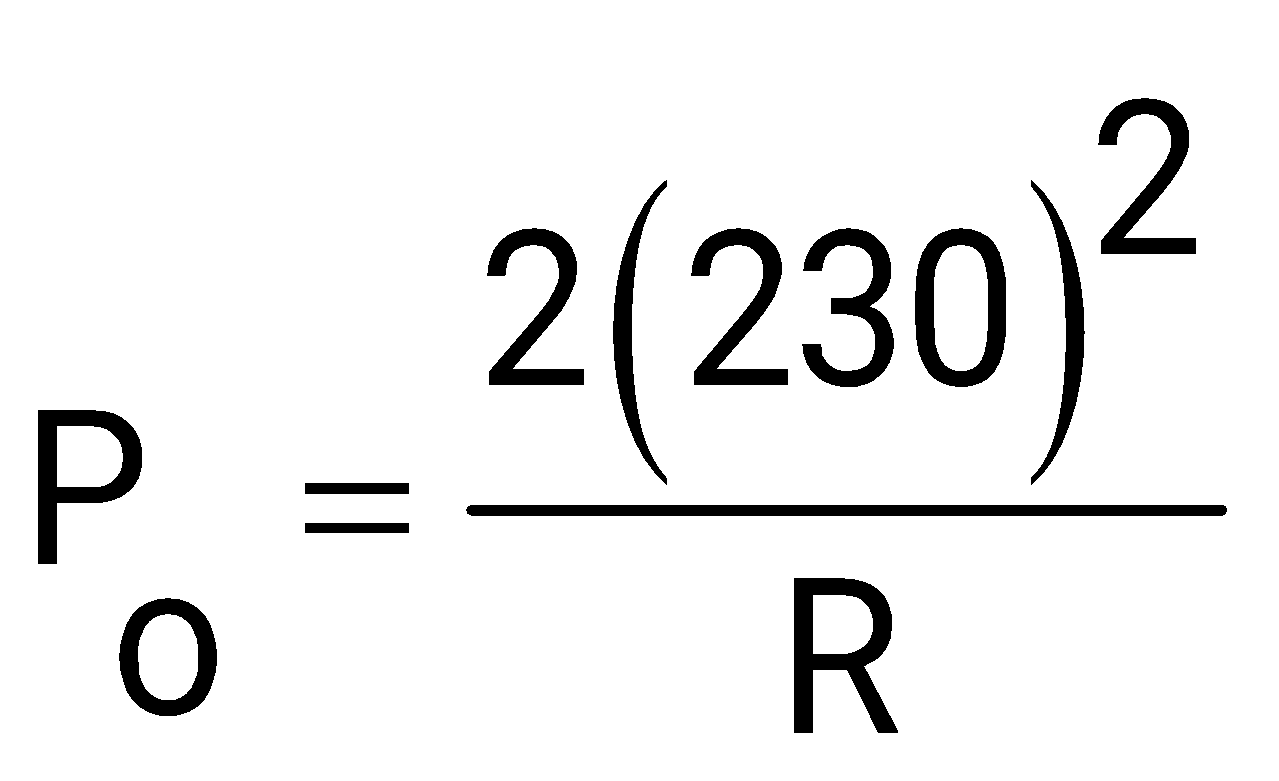

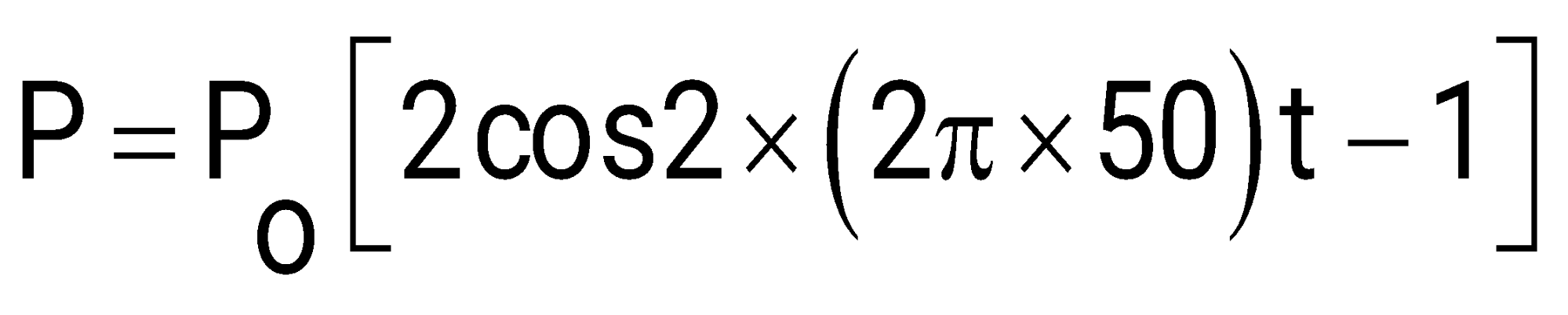

A water boiler at home is switched on the a.c. mains supplying power at 230V/50Hz. The frequency of instantaneous power consumed by the boiler is

Power consumed by boiler =

where V = voltage across boiler =

Here,

Note that 230V is rms value of the supply voltage

R = resistance of Boiler circuit coil

Where

Hence frequency of P is 100Hz

Note: The instantaneous power in a single phase AC Circuit oscillates at twice the supply frequency.

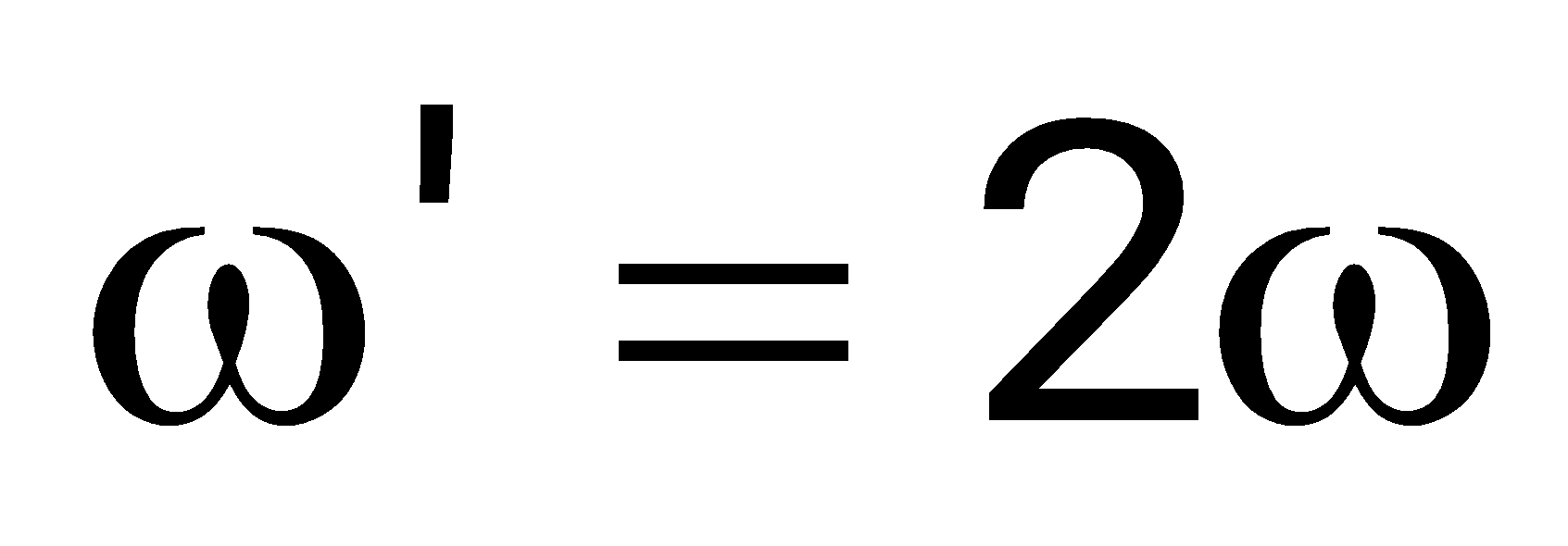

A coil (which can be modeled as a series RL circuit) has been designed for high-Q performance at a rated voltage and a specified frequency. If the frequency of operation is doubled, and the coil is operated at the same rated voltage, then the Q-factor and the active power P consumed by the coil will be affected as follows

Since Q- factor of series RL circuit =

When frequency is doubted,

Hence, Q is doubled.

Active power,

Current in a RL Series Circuit is given by,

Since, ,

Since coil is having high quality factor. So,

So P decreased by 4 times.

A series R-L-C circuit has the following parameter values: , , .The Q factor of the circuit at resonance is __________

Since resonant frequency,

Quality factor of series RLC circuit =

In the network system shown in figure, find the current through using nodal method. The values of voltages are given in volts and the impedances are given in ohms.

The given network is,

Applying KCL at node ‘’

Current through

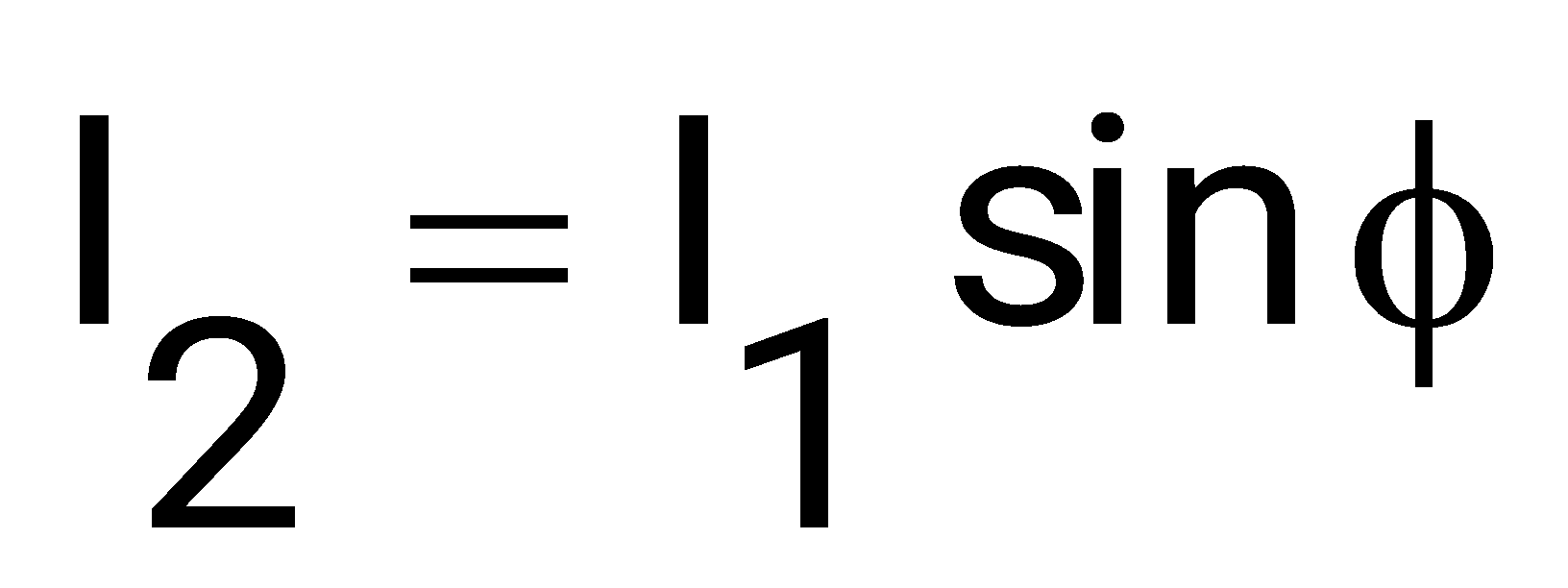

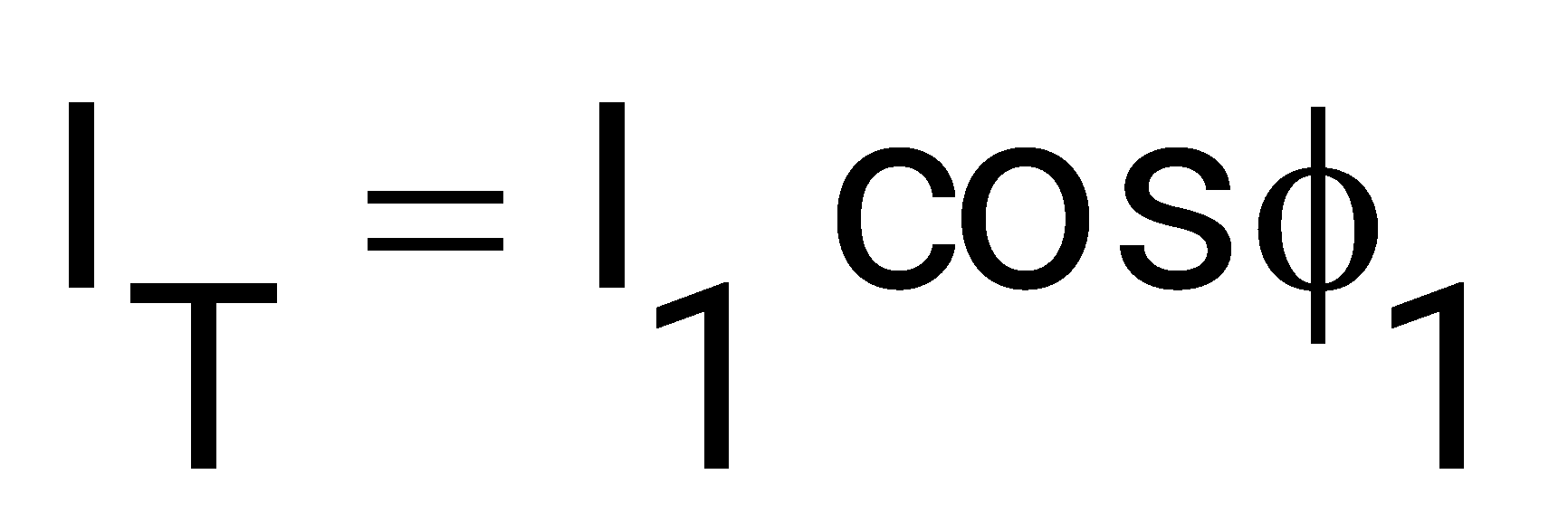

At resonance, the given parallel circuit constituted by an iron-coil and a capacitor behaves like

The phasor diagram for the given circuit is shown below,

At resonance, only in phase component of current remains so that power factor should be unity.

Hence, quadrature component of current must cancel out.

Total Current,

is the impedance angle of ‘R - L’ branch.

The current in RL branch would be,

Since

Total impedance

Since, the power factor is unity the impedance will be resistive.

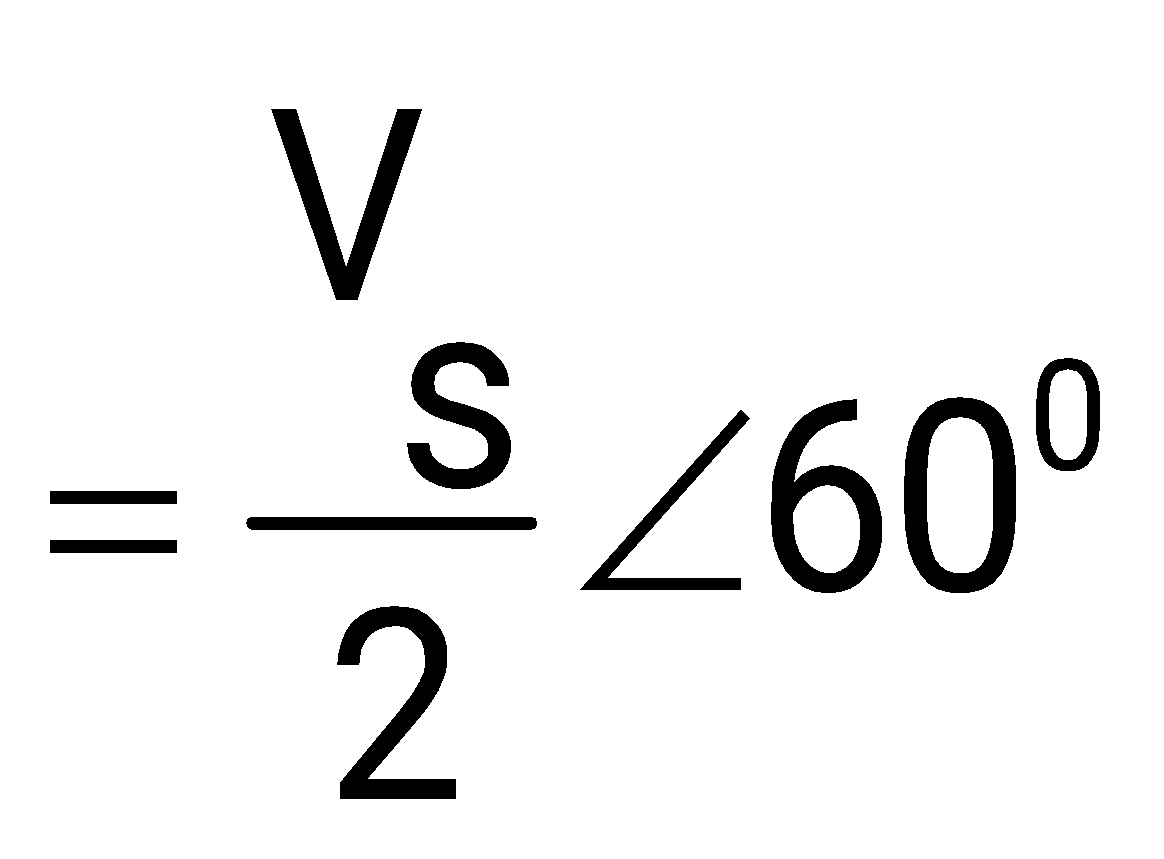

In the given circuit, the voltage , has a phase angle of _____________ with respect to .

Inductor voltage can be calculated using Potential Divider,

Hence, leads by 60°.

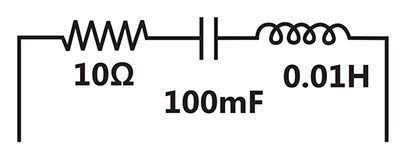

The following circuit (figure) resonates at

Impedance of circuit

For resonance, imaginary part of impedance = 0

Hence,

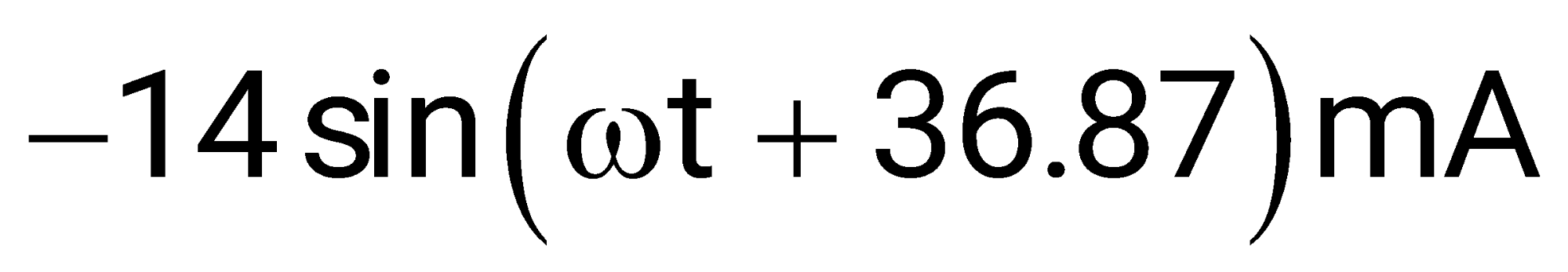

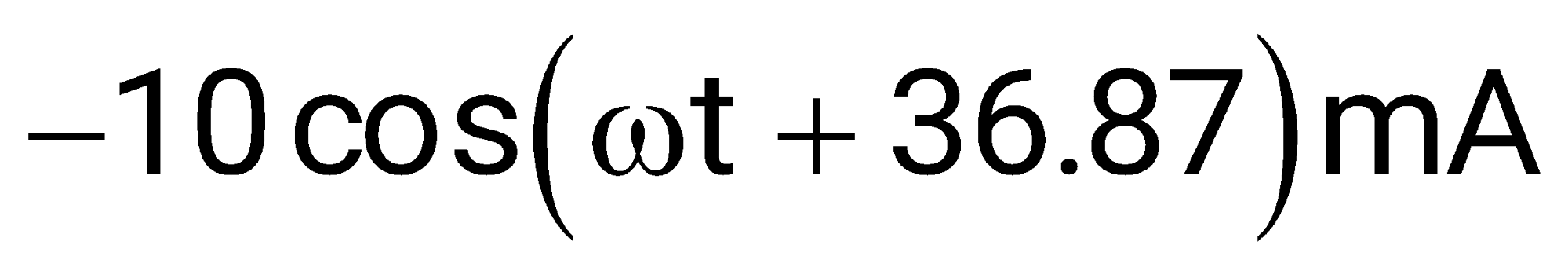

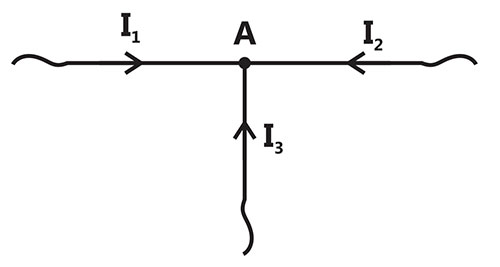

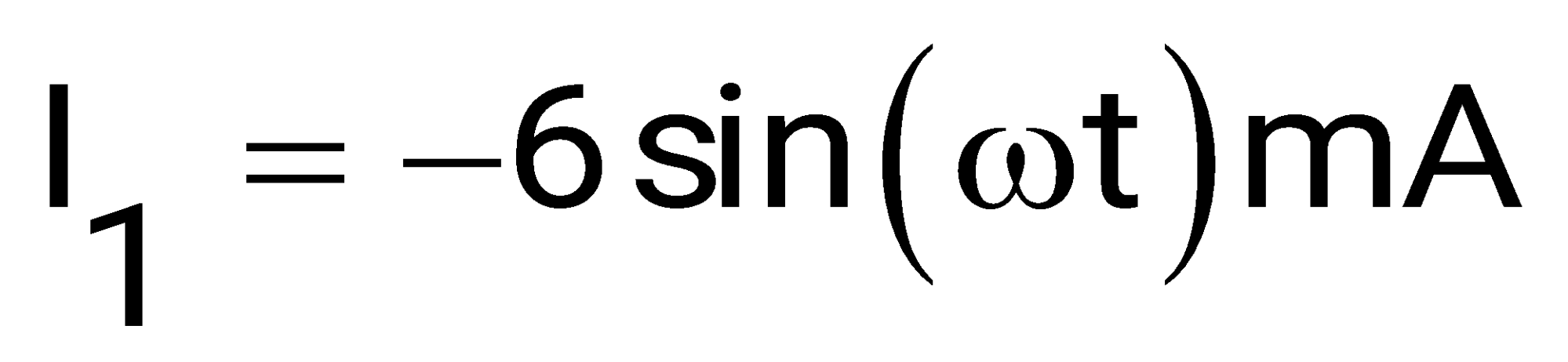

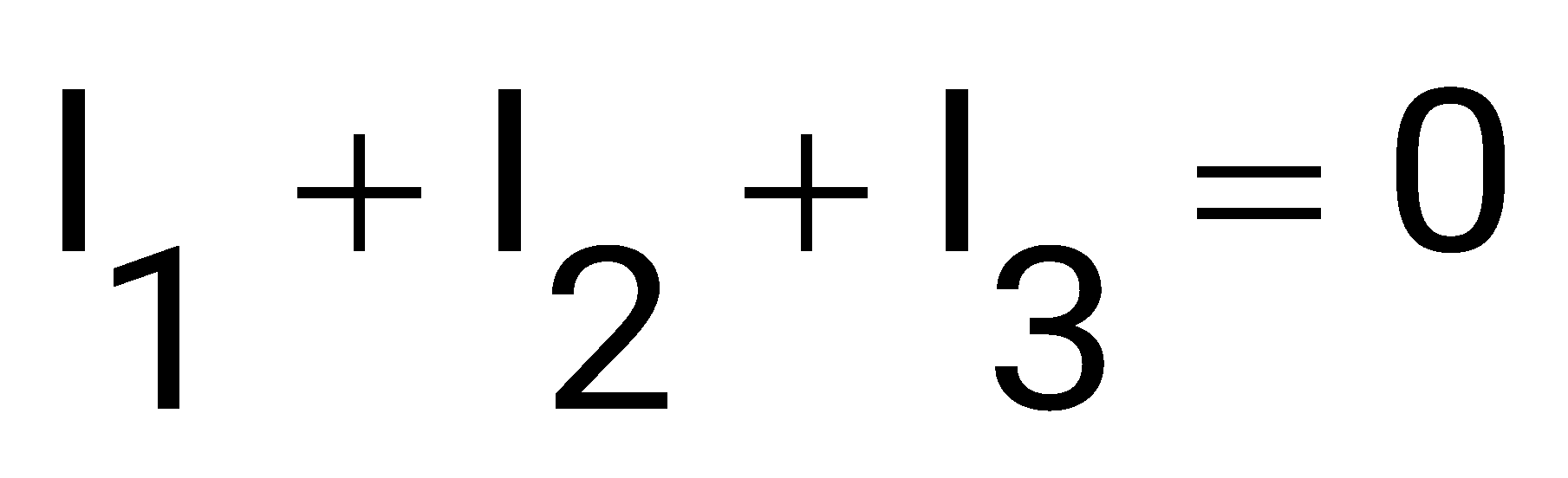

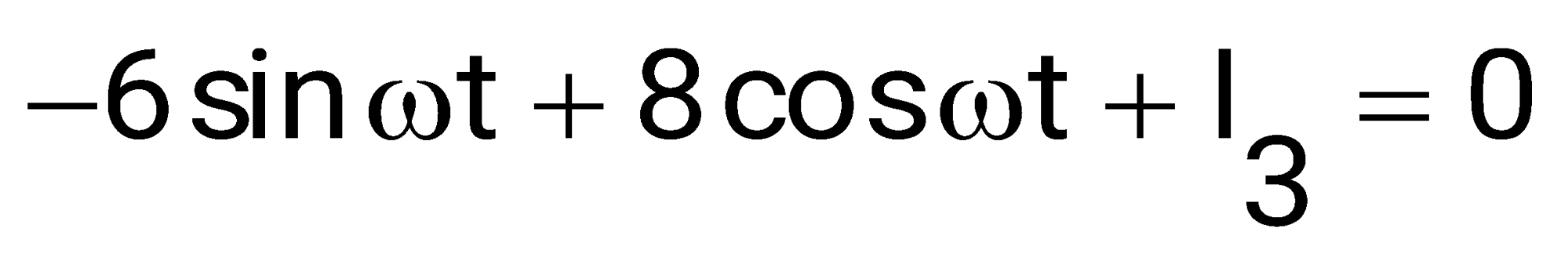

Currents , and meet at a junction (node) in a circuit. All currents are marked as entering the node.

If and , then will be

The arrangement of three currents entering a node is shown in the figure,

Using KCL at node ‘A’

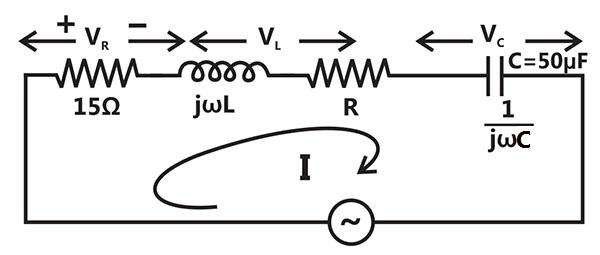

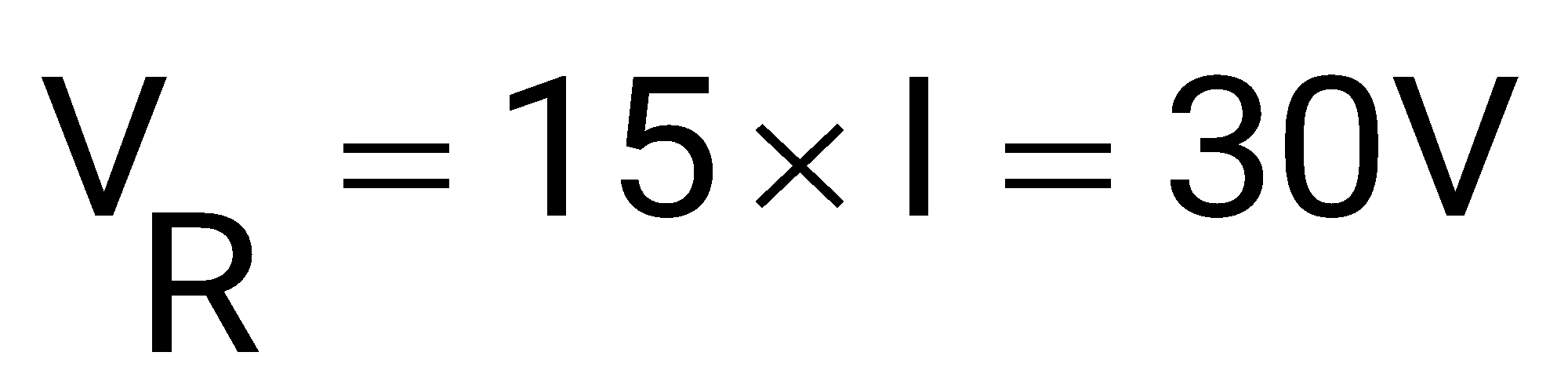

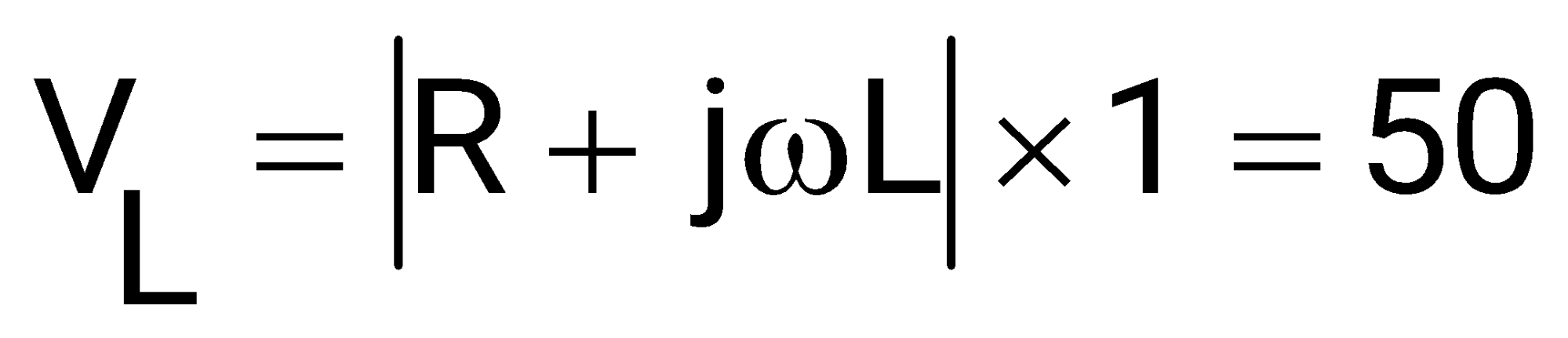

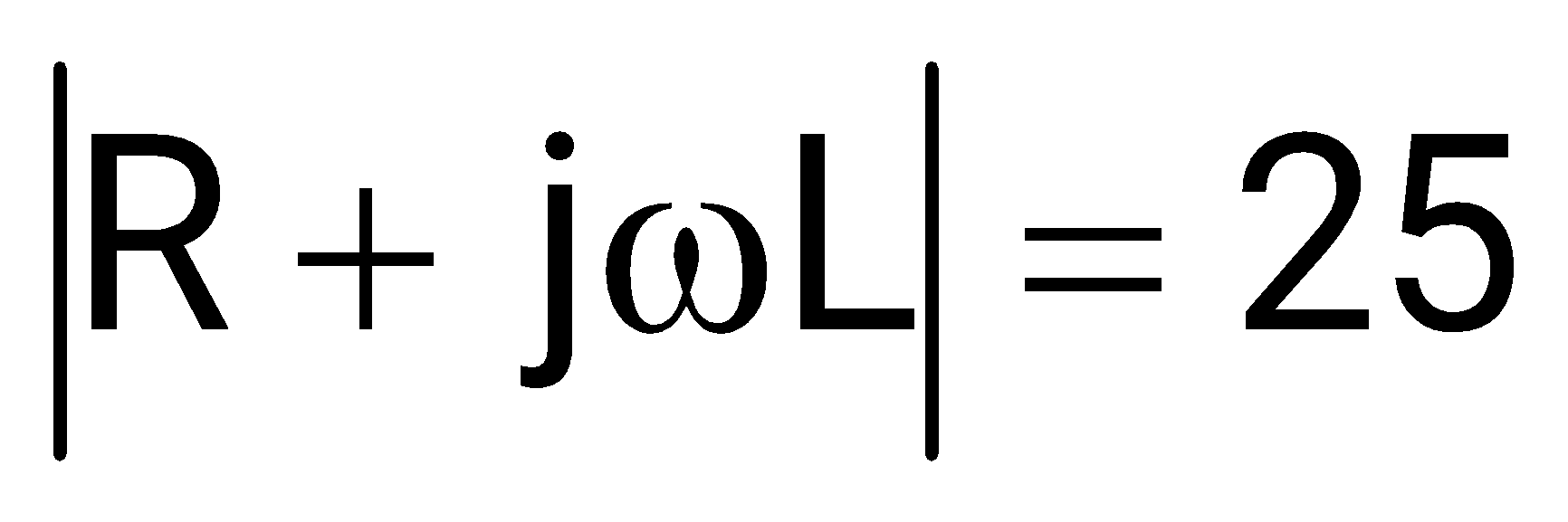

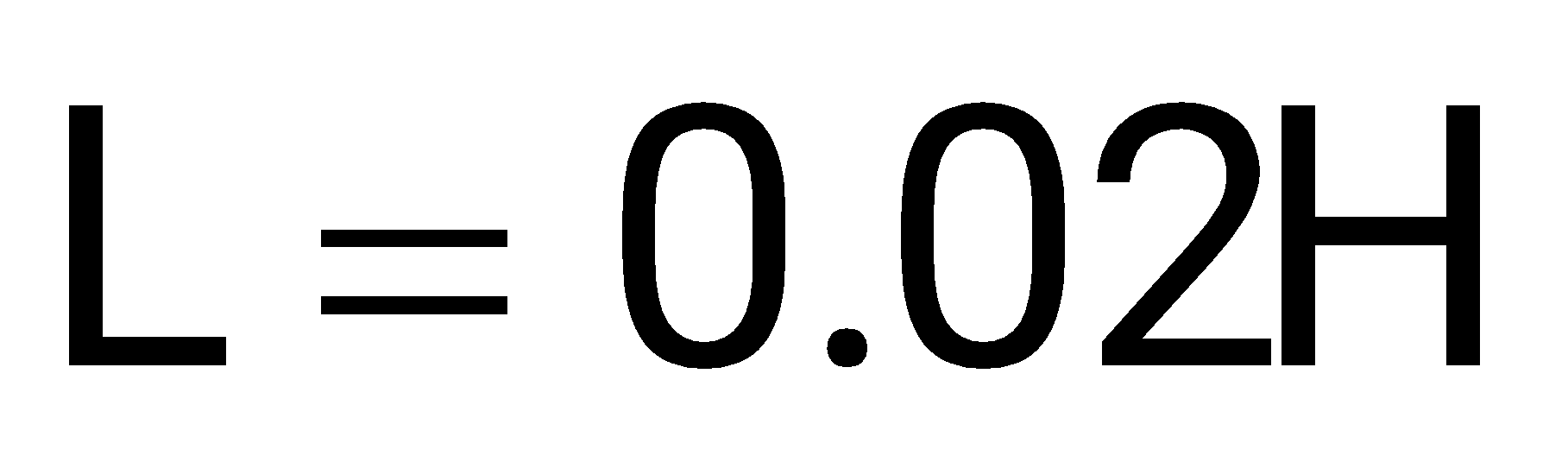

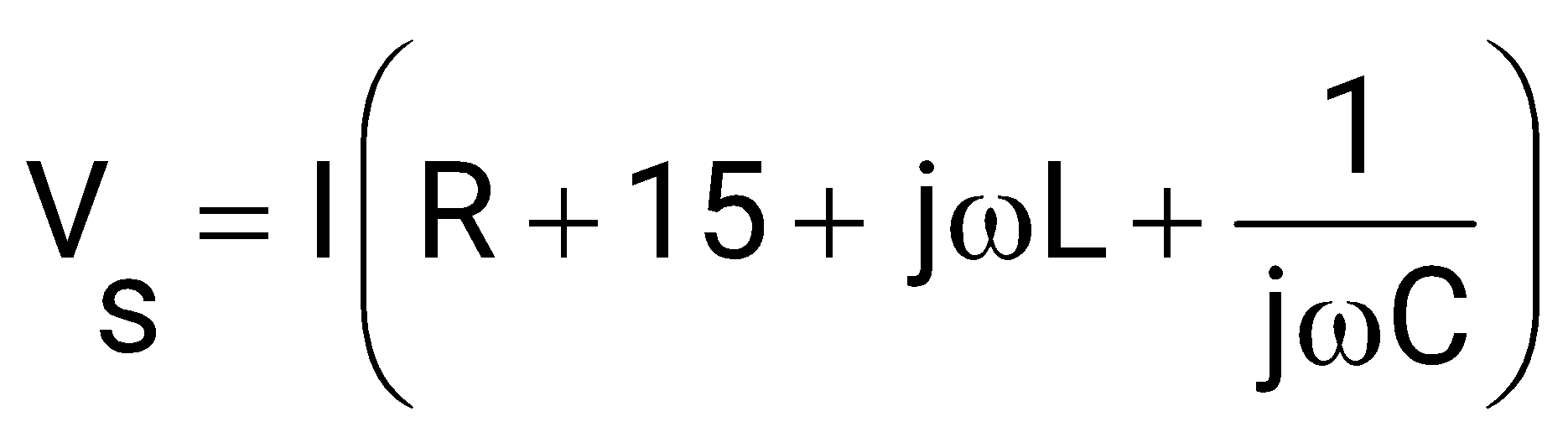

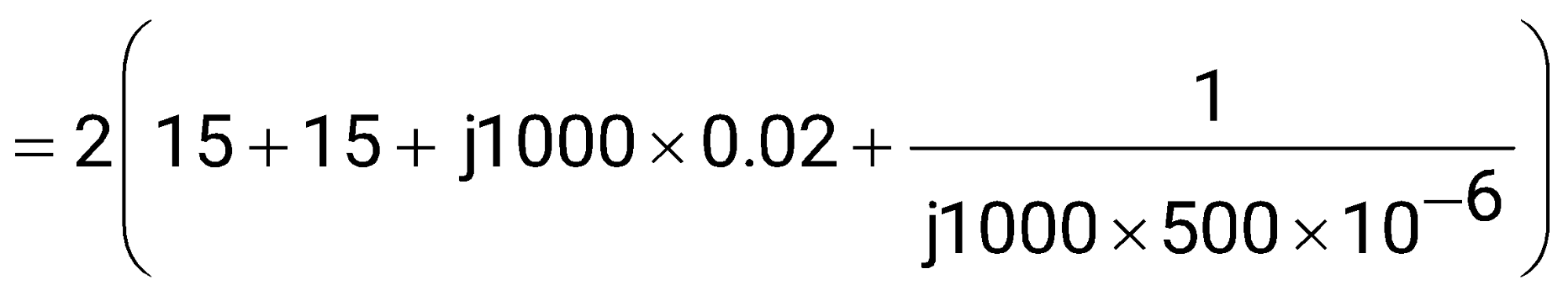

A constant voltage frequency sinusoidal voltage source of magnitude is connected to a series circuit made of a resistance of 15Ω, a coil of winding resistance R and inductance L and a 50μF capacitor. The voltage across the 15Ω resistors is 30V, across the coil is 50V, across the capacitor is 40V, The voltage across the combination of the 15Ω resistor and the coil together is 72.11V. Determine the values of the inductance L, winding resistance R and the source voltage V.

The circuit configuration for the data given is shown below,

--------------(1)

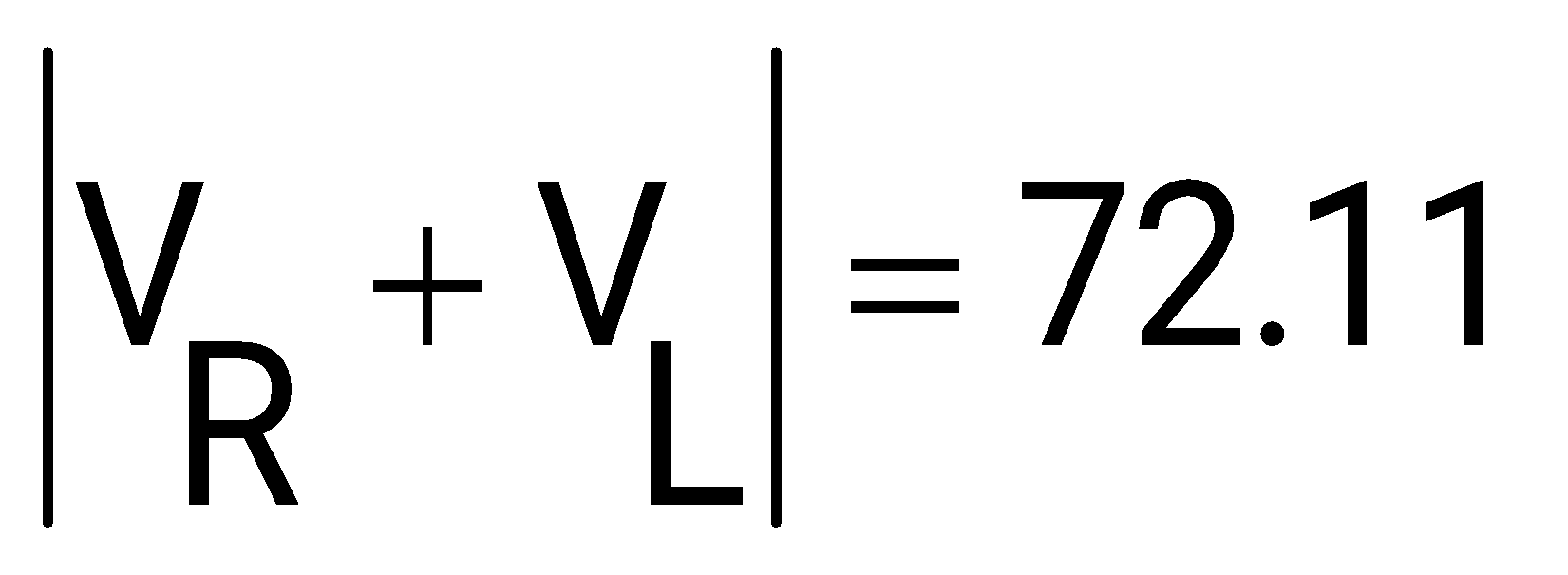

--------------(2)

The voltage across resistance R and 15Ω is in phase and voltage in Inductor is 90° leading with respect to resistor voltage.

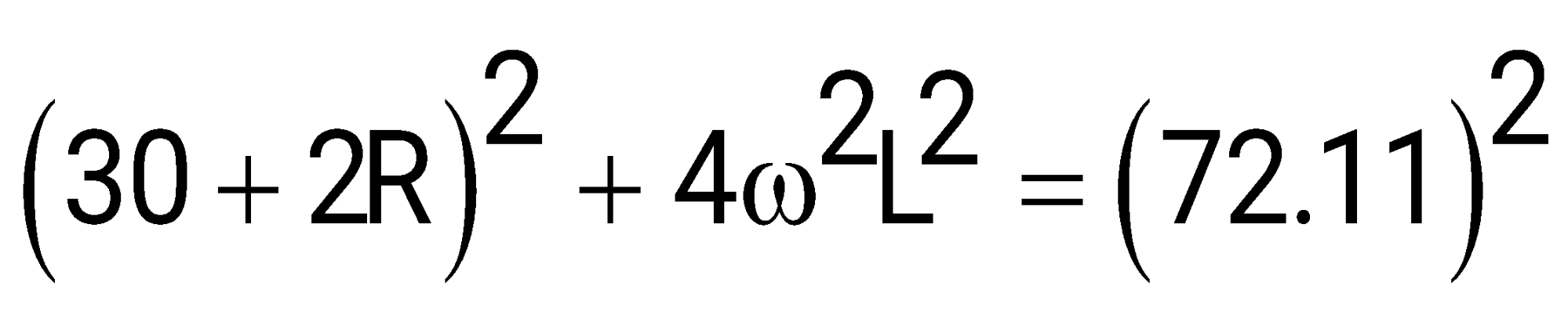

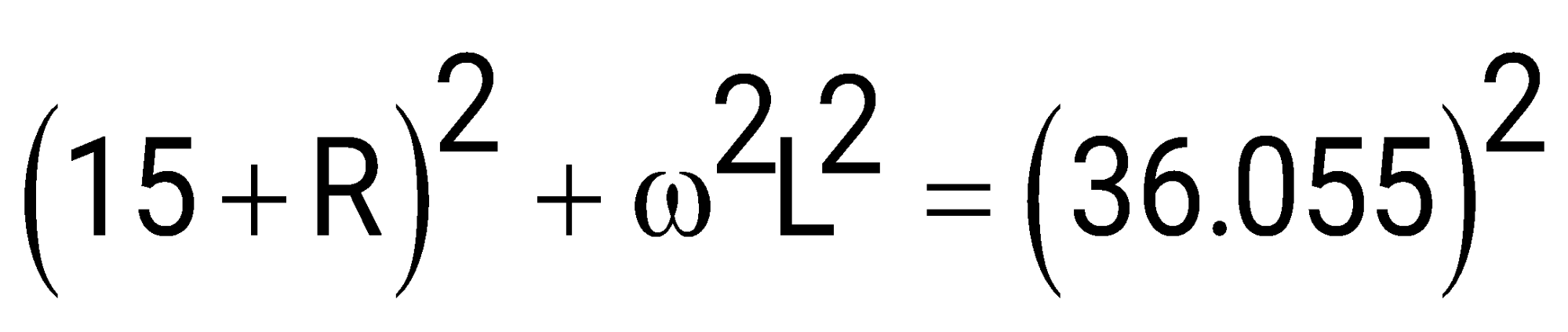

From equation 2

Since,

Put the value of ‘R’ & ‘ω’ in equation 2

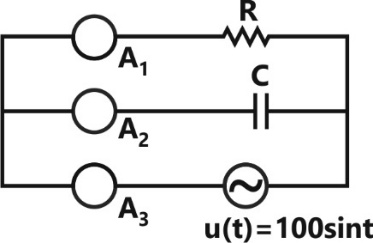

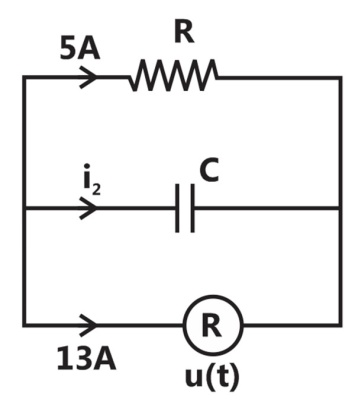

In the figure shown, are ideal ammeters. If read 5 and 13A respectively, reading of will be

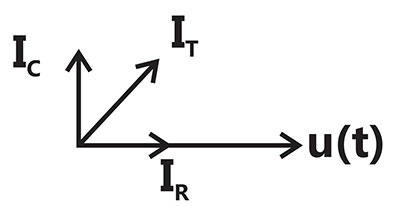

The phasor diagram for parallel RC circuit is shown below,

& are in phase

Hence, reading of 2nd ammeter,

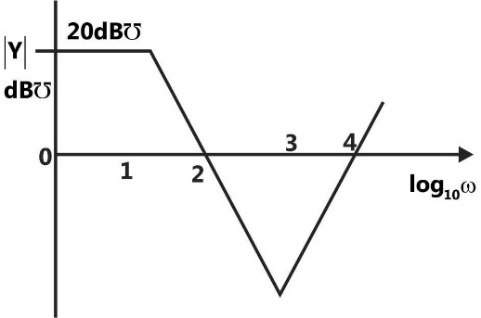

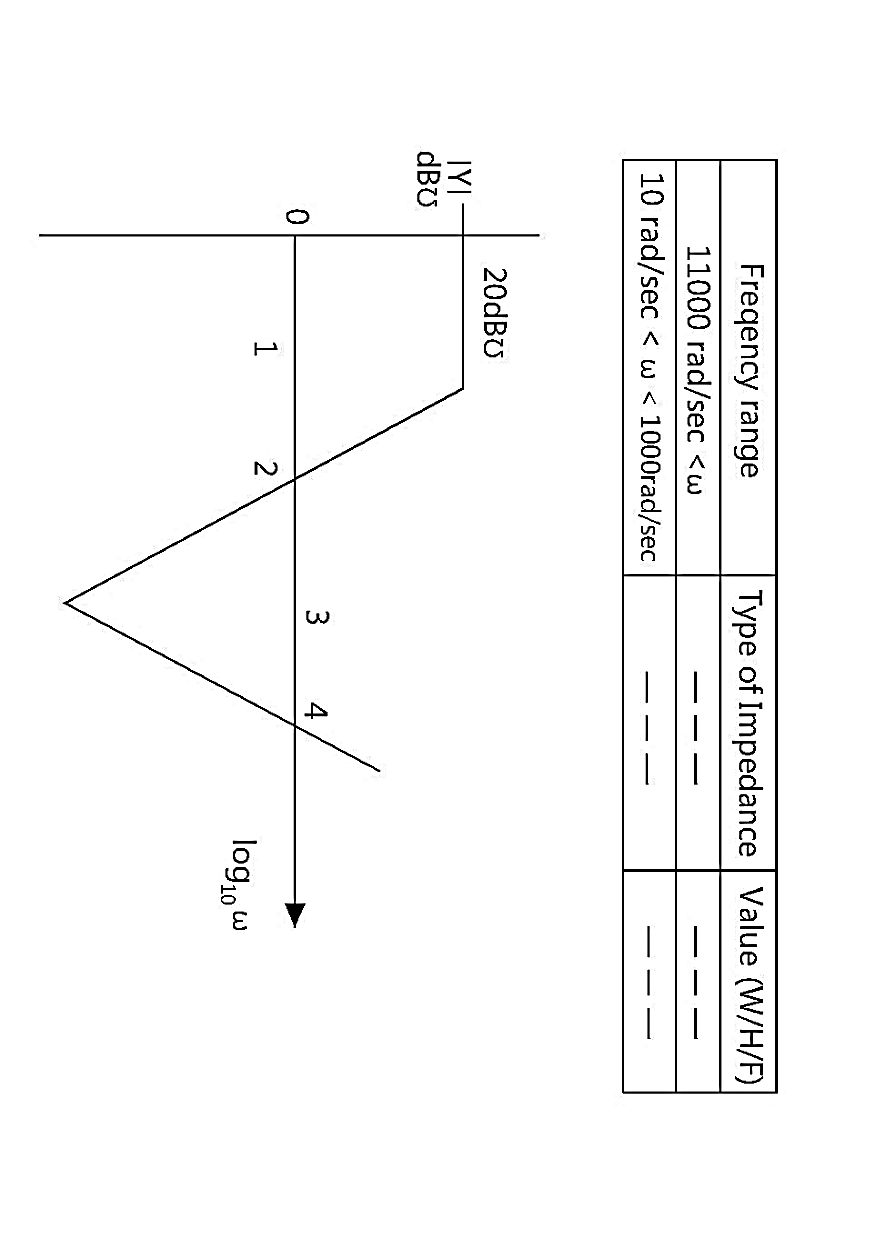

A one port active network has an input admittance Y, the magnitude of which is shown in figure as a function of frequency. The circuit is resistive or capacitive in different frequency ranges.

Complete the following table:

Frequency Range | Type of Impedance | Value (Ω/H/F) |

10000 rad/sec < ω | A | P |

10 rad/sec < ω < 1000 rad/sec | B | Q |

The plot of admittance Vs frequency is shown below,

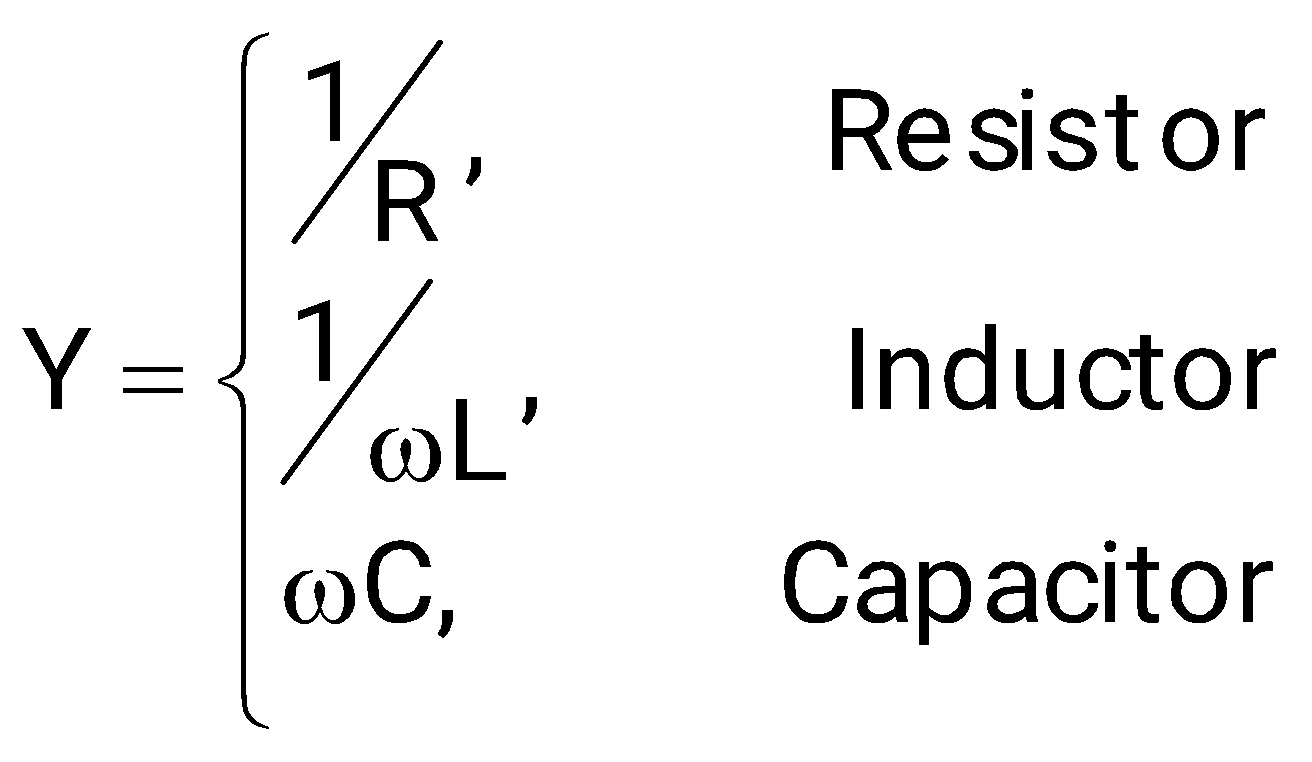

The admittance of various circuit elements is,

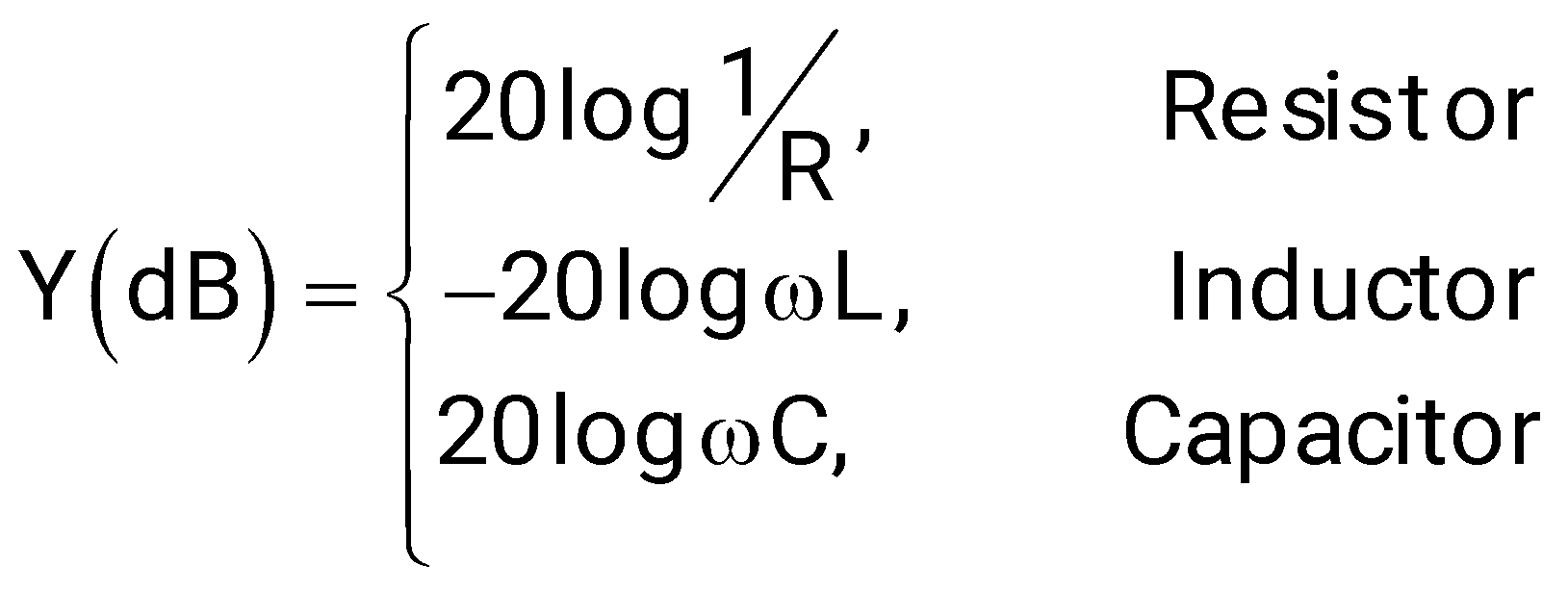

In dB the admittance is given by,

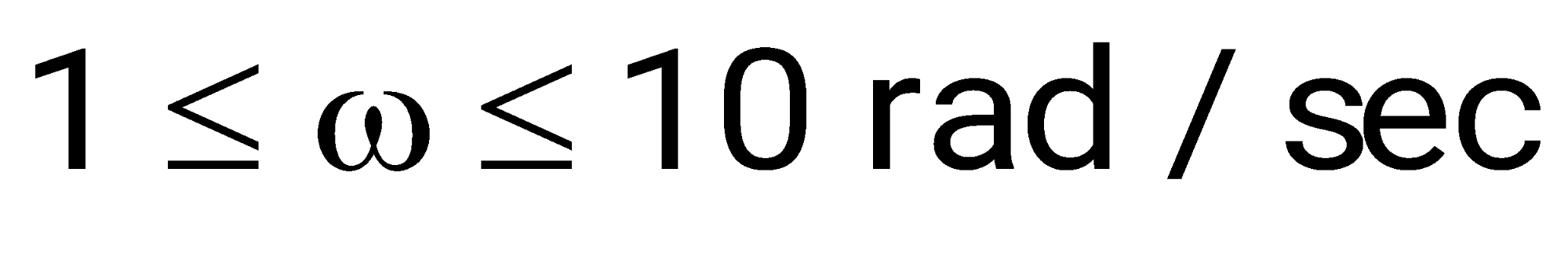

As the magnitude of admittance is constant between, the impedance would be resistive.

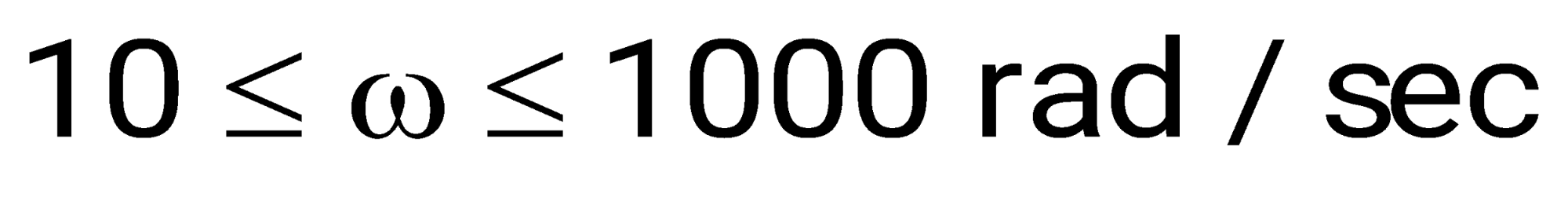

The admittance has a negative slope between, the impedance is inductive and its value at is 20dB

L = 0.01 H

The admittance has a positive slope between, the impedance is capacitive and its value at is 0dB

C = 100μF

In figure calculate

(a) The power delivered by each source

(b) The power dissipated in each resistor

(a) -j4.33, 7.5 +j4.33 (b) 4.5, 3)

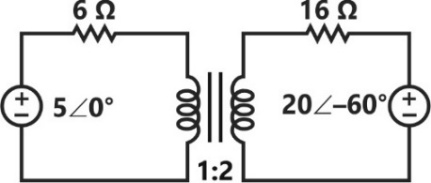

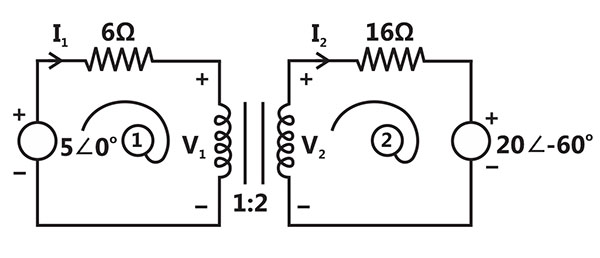

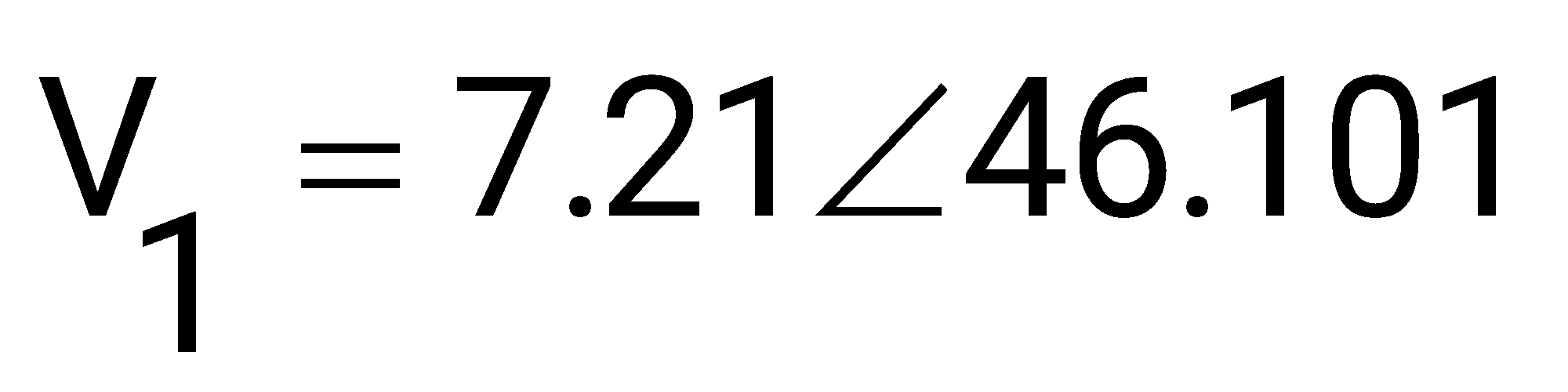

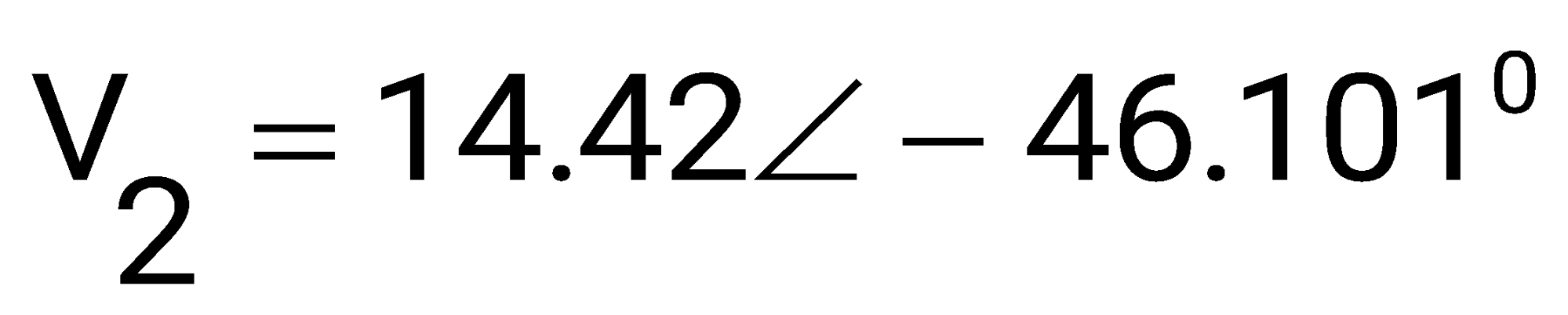

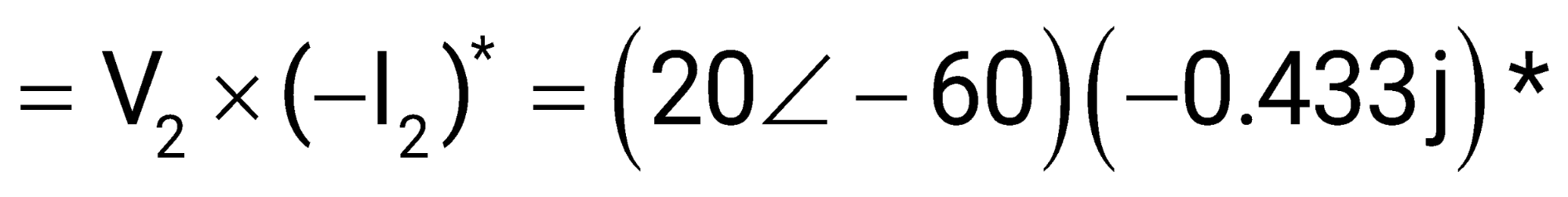

Based on Transformation Ratio,

and

Applying KVL in loop 1

………(1)

………..(2)

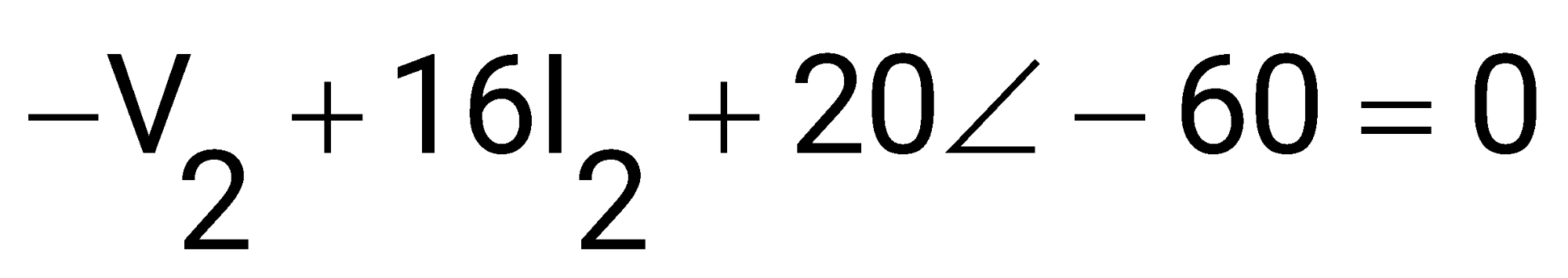

Applying KVL in Loop 2

………(3)

Substituting the values of and

………(4)

Adding equation 2 & 4

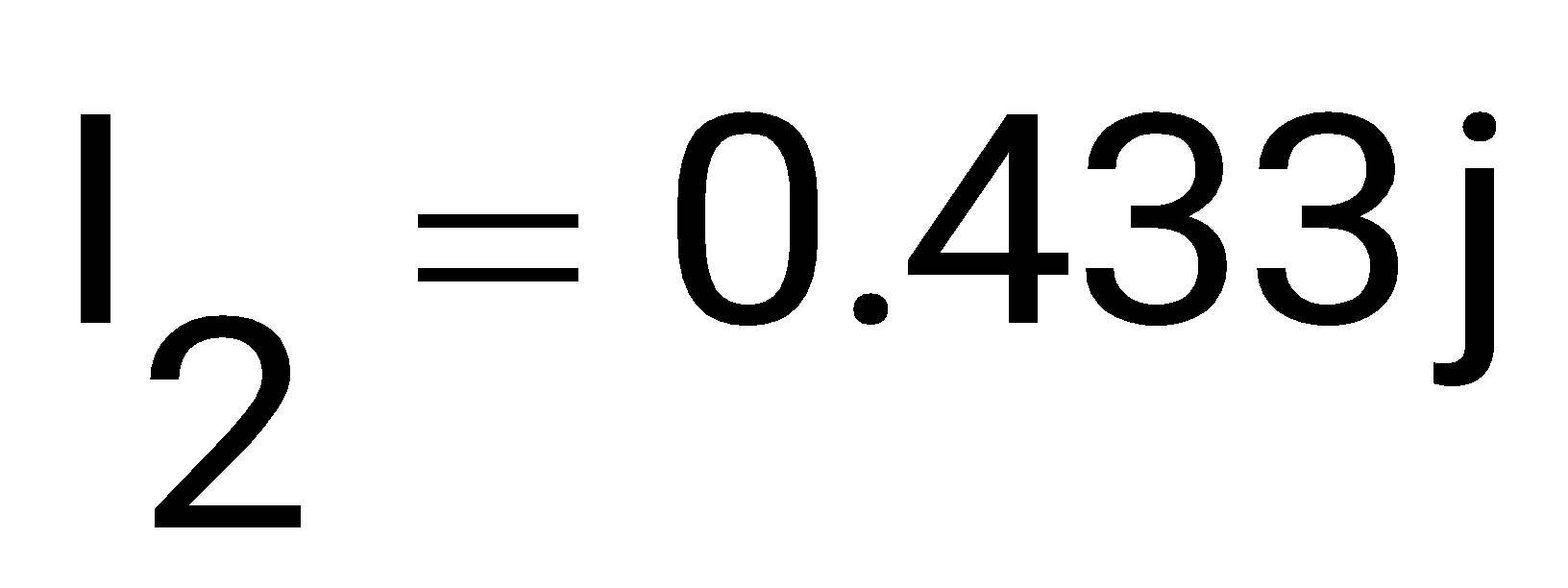

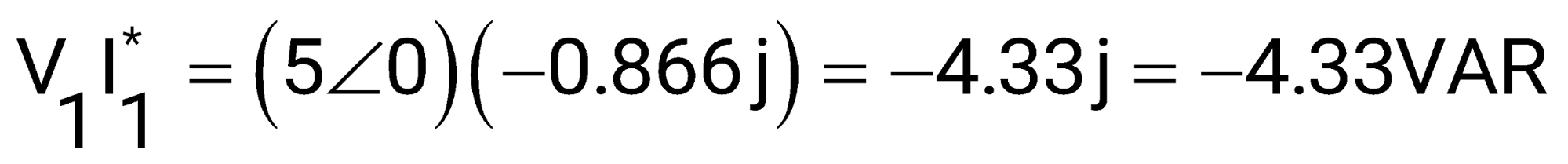

(a) Power delivered by source (1)

Power delivered by source (2)

(b) Power dissipates in 6Ω resistor = 4.5 Watt

Power dissipates in 16Ω resistor