Practice over 1000+ GATE-level questions from this topic!

Designed to match the latest GATE pattern with topic-wise precision, difficulty tagging, and detailed solutions.

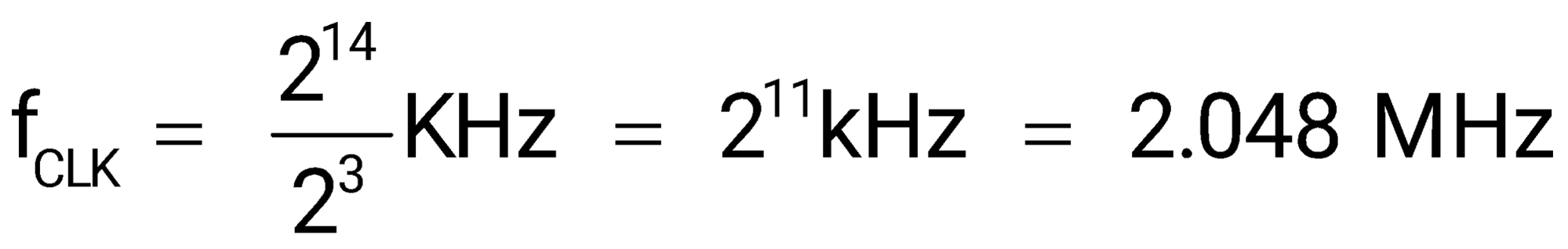

A 16-bit synchronous binary up-counter is clocked with a frequency fCLK. The two most significant bits are OR-ed together to form an output Y. Measurements show' that Y is periodic, and the duration for which Y remains high in each period is 24 ms. The clock frequency fCLK is _________ MHz. (Round off to 2 decimal places.)

The output Y will be 1 whenever any of the two MSB is 1.

Total number of clock cycles = 216

16th bit is 0 for first 215 cycles & 1 for next 215 cycle

15th bit is 0 for first 214 cycles then 1 for next 214 cycles & so on

First 214 cycles: both 0 ; Y = 0

Next 214 cycles: MSB = 0, 15th bit = 1 ; Y = 1

Next 214 cycles: MSB = 1, 15th bit = 0 ; Y = 1

Next 214 cycles: MSB = 1, 15th bit = 1 ; Y = 1

∴ Y = 1 for 3 × 214 cycles

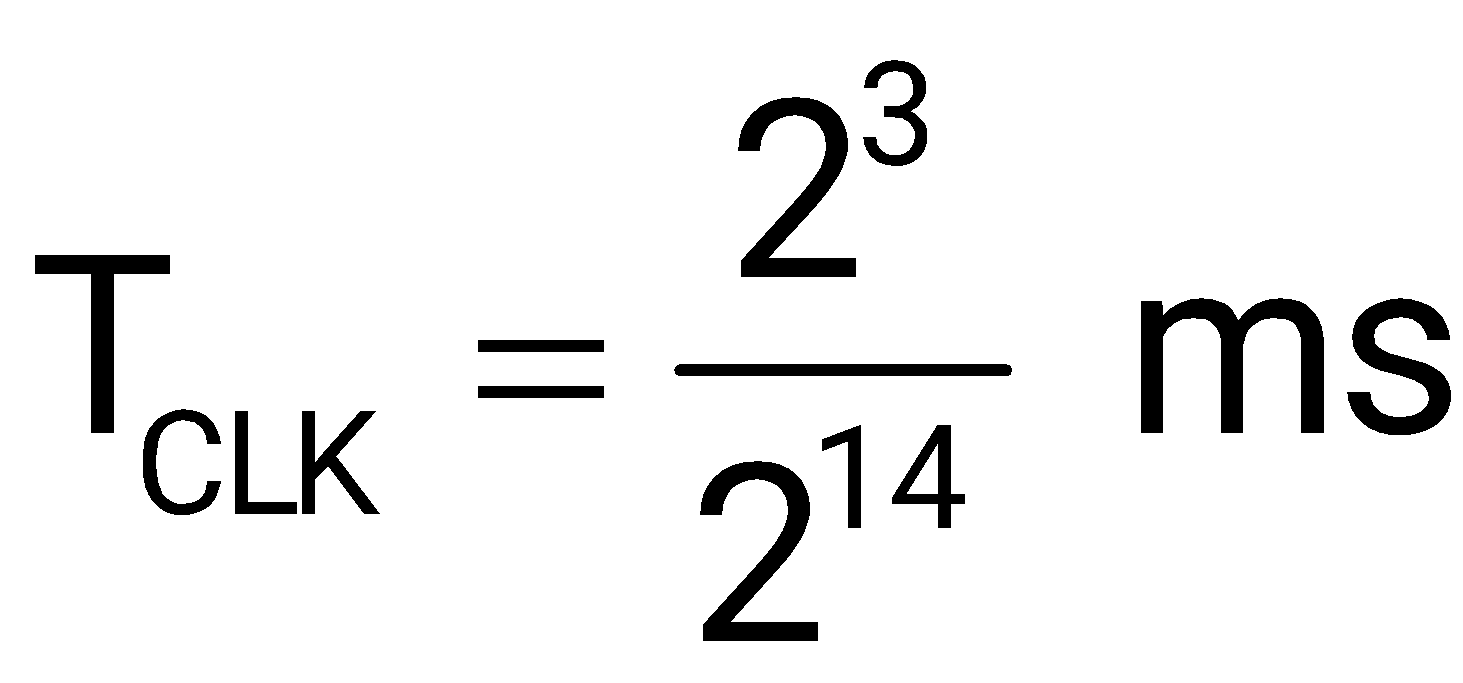

3 × 214 TCLK = 24 ms