Practice over 1000+ GATE-level questions from this topic!

Designed to match the latest GATE pattern with topic-wise precision, difficulty tagging, and detailed solutions.

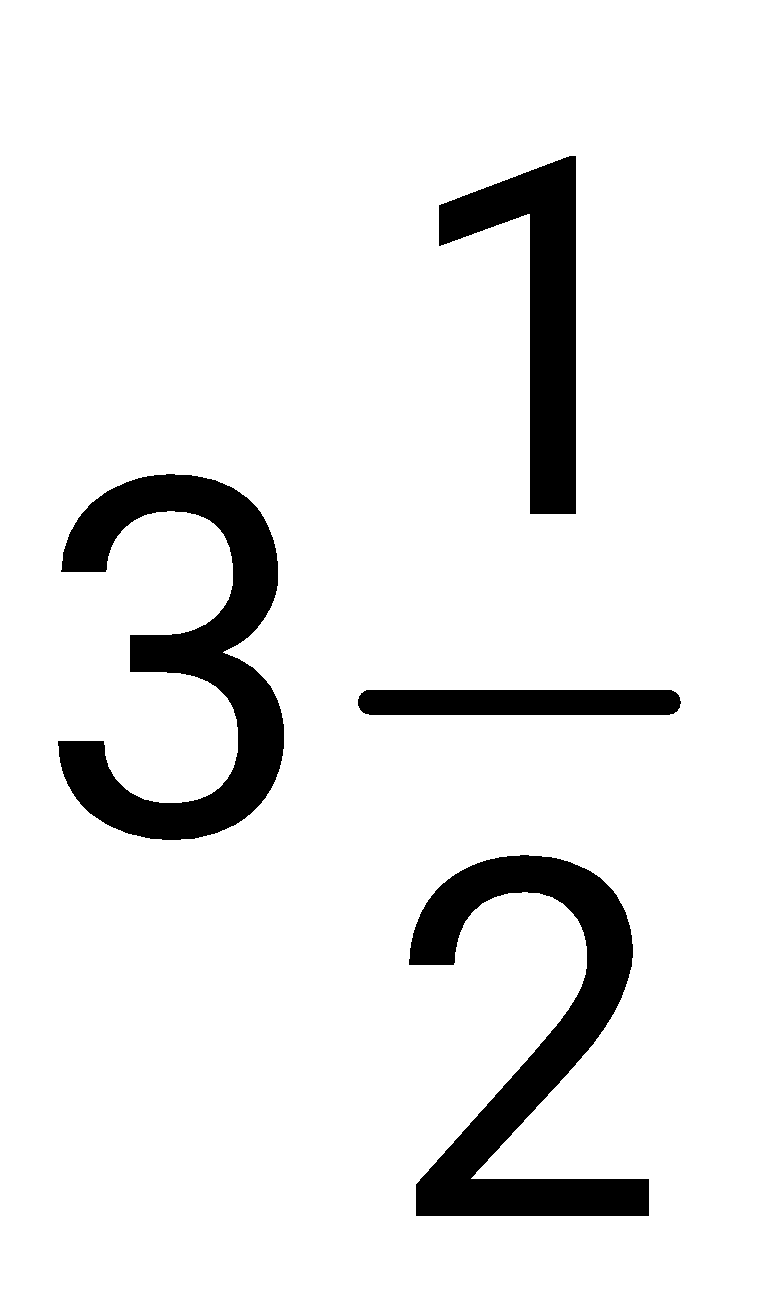

A  digit, 2 V full scale slope ADC has its integration time set to 300ms. If the input to the ADC is (1+1sin314t)V, then the ADC output will be

digit, 2 V full scale slope ADC has its integration time set to 300ms. If the input to the ADC is (1+1sin314t)V, then the ADC output will be

1.000

1.999

1.414

1.500

A 3.5 digit ADC just implies that it can count from 0 to 1999.The integration time and the clock rate of the counter are related such that a full-scale input (1.999V) gives 1999 counts. From this, you can infer that the clock speed is 2000 counts/300 ms = 6667 Hz. Therefore, a half-scale input will give half the count in the counter, or 1000 counts.

The only reason the integration time was given was so that you would realize that it incorporates only whole cycles of the AC frequency, and since the mean value of a sine wave is zero, it contributes nothing to the final reading.