Login to track your progress, bookmark questions, and view history.

Practice over 1000+ GATE-level questions from this topic!

Designed to match the latest GATE pattern with topic-wise precision, difficulty tagging, and detailed solutions.

Q#1

Logic Family

GATE EE 2006

MCQ

+2 marks

-0.66 marks

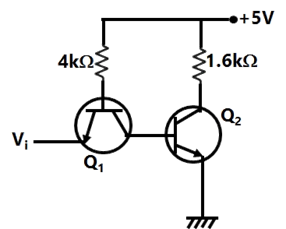

A TTL NOT gate circuit is shown in figure. Assuming VBE = 0.7V of both the transistors, if Vi = 3.0 V, then the states of the two transistors will be

ON and

ON and  OFF

OFF

reverse ON and

reverse ON and  OFF

OFF

reverse ON and

reverse ON and  ON

ON

OFF and

OFF and  reverse ON

reverse ON

Explanation:

In TTL Logic, if the input is high then the Transistor Q1 is in Reverse Active Mode and when input is low then the Transistor is in Forward Active Mode. In reverse active mode, the current flows from emitter to collector and turns ON the transistor Q2.

Q1 reverse ON and Q2 is ON.

Login to keep track of your progress with the tool with daily goals, questions preparation and more.

Browse Practice Questions by Chapters / Topics in Browse Practice Questions by Chapters / Topics in GATE Electrical Engineering

Total Questions

Attempted

% Attempted

Correct

% Correct

Login to keep track of your progress with the tool with daily goals, questions preparation and more.

Login to track your progress, bookmark questions, and view history.