Login to track your progress, bookmark questions, and view history.

Practice over 1000+ GATE-level questions from this topic!

Designed to match the latest GATE pattern with topic-wise precision, difficulty tagging, and detailed solutions.

Q#1

Network Theorems (DC Circuits)

GATE EE 2009

MCQ

+2 marks

-0.66 marks

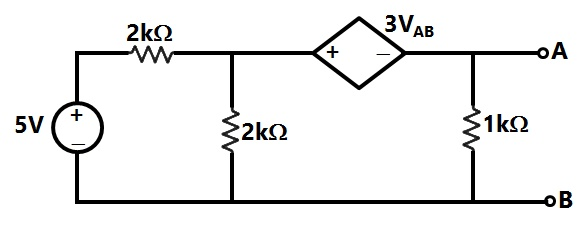

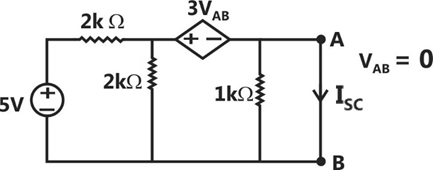

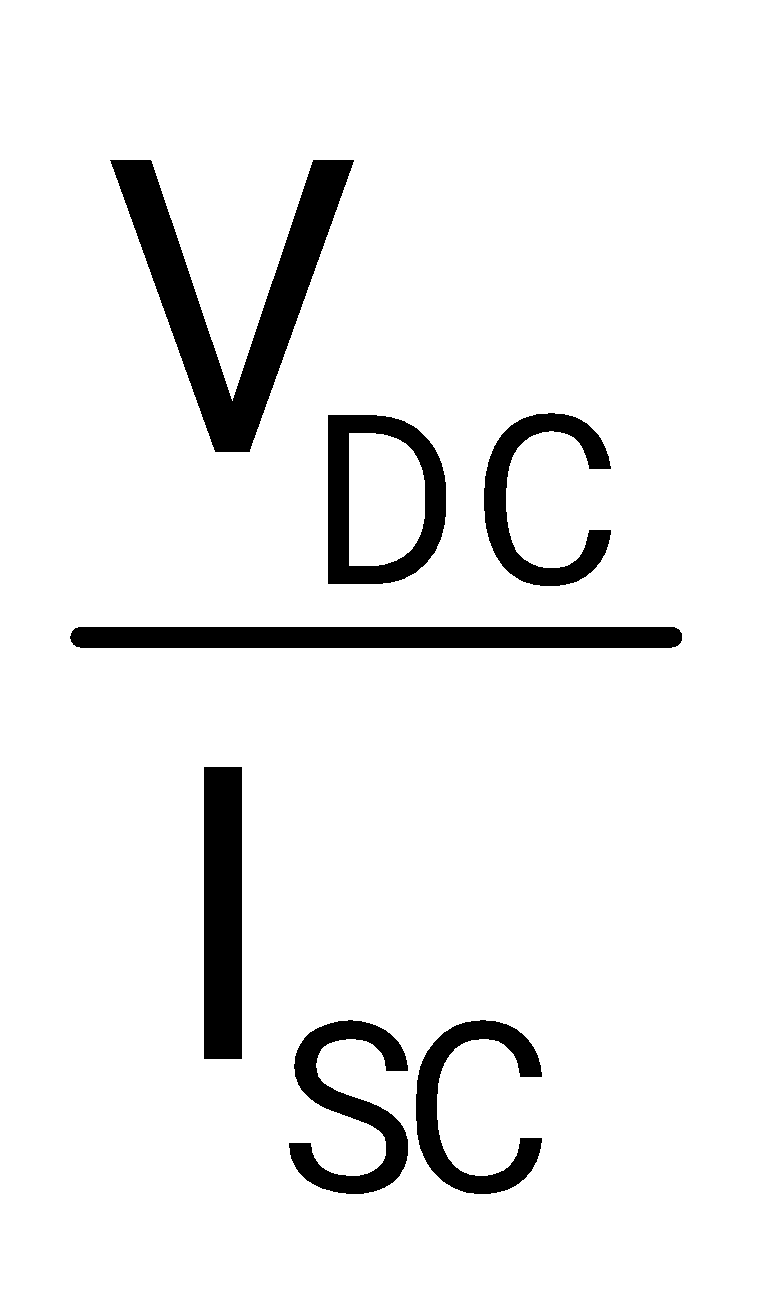

For the circuit given above, the Thevenin's resistance across the terminals A and B is

0.5 kΩ

0.2 kΩ

1 kΩ

0.11 kΩ

Explanation:

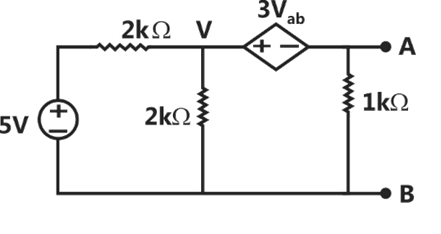

For Vth, the load terminals must be open circuited as shown below,

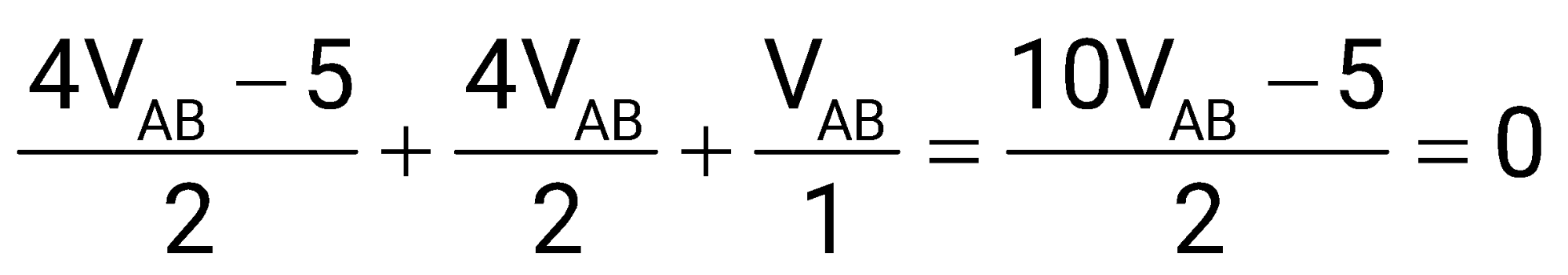

Applying KCL at node with voltage ‘V’

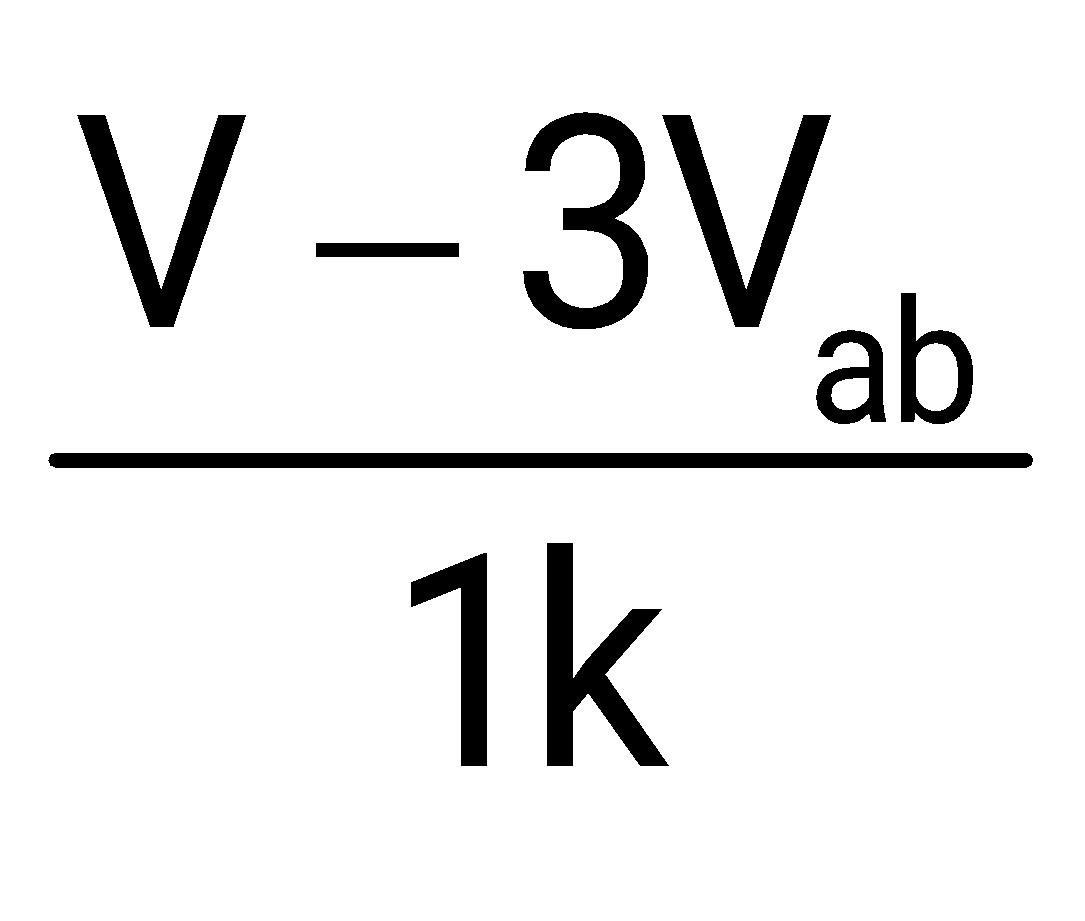

+

+  +

+  = 0 -------- (1)

= 0 -------- (1)

By KVL,

VAB + 3VAB = V

V = 4 VAB --------(2)

from (1) & (2)

+

+  = 0

= 0

VAB = 0.5V

For RTh

Calculate IN or ISC

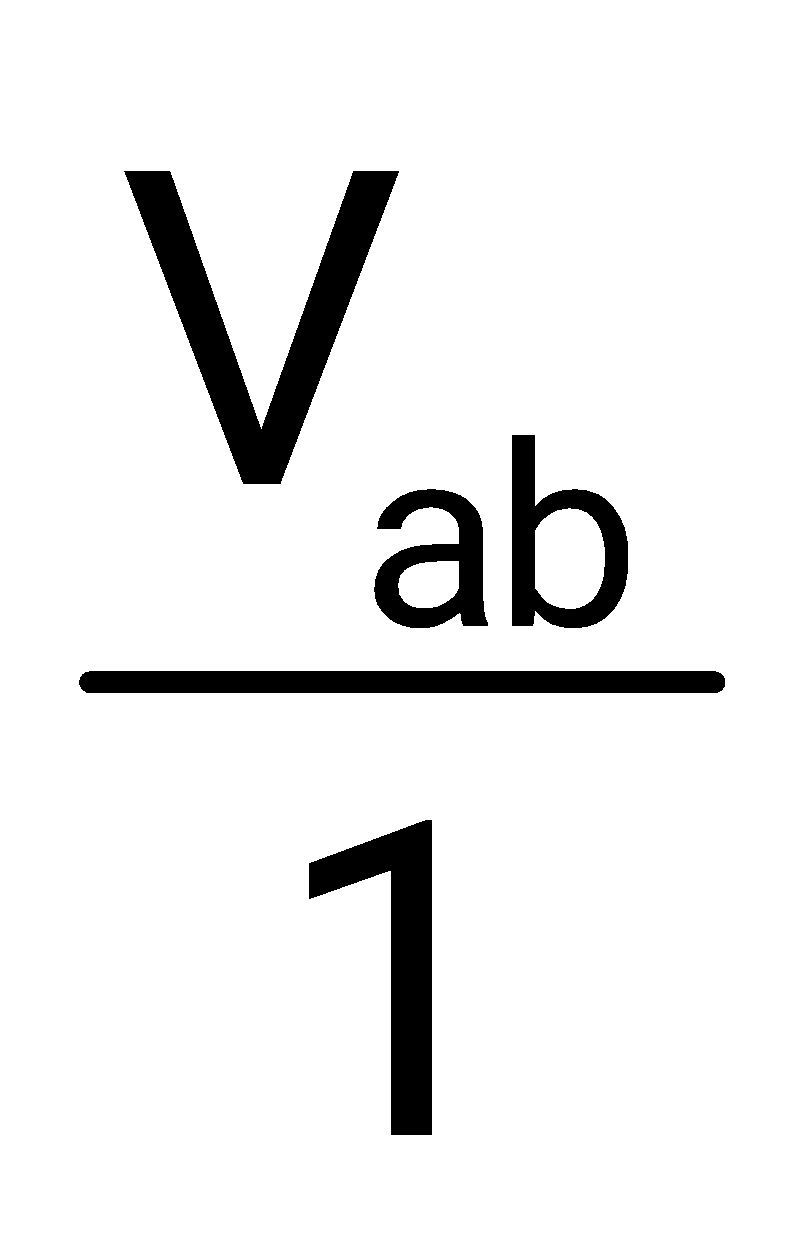

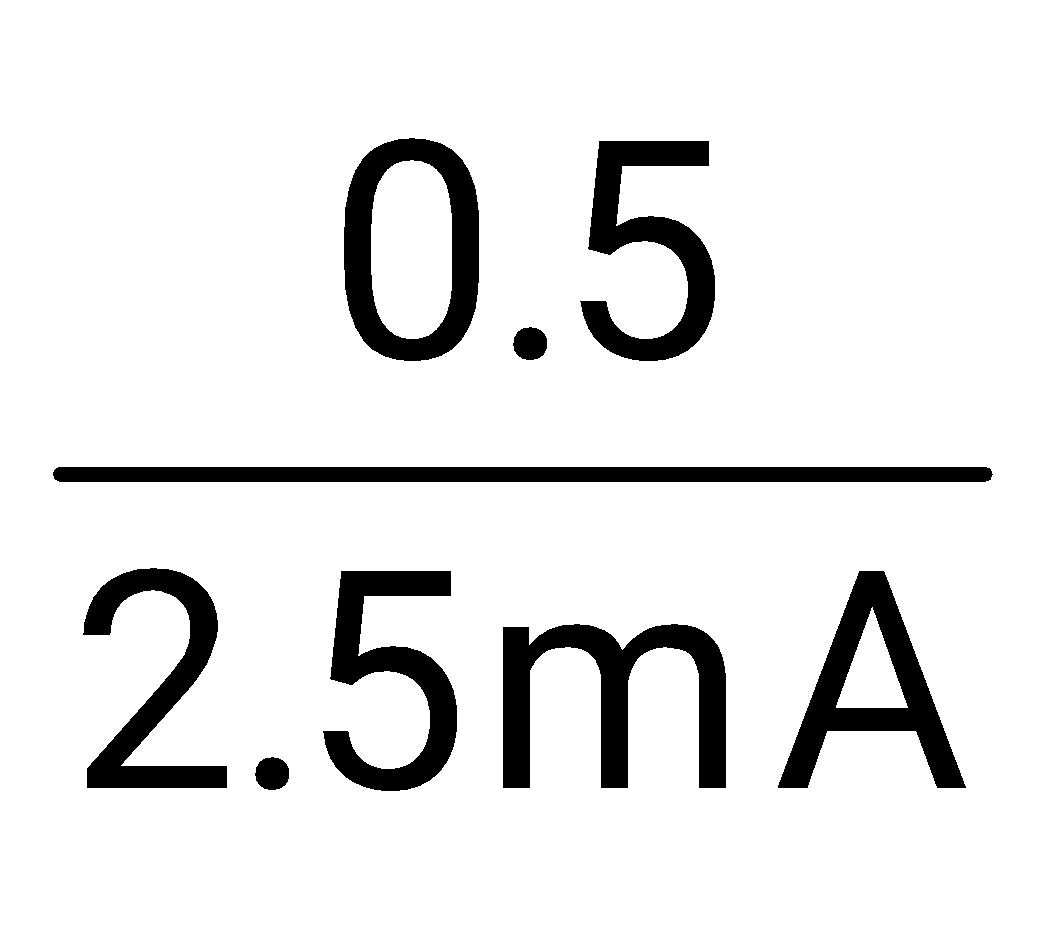

Rth =  =

=  =

=

Login to keep track of your progress with the tool with daily goals, questions preparation and more.

Browse Practice Questions by Chapters / Topics in Browse Practice Questions by Chapters / Topics in GATE Electrical Engineering

Total Questions

Attempted

% Attempted

Correct

% Correct

Login to keep track of your progress with the tool with daily goals, questions preparation and more.

Login to track your progress, bookmark questions, and view history.