Practice over 1000+ GATE-level questions from this topic!

Designed to match the latest GATE pattern with topic-wise precision, difficulty tagging, and detailed solutions.

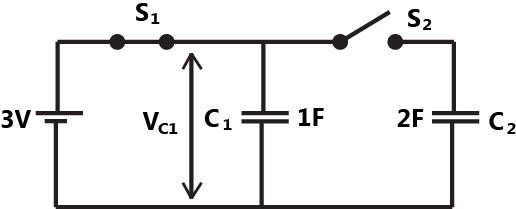

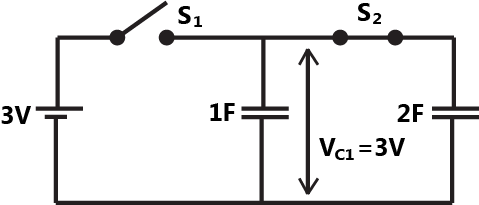

In the figure shown, all elements used are ideal. For time t < 0, \(S_1\) remained closed and \(S_2\) open. At

t = 0, \(S_1\) is opened and \(S_2\) is closed. If the voltage \(Vc_2\) across the capacitor \(C_2\) at t = 0 is zero, the voltage across the capacitor combination at  will be

will be

1V

2V

1.5V

3V

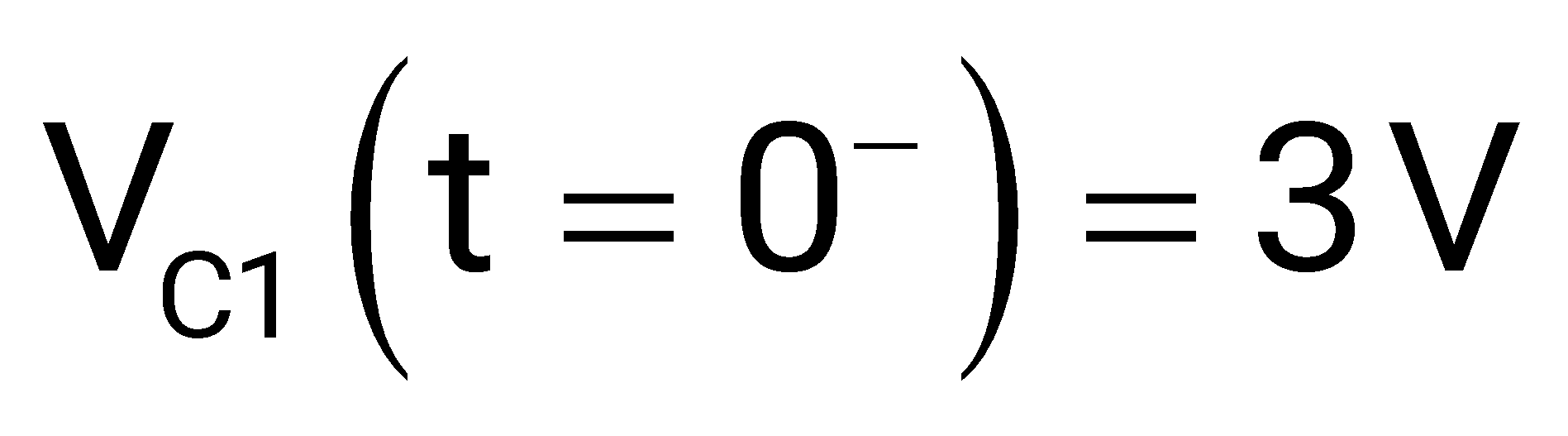

For t < 0, the circuit configuration is shown below,

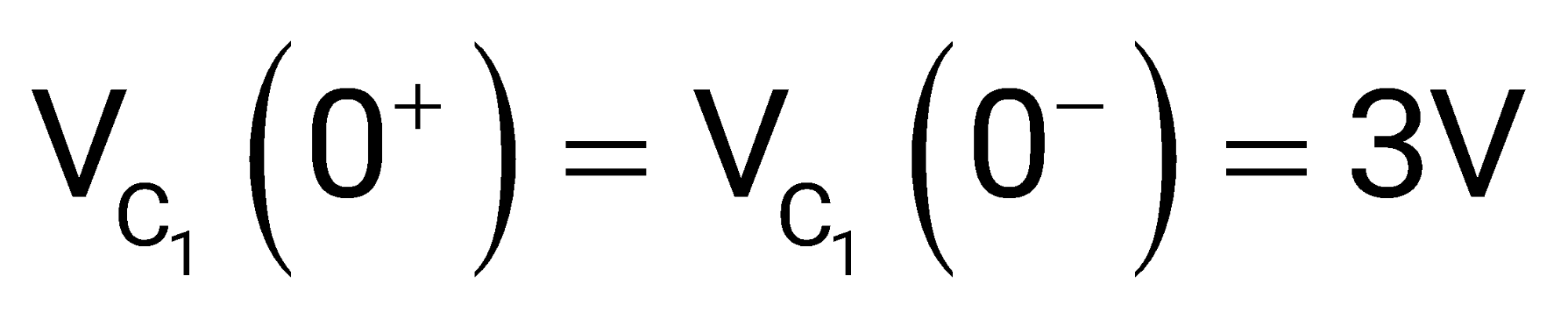

Since voltage across capacitor doesn’t change immediately

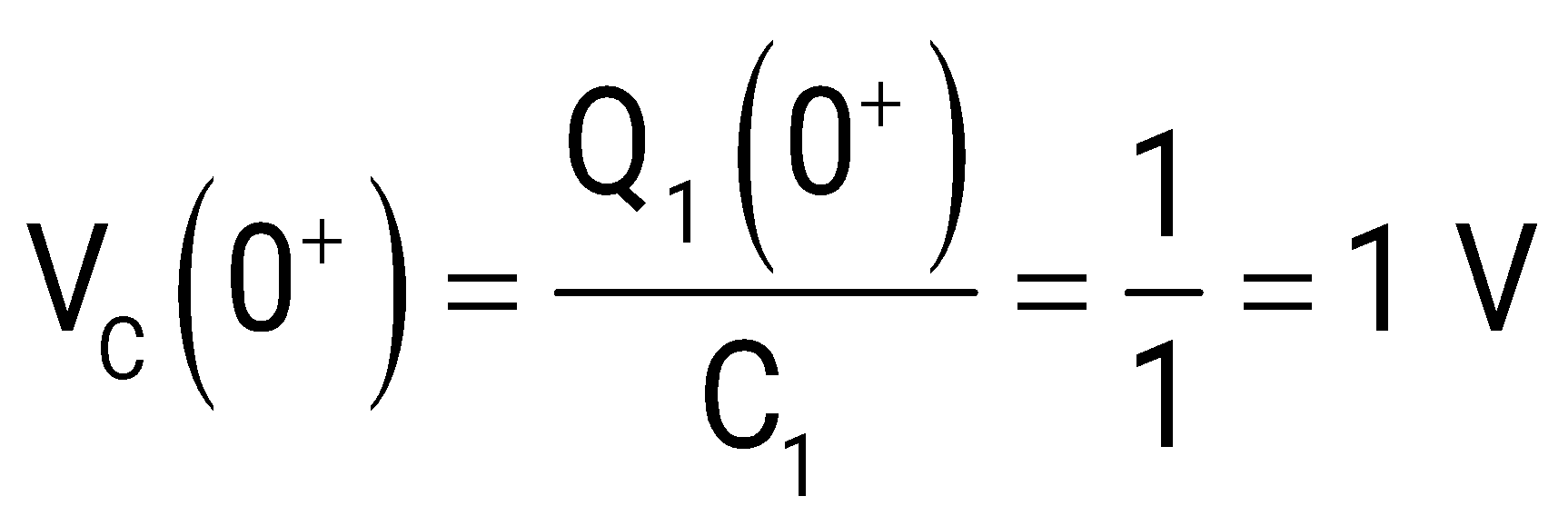

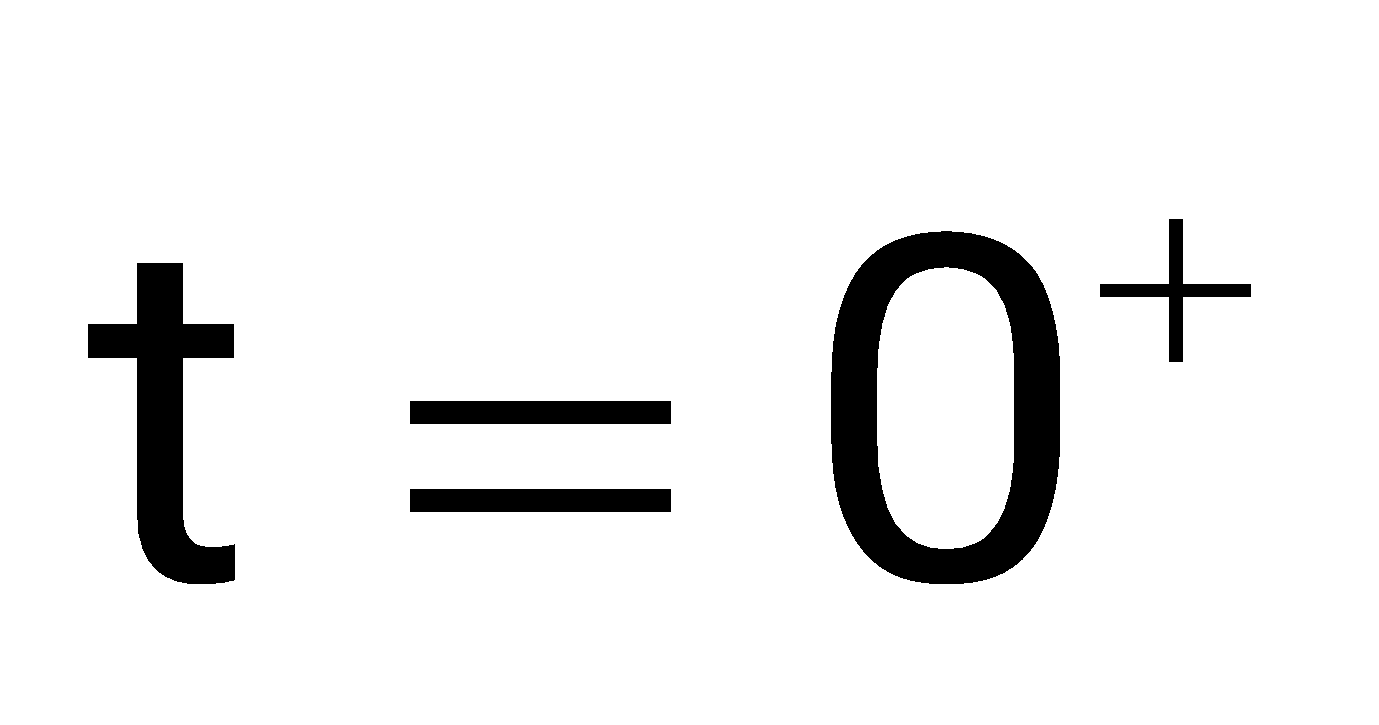

At  , the circuit configuration is shown below,

, the circuit configuration is shown below,

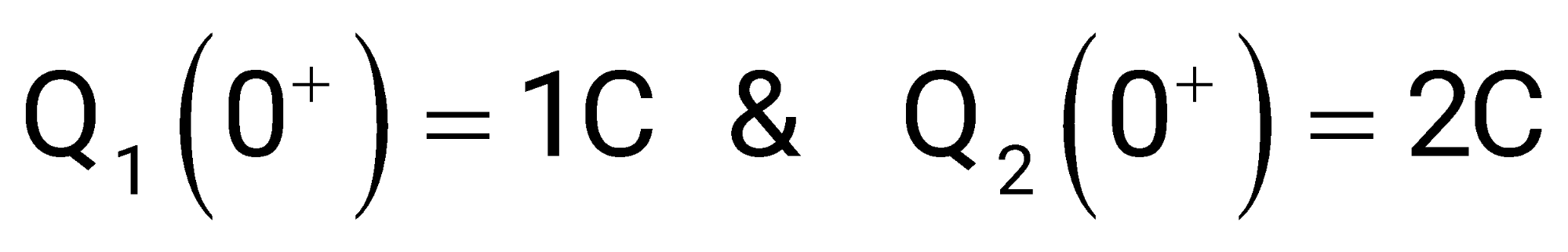

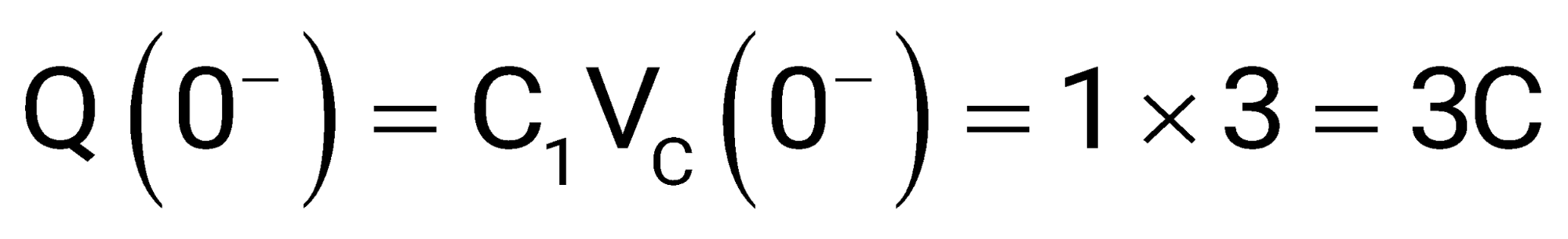

Change stored in  before t=0

before t=0

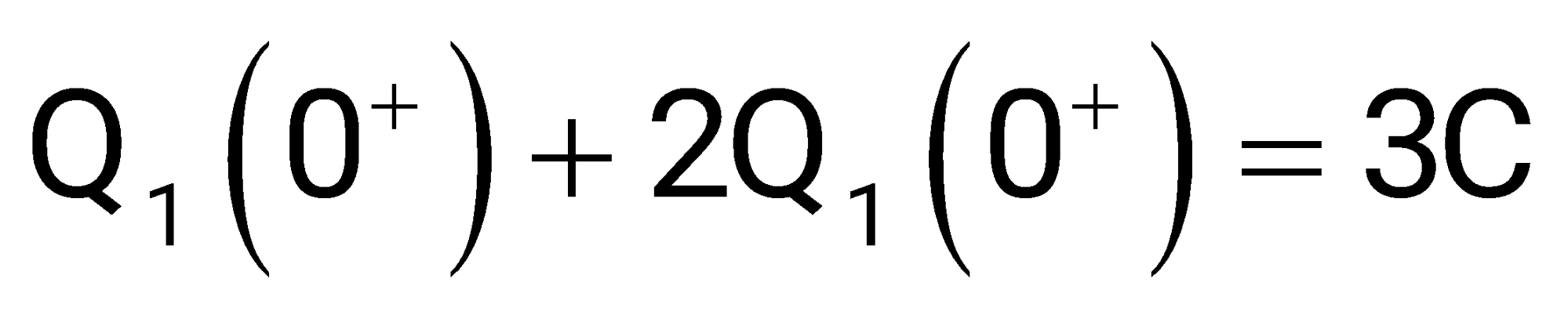

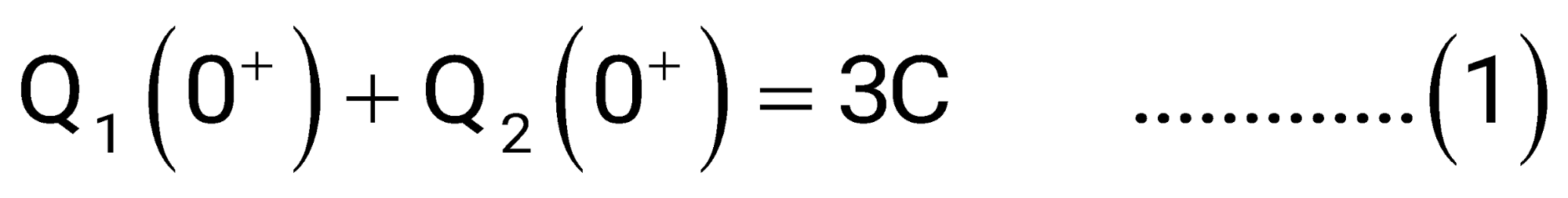

Since, there is no resistor in the circuit, the charge shall remain conserved.

So, charge stored after t=0 in the combination of capacitor

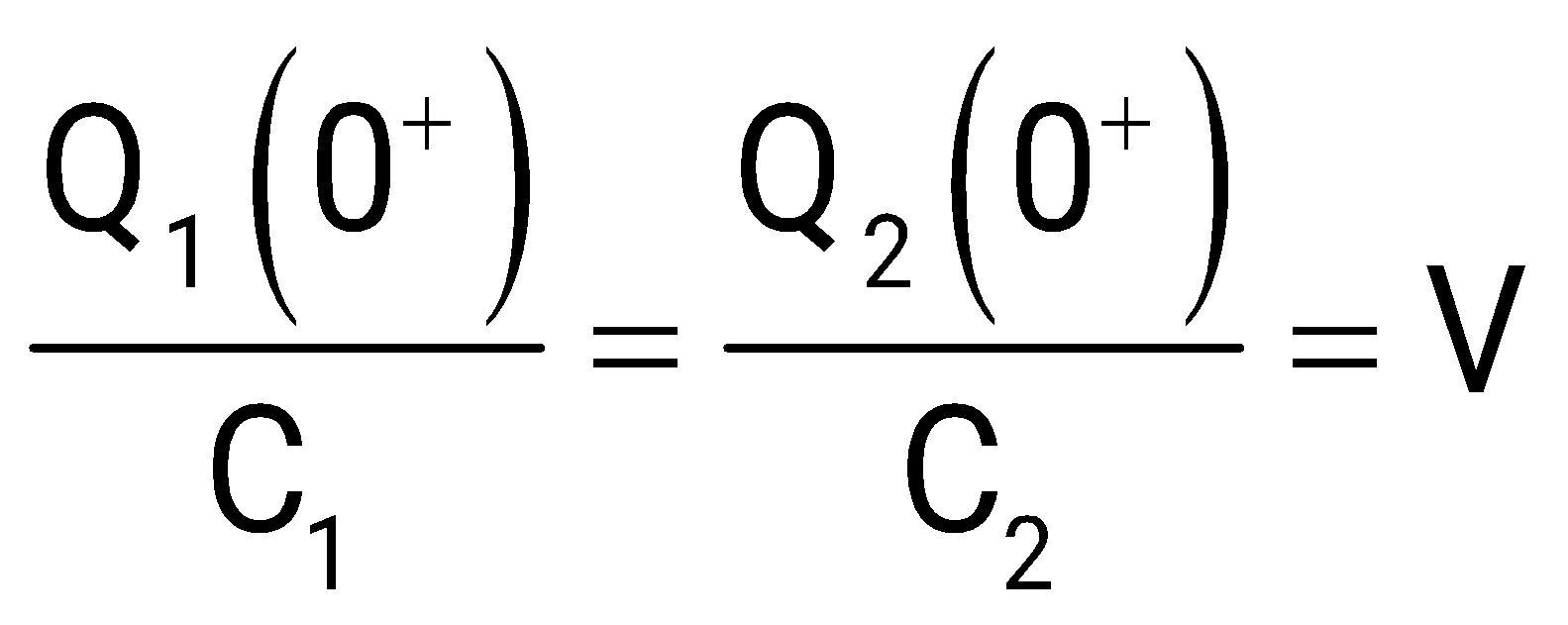

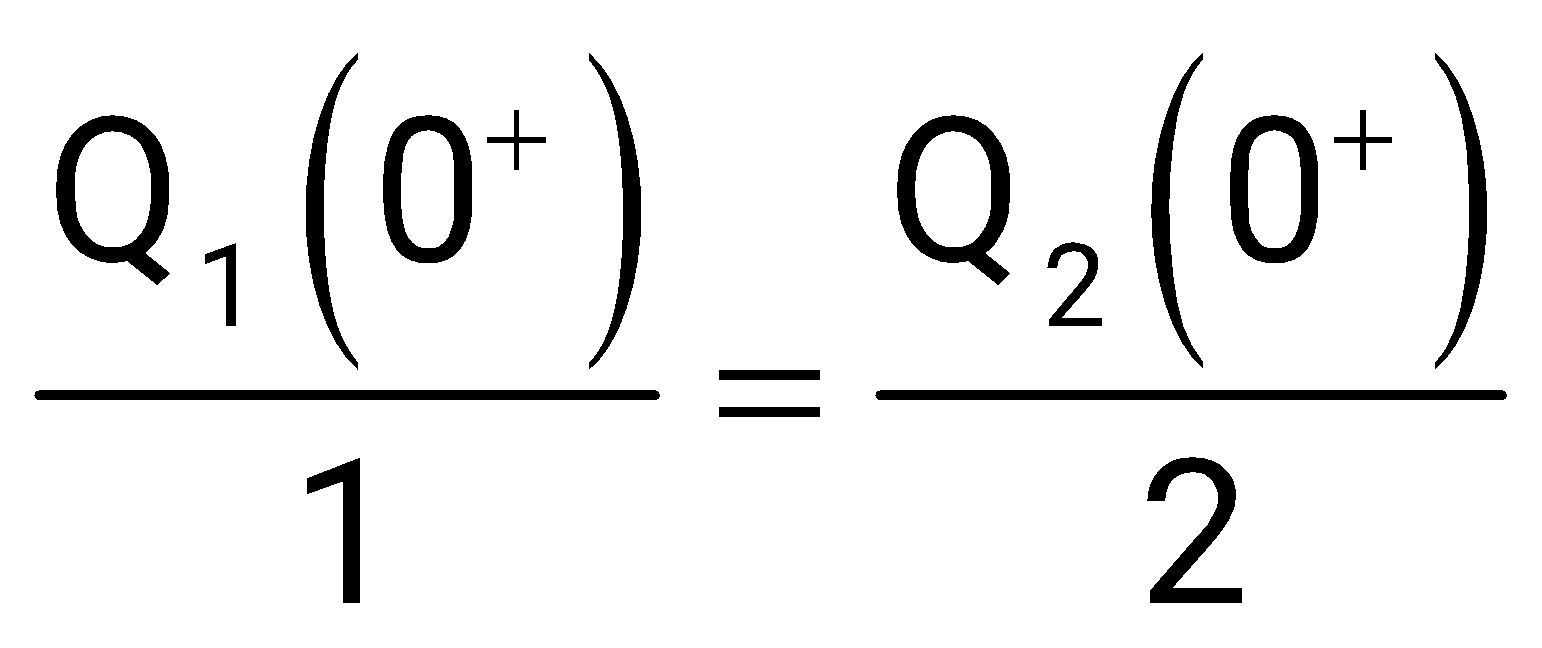

Since voltage across both capacitor will be identical as both are in parallel

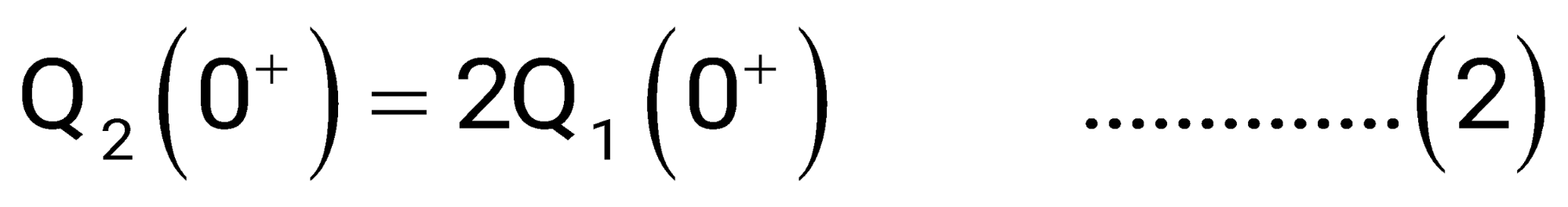

From equation (1) & (2)