Login to track your progress, bookmark questions, and view history.

Practice over 1000+ GATE-level questions from this topic!

Designed to match the latest GATE pattern with topic-wise precision, difficulty tagging, and detailed solutions.

Q#1

Microprocessor

GATE EE 2002

MCQ

+1 mark

-0.33 marks

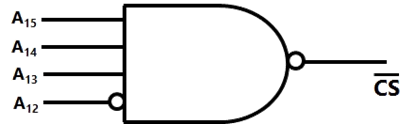

The logic circuit used to generate the active low chip selects (CS) by an 8085 microprocessor to address a peripheral is shown in Figure. The peripheral will respond to addresses in the range.

E000-EFFF

000E-FFFE

1000-FFFF

0001-FFF1

Explanation:

Since, the CS signals is an active low signal so the output of NAND Gate must be 0 to assert the Chip Select signal. Hence, all inputs must be asserted to make the output zero.

Since, A12 is associated with an inverter, it must be LOW to be asserted.

A15 = 1, A14 = 1, A13 = 1, A12 = 0.

Minimum Address = 1110 0000 0000 0000 (E000 H)

Maximum Address = 1110 1111 1111 1111 (EFFF H)

Login to keep track of your progress with the tool with daily goals, questions preparation and more.

Browse Practice Questions by Chapters / Topics in Browse Practice Questions by Chapters / Topics in GATE Electrical Engineering

Total Questions

Attempted

% Attempted

Correct

% Correct

Login to keep track of your progress with the tool with daily goals, questions preparation and more.

Login to track your progress, bookmark questions, and view history.