Login to track your progress, bookmark questions, and view history.

Practice over 1000+ GATE-level questions from this topic!

Designed to match the latest GATE pattern with topic-wise precision, difficulty tagging, and detailed solutions.

Q#1

Data Converters

GATE EE 2003

MCQ

+2 marks

-0.66 marks

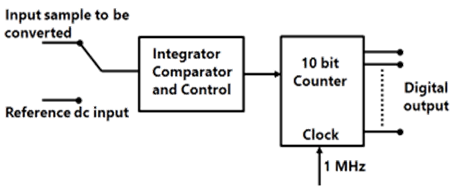

The simplified block diagram of a 10-bit A/D converter of dual slope integrator type is shown in figure. The 10-bit counter at the output is clocked by a 1MHz clock. Assuming negligible timing overhead for the control logic, the maximum frequency of the analog signal that can be converted using this A/D converter is approximately

2 kHz

1 kHz

500 Hz

250 Hz

Explanation:

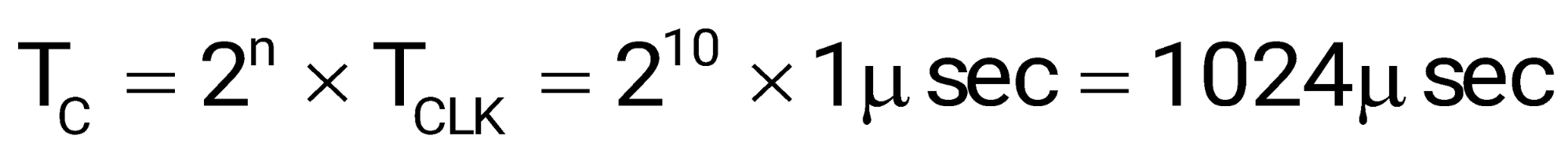

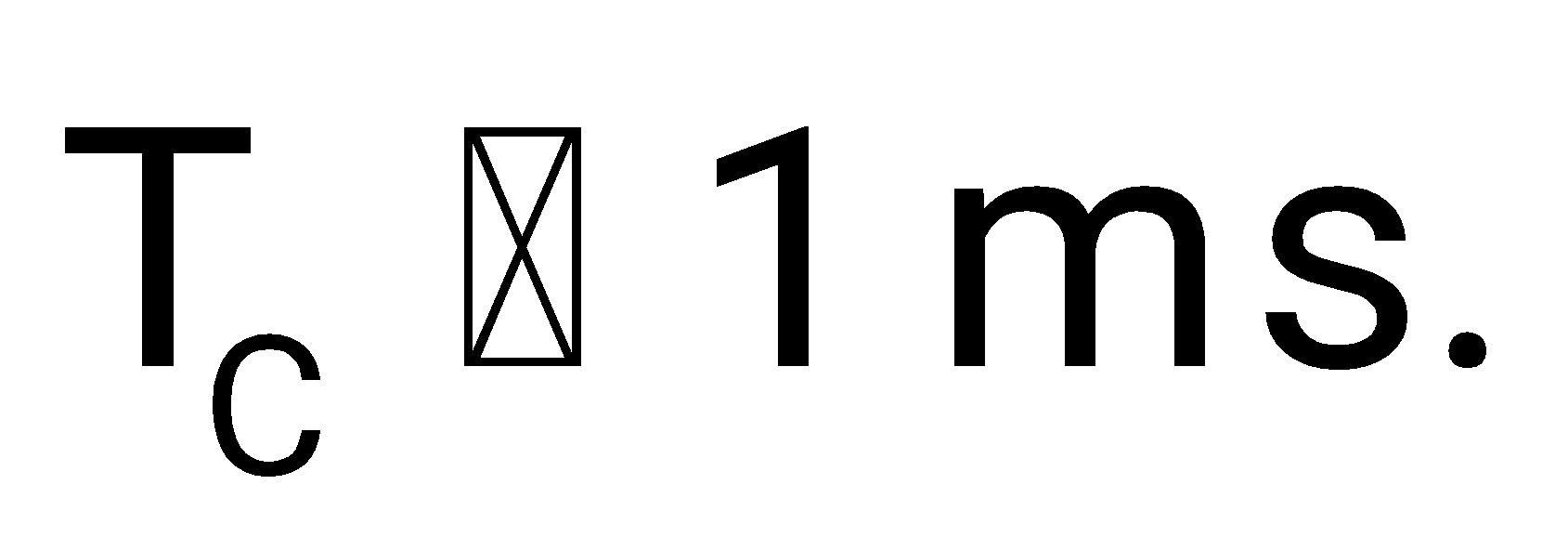

Minimum conversion time of dual slope ADC

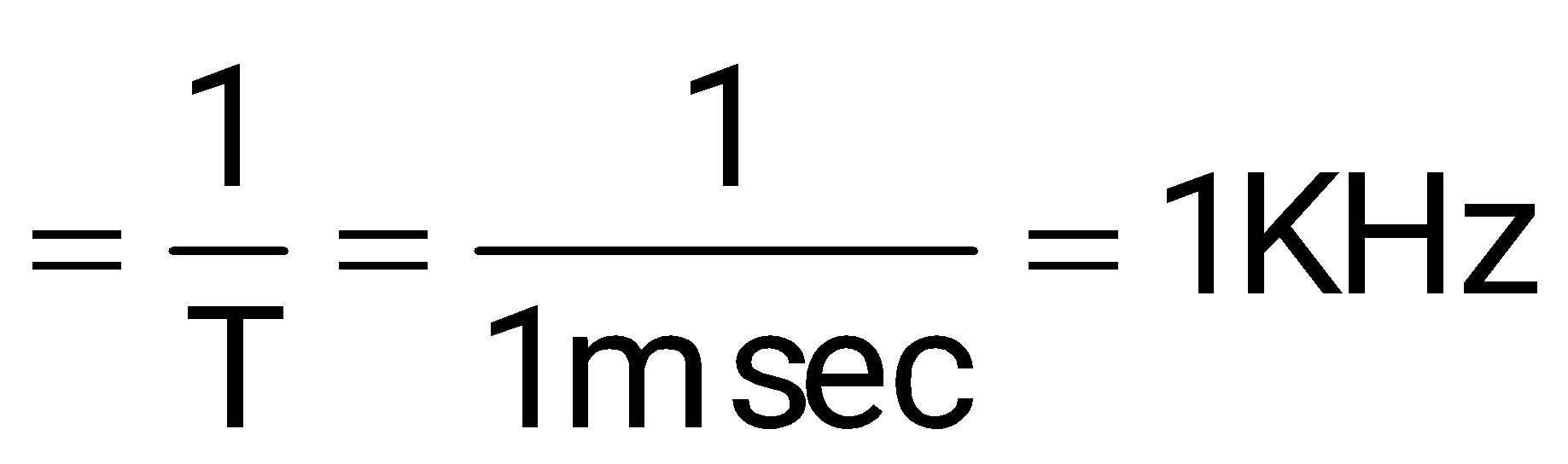

Maximum sampling frequency

Login to keep track of your progress with the tool with daily goals, questions preparation and more.

Browse Practice Questions by Chapters / Topics in Browse Practice Questions by Chapters / Topics in GATE Electrical Engineering

Total Questions

Attempted

% Attempted

Correct

% Correct

Login to keep track of your progress with the tool with daily goals, questions preparation and more.

Login to track your progress, bookmark questions, and view history.